a8a4eddc319819ab57029f40ea149657.ppt

- Количество слайдов: 17

Controls renovation workshop Standardized Hardware Modules Javier Serrano, AB-CO-HT MJD 54803

Controls renovation workshop Standardized Hardware Modules Javier Serrano, AB-CO-HT MJD 54803

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 2

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 2

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 3

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 3

Introduction: the Controls HW Kit l Both VME and PCI. l Includes analog and digital I/O, field busses (incl. timing), stepping motor control and misc (pulse repeaters, adapters…). l For each component, we (will) support: ¡ ¡ ¡ ¡ ¡ Hardware: user manual, help in debugging… Device driver with I/O emulation for Linux, with documentation. A test program on top of the driver, with documentation. A library on top of the driver, with documentation and usage examples. We don’t support anyone bypassing this library. A test program on top of the library, with documentation. A test procedure. An installation procedure. A wiki with known issues and the level of support offered for a given module (if different from “complete support”). Version management of all HW and SW above. All of the above are based on templates and standard procedures. This is of course important for maintainability.

Introduction: the Controls HW Kit l Both VME and PCI. l Includes analog and digital I/O, field busses (incl. timing), stepping motor control and misc (pulse repeaters, adapters…). l For each component, we (will) support: ¡ ¡ ¡ ¡ ¡ Hardware: user manual, help in debugging… Device driver with I/O emulation for Linux, with documentation. A test program on top of the driver, with documentation. A library on top of the driver, with documentation and usage examples. We don’t support anyone bypassing this library. A test program on top of the library, with documentation. A test procedure. An installation procedure. A wiki with known issues and the level of support offered for a given module (if different from “complete support”). Version management of all HW and SW above. All of the above are based on templates and standard procedures. This is of course important for maintainability.

Motivations l Standard hardware modules ¡ Obsolescence problems l Some solutions are more than 30 years old → poor reliability. l Detailed knowledge has been lost: CAMAC, PSB matrix. . . → poor support. ¡ Quality of support from some companies is poor. l Drivers ¡ Reduced maintenance team. l Need to reduce maintenance costs by standardizing. l A standard approach for drivers/libraries and test programs is being defined. l Big upgrade operation needed after that, with help from industry and temporary labour.

Motivations l Standard hardware modules ¡ Obsolescence problems l Some solutions are more than 30 years old → poor reliability. l Detailed knowledge has been lost: CAMAC, PSB matrix. . . → poor support. ¡ Quality of support from some companies is poor. l Drivers ¡ Reduced maintenance team. l Need to reduce maintenance costs by standardizing. l A standard approach for drivers/libraries and test programs is being defined. l Big upgrade operation needed after that, with help from industry and temporary labour.

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 6

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 6

General strategy l Use the new FPGA Mezzanine Card (FMC) Vita 57 standard. l Design/buy FMCs which can be placed on VME, PCIe… carriers. l In the following, we assign a work package per module category, which includes both SW and HW development. ¡ ¡ ¡ WP 1: Analog input. WP 2: Analog output. WP 3: Digital I/O with interrupts. WP 4: timing and field busses. WP 5: stepping motor control. WP 6: misc developments, including carriers. l Special work package (WP 7) for the migration of legacy device drivers to the new front end platforms. l Assumptions for budgeting and manpower: a designer designs one module in 3 FTE months, a software developer takes roughly 2 FTE months to do his/her part, and the whole thing including prototypes costs 30 k. l Following slides show proposed state of HW kit in two years, with needs for work highlighted in orange.

General strategy l Use the new FPGA Mezzanine Card (FMC) Vita 57 standard. l Design/buy FMCs which can be placed on VME, PCIe… carriers. l In the following, we assign a work package per module category, which includes both SW and HW development. ¡ ¡ ¡ WP 1: Analog input. WP 2: Analog output. WP 3: Digital I/O with interrupts. WP 4: timing and field busses. WP 5: stepping motor control. WP 6: misc developments, including carriers. l Special work package (WP 7) for the migration of legacy device drivers to the new front end platforms. l Assumptions for budgeting and manpower: a designer designs one module in 3 FTE months, a software developer takes roughly 2 FTE months to do his/her part, and the whole thing including prototypes costs 30 k. l Following slides show proposed state of HW kit in two years, with needs for work highlighted in orange.

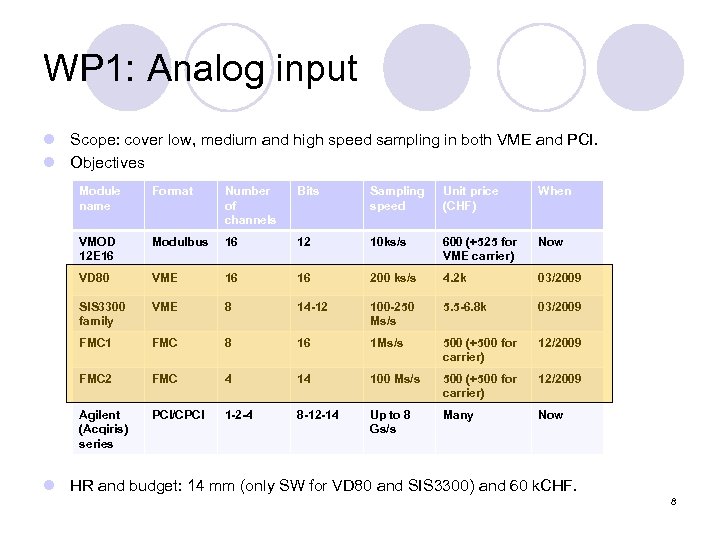

WP 1: Analog input l Scope: cover low, medium and high speed sampling in both VME and PCI. l Objectives Module name Format Number of channels Bits Sampling speed Unit price (CHF) When VMOD 12 E 16 Modulbus 16 12 10 ks/s 600 (+525 for VME carrier) Now VD 80 VME 16 16 200 ks/s 4. 2 k 03/2009 SIS 3300 family VME 8 14 -12 100 -250 Ms/s 5. 5 -6. 8 k 03/2009 FMC 1 FMC 8 16 1 Ms/s 500 (+500 for carrier) 12/2009 FMC 2 FMC 4 14 100 Ms/s 500 (+500 for carrier) 12/2009 Agilent (Acqiris) series PCI/CPCI 1 -2 -4 8 -12 -14 Up to 8 Gs/s Many Now l HR and budget: 14 mm (only SW for VD 80 and SIS 3300) and 60 k. CHF. 8

WP 1: Analog input l Scope: cover low, medium and high speed sampling in both VME and PCI. l Objectives Module name Format Number of channels Bits Sampling speed Unit price (CHF) When VMOD 12 E 16 Modulbus 16 12 10 ks/s 600 (+525 for VME carrier) Now VD 80 VME 16 16 200 ks/s 4. 2 k 03/2009 SIS 3300 family VME 8 14 -12 100 -250 Ms/s 5. 5 -6. 8 k 03/2009 FMC 1 FMC 8 16 1 Ms/s 500 (+500 for carrier) 12/2009 FMC 2 FMC 4 14 100 Ms/s 500 (+500 for carrier) 12/2009 Agilent (Acqiris) series PCI/CPCI 1 -2 -4 8 -12 -14 Up to 8 Gs/s Many Now l HR and budget: 14 mm (only SW for VD 80 and SIS 3300) and 60 k. CHF. 8

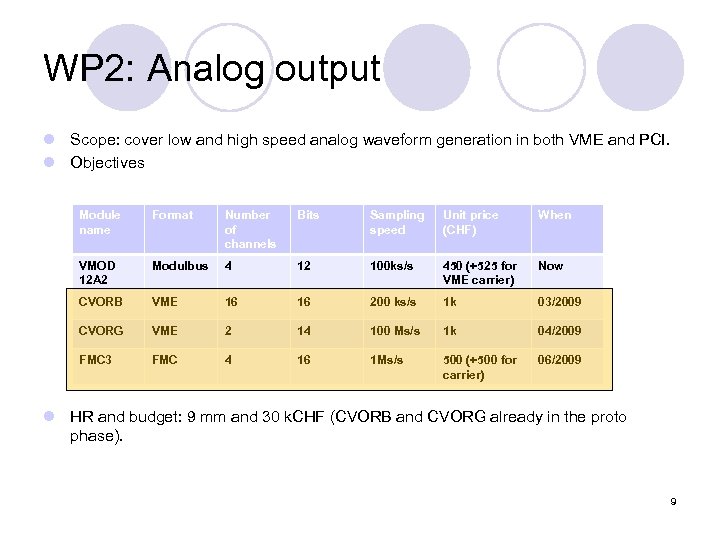

WP 2: Analog output l Scope: cover low and high speed analog waveform generation in both VME and PCI. l Objectives Module name Format Number of channels Bits Sampling speed Unit price (CHF) When VMOD 12 A 2 Modulbus 4 12 100 ks/s 450 (+525 for VME carrier) Now CVORB VME 16 16 200 ks/s 1 k 03/2009 CVORG VME 2 14 100 Ms/s 1 k 04/2009 FMC 3 FMC 4 16 1 Ms/s 500 (+500 for carrier) 06/2009 l HR and budget: 9 mm and 30 k. CHF (CVORB and CVORG already in the proto phase). 9

WP 2: Analog output l Scope: cover low and high speed analog waveform generation in both VME and PCI. l Objectives Module name Format Number of channels Bits Sampling speed Unit price (CHF) When VMOD 12 A 2 Modulbus 4 12 100 ks/s 450 (+525 for VME carrier) Now CVORB VME 16 16 200 ks/s 1 k 03/2009 CVORG VME 2 14 100 Ms/s 1 k 04/2009 FMC 3 FMC 4 16 1 Ms/s 500 (+500 for carrier) 06/2009 l HR and budget: 9 mm and 30 k. CHF (CVORB and CVORG already in the proto phase). 9

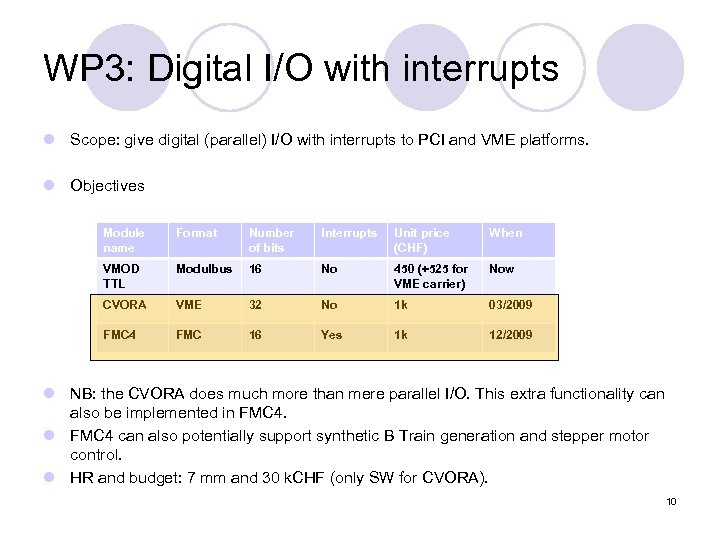

WP 3: Digital I/O with interrupts l Scope: give digital (parallel) I/O with interrupts to PCI and VME platforms. l Objectives Module name Format Number of bits Interrupts Unit price (CHF) When VMOD TTL Modulbus 16 No 450 (+525 for VME carrier) Now CVORA VME 32 No 1 k 03/2009 FMC 4 FMC 16 Yes 1 k 12/2009 l NB: the CVORA does much more than mere parallel I/O. This extra functionality can also be implemented in FMC 4. l FMC 4 can also potentially support synthetic B Train generation and stepper motor control. l HR and budget: 7 mm and 30 k. CHF (only SW for CVORA). 10

WP 3: Digital I/O with interrupts l Scope: give digital (parallel) I/O with interrupts to PCI and VME platforms. l Objectives Module name Format Number of bits Interrupts Unit price (CHF) When VMOD TTL Modulbus 16 No 450 (+525 for VME carrier) Now CVORA VME 32 No 1 k 03/2009 FMC 4 FMC 16 Yes 1 k 12/2009 l NB: the CVORA does much more than mere parallel I/O. This extra functionality can also be implemented in FMC 4. l FMC 4 can also potentially support synthetic B Train generation and stepper motor control. l HR and budget: 7 mm and 30 k. CHF (only SW for CVORA). 10

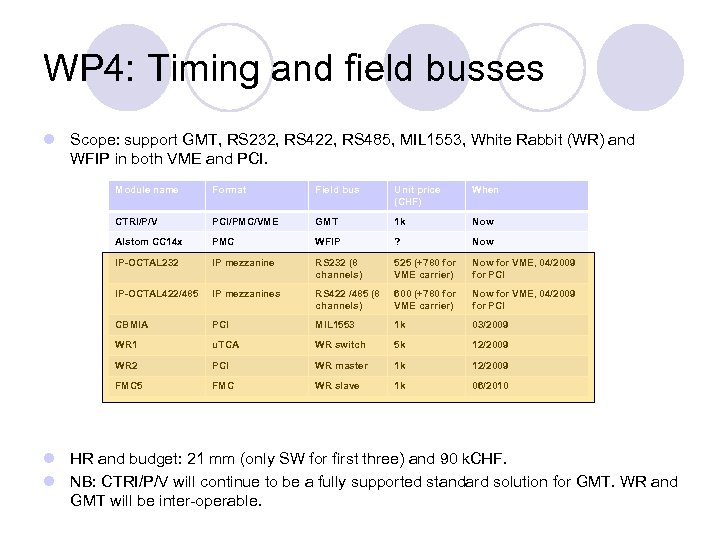

WP 4: Timing and field busses l Scope: support GMT, RS 232, RS 422, RS 485, MIL 1553, White Rabbit (WR) and WFIP in both VME and PCI. Module name Format Field bus Unit price (CHF) When CTRI/P/V PCI/PMC/VME GMT 1 k Now Alstom CC 14 x PMC WFIP ? Now IP-OCTAL 232 IP mezzanine RS 232 (8 channels) 525 (+780 for VME carrier) Now for VME, 04/2009 for PCI IP-OCTAL 422/485 IP mezzanines RS 422 /485 (8 channels) 600 (+780 for VME carrier) Now for VME, 04/2009 for PCI CBMIA PCI MIL 1553 1 k 03/2009 WR 1 u. TCA WR switch 5 k 12/2009 WR 2 PCI WR master 1 k 12/2009 FMC 5 FMC WR slave 1 k 06/2010 l HR and budget: 21 mm (only SW for first three) and 90 k. CHF. l NB: CTRI/P/V will continue to be a fully supported standard solution for GMT. WR and GMT will be inter-operable.

WP 4: Timing and field busses l Scope: support GMT, RS 232, RS 422, RS 485, MIL 1553, White Rabbit (WR) and WFIP in both VME and PCI. Module name Format Field bus Unit price (CHF) When CTRI/P/V PCI/PMC/VME GMT 1 k Now Alstom CC 14 x PMC WFIP ? Now IP-OCTAL 232 IP mezzanine RS 232 (8 channels) 525 (+780 for VME carrier) Now for VME, 04/2009 for PCI IP-OCTAL 422/485 IP mezzanines RS 422 /485 (8 channels) 600 (+780 for VME carrier) Now for VME, 04/2009 for PCI CBMIA PCI MIL 1553 1 k 03/2009 WR 1 u. TCA WR switch 5 k 12/2009 WR 2 PCI WR master 1 k 12/2009 FMC 5 FMC WR slave 1 k 06/2010 l HR and budget: 21 mm (only SW for first three) and 90 k. CHF. l NB: CTRI/P/V will continue to be a fully supported standard solution for GMT. WR and GMT will be inter-operable.

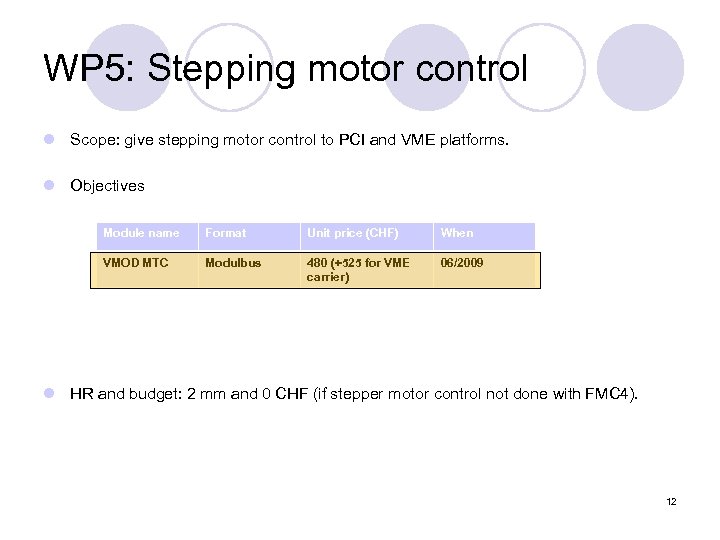

WP 5: Stepping motor control l Scope: give stepping motor control to PCI and VME platforms. l Objectives Module name Format Unit price (CHF) When VMOD MTC Modulbus 480 (+525 for VME carrier) 06/2009 l HR and budget: 2 mm and 0 CHF (if stepper motor control not done with FMC 4). 12

WP 5: Stepping motor control l Scope: give stepping motor control to PCI and VME platforms. l Objectives Module name Format Unit price (CHF) When VMOD MTC Modulbus 480 (+525 for VME carrier) 06/2009 l HR and budget: 2 mm and 0 CHF (if stepper motor control not done with FMC 4). 12

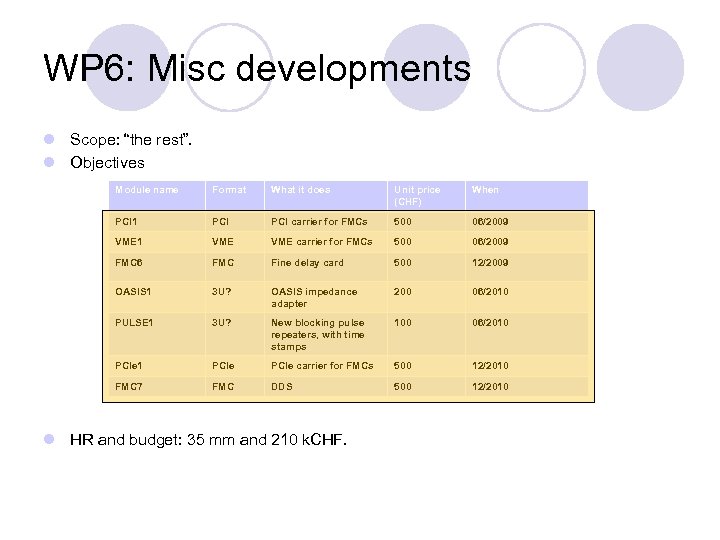

WP 6: Misc developments l Scope: “the rest”. l Objectives Module name Format What it does Unit price (CHF) When PCI 1 PCI carrier for FMCs 500 06/2009 VME 1 VME carrier for FMCs 500 06/2009 FMC 6 FMC Fine delay card 500 12/2009 OASIS 1 3 U? OASIS impedance adapter 200 06/2010 PULSE 1 3 U? New blocking pulse repeaters, with time stamps 100 06/2010 PCIe 1 PCIe carrier for FMCs 500 12/2010 FMC 7 FMC DDS 500 12/2010 l HR and budget: 35 mm and 210 k. CHF.

WP 6: Misc developments l Scope: “the rest”. l Objectives Module name Format What it does Unit price (CHF) When PCI 1 PCI carrier for FMCs 500 06/2009 VME 1 VME carrier for FMCs 500 06/2009 FMC 6 FMC Fine delay card 500 12/2009 OASIS 1 3 U? OASIS impedance adapter 200 06/2010 PULSE 1 3 U? New blocking pulse repeaters, with time stamps 100 06/2010 PCIe 1 PCIe carrier for FMCs 500 12/2010 FMC 7 FMC DDS 500 12/2010 l HR and budget: 35 mm and 210 k. CHF.

WP 7: migration of drivers to new platforms l Some 30 drivers concerned. Not all of them will need rewriting depending on upgrade strategies. l Assume half of them need rework → 30 mm of work. 14

WP 7: migration of drivers to new platforms l Some 30 drivers concerned. Not all of them will need rewriting depending on upgrade strategies. l Assume half of them need rework → 30 mm of work. 14

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 15

Outline l Motivations l Work Packages ¡Scope ¡Objectives ¡Budget Estimation ¡Human Resources l Conclusions l Summary table 15

Conclusions l We need to revise quickly our standard kit of HW modules to deal with lack of support due to obsolescence and also to support the new PCI platforms. l A global schedule is proposed over two years: ¡ Immediate deliverables: l MIL 1553 master in PCI. l VD 80 (100 ks/s 16 channel sampler in VME). l CVORB (GFAS replacement) in VME. ¡ Need in-depth discussion with clients to fine-tune further milestones. l Global estimated cost: 72 mm and 834 k. CHF.

Conclusions l We need to revise quickly our standard kit of HW modules to deal with lack of support due to obsolescence and also to support the new PCI platforms. l A global schedule is proposed over two years: ¡ Immediate deliverables: l MIL 1553 master in PCI. l VD 80 (100 ks/s 16 channel sampler in VME). l CVORB (GFAS replacement) in VME. ¡ Need in-depth discussion with clients to fine-tune further milestones. l Global estimated cost: 72 mm and 834 k. CHF.

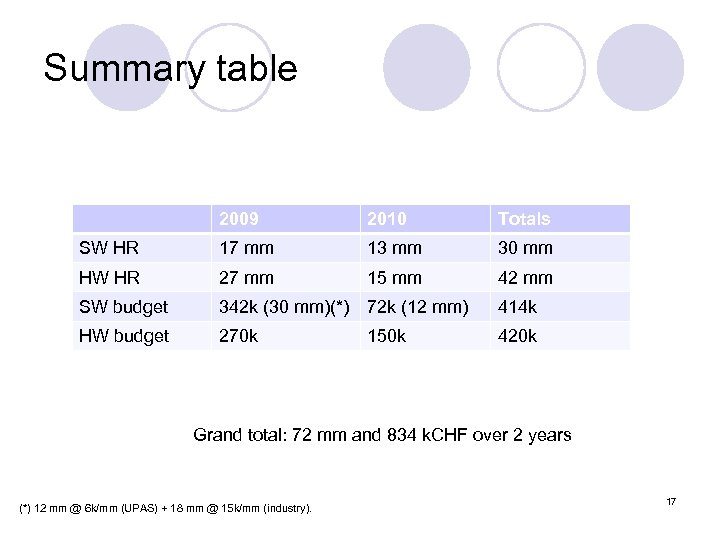

Summary table 2009 2010 Totals SW HR 17 mm 13 mm 30 mm HW HR 27 mm 15 mm 42 mm SW budget 342 k (30 mm)(*) 72 k (12 mm) 414 k HW budget 270 k 150 k 420 k Grand total: 72 mm and 834 k. CHF over 2 years (*) 12 mm @ 6 k/mm (UPAS) + 18 mm @ 15 k/mm (industry). 17

Summary table 2009 2010 Totals SW HR 17 mm 13 mm 30 mm HW HR 27 mm 15 mm 42 mm SW budget 342 k (30 mm)(*) 72 k (12 mm) 414 k HW budget 270 k 150 k 420 k Grand total: 72 mm and 834 k. CHF over 2 years (*) 12 mm @ 6 k/mm (UPAS) + 18 mm @ 15 k/mm (industry). 17