9f391b0c3e41a1bad8f6e7215c930110.ppt

- Количество слайдов: 10

Computer Architecture Lecture 8 by Engineer A. Lecturer Aymen Hasan Al. Awady 30/12/2013 University of Kufa - Informatics Center for Research and Rehabilitation 1 1

1. I/O Interfacing with 8085 • The 8085 MPU needs to be interfaced with the I/O devices to get (in or out) the information from or to the “outside world”. • There are two modes of I/O interfacing which are parallel I/O mode and serial I/O mode. 1. Parallel I/O mode uses all 8 -bits data bus to connect the I/O device to the MPU (keyboard and display). 2. Serial mode used only one bit in serial I/O control (lecture 4) for interfacing such in cassette tape with MPU. 2

1. 2 I/O Interfacing with 8085 • In I/O parallel mode, the devices can be interfaced using two techniques: peripheral –mapped I/O and memorymapped I/O. Peripheral Mapped I/O: interface I/O devices with 8085 MPU. • I/O connect to “port number” within the 8 -bit address range of 00 H to FFH. • The user access these devices using the IN and OUT instructions only. Memory-Mapped I/O: I/O devices using addresses from memory space ranges from 0000 H –FFFFH. • The exchange of data with I/O devices follows the transfer of data with memory. The user uses the same instructions used for memory. 3

1. 2. 2 Memory-Mapped I/O Example : You might wonder how the communication might work. Suppose you have a printer, and it has some status bits. These bits may reside at some memory address that the CPU "knows" is for the printer. Thus, to get information from the printer, you read a byte or a word from that address. That byte might tell you if the printer is printing, or is out of paper, or out of toner, or what kind of paper is being used, etc. http: //www. cs. umd. edu/class/spring 2003/cmsc 311/Notes/IO/mapped. html 4

1. 3 The interfacing of output devices • Output devices are usually slow. • Also, the output is usually expected to continue on the output device for a long period of time. • On the other hand, the data on the data bus (inside MPU) will only be present for a very short period (microseconds). So, it has to be latched externally (using buffer). PUNJAB EDUSAT SOCIETY (PES) 5

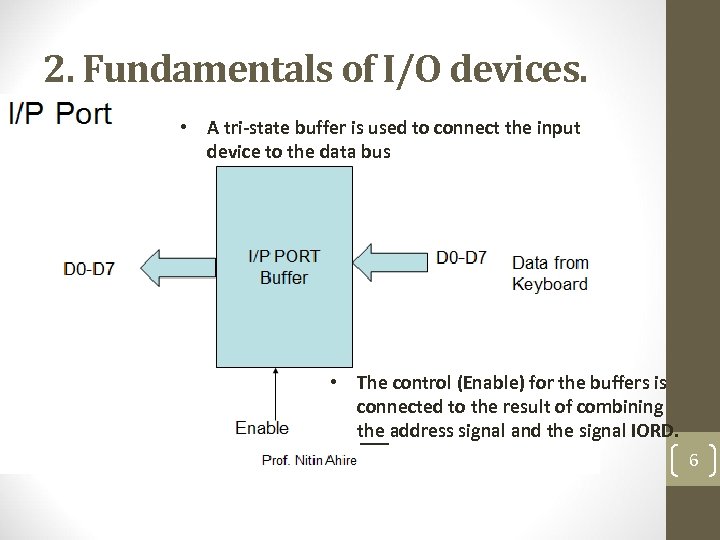

2. Fundamentals of I/O devices. • A tri-state buffer is used to connect the input device to the data bus • The control (Enable) for the buffers is connected to the result of combining the address signal and the signal IORD. 6

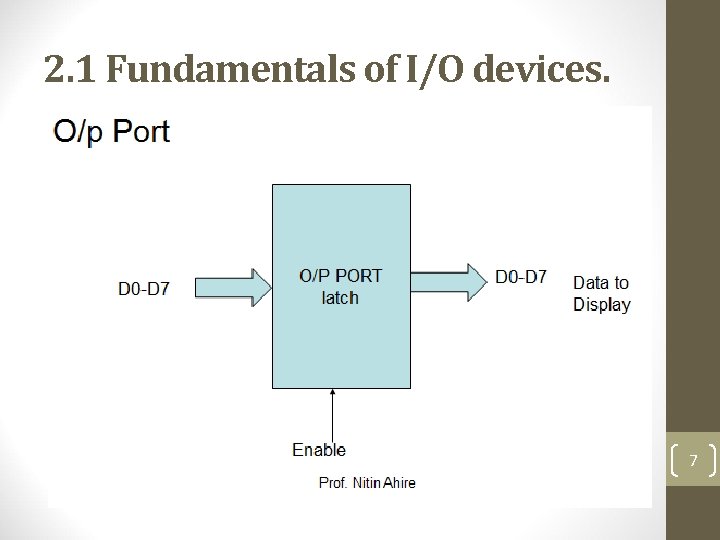

2. 1 Fundamentals of I/O devices. 7

2. 3 I/O Interfacing with 8085 • 8085 MPU separates memory from I/O, via software, ex: instruction like IN and, OUT for I/O interfacing and STA and LDA for memory. • When these instructions decoded by the processor it generates appropriate control signals IO/M. • In 8085 it is possible to connect 256 I/O ports (Can address 28=256 locations) and 64 Kb memory (Can address 216=64 k locations). 8

2. 4 Memory Mapping Vs Peripheral I/O Characteristics Memory-mapped I/O Peripheral Mapped I/O 1. Device address Address is 16 bit ( A 0 A 15) Address is 8 bit (A 0 -A 7) 2. Control signals MEMR and MEWR IOR and IOW 3. Instructions Memory related such as STA and LDA, LDAX , MOV M, R etc. IN and OUT 4. Data transfer Between registers and I/O devices Between accumulator and I/O devices 5. Maximum number of I/O 64 K shared between I/O and system memory. 256 input device and 256 output device. 6. Execution speed 13 T-state (STA, and LDA) 10 T-state 7 T-state (MOV M, R) 7. Hardware requirements More hardware to decode 16. -bit address Less hardware to decode 8 -bit address. 8. Other features Arithmetic or logical operation can be performed with I/O data Not available. 9

End of lecture 8 10

9f391b0c3e41a1bad8f6e7215c930110.ppt