8f15a65d82b6f8196ffd371f328c3871.ppt

- Количество слайдов: 54

CMPE 382 / ECE 510 Computer Organization & Architecture Appendix A- Pipelining

CMPE 382 / ECE 510 Computer Organization & Architecture Appendix A- Pipelining

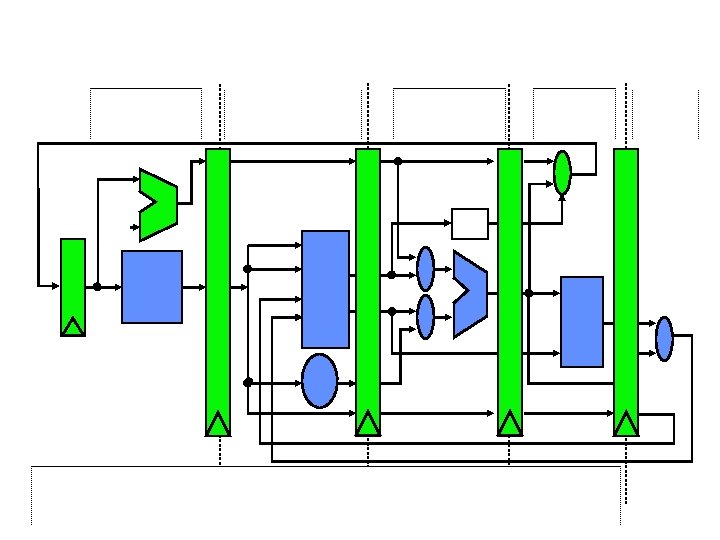

Pipeline Stages

Pipeline Stages

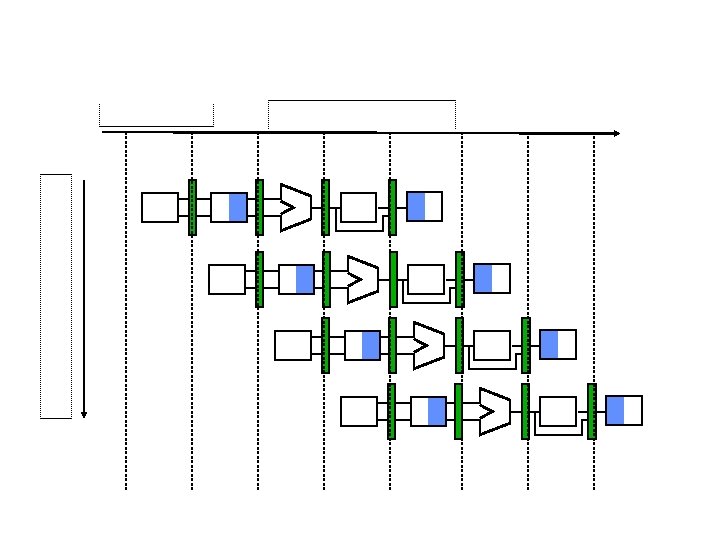

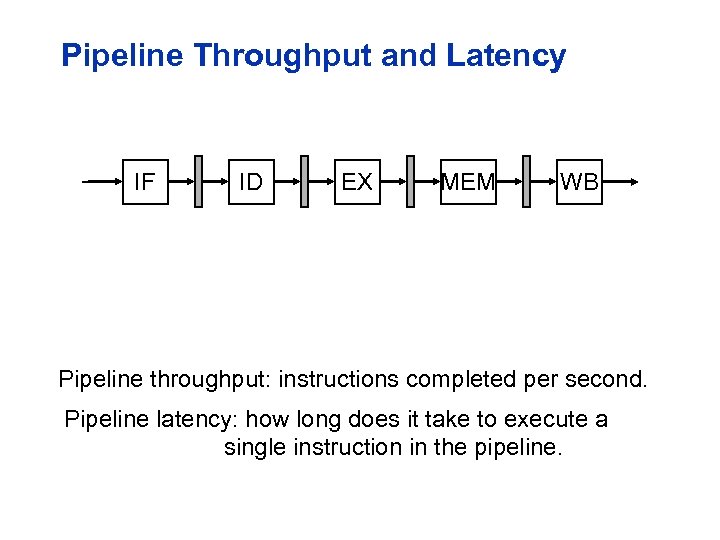

Pipeline Throughput and Latency IF ID EX MEM WB Pipeline throughput: instructions completed per second. Pipeline latency: how long does it take to execute a single instruction in the pipeline.

Pipeline Throughput and Latency IF ID EX MEM WB Pipeline throughput: instructions completed per second. Pipeline latency: how long does it take to execute a single instruction in the pipeline.

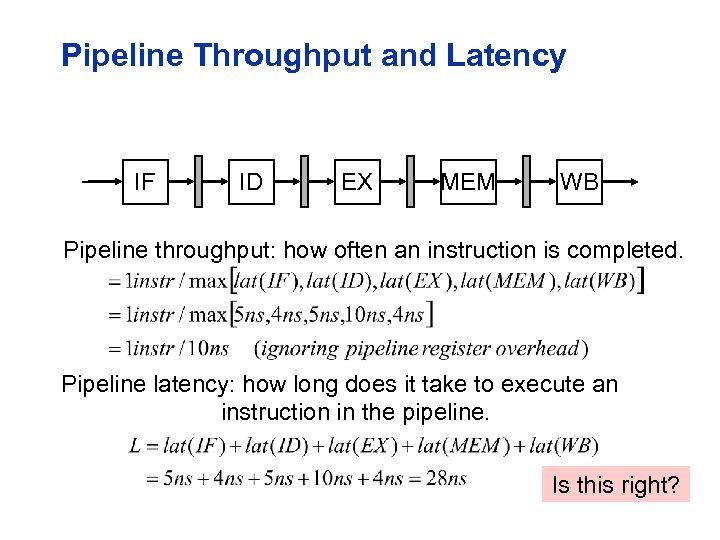

Pipeline Throughput and Latency IF ID EX MEM WB Pipeline throughput: how often an instruction is completed. Pipeline latency: how long does it take to execute an instruction in the pipeline. Is this right?

Pipeline Throughput and Latency IF ID EX MEM WB Pipeline throughput: how often an instruction is completed. Pipeline latency: how long does it take to execute an instruction in the pipeline. Is this right?

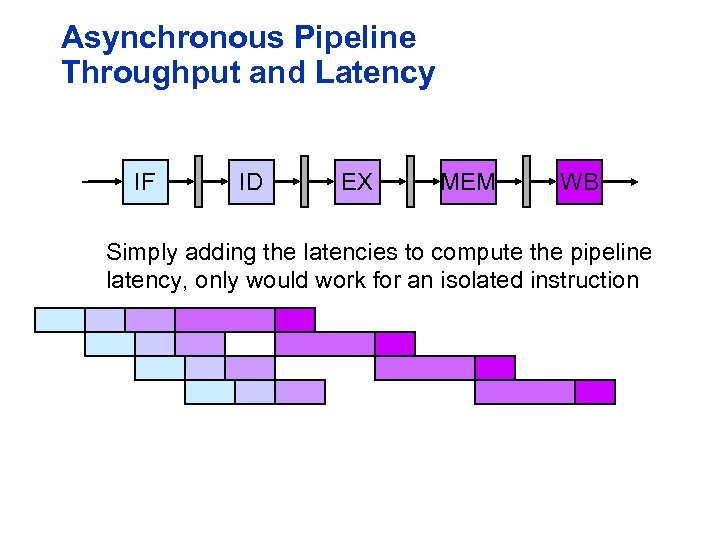

Asynchronous Pipeline Throughput and Latency IF ID EX MEM WB Simply adding the latencies to compute the pipeline latency, only would work for an isolated instruction

Asynchronous Pipeline Throughput and Latency IF ID EX MEM WB Simply adding the latencies to compute the pipeline latency, only would work for an isolated instruction

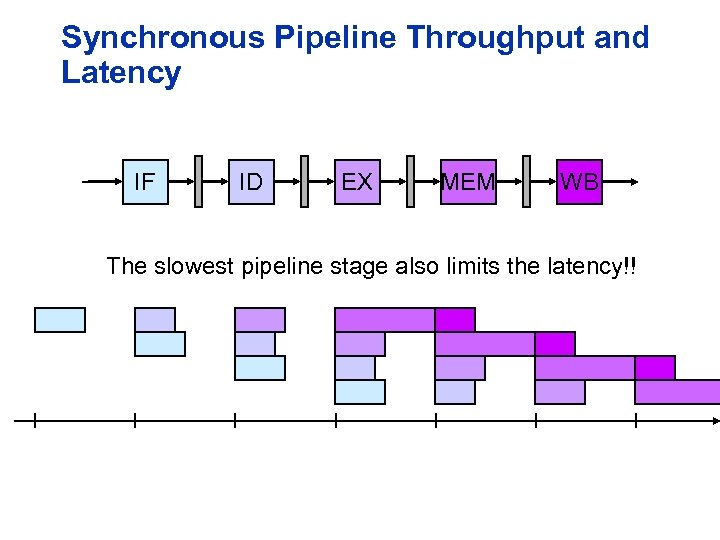

Synchronous Pipeline Throughput and Latency IF ID EX MEM WB The slowest pipeline stage also limits the latency!!

Synchronous Pipeline Throughput and Latency IF ID EX MEM WB The slowest pipeline stage also limits the latency!!

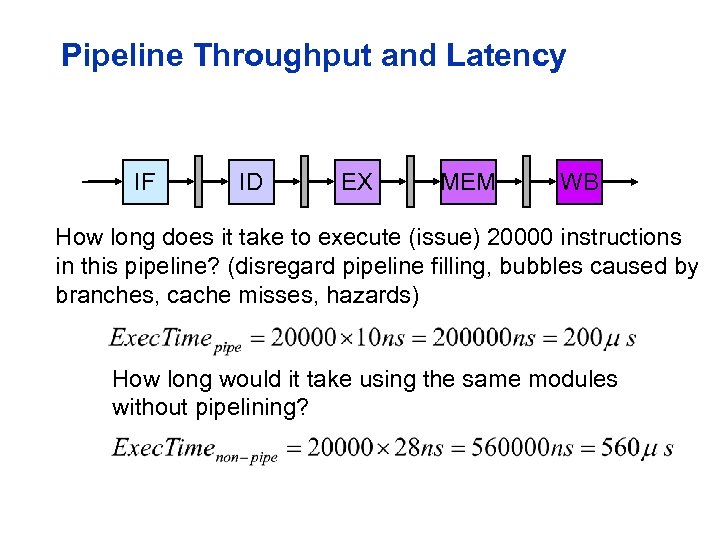

Pipeline Throughput and Latency IF ID EX MEM WB How long does it take to execute (issue) 20000 instructions in this pipeline? (disregard pipeline filling, bubbles caused by branches, cache misses, hazards) How long would it take using the same modules without pipelining?

Pipeline Throughput and Latency IF ID EX MEM WB How long does it take to execute (issue) 20000 instructions in this pipeline? (disregard pipeline filling, bubbles caused by branches, cache misses, hazards) How long would it take using the same modules without pipelining?

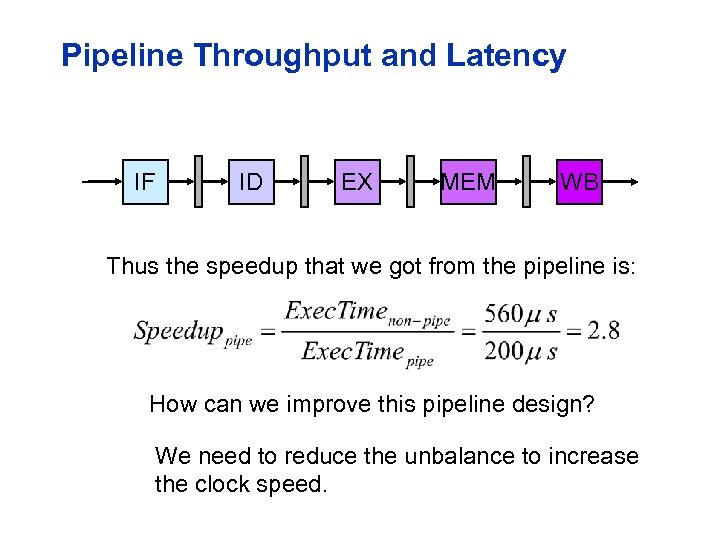

Pipeline Throughput and Latency IF ID EX MEM WB Thus the speedup that we got from the pipeline is: How can we improve this pipeline design? We need to reduce the unbalance to increase the clock speed.

Pipeline Throughput and Latency IF ID EX MEM WB Thus the speedup that we got from the pipeline is: How can we improve this pipeline design? We need to reduce the unbalance to increase the clock speed.

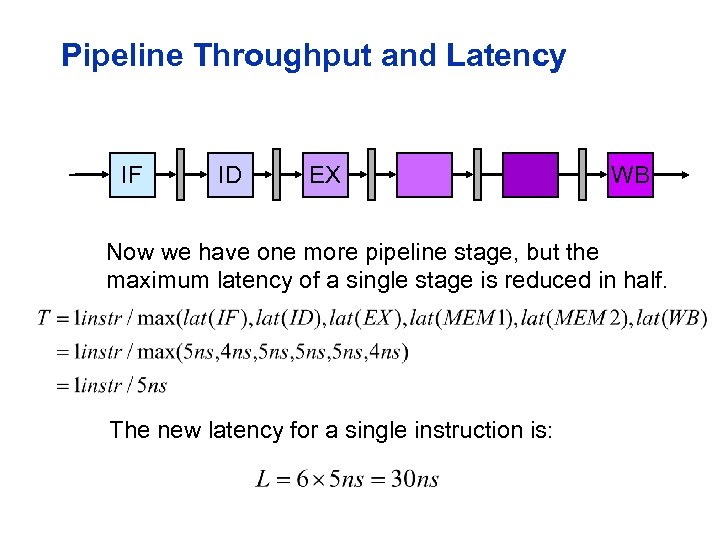

Pipeline Throughput and Latency IF ID EX WB Now we have one more pipeline stage, but the maximum latency of a single stage is reduced in half. The new latency for a single instruction is:

Pipeline Throughput and Latency IF ID EX WB Now we have one more pipeline stage, but the maximum latency of a single stage is reduced in half. The new latency for a single instruction is:

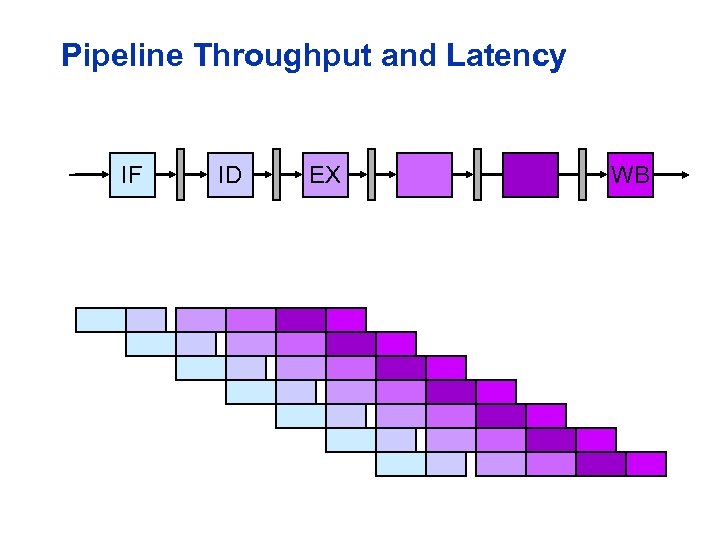

Pipeline Throughput and Latency IF ID EX WB

Pipeline Throughput and Latency IF ID EX WB

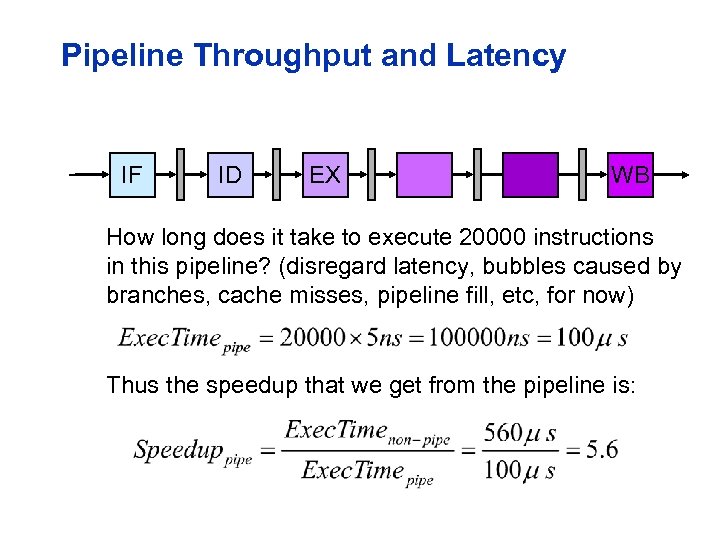

Pipeline Throughput and Latency IF ID EX WB How long does it take to execute 20000 instructions in this pipeline? (disregard latency, bubbles caused by branches, cache misses, pipeline fill, etc, for now) Thus the speedup that we get from the pipeline is:

Pipeline Throughput and Latency IF ID EX WB How long does it take to execute 20000 instructions in this pipeline? (disregard latency, bubbles caused by branches, cache misses, pipeline fill, etc, for now) Thus the speedup that we get from the pipeline is:

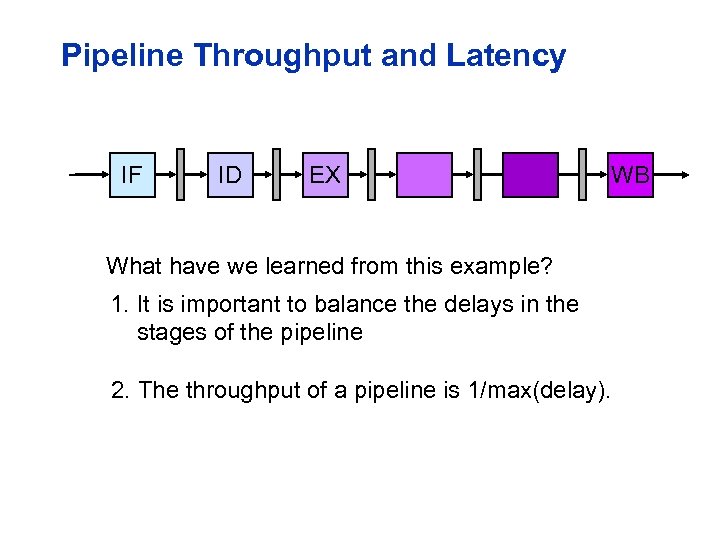

Pipeline Throughput and Latency IF ID EX WB What have we learned from this example? 1. It is important to balance the delays in the stages of the pipeline 2. The throughput of a pipeline is 1/max(delay).

Pipeline Throughput and Latency IF ID EX WB What have we learned from this example? 1. It is important to balance the delays in the stages of the pipeline 2. The throughput of a pipeline is 1/max(delay).

Pipelining is not quite that easy!

Pipelining is not quite that easy!

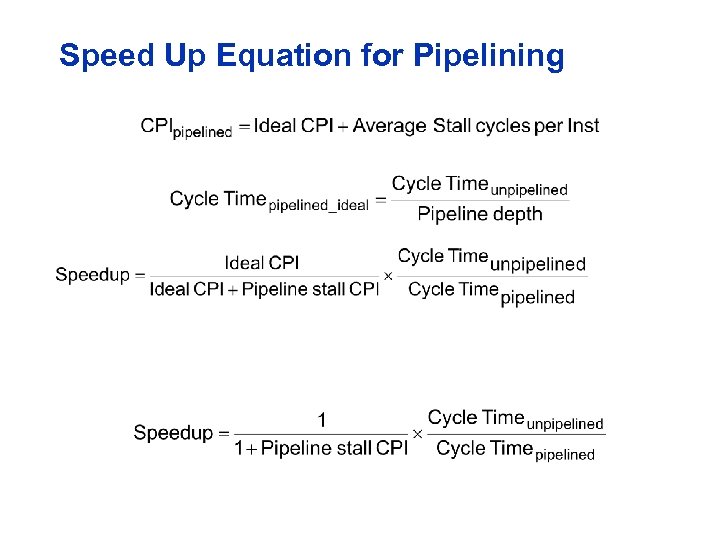

Speed Up Equation for Pipelining

Speed Up Equation for Pipelining

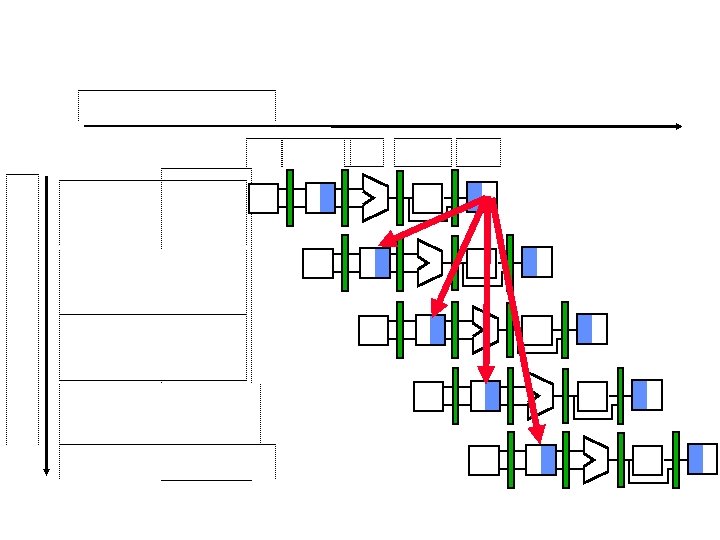

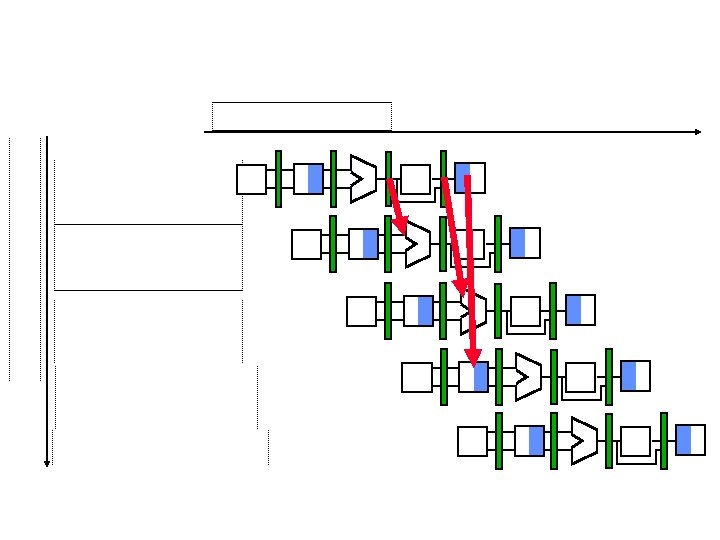

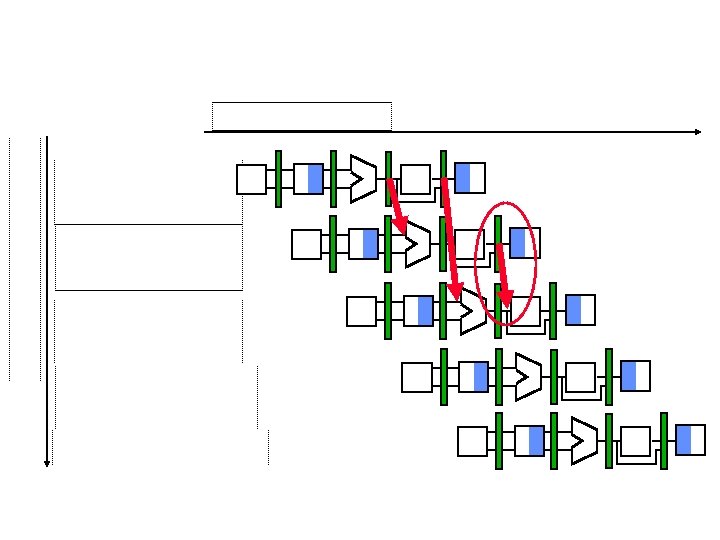

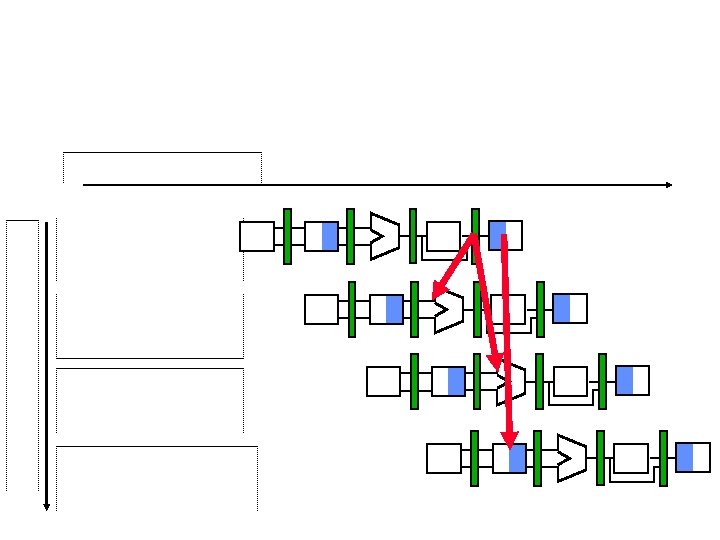

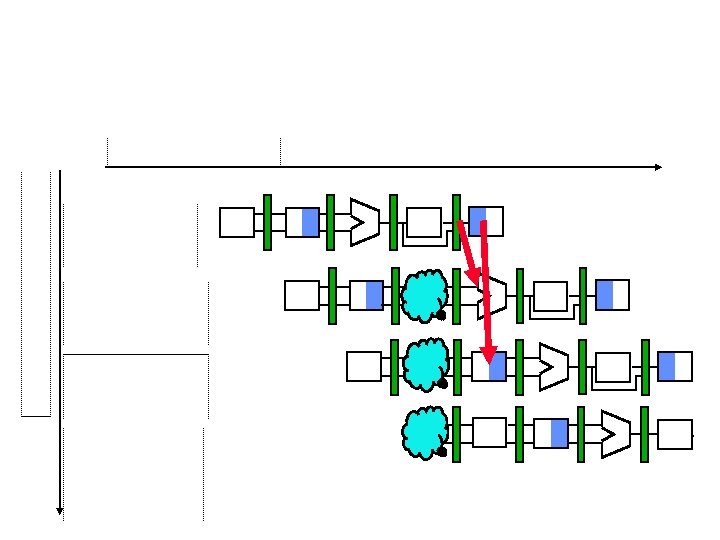

Three Generic Data Hazards

Three Generic Data Hazards

Three Generic Data Hazards

Three Generic Data Hazards

Three Generic Data Hazards

Three Generic Data Hazards

Mental Exercise

Mental Exercise

Software Scheduling to Avoid Load Hazards

Software Scheduling to Avoid Load Hazards

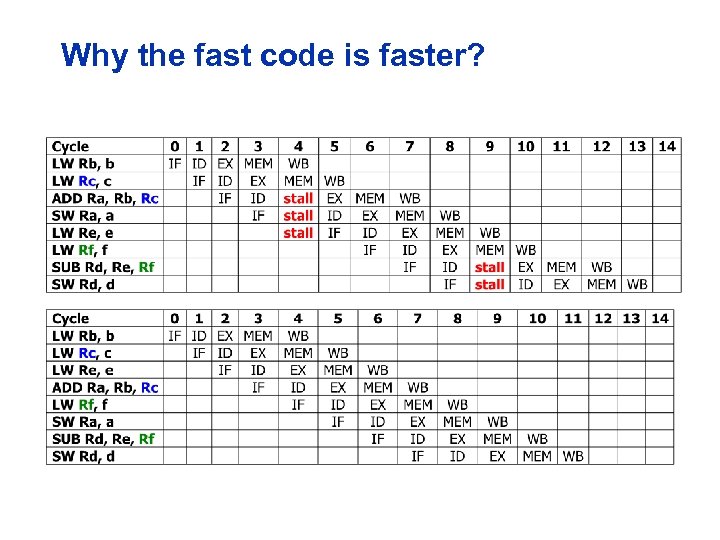

Why the fast code is faster?

Why the fast code is faster?

Mental Exercise – software forwarding

Mental Exercise – software forwarding

Mental Exercise – Problems with software solution

Mental Exercise – Problems with software solution

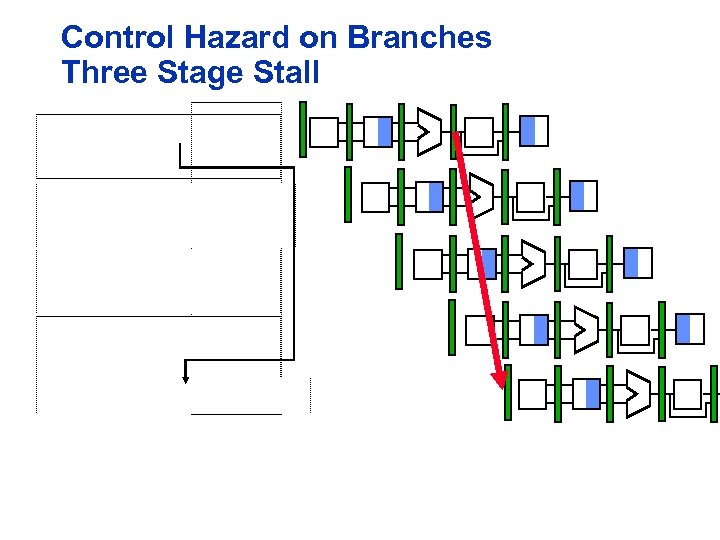

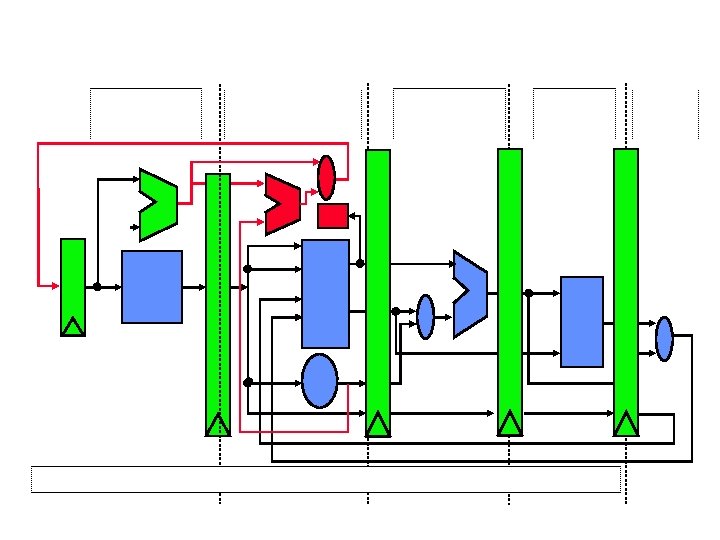

Control Hazard on Branches Three Stage Stall

Control Hazard on Branches Three Stage Stall

Branch Stall Impact

Branch Stall Impact

Four Branch Hazard Alternatives

Four Branch Hazard Alternatives

Four Branch Hazard Alternatives

Four Branch Hazard Alternatives

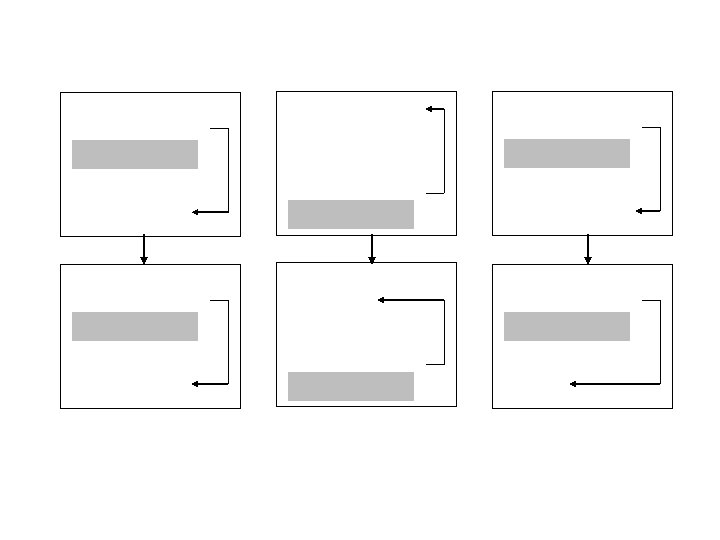

Delayed Branch

Delayed Branch

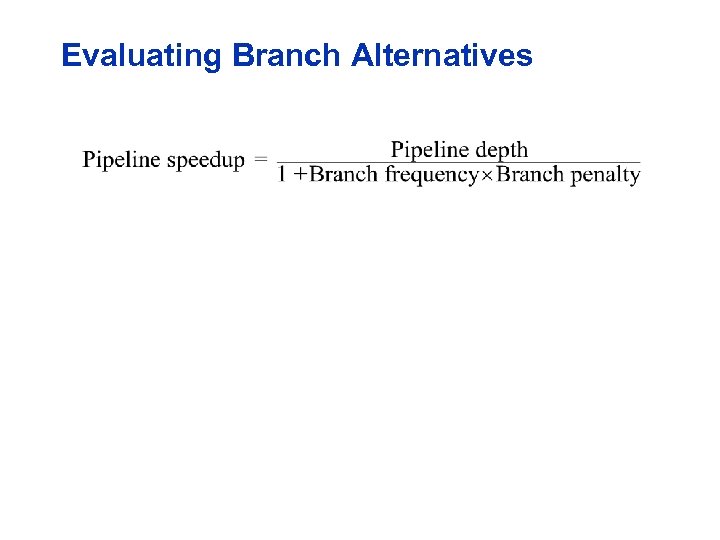

Evaluating Branch Alternatives

Evaluating Branch Alternatives

Static (compiler) branch prediction

Static (compiler) branch prediction

Dynamic Branch Prediction

Dynamic Branch Prediction

Problems with Pipelining

Problems with Pipelining

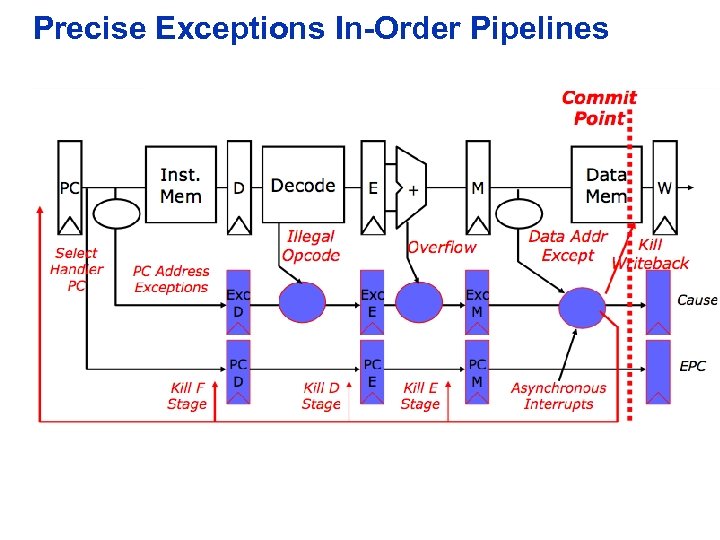

Precise Exceptions In-Order Pipelines

Precise Exceptions In-Order Pipelines

Mismatched Pipeline Lengths

Mismatched Pipeline Lengths

Interrupts and Exceptions

Interrupts and Exceptions

Recovery from Exceptions Within Instructions

Recovery from Exceptions Within Instructions

Recovery from Exceptions Within Instructions

Recovery from Exceptions Within Instructions

Imprecise Exceptions

Imprecise Exceptions

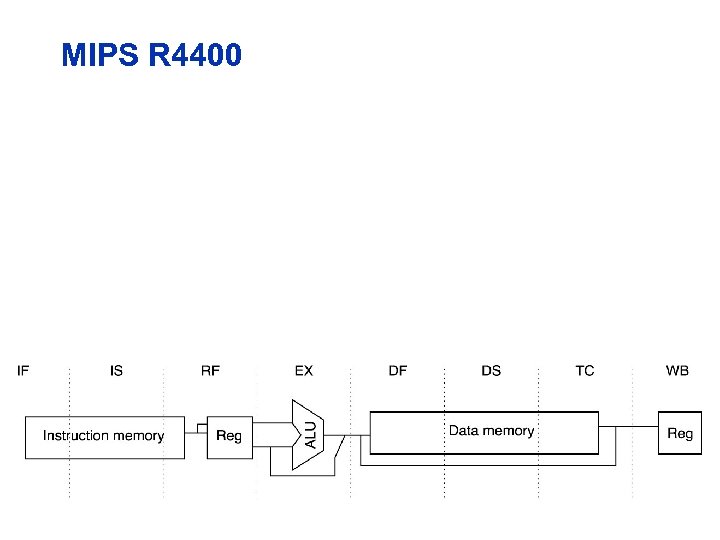

MIPS R 4400

MIPS R 4400

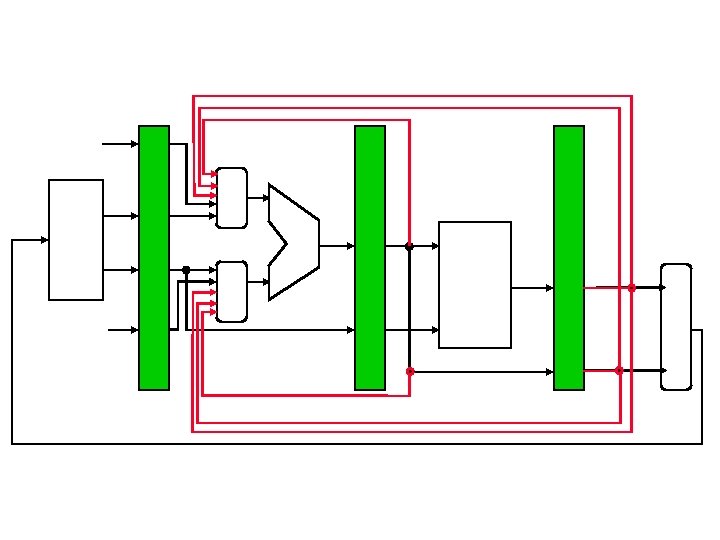

What's needed to oversee correct out-of-order instruction completion?

What's needed to oversee correct out-of-order instruction completion?

Scoreboard for out-of-order execution

Scoreboard for out-of-order execution

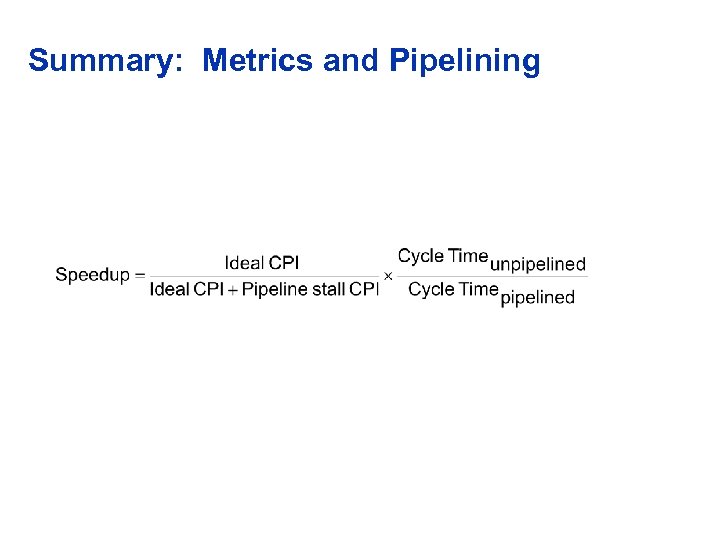

Summary: Metrics and Pipelining

Summary: Metrics and Pipelining