d2e3428f7a24e8334a0fbccc40bf1e0c.ppt

- Количество слайдов: 54

CMOS Analog Design Using All-Region MOSFET Modeling Chapter 8 Operational amplifiers

CMOS Analog Design Using All-Region MOSFET Modeling Chapter 8 Operational amplifiers

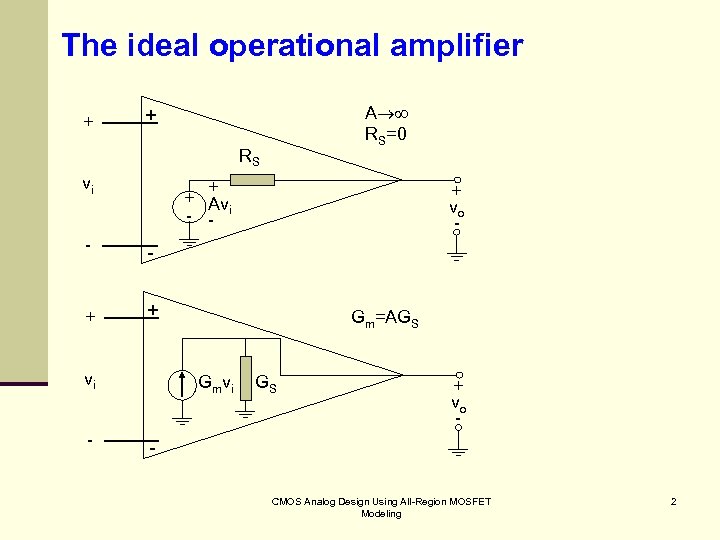

The ideal operational amplifier + A RS=0 + RS vi + + Av - - i - - + + vo - + vi - Gm=AGS Gmvi GS + vo - CMOS Analog Design Using All-Region MOSFET Modeling 2

The ideal operational amplifier + A RS=0 + RS vi + + Av - - i - - + + vo - + vi - Gm=AGS Gmvi GS + vo - CMOS Analog Design Using All-Region MOSFET Modeling 2

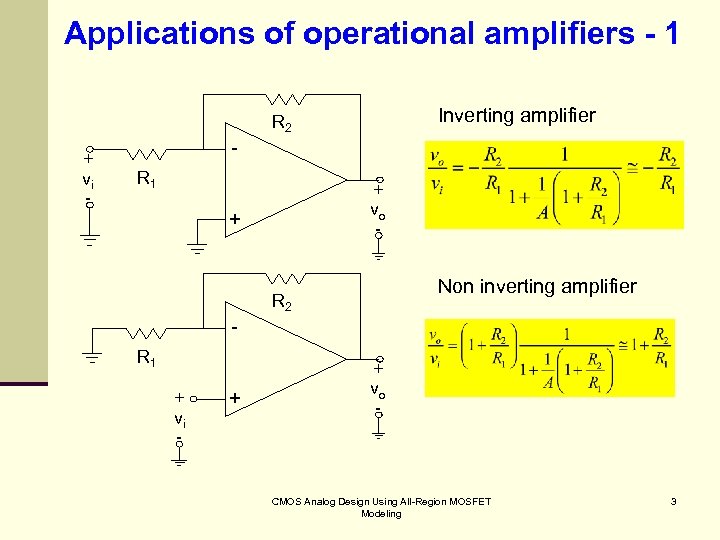

Applications of operational amplifiers - 1 Inverting amplifier R 2 + vi - R 1 + vo - + Non inverting amplifier R 2 R 1 + vi - + + vo - CMOS Analog Design Using All-Region MOSFET Modeling 3

Applications of operational amplifiers - 1 Inverting amplifier R 2 + vi - R 1 + vo - + Non inverting amplifier R 2 R 1 + vi - + + vo - CMOS Analog Design Using All-Region MOSFET Modeling 3

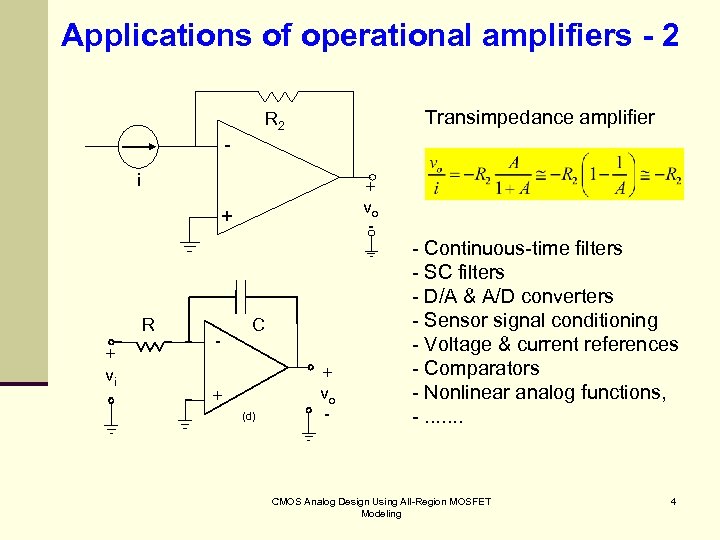

Applications of operational amplifiers - 2 Transimpedance amplifier R 2 i + vo - + R + vi - - C + (d) + vo - - Continuous-time filters - SC filters - D/A & A/D converters - Sensor signal conditioning - Voltage & current references - Comparators - Nonlinear analog functions, -. . . . CMOS Analog Design Using All-Region MOSFET Modeling 4

Applications of operational amplifiers - 2 Transimpedance amplifier R 2 i + vo - + R + vi - - C + (d) + vo - - Continuous-time filters - SC filters - D/A & A/D converters - Sensor signal conditioning - Voltage & current references - Comparators - Nonlinear analog functions, -. . . . CMOS Analog Design Using All-Region MOSFET Modeling 4

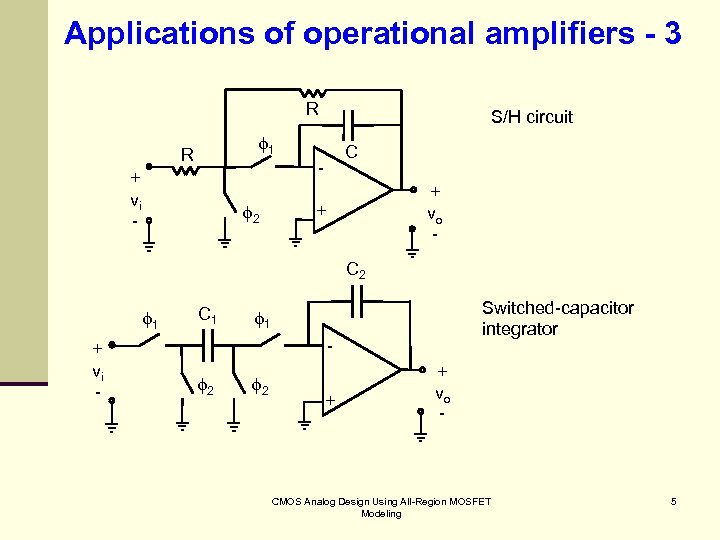

Applications of operational amplifiers - 3 R S/H circuit 1 R C - + vi - 2 + vo - + C 2 1 + vi - C 1 Switched-capacitor integrator 1 - 2 2 + + vo - CMOS Analog Design Using All-Region MOSFET Modeling 5

Applications of operational amplifiers - 3 R S/H circuit 1 R C - + vi - 2 + vo - + C 2 1 + vi - C 1 Switched-capacitor integrator 1 - 2 2 + + vo - CMOS Analog Design Using All-Region MOSFET Modeling 5

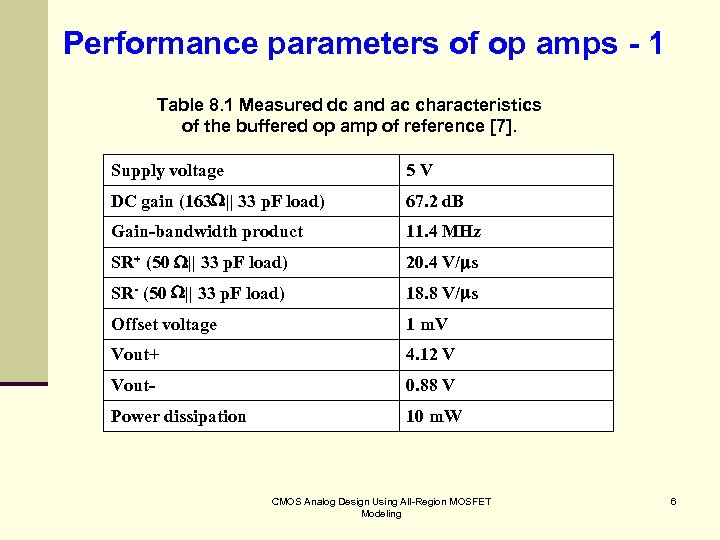

Performance parameters of op amps - 1 Table 8. 1 Measured dc and ac characteristics of the buffered op amp of reference [7]. Supply voltage 5 V DC gain (163 || 33 p. F load) 67. 2 d. B Gain-bandwidth product 11. 4 MHz SR+ (50 || 33 p. F load) 20. 4 V/ s SR- (50 || 33 p. F load) 18. 8 V/ s Offset voltage 1 m. V Vout+ 4. 12 V Vout- 0. 88 V Power dissipation 10 m. W CMOS Analog Design Using All-Region MOSFET Modeling 6

Performance parameters of op amps - 1 Table 8. 1 Measured dc and ac characteristics of the buffered op amp of reference [7]. Supply voltage 5 V DC gain (163 || 33 p. F load) 67. 2 d. B Gain-bandwidth product 11. 4 MHz SR+ (50 || 33 p. F load) 20. 4 V/ s SR- (50 || 33 p. F load) 18. 8 V/ s Offset voltage 1 m. V Vout+ 4. 12 V Vout- 0. 88 V Power dissipation 10 m. W CMOS Analog Design Using All-Region MOSFET Modeling 6

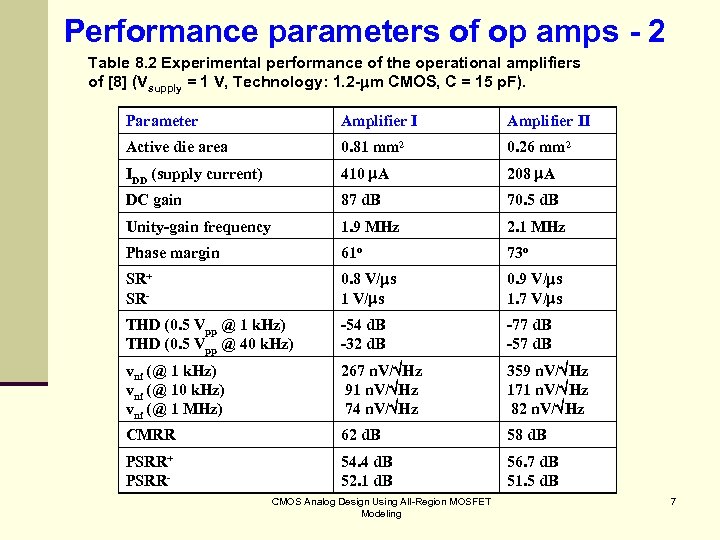

Performance parameters of op amps - 2 Table 8. 2 Experimental performance of the operational amplifiers of [8] (Vsupply = 1 V, Technology: 1. 2 - m CMOS, C = 15 p. F). Parameter Amplifier II Active die area 0. 81 mm 2 0. 26 mm 2 IDD (supply current) 410 A 208 A DC gain 87 d. B 70. 5 d. B Unity-gain frequency 1. 9 MHz 2. 1 MHz Phase margin 61 o 73 o SR+ SR- 0. 8 V/ s 1 V/ s 0. 9 V/ s 1. 7 V/ s THD (0. 5 Vpp @ 1 k. Hz) THD (0. 5 Vpp @ 40 k. Hz) -54 d. B -32 d. B -77 d. B -57 d. B vni (@ 1 k. Hz) vni (@ 10 k. Hz) vni (@ 1 MHz) 267 n. V/ Hz 91 n. V/ Hz 74 n. V/ Hz 359 n. V/ Hz 171 n. V/ Hz 82 n. V/ Hz CMRR 62 d. B 58 d. B PSRR+ PSRR- 54. 4 d. B 52. 1 d. B 56. 7 d. B 51. 5 d. B CMOS Analog Design Using All-Region MOSFET Modeling 7

Performance parameters of op amps - 2 Table 8. 2 Experimental performance of the operational amplifiers of [8] (Vsupply = 1 V, Technology: 1. 2 - m CMOS, C = 15 p. F). Parameter Amplifier II Active die area 0. 81 mm 2 0. 26 mm 2 IDD (supply current) 410 A 208 A DC gain 87 d. B 70. 5 d. B Unity-gain frequency 1. 9 MHz 2. 1 MHz Phase margin 61 o 73 o SR+ SR- 0. 8 V/ s 1 V/ s 0. 9 V/ s 1. 7 V/ s THD (0. 5 Vpp @ 1 k. Hz) THD (0. 5 Vpp @ 40 k. Hz) -54 d. B -32 d. B -77 d. B -57 d. B vni (@ 1 k. Hz) vni (@ 10 k. Hz) vni (@ 1 MHz) 267 n. V/ Hz 91 n. V/ Hz 74 n. V/ Hz 359 n. V/ Hz 171 n. V/ Hz 82 n. V/ Hz CMRR 62 d. B 58 d. B PSRR+ PSRR- 54. 4 d. B 52. 1 d. B 56. 7 d. B 51. 5 d. B CMOS Analog Design Using All-Region MOSFET Modeling 7

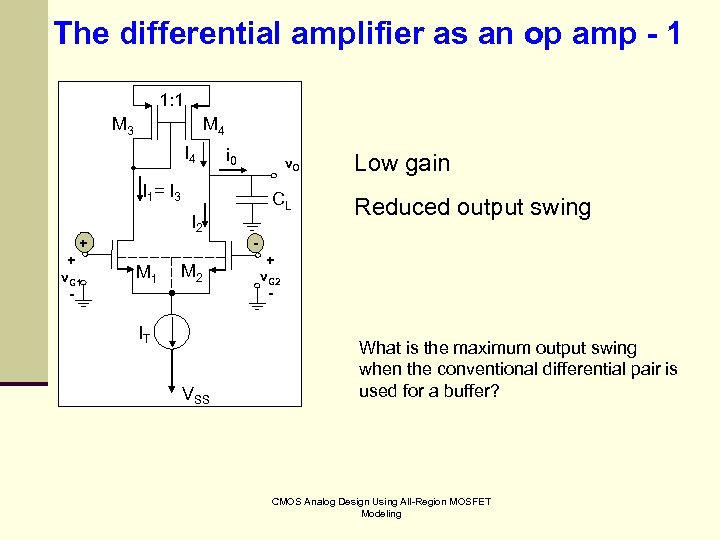

The differential amplifier as an op amp - 1 1: 1 M 3 M 4 I 4 i 0 v. O I 1 = I 3 CL I 2 + + v. G 1 - Low gain Reduced output swing - M 1 M 2 IT VSS + v. G 2 - What is the maximum output swing when the conventional differential pair is used for a buffer? CMOS Analog Design Using All-Region MOSFET Modeling

The differential amplifier as an op amp - 1 1: 1 M 3 M 4 I 4 i 0 v. O I 1 = I 3 CL I 2 + + v. G 1 - Low gain Reduced output swing - M 1 M 2 IT VSS + v. G 2 - What is the maximum output swing when the conventional differential pair is used for a buffer? CMOS Analog Design Using All-Region MOSFET Modeling

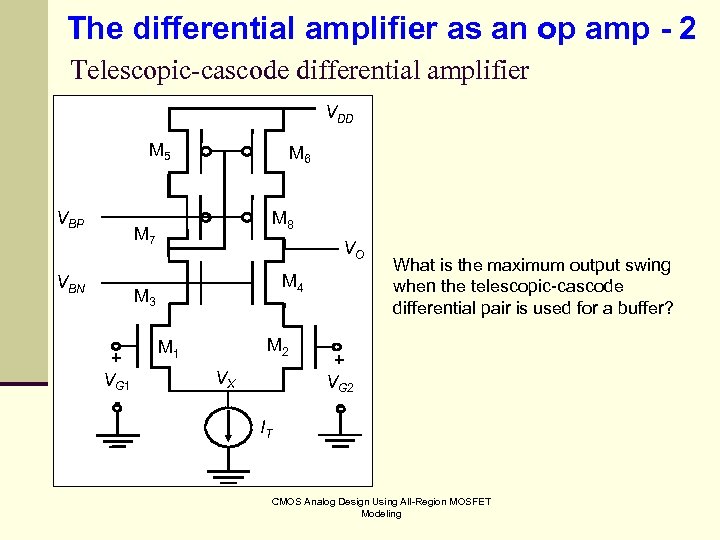

The differential amplifier as an op amp - 2 Telescopic-cascode differential amplifier VDD M 5 VBP M 6 M 8 M 7 VBN VO M 4 M 3 + VG 1 - M 2 M 1 VX What is the maximum output swing when the telescopic-cascode differential pair is used for a buffer? + VG 2 - IT CMOS Analog Design Using All-Region MOSFET Modeling

The differential amplifier as an op amp - 2 Telescopic-cascode differential amplifier VDD M 5 VBP M 6 M 8 M 7 VBN VO M 4 M 3 + VG 1 - M 2 M 1 VX What is the maximum output swing when the telescopic-cascode differential pair is used for a buffer? + VG 2 - IT CMOS Analog Design Using All-Region MOSFET Modeling

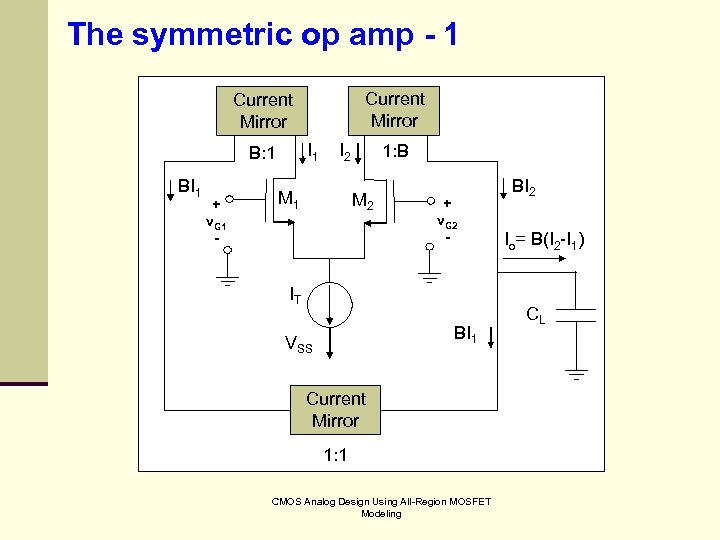

The symmetric op amp - 1 Current Mirror I 1 B: 1 BI 1 + v. G 1 - I 2 M 1 1: B M 2 + v. G 2 - IT BI 1 VSS Current Mirror 1: 1 CMOS Analog Design Using All-Region MOSFET Modeling BI 2 Io= B(I 2 -I 1) CL

The symmetric op amp - 1 Current Mirror I 1 B: 1 BI 1 + v. G 1 - I 2 M 1 1: B M 2 + v. G 2 - IT BI 1 VSS Current Mirror 1: 1 CMOS Analog Design Using All-Region MOSFET Modeling BI 2 Io= B(I 2 -I 1) CL

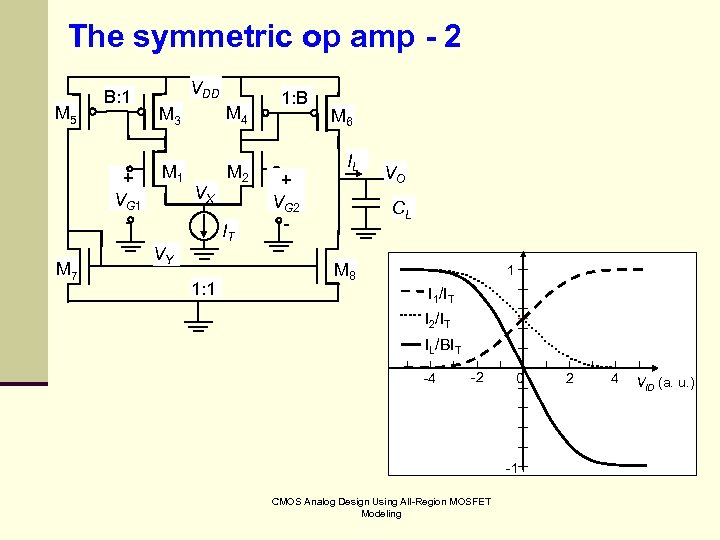

The symmetric op amp - 2 M 5 B: 1 + VG 1 M 7 VDD M 3 M 4 M 1 M 2 VX IT VY 1: 1 1: B + VG 2 - M 6 IL VO CL M 8 1 I 1/IT I 2/IT IL/BIT -4 -2 0 -1 CMOS Analog Design Using All-Region MOSFET Modeling 2 4 VID (a. u. )

The symmetric op amp - 2 M 5 B: 1 + VG 1 M 7 VDD M 3 M 4 M 1 M 2 VX IT VY 1: 1 1: B + VG 2 - M 6 IL VO CL M 8 1 I 1/IT I 2/IT IL/BIT -4 -2 0 -1 CMOS Analog Design Using All-Region MOSFET Modeling 2 4 VID (a. u. )

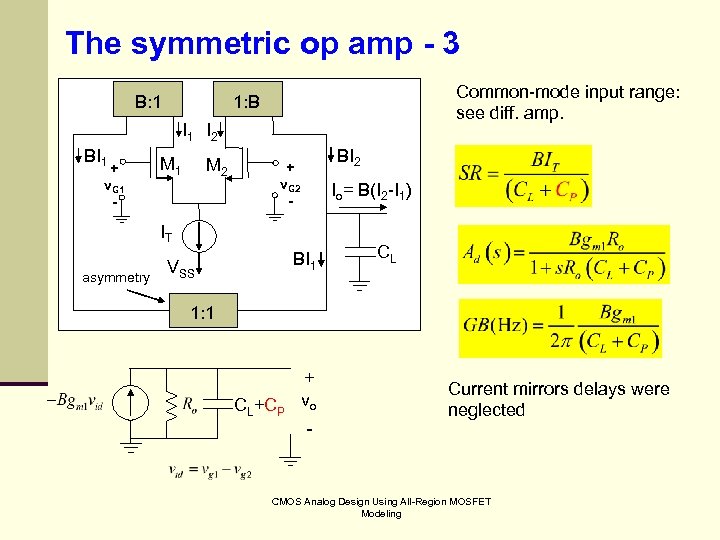

The symmetric op amp - 3 B: 1 Common-mode input range: see diff. amp. 1: B I 1 I 2 BI 1 + v. G 1 - M 1 M 2 BI 2 + v. G 2 - Io= B(I 2 -I 1) IT asymmetry BI 1 VSS CL 1: 1 CL+CP + vo - Current mirrors delays were neglected CMOS Analog Design Using All-Region MOSFET Modeling

The symmetric op amp - 3 B: 1 Common-mode input range: see diff. amp. 1: B I 1 I 2 BI 1 + v. G 1 - M 1 M 2 BI 2 + v. G 2 - Io= B(I 2 -I 1) IT asymmetry BI 1 VSS CL 1: 1 CL+CP + vo - Current mirrors delays were neglected CMOS Analog Design Using All-Region MOSFET Modeling

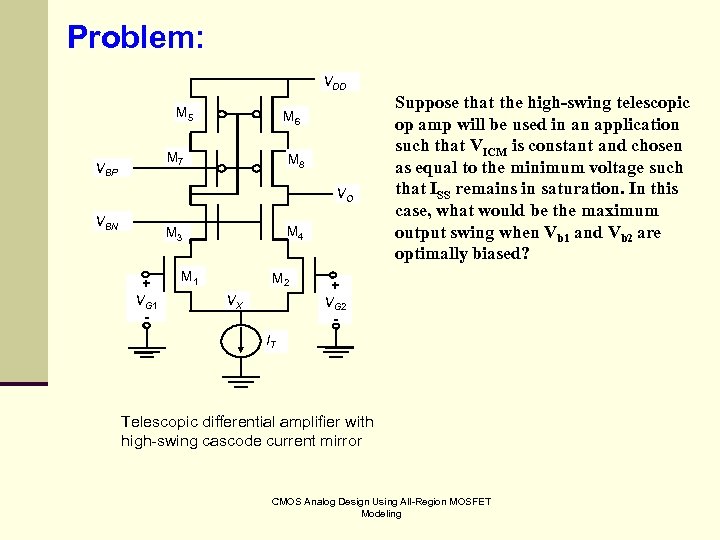

Problem: VDD M 5 M 6 M 7 VBP M 8 VO VBN M 4 M 3 + VG 1 - M 1 M 2 VX Suppose that the high-swing telescopic op amp will be used in an application such that VICM is constant and chosen as equal to the minimum voltage such that ISS remains in saturation. In this case, what would be the maximum output swing when Vb 1 and Vb 2 are optimally biased? + VG 2 - IT Telescopic differential amplifier with high-swing cascode current mirror CMOS Analog Design Using All-Region MOSFET Modeling

Problem: VDD M 5 M 6 M 7 VBP M 8 VO VBN M 4 M 3 + VG 1 - M 1 M 2 VX Suppose that the high-swing telescopic op amp will be used in an application such that VICM is constant and chosen as equal to the minimum voltage such that ISS remains in saturation. In this case, what would be the maximum output swing when Vb 1 and Vb 2 are optimally biased? + VG 2 - IT Telescopic differential amplifier with high-swing cascode current mirror CMOS Analog Design Using All-Region MOSFET Modeling

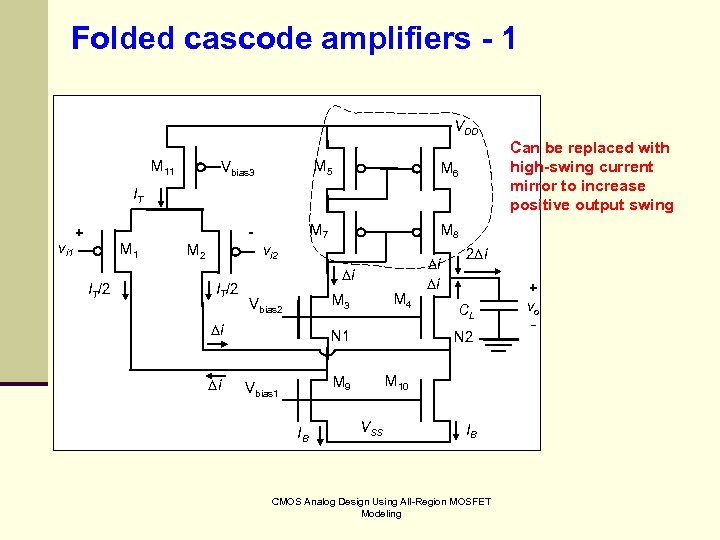

Folded cascode amplifiers - 1 VDD M 11 Vbias 3 M 5 M 6 - M 7 Can be replaced with high-swing current mirror to increase positive output swing M 8 IT vi 1 + M 1 IT/2 vi 2 M 2 IT/2 i Vbias 2 i i M 4 M 3 N 1 IB 2 i CL N 2 M 10 M 9 Vbias 1 i i VSS IB CMOS Analog Design Using All-Region MOSFET Modeling + vo -

Folded cascode amplifiers - 1 VDD M 11 Vbias 3 M 5 M 6 - M 7 Can be replaced with high-swing current mirror to increase positive output swing M 8 IT vi 1 + M 1 IT/2 vi 2 M 2 IT/2 i Vbias 2 i i M 4 M 3 N 1 IB 2 i CL N 2 M 10 M 9 Vbias 1 i i VSS IB CMOS Analog Design Using All-Region MOSFET Modeling + vo -

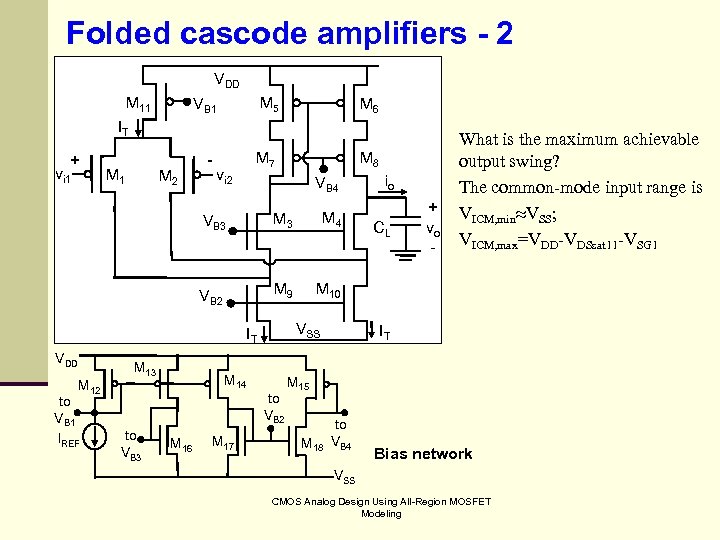

Folded cascode amplifiers - 2 VDD M 11 M 5 VB 1 M 6 IT + vi 1 M 2 - vi 2 M 7 M 8 VB 4 VB 3 M 4 VB 2 M 9 M 12 to VB 1 IREF M 13 to VB 3 M 14 M 16 + vo - M 10 VSS IT VDD io What is the maximum achievable output swing? The common-mode input range is VICM, min VSS; VICM, max=VDD-VDSsat 11 -VSG 1 M 17 to VB 2 CL IT M 15 M 18 to VB 4 Bias network VSS CMOS Analog Design Using All-Region MOSFET Modeling

Folded cascode amplifiers - 2 VDD M 11 M 5 VB 1 M 6 IT + vi 1 M 2 - vi 2 M 7 M 8 VB 4 VB 3 M 4 VB 2 M 9 M 12 to VB 1 IREF M 13 to VB 3 M 14 M 16 + vo - M 10 VSS IT VDD io What is the maximum achievable output swing? The common-mode input range is VICM, min VSS; VICM, max=VDD-VDSsat 11 -VSG 1 M 17 to VB 2 CL IT M 15 M 18 to VB 4 Bias network VSS CMOS Analog Design Using All-Region MOSFET Modeling

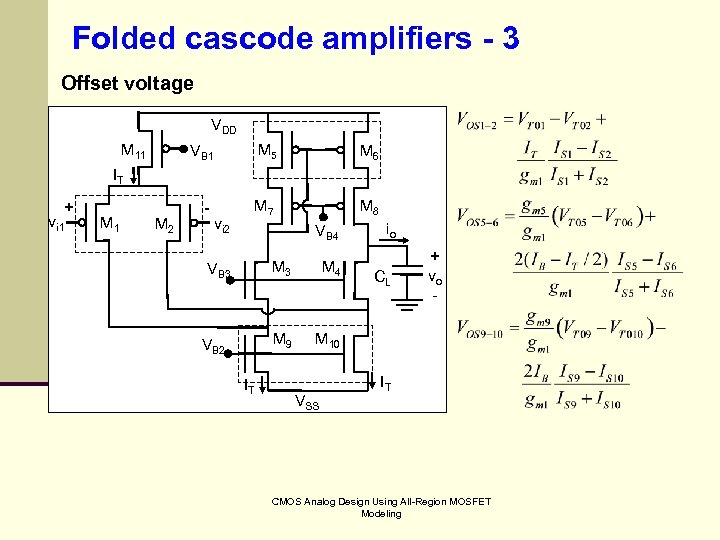

Folded cascode amplifiers - 3 Offset voltage VDD M 11 VB 1 M 5 M 6 - M 7 M 8 IT + vi 1 M 2 vi 2 VB 4 M 3 VB 2 IT M 4 M 9 VB 3 io + vo - M 10 VSS CL IT CMOS Analog Design Using All-Region MOSFET Modeling

Folded cascode amplifiers - 3 Offset voltage VDD M 11 VB 1 M 5 M 6 - M 7 M 8 IT + vi 1 M 2 vi 2 VB 4 M 3 VB 2 IT M 4 M 9 VB 3 io + vo - M 10 VSS CL IT CMOS Analog Design Using All-Region MOSFET Modeling

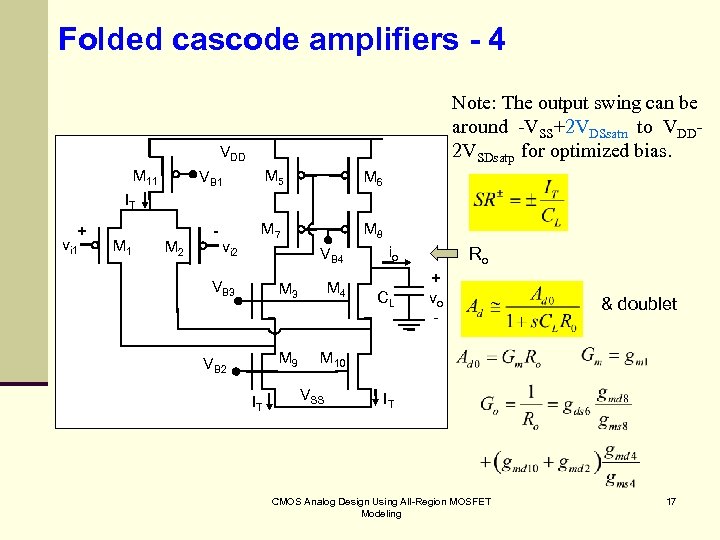

Folded cascode amplifiers - 4 Note: The output swing can be around -VSS+2 VDSsatn to VDD 2 VSDsatp for optimized bias. VDD M 11 VB 1 M 5 M 6 - M 7 M 8 IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io Ro + vo - M 10 VSS CL & doublet IT CMOS Analog Design Using All-Region MOSFET Modeling 17

Folded cascode amplifiers - 4 Note: The output swing can be around -VSS+2 VDSsatn to VDD 2 VSDsatp for optimized bias. VDD M 11 VB 1 M 5 M 6 - M 7 M 8 IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io Ro + vo - M 10 VSS CL & doublet IT CMOS Analog Design Using All-Region MOSFET Modeling 17

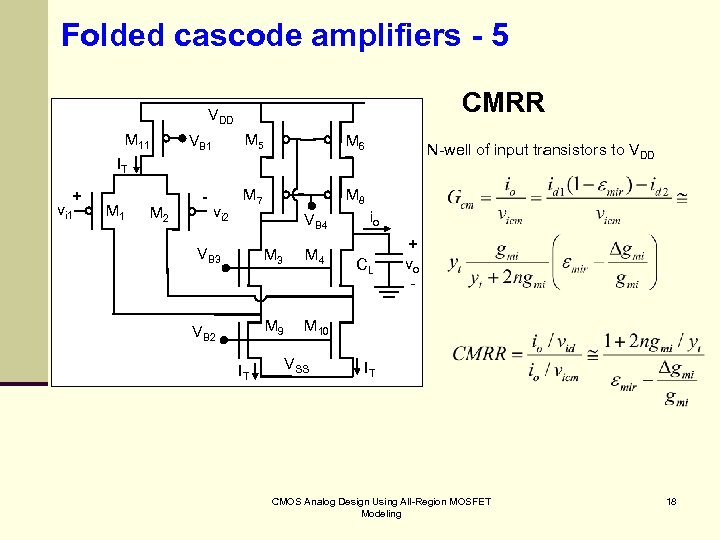

Folded cascode amplifiers - 5 CMRR VDD M 11 VB 1 M 5 M 6 - M 7 M 8 N-well of input transistors to VDD IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io + vo - M 10 VSS CL IT CMOS Analog Design Using All-Region MOSFET Modeling 18

Folded cascode amplifiers - 5 CMRR VDD M 11 VB 1 M 5 M 6 - M 7 M 8 N-well of input transistors to VDD IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io + vo - M 10 VSS CL IT CMOS Analog Design Using All-Region MOSFET Modeling 18

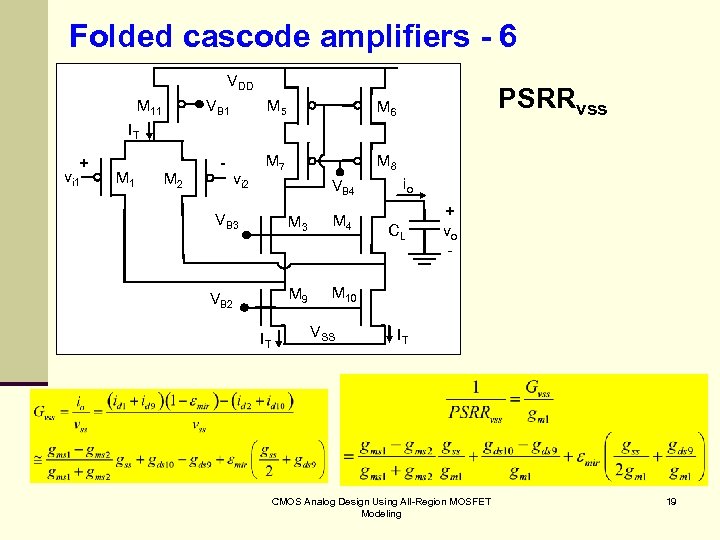

Folded cascode amplifiers - 6 VDD M 11 VB 1 M 5 - M 7 PSRRvss M 6 M 8 IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io + vo - M 10 VSS CL IT CMOS Analog Design Using All-Region MOSFET Modeling 19

Folded cascode amplifiers - 6 VDD M 11 VB 1 M 5 - M 7 PSRRvss M 6 M 8 IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io + vo - M 10 VSS CL IT CMOS Analog Design Using All-Region MOSFET Modeling 19

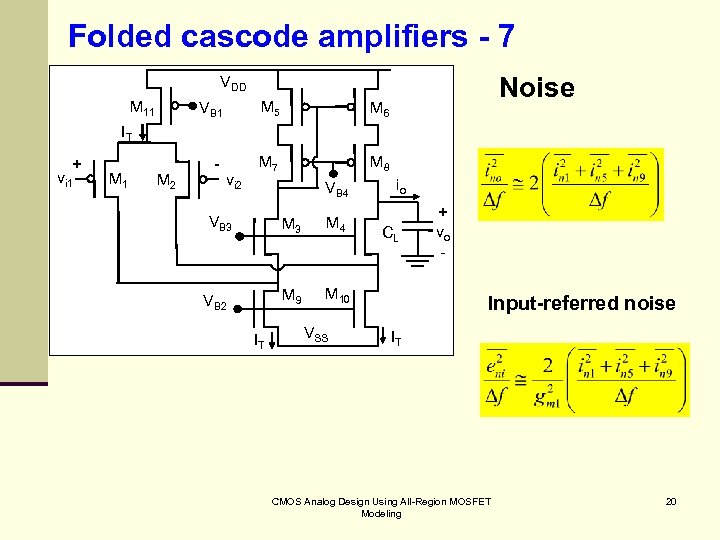

Folded cascode amplifiers - 7 Noise VDD M 11 VB 1 M 5 M 6 - M 7 M 8 IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io M 10 VSS CL + vo - Input-referred noise IT CMOS Analog Design Using All-Region MOSFET Modeling 20

Folded cascode amplifiers - 7 Noise VDD M 11 VB 1 M 5 M 6 - M 7 M 8 IT + vi 1 M 2 vi 2 VB 4 VB 3 M 9 VB 2 IT M 4 io M 10 VSS CL + vo - Input-referred noise IT CMOS Analog Design Using All-Region MOSFET Modeling 20

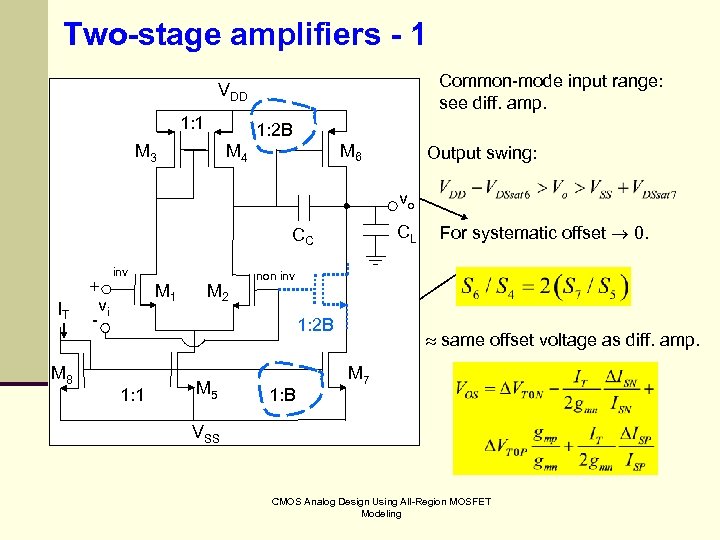

Two-stage amplifiers - 1 Common-mode input range: see diff. amp. VDD 1: 1 1: 2 B M 3 M 6 M 4 Output swing: vo CL CC IT M 8 + vi - inv M 1 M 2 non inv 1: 2 B 1: 1 M 5 For systematic offset 0. 1: B same offset voltage as diff. amp. M 7 VSS CMOS Analog Design Using All-Region MOSFET Modeling

Two-stage amplifiers - 1 Common-mode input range: see diff. amp. VDD 1: 1 1: 2 B M 3 M 6 M 4 Output swing: vo CL CC IT M 8 + vi - inv M 1 M 2 non inv 1: 2 B 1: 1 M 5 For systematic offset 0. 1: B same offset voltage as diff. amp. M 7 VSS CMOS Analog Design Using All-Region MOSFET Modeling

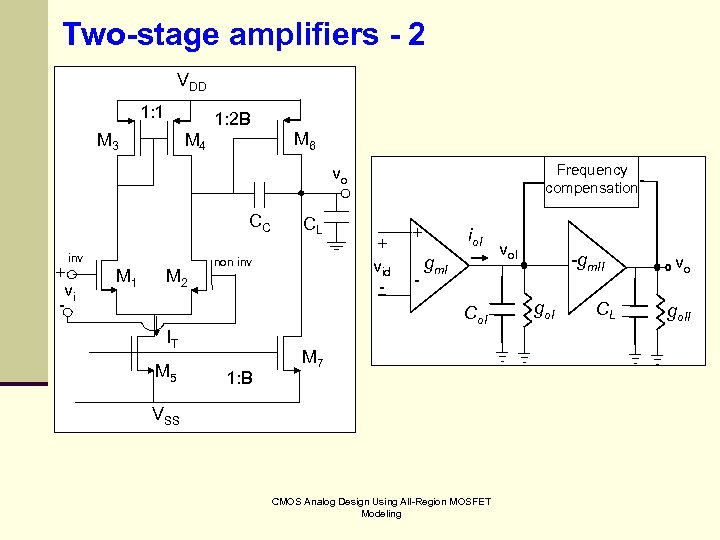

Two-stage amplifiers - 2 VDD 1: 1 1: 2 B M 3 M 6 M 4 Frequency compensation vo CC inv + vi - M 1 M 2 CL non inv + vid - + - io. I gm. I Co. I IT M 5 1: B M 7 VSS CMOS Analog Design Using All-Region MOSFET Modeling vo. I -gm. II go. I CL vo go. II

Two-stage amplifiers - 2 VDD 1: 1 1: 2 B M 3 M 6 M 4 Frequency compensation vo CC inv + vi - M 1 M 2 CL non inv + vid - + - io. I gm. I Co. I IT M 5 1: B M 7 VSS CMOS Analog Design Using All-Region MOSFET Modeling vo. I -gm. II go. I CL vo go. II

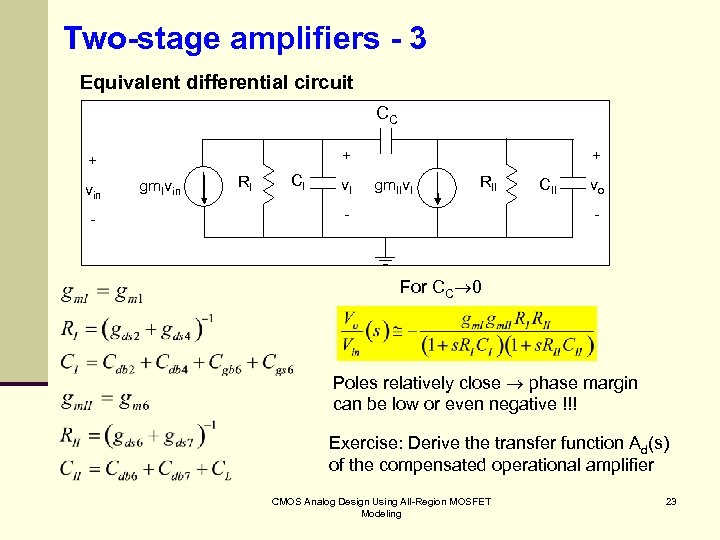

Two-stage amplifiers - 3 Equivalent differential circuit CC + + vin - gm. Ivin RI CI v. I + gm. IIv. I RII - CII vo - For CC 0 Poles relatively close phase margin can be low or even negative !!! Exercise: Derive the transfer function Ad(s) of the compensated operational amplifier CMOS Analog Design Using All-Region MOSFET Modeling 23

Two-stage amplifiers - 3 Equivalent differential circuit CC + + vin - gm. Ivin RI CI v. I + gm. IIv. I RII - CII vo - For CC 0 Poles relatively close phase margin can be low or even negative !!! Exercise: Derive the transfer function Ad(s) of the compensated operational amplifier CMOS Analog Design Using All-Region MOSFET Modeling 23

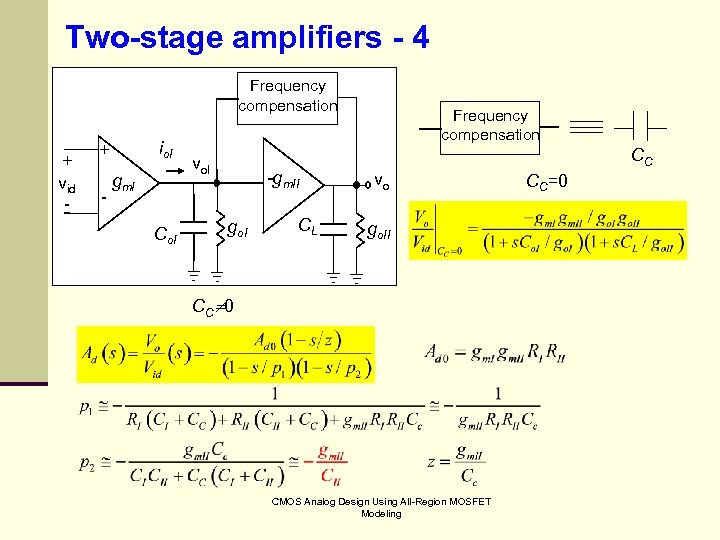

Two-stage amplifiers - 4 Frequency compensation + vid - io. I + - gm. I Co. I vo. I -gm. II go. I CL Frequency compensation CC vo go. II CC 0 CMOS Analog Design Using All-Region MOSFET Modeling CC=0

Two-stage amplifiers - 4 Frequency compensation + vid - io. I + - gm. I Co. I vo. I -gm. II go. I CL Frequency compensation CC vo go. II CC 0 CMOS Analog Design Using All-Region MOSFET Modeling CC=0

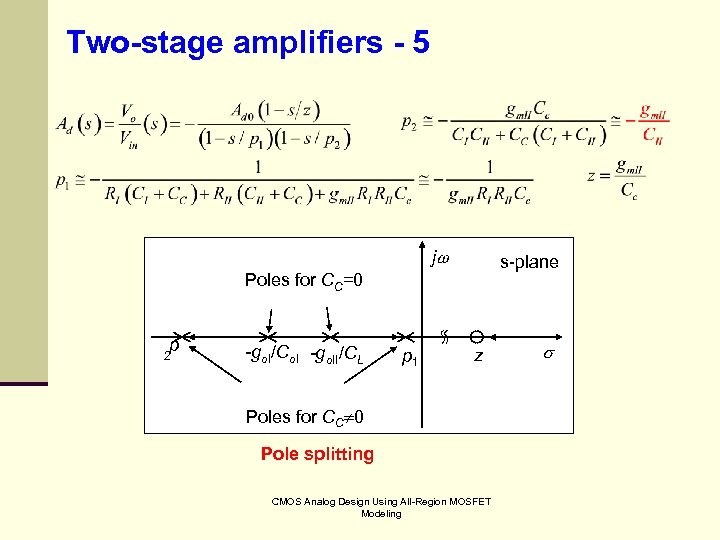

Two-stage amplifiers - 5 j s-plane Poles for CC=0 p 2 -go. I/Co. I -go. II/CL p 1 z Poles for CC 0 Pole splitting CMOS Analog Design Using All-Region MOSFET Modeling

Two-stage amplifiers - 5 j s-plane Poles for CC=0 p 2 -go. I/Co. I -go. II/CL p 1 z Poles for CC 0 Pole splitting CMOS Analog Design Using All-Region MOSFET Modeling

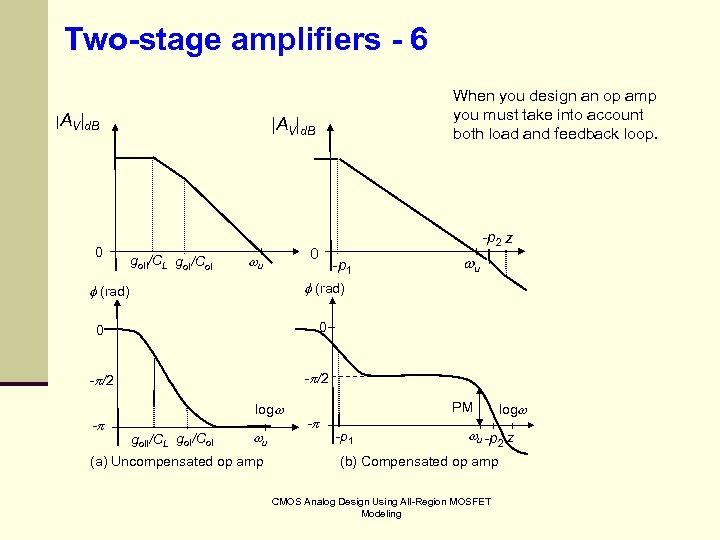

Two-stage amplifiers - 6 |AV|d. B 0 |AV|d. B go. II/CL go. I/Co. I -p 2 z 0 u -p 1 u (rad) 0 0 - /2 - When you design an op amp you must take into account both load and feedback loop. log go. II/CL go. I/Co. I u (a) Uncompensated op amp - PM -p 1 log u -p z 2 (b) Compensated op amp CMOS Analog Design Using All-Region MOSFET Modeling

Two-stage amplifiers - 6 |AV|d. B 0 |AV|d. B go. II/CL go. I/Co. I -p 2 z 0 u -p 1 u (rad) 0 0 - /2 - When you design an op amp you must take into account both load and feedback loop. log go. II/CL go. I/Co. I u (a) Uncompensated op amp - PM -p 1 log u -p z 2 (b) Compensated op amp CMOS Analog Design Using All-Region MOSFET Modeling

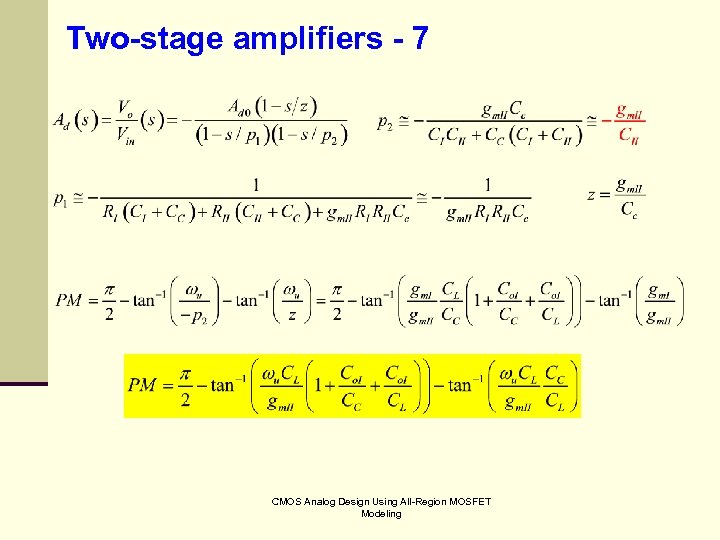

Two-stage amplifiers - 7 CMOS Analog Design Using All-Region MOSFET Modeling

Two-stage amplifiers - 7 CMOS Analog Design Using All-Region MOSFET Modeling

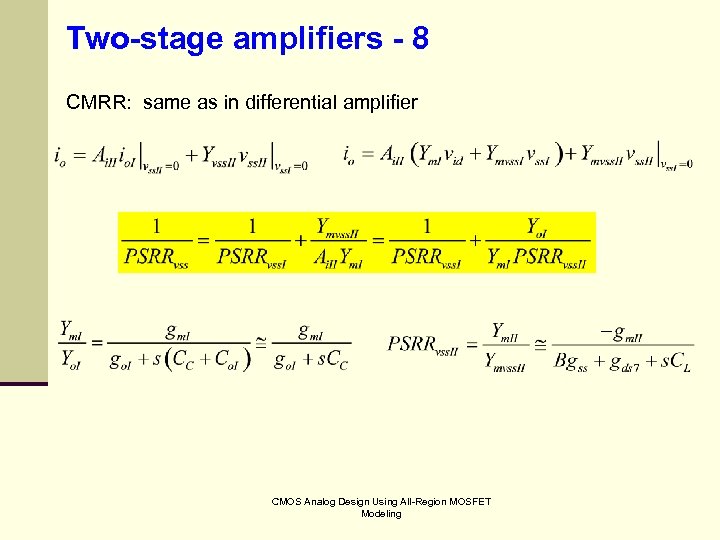

Two-stage amplifiers - 8 CMRR: same as in differential amplifier CMOS Analog Design Using All-Region MOSFET Modeling

Two-stage amplifiers - 8 CMRR: same as in differential amplifier CMOS Analog Design Using All-Region MOSFET Modeling

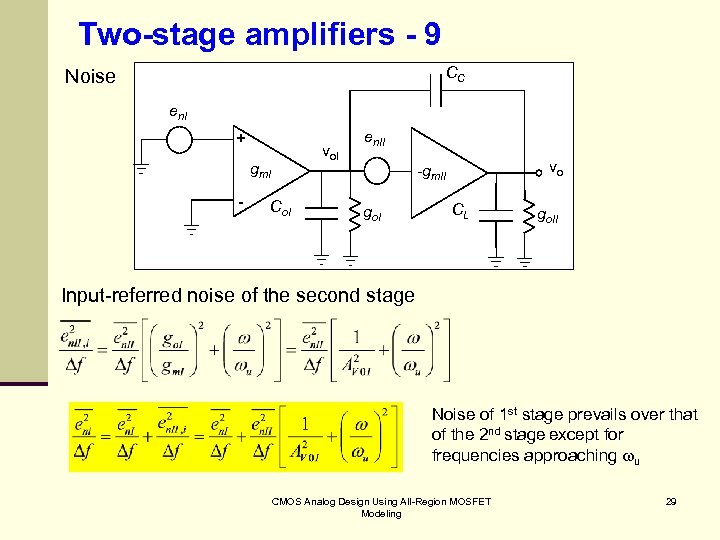

Two-stage amplifiers - 9 CC Noise en. I + vo. I gm. I - Co. I en. II vo -gm. II go. I CL go. II Input-referred noise of the second stage Noise of 1 st stage prevails over that of the 2 nd stage except for frequencies approaching u CMOS Analog Design Using All-Region MOSFET Modeling 29

Two-stage amplifiers - 9 CC Noise en. I + vo. I gm. I - Co. I en. II vo -gm. II go. I CL go. II Input-referred noise of the second stage Noise of 1 st stage prevails over that of the 2 nd stage except for frequencies approaching u CMOS Analog Design Using All-Region MOSFET Modeling 29

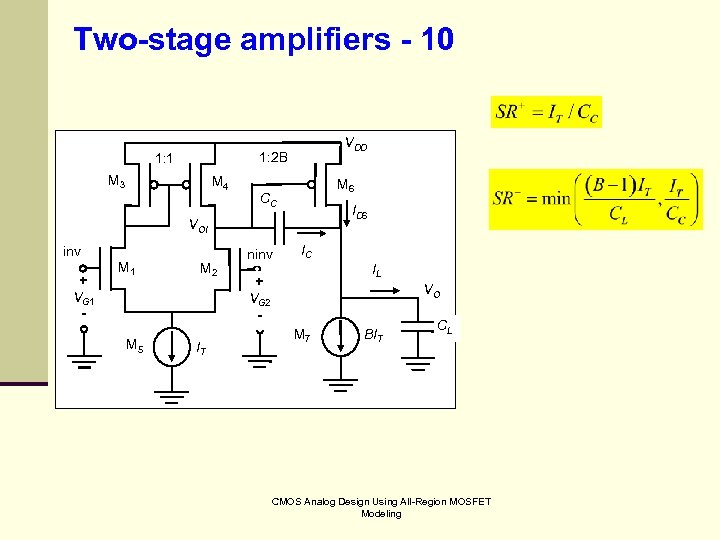

Two-stage amplifiers - 10 VDD 1: 2 B 1: 1 M 3 M 4 M 6 CC ID 6 VOI inv + VG 1 - M 1 M 5 M 2 IT ninv IC IL + VG 2 - VO M 7 BIT CL CMOS Analog Design Using All-Region MOSFET Modeling

Two-stage amplifiers - 10 VDD 1: 2 B 1: 1 M 3 M 4 M 6 CC ID 6 VOI inv + VG 1 - M 1 M 5 M 2 IT ninv IC IL + VG 2 - VO M 7 BIT CL CMOS Analog Design Using All-Region MOSFET Modeling

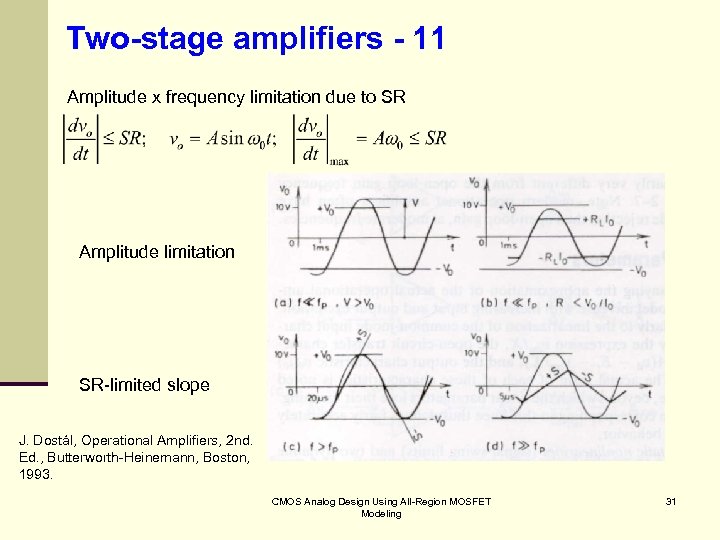

Two-stage amplifiers - 11 Amplitude x frequency limitation due to SR Amplitude limitation SR-limited slope J. Dostál, Operational Amplifiers, 2 nd. Ed. , Butterworth-Heinemann, Boston, 1993. CMOS Analog Design Using All-Region MOSFET Modeling 31

Two-stage amplifiers - 11 Amplitude x frequency limitation due to SR Amplitude limitation SR-limited slope J. Dostál, Operational Amplifiers, 2 nd. Ed. , Butterworth-Heinemann, Boston, 1993. CMOS Analog Design Using All-Region MOSFET Modeling 31

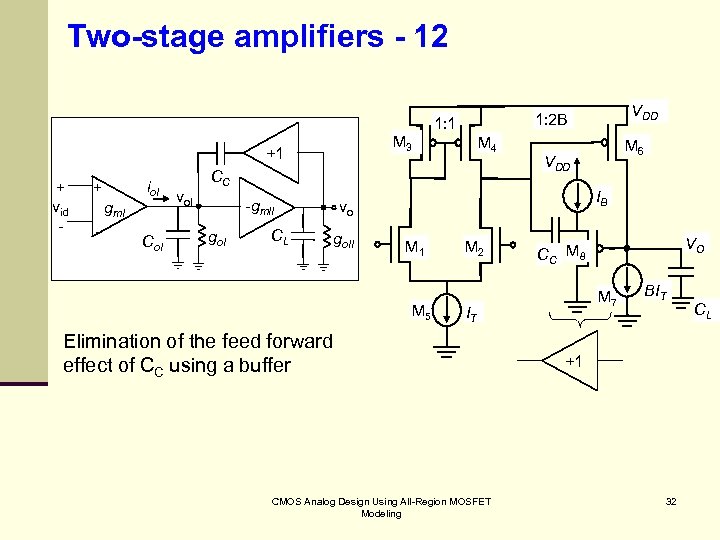

Two-stage amplifiers - 12 M 3 +1 + vid - io. I + gm. I - Co. I vo. I M 4 CC -gm. II go. I CL M 6 VDD IB vo go. II VDD 1: 2 B 1: 1 M 5 M 2 M 7 IT Elimination of the feed forward effect of CC using a buffer CMOS Analog Design Using All-Region MOSFET Modeling VO C C M 8 BIT +1 32 CL

Two-stage amplifiers - 12 M 3 +1 + vid - io. I + gm. I - Co. I vo. I M 4 CC -gm. II go. I CL M 6 VDD IB vo go. II VDD 1: 2 B 1: 1 M 5 M 2 M 7 IT Elimination of the feed forward effect of CC using a buffer CMOS Analog Design Using All-Region MOSFET Modeling VO C C M 8 BIT +1 32 CL

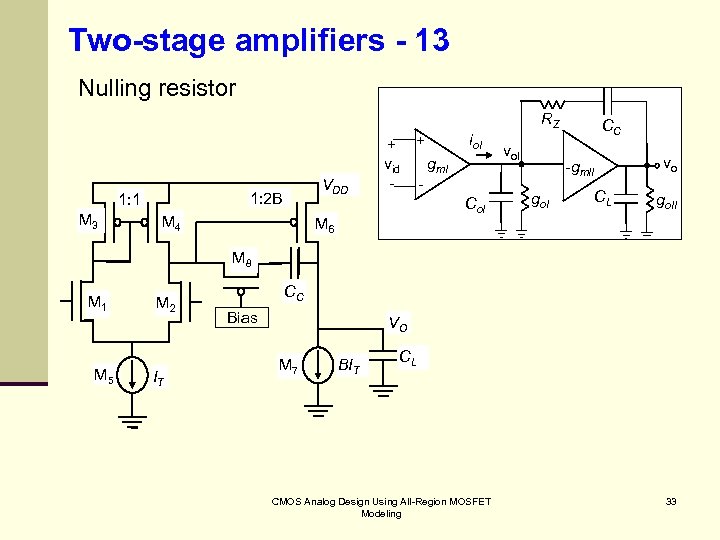

Two-stage amplifiers - 13 Nulling resistor 1: 2 B 1: 1 M 3 VDD M 4 + + vid gm. I - - io. I Co. I M 6 RZ vo. I CC vo -gm. II go. I CL go. II M 8 M 1 M 5 M 2 IT CC Bias VO M 7 BIT CL CMOS Analog Design Using All-Region MOSFET Modeling 33

Two-stage amplifiers - 13 Nulling resistor 1: 2 B 1: 1 M 3 VDD M 4 + + vid gm. I - - io. I Co. I M 6 RZ vo. I CC vo -gm. II go. I CL go. II M 8 M 1 M 5 M 2 IT CC Bias VO M 7 BIT CL CMOS Analog Design Using All-Region MOSFET Modeling 33

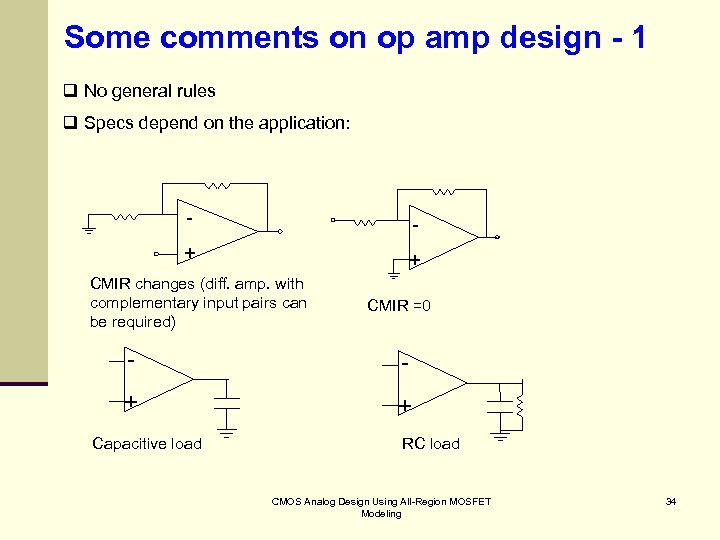

Some comments on op amp design - 1 q No general rules q Specs depend on the application: - - + + CMIR changes (diff. amp. with complementary input pairs can be required) CMIR =0 - - + + Capacitive load RC load CMOS Analog Design Using All-Region MOSFET Modeling 34

Some comments on op amp design - 1 q No general rules q Specs depend on the application: - - + + CMIR changes (diff. amp. with complementary input pairs can be required) CMIR =0 - - + + Capacitive load RC load CMOS Analog Design Using All-Region MOSFET Modeling 34

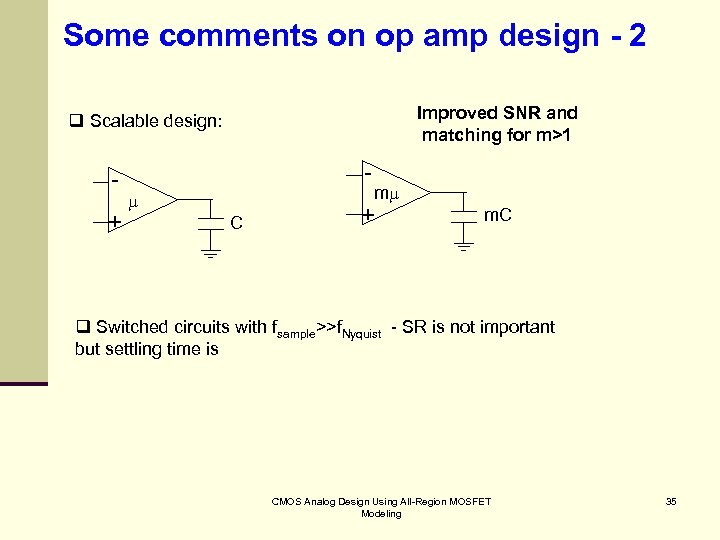

Some comments on op amp design - 2 Improved SNR and matching for m>1 q Scalable design: + C m + m. C q Switched circuits with fsample>>f. Nyquist - SR is not important but settling time is CMOS Analog Design Using All-Region MOSFET Modeling 35

Some comments on op amp design - 2 Improved SNR and matching for m>1 q Scalable design: + C m + m. C q Switched circuits with fsample>>f. Nyquist - SR is not important but settling time is CMOS Analog Design Using All-Region MOSFET Modeling 35

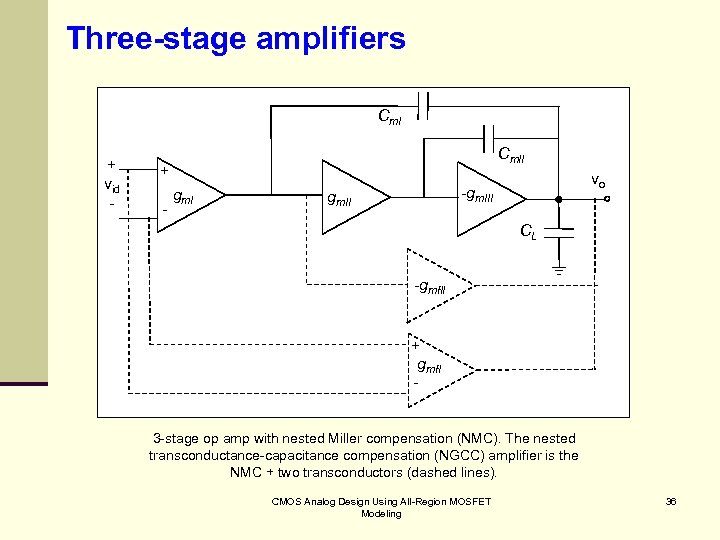

Three-stage amplifiers Cm. I + vid - Cm. II + - gm. I vo -gm. III gm. II CL -gmf. II + gmf. I 3 -stage op amp with nested Miller compensation (NMC). The nested transconductance-capacitance compensation (NGCC) amplifier is the NMC + two transconductors (dashed lines). CMOS Analog Design Using All-Region MOSFET Modeling 36

Three-stage amplifiers Cm. I + vid - Cm. II + - gm. I vo -gm. III gm. II CL -gmf. II + gmf. I 3 -stage op amp with nested Miller compensation (NMC). The nested transconductance-capacitance compensation (NGCC) amplifier is the NMC + two transconductors (dashed lines). CMOS Analog Design Using All-Region MOSFET Modeling 36

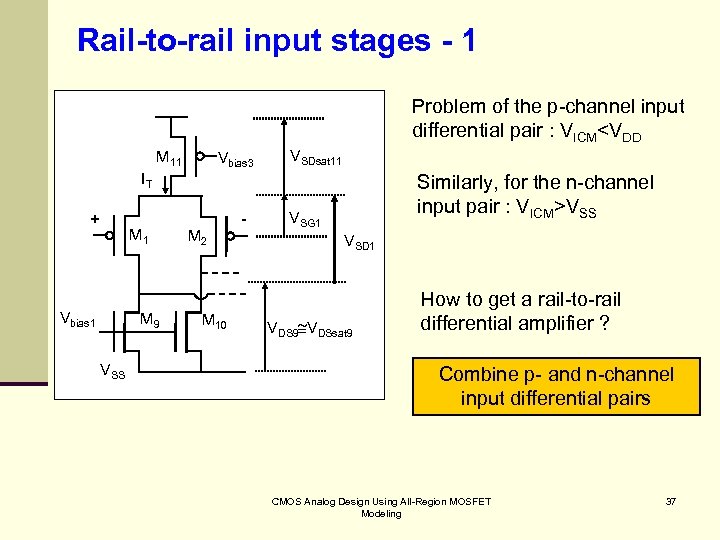

Rail-to-rail input stages - 1 Problem of the p-channel input differential pair : VICM

Rail-to-rail input stages - 1 Problem of the p-channel input differential pair : VICM

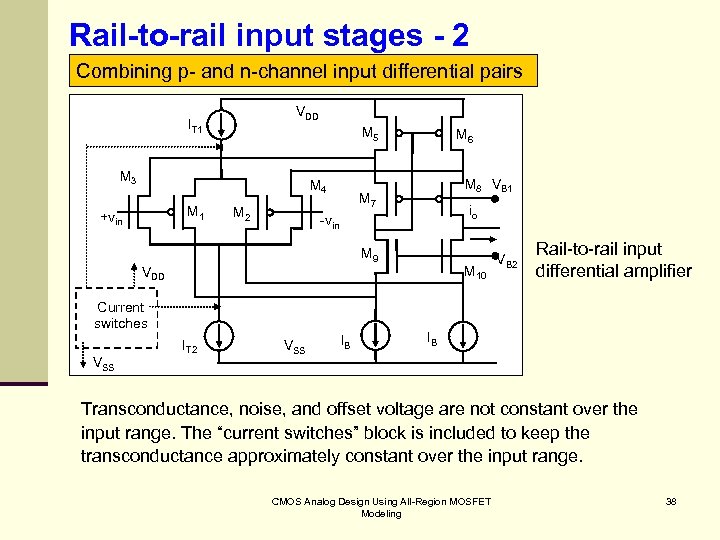

Rail-to-rail input stages - 2 Combining p- and n-channel input differential pairs VDD IT 1 M 5 M 3 M 4 M 1 +vin M 2 M 6 M 8 VB 1 M 7 io -vin M 9 M 10 VDD Current switches VSS IT 2 VSS IB VB 2 Rail-to-rail input differential amplifier IB Transconductance, noise, and offset voltage are not constant over the input range. The “current switches” block is included to keep the transconductance approximately constant over the input range. CMOS Analog Design Using All-Region MOSFET Modeling 38

Rail-to-rail input stages - 2 Combining p- and n-channel input differential pairs VDD IT 1 M 5 M 3 M 4 M 1 +vin M 2 M 6 M 8 VB 1 M 7 io -vin M 9 M 10 VDD Current switches VSS IT 2 VSS IB VB 2 Rail-to-rail input differential amplifier IB Transconductance, noise, and offset voltage are not constant over the input range. The “current switches” block is included to keep the transconductance approximately constant over the input range. CMOS Analog Design Using All-Region MOSFET Modeling 38

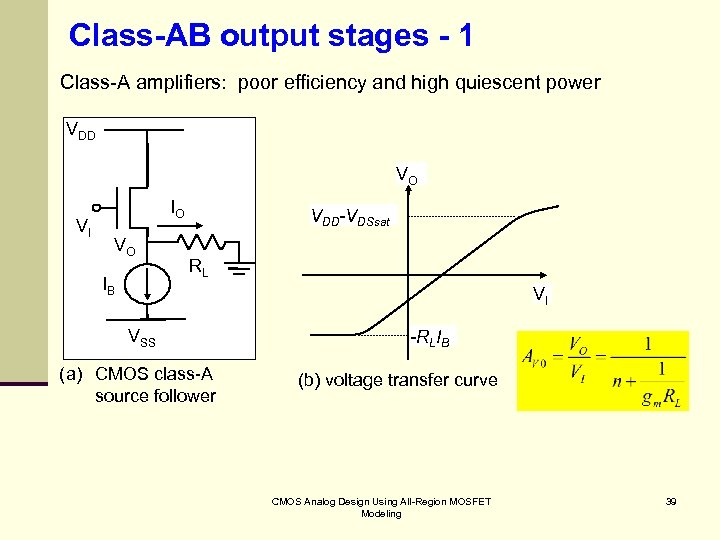

Class-AB output stages - 1 Class-A amplifiers: poor efficiency and high quiescent power VDD VO VI IO VO IB VDD-VDSsat RL VI VSS (a) CMOS class-A source follower -RLIB (b) voltage transfer curve CMOS Analog Design Using All-Region MOSFET Modeling 39

Class-AB output stages - 1 Class-A amplifiers: poor efficiency and high quiescent power VDD VO VI IO VO IB VDD-VDSsat RL VI VSS (a) CMOS class-A source follower -RLIB (b) voltage transfer curve CMOS Analog Design Using All-Region MOSFET Modeling 39

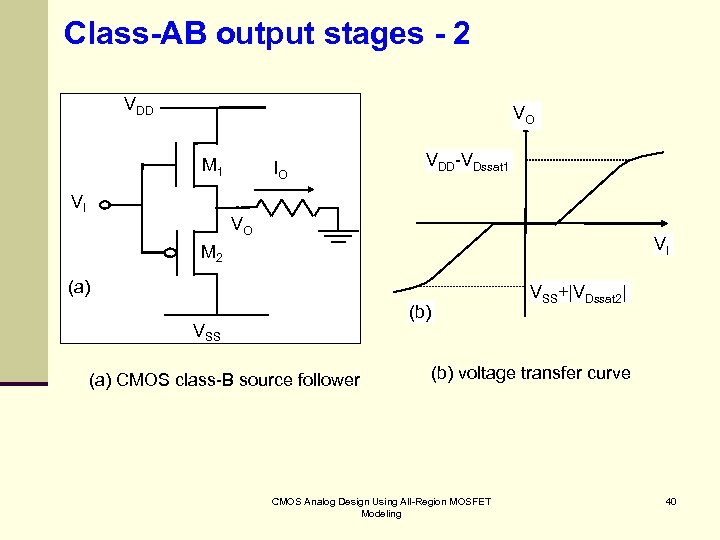

Class-AB output stages - 2 VDD VO M 1 VI IO VDD-VDssat 1 VO VI M 2 (a) VSS+|VDssat 2| (b) VSS (a) CMOS class-B source follower (b) voltage transfer curve CMOS Analog Design Using All-Region MOSFET Modeling 40

Class-AB output stages - 2 VDD VO M 1 VI IO VDD-VDssat 1 VO VI M 2 (a) VSS+|VDssat 2| (b) VSS (a) CMOS class-B source follower (b) voltage transfer curve CMOS Analog Design Using All-Region MOSFET Modeling 40

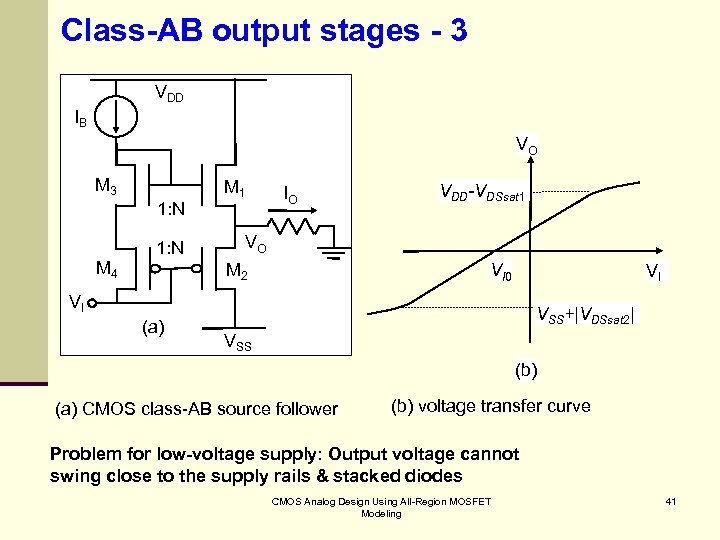

Class-AB output stages - 3 VDD IB VO M 3 1: N M 4 1: N M 1 IO VDD-VDSsat 1 VO M 2 VI 0 VI VI (a) VSS+|VDSsat 2| VSS (b) (a) CMOS class-AB source follower (b) voltage transfer curve Problem for low-voltage supply: Output voltage cannot swing close to the supply rails & stacked diodes CMOS Analog Design Using All-Region MOSFET Modeling 41

Class-AB output stages - 3 VDD IB VO M 3 1: N M 4 1: N M 1 IO VDD-VDSsat 1 VO M 2 VI 0 VI VI (a) VSS+|VDSsat 2| VSS (b) (a) CMOS class-AB source follower (b) voltage transfer curve Problem for low-voltage supply: Output voltage cannot swing close to the supply rails & stacked diodes CMOS Analog Design Using All-Region MOSFET Modeling 41

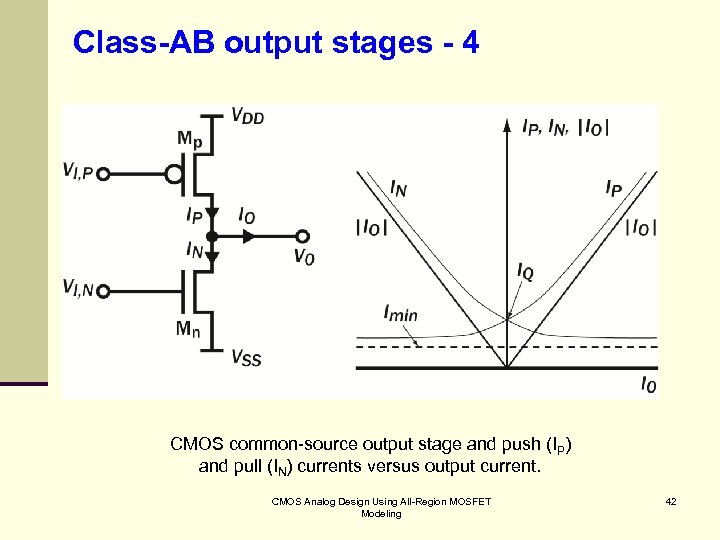

Class-AB output stages - 4 CMOS common-source output stage and push (IP) and pull (IN) currents versus output current. CMOS Analog Design Using All-Region MOSFET Modeling 42

Class-AB output stages - 4 CMOS common-source output stage and push (IP) and pull (IN) currents versus output current. CMOS Analog Design Using All-Region MOSFET Modeling 42

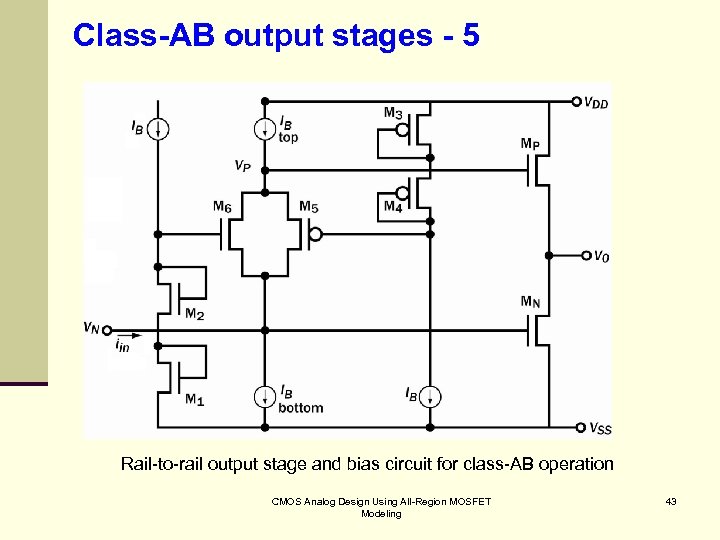

Class-AB output stages - 5 Rail-to-rail output stage and bias circuit for class-AB operation CMOS Analog Design Using All-Region MOSFET Modeling 43

Class-AB output stages - 5 Rail-to-rail output stage and bias circuit for class-AB operation CMOS Analog Design Using All-Region MOSFET Modeling 43

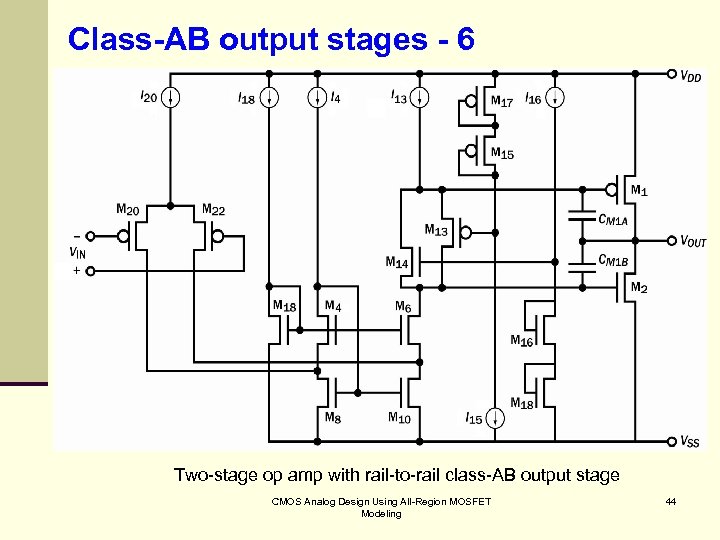

Class-AB output stages - 6 Two-stage op amp with rail-to-rail class-AB output stage CMOS Analog Design Using All-Region MOSFET Modeling 44

Class-AB output stages - 6 Two-stage op amp with rail-to-rail class-AB output stage CMOS Analog Design Using All-Region MOSFET Modeling 44

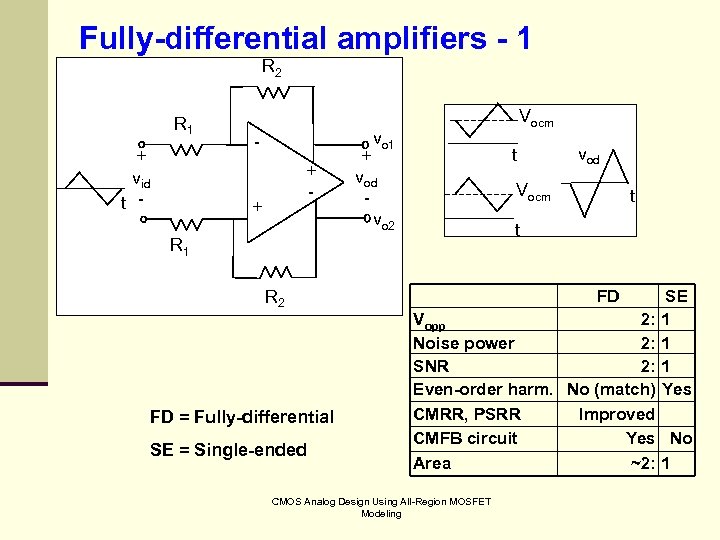

Fully-differential amplifiers - 1 R 2 R 1 + vid t - Vocm vo 1 + - + t + vod vo 2 Vocm R 2 SE = Single-ended t t R 1 FD = Fully-differential vod FD SE 1 1 1 Yes Vopp 2: Noise power 2: SNR 2: Even-order harm. No (match) CMRR, PSRR Improved CMFB circuit Yes No Area ~2: 1 CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 1 R 2 R 1 + vid t - Vocm vo 1 + - + t + vod vo 2 Vocm R 2 SE = Single-ended t t R 1 FD = Fully-differential vod FD SE 1 1 1 Yes Vopp 2: Noise power 2: SNR 2: Even-order harm. No (match) CMRR, PSRR Improved CMFB circuit Yes No Area ~2: 1 CMOS Analog Design Using All-Region MOSFET Modeling

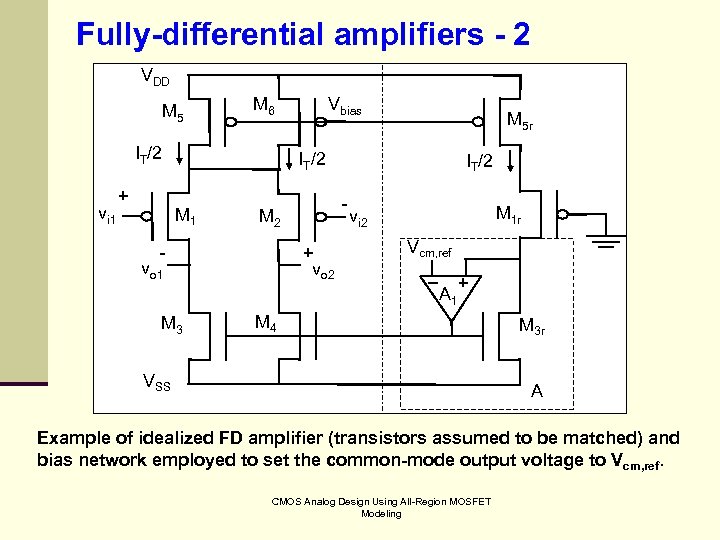

Fully-differential amplifiers - 2 VDD M 5 M 6 IT/2 vi 1 + Vbias M 5 r IT/2 M 1 + vo 2 vo 1 M 3 - M 2 - IT/2 M 1 r vi 2 Vcm, ref A 1 + M 4 VSS M 3 r A Example of idealized FD amplifier (transistors assumed to be matched) and bias network employed to set the common-mode output voltage to Vcm, ref. CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 2 VDD M 5 M 6 IT/2 vi 1 + Vbias M 5 r IT/2 M 1 + vo 2 vo 1 M 3 - M 2 - IT/2 M 1 r vi 2 Vcm, ref A 1 + M 4 VSS M 3 r A Example of idealized FD amplifier (transistors assumed to be matched) and bias network employed to set the common-mode output voltage to Vcm, ref. CMOS Analog Design Using All-Region MOSFET Modeling

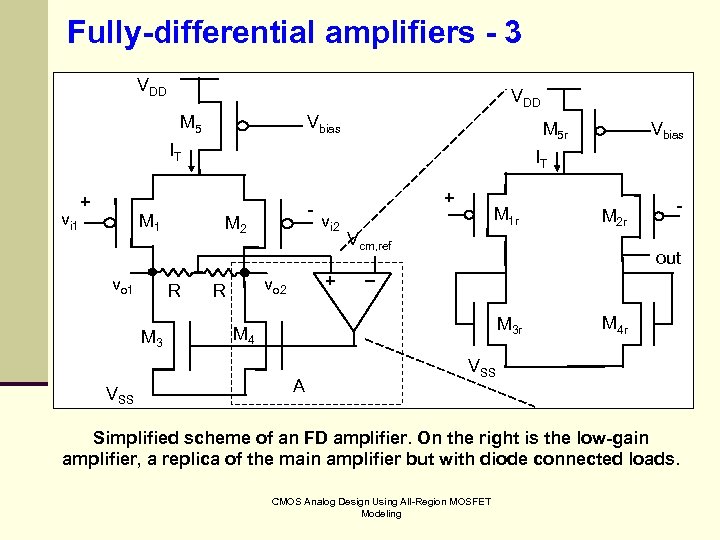

Fully-differential amplifiers - 3 VDD M 5 Vbias M 5 r IT vi 1 + M 1 vo 1 M 3 VSS IT - M 2 R Vbias vi 2 + vo 2 R + M 1 r Vcm, ref out M 3 r M 4 A M 2 r M 4 r VSS Simplified scheme of an FD amplifier. On the right is the low-gain amplifier, a replica of the main amplifier but with diode connected loads. CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 3 VDD M 5 Vbias M 5 r IT vi 1 + M 1 vo 1 M 3 VSS IT - M 2 R Vbias vi 2 + vo 2 R + M 1 r Vcm, ref out M 3 r M 4 A M 2 r M 4 r VSS Simplified scheme of an FD amplifier. On the right is the low-gain amplifier, a replica of the main amplifier but with diode connected loads. CMOS Analog Design Using All-Region MOSFET Modeling

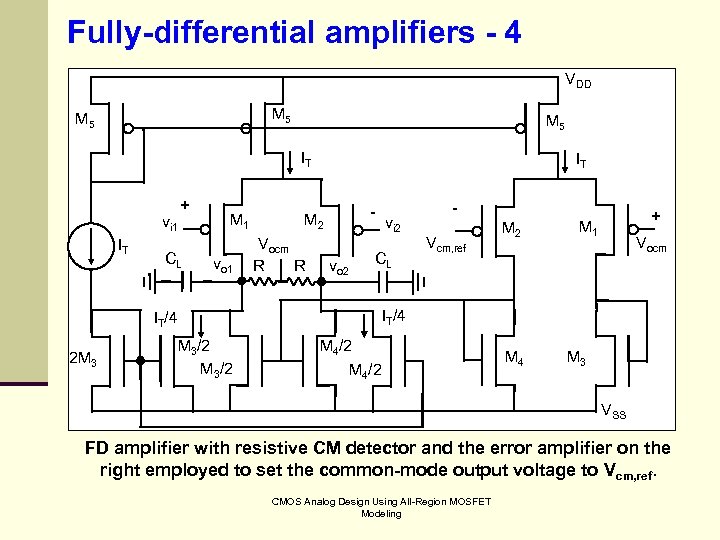

Fully-differential amplifiers - 4 VDD M 5 M 5 IT + vi 1 IT CL M 1 vo 1 IT - M 2 Vocm R R vo 2 CL M 3/2 Vcm, ref M 2 + M 1 Vocm IT/4 2 M 3 vi 2 - M 4/2 M 4 M 3 VSS FD amplifier with resistive CM detector and the error amplifier on the right employed to set the common-mode output voltage to Vcm, ref. CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 4 VDD M 5 M 5 IT + vi 1 IT CL M 1 vo 1 IT - M 2 Vocm R R vo 2 CL M 3/2 Vcm, ref M 2 + M 1 Vocm IT/4 2 M 3 vi 2 - M 4/2 M 4 M 3 VSS FD amplifier with resistive CM detector and the error amplifier on the right employed to set the common-mode output voltage to Vcm, ref. CMOS Analog Design Using All-Region MOSFET Modeling

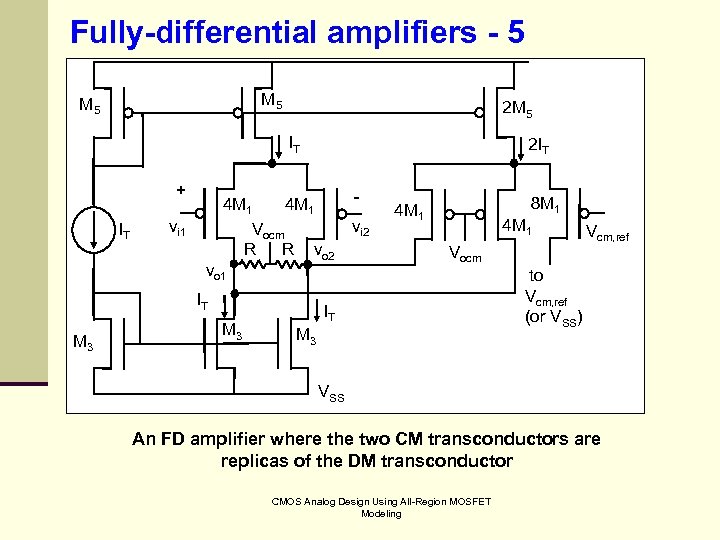

Fully-differential amplifiers - 5 M 5 2 M 5 IT + IT 2 IT 4 M 1 vi 2 Vocm R R vo 2 vi 1 vo 1 IT M 3 8 M 1 4 M 1 Vocm IT M 3 Vcm, ref to Vcm, ref (or VSS) VSS An FD amplifier where the two CM transconductors are replicas of the DM transconductor CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 5 M 5 2 M 5 IT + IT 2 IT 4 M 1 vi 2 Vocm R R vo 2 vi 1 vo 1 IT M 3 8 M 1 4 M 1 Vocm IT M 3 Vcm, ref to Vcm, ref (or VSS) VSS An FD amplifier where the two CM transconductors are replicas of the DM transconductor CMOS Analog Design Using All-Region MOSFET Modeling

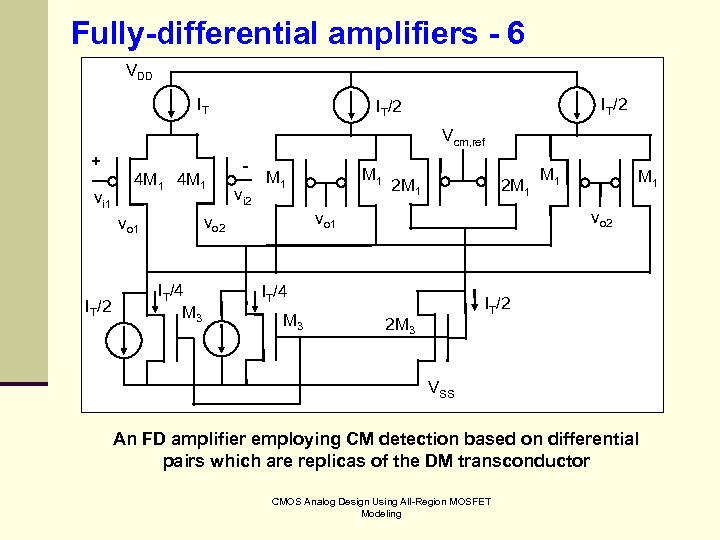

Fully-differential amplifiers - 6 VDD IT IT/2 Vcm, ref + vi 1 4 M 1 vi 2 IT/4 M 3 M 1 2 M 1 IT/4 M 3 M 1 vo 2 vo 1 IT/2 - IT/2 2 M 3 VSS An FD amplifier employing CM detection based on differential pairs which are replicas of the DM transconductor CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 6 VDD IT IT/2 Vcm, ref + vi 1 4 M 1 vi 2 IT/4 M 3 M 1 2 M 1 IT/4 M 3 M 1 vo 2 vo 1 IT/2 - IT/2 2 M 3 VSS An FD amplifier employing CM detection based on differential pairs which are replicas of the DM transconductor CMOS Analog Design Using All-Region MOSFET Modeling

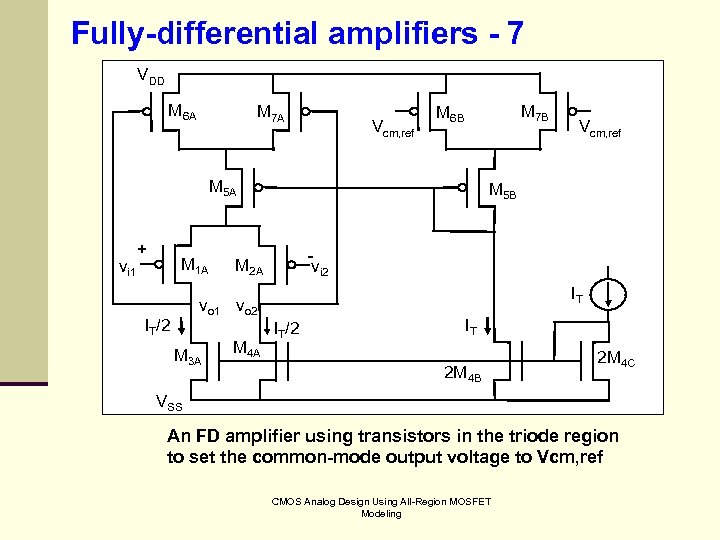

Fully-differential amplifiers - 7 VDD M 6 A M 7 A Vcm, ref M 7 B M 6 B M 5 A vi 1 + M 1 A M 5 B vi 2 M 2 A IT vo 1 vo 2 IT/2 M 3 A M 4 A Vcm, ref IT/2 IT 2 M 4 B 2 M 4 C VSS An FD amplifier using transistors in the triode region to set the common-mode output voltage to Vcm, ref CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 7 VDD M 6 A M 7 A Vcm, ref M 7 B M 6 B M 5 A vi 1 + M 1 A M 5 B vi 2 M 2 A IT vo 1 vo 2 IT/2 M 3 A M 4 A Vcm, ref IT/2 IT 2 M 4 B 2 M 4 C VSS An FD amplifier using transistors in the triode region to set the common-mode output voltage to Vcm, ref CMOS Analog Design Using All-Region MOSFET Modeling

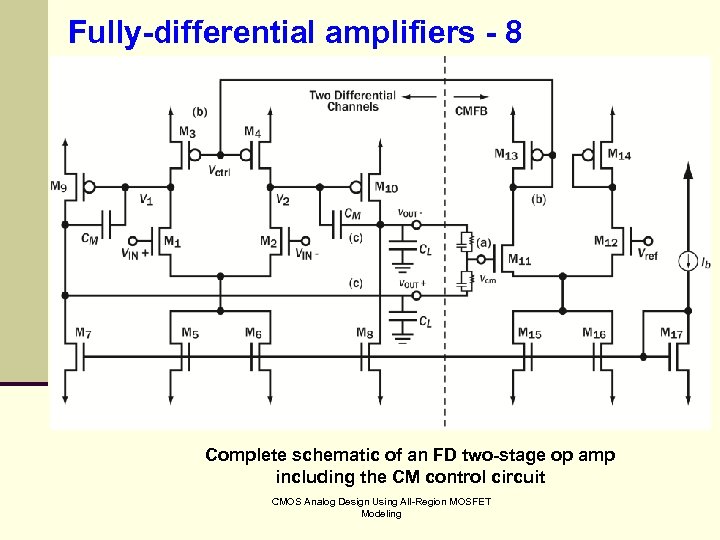

Fully-differential amplifiers - 8 Complete schematic of an FD two-stage op amp including the CM control circuit CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 8 Complete schematic of an FD two-stage op amp including the CM control circuit CMOS Analog Design Using All-Region MOSFET Modeling

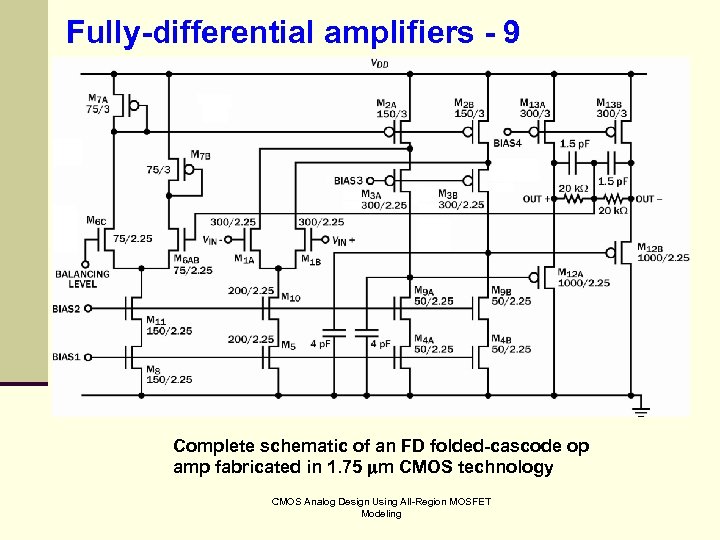

Fully-differential amplifiers - 9 Complete schematic of an FD folded-cascode op amp fabricated in 1. 75 m CMOS technology CMOS Analog Design Using All-Region MOSFET Modeling

Fully-differential amplifiers - 9 Complete schematic of an FD folded-cascode op amp fabricated in 1. 75 m CMOS technology CMOS Analog Design Using All-Region MOSFET Modeling

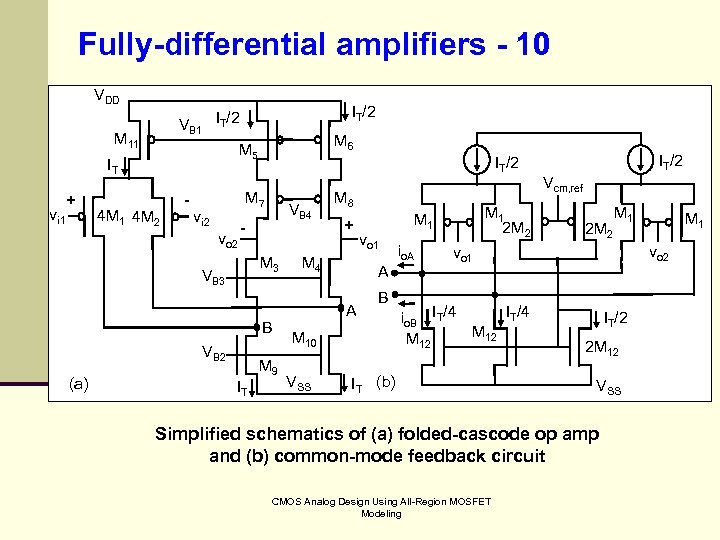

Fully-differential amplifiers - 10 VDD M 11 + M 6 M 5 IT vi 1 IT/2 VB 1 IT/2 4 M 1 4 M 2 - M 7 vi 2 vo 2 VB 4 M 3 VB 3 B VB 2 (a) M 9 IT IT/2 Vcm, ref M 8 + M 4 vo 1 A A B M 10 VSS M 1 2 M 2 M 1 io. A 2 M 2 M 1 vo 2 vo 1 IT/4 io. B IT/4 M 12 IT (b) IT/2 2 M 12 VSS Simplified schematics of (a) folded-cascode op amp and (b) common-mode feedback circuit CMOS Analog Design Using All-Region MOSFET Modeling M 1

Fully-differential amplifiers - 10 VDD M 11 + M 6 M 5 IT vi 1 IT/2 VB 1 IT/2 4 M 1 4 M 2 - M 7 vi 2 vo 2 VB 4 M 3 VB 3 B VB 2 (a) M 9 IT IT/2 Vcm, ref M 8 + M 4 vo 1 A A B M 10 VSS M 1 2 M 2 M 1 io. A 2 M 2 M 1 vo 2 vo 1 IT/4 io. B IT/4 M 12 IT (b) IT/2 2 M 12 VSS Simplified schematics of (a) folded-cascode op amp and (b) common-mode feedback circuit CMOS Analog Design Using All-Region MOSFET Modeling M 1