ЦАП_ADuC.pptx

- Количество слайдов: 18

Цифро-Аналоговый преобразователь

Регистр управления DACCON • Адрес регистра FDH • Значение регистра при вкл. Питания 04 H • Побитная адресация НЕТ

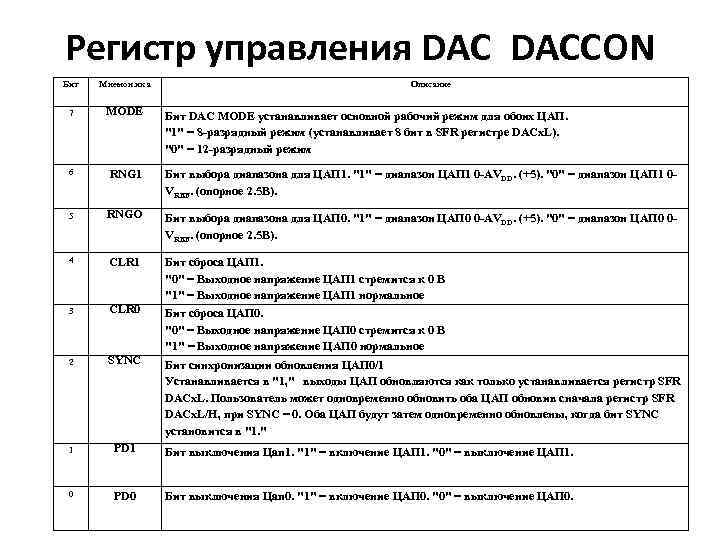

Регистр управления DACCON Бит Мнемон. ика Описание 7 MODE 6 RNG 1 Бит выбора диапазона для ЦАП 1. "1" = диапазон ЦАП 1 0 -AVDD. (+5). "0" = диапазон ЦАП 1 0 VREF. (опорное 2. 5 В). 5 RNGO Бит выбора диапазона для ЦАП 0. "1" = диапазон ЦАП 0 0 -AVDD. (+5). "0" = диапазон ЦАП 0 0 VREF. (опорное 2. 5 В). 4 CLR 1 Бит сброса ЦАП 1. "0" = Выходное напряжение ЦАП 1 стремится к 0 В "1" = Выходное напряжение ЦАП 1 нормальное 3 CLR 0 Бит сброса ЦАП 0. "0" = Выходное напряжение ЦАП 0 стремится к 0 В "1" = Выходное напряжение ЦАП 0 нормальное 2 SYNC Бит синхронизации обновления ЦАП 0/1 Устанавливается в "1, " выходы ЦАП обновляются как только устанавливается регистр SFR DACx. L. Пользователь может одновременно обновить оба ЦАП обновив сначала регистр SFR DACx. L/H, при SYNC = 0. Оба ЦАП будут затем одновременно обновлены, когда бит SYNC установится в "1. " 1 PD 1 Бит выключения Цап 1. "1" = включение ЦАП 1. "0" = выключение ЦАП 1. 0 PD 0 Бит выключения Цап 0. "1" = включение ЦАП 0. "0" = выключение ЦАП 0. Бит DAC MODE устанавливает основной рабочий режим для обоих ЦАП. "1" = 8 -разрядный режим (устанавливает 8 бит в SFR регистре DACx. L). "0" = 12 -разрядный режим

Регистры данных DAC 0 H/L ; DAC 1 H/L В регистры записываются входные данные ЦАП

Широтно-импульсный модулятор (ШИМ)

Регистры ШИМ • управляющий регистр (PWMCON), Значение по умолчанию при включение питания 00 Н Побитовая адресация Нет • четыре регистра данных (PWMOH, PWMOL, PWMIH, и PWM 1 L).

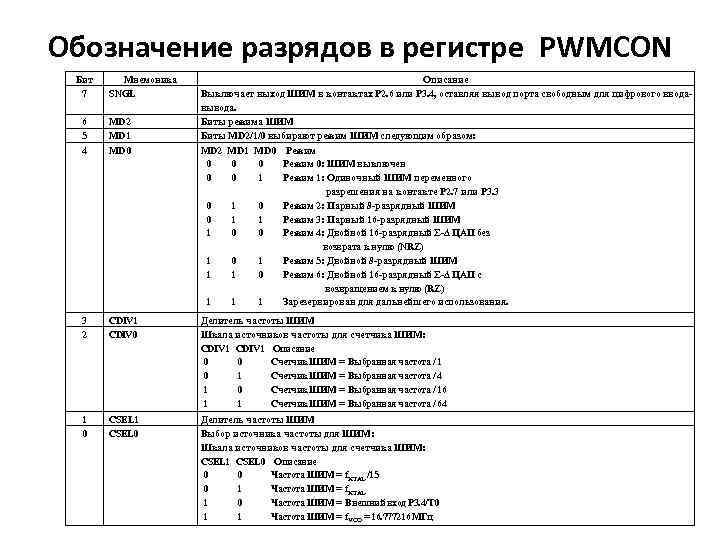

Обозначение разрядов в регистре PWMCON Бит 7 Мнемоника SNGL Описание Выключает выход ШИМ в контактах P 2. 6 или P 3. 4, оставляя вывод порта свободным для цифрового вводавывода. Биты режима ШИМ Биты MD 2/1/0 выбирают режим ШИМ следующим образом: MD 2 MD 1 MD 0 Режим 0 0 0 Режим 0: ШИМ выключен 0 0 1 Режим 1: Одиночный ШИМ переменного разрешения на контакте P 2. 7 или P 3. 3 0 1 0 Режим 2: Парный 8 -разрядный ШИМ 0 1 1 Режим 3: Парный 16 -разрядный ШИМ 1 0 0 Режим 4: Двойной 16 -разрядный Σ-Δ ЦАП без возврата к нулю (NRZ) 1 0 1 Режим 5: Двойной 8 -разрядный ШИМ 1 1 0 Режим 6: Двойной 16 -разрядный Σ-Δ ЦАП с возвращением к нулю (RZ) 1 1 1 Зарезервирован для дальнейшего использования. 6 5 4 MD 2 MD 1 MD 0 3 2 CDIV 1 CDIV 0 Делитель частоты ШИМ Шкала источников частоты для счетчика ШИМ: CDIV 1 Описание 0 0 Счетчик ШИМ = Выбранная частота / 1 0 1 Счетчик ШИМ = Выбранная частота / 4 1 0 Счетчик ШИМ = Выбранная частота / 16 1 1 Счетчик ШИМ = Выбранная частота / 64 1 0 CSEL 1 CSEL 0 Делитель частоты ШИМ Выбор источника частоты для ШИМ: Шкала источников частоты для счетчика ШИМ: CSEL 1 CSEL 0 Описание 0 0 Частота ШИМ = f. XTAL /15 0 1 Частота ШИМ = f. XTAL 1 0 Частота ШИМ = Внешний вход P 3. 4/T 0 1 1 Частота ШИМ = f. VCO = 16. 777216 МГц

Режим 0: ШИМ выключен и это позволяет использовать P 2. 6 и P 2. 7 как обычно.

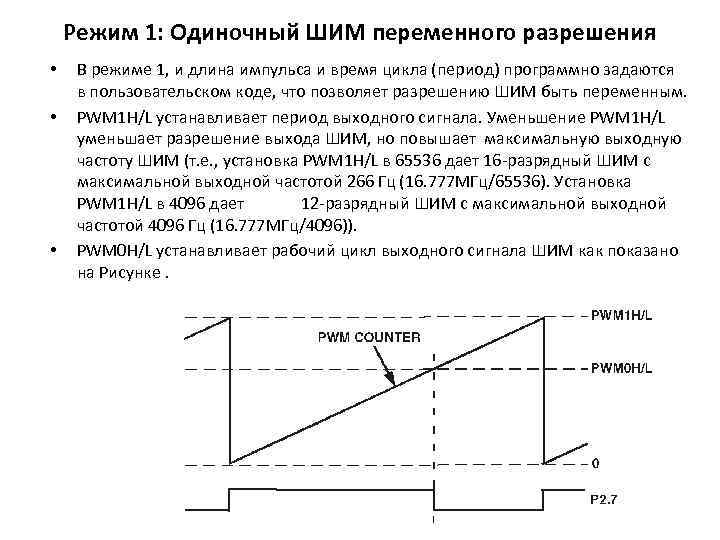

Режим 1: Одиночный ШИМ переменного разрешения • • • В режиме 1, и длина импульса и время цикла (период) программно задаются в пользовательском коде, что позволяет разрешению ШИМ быть переменным. PWM 1 H/L устанавливает период выходного сигнала. Уменьшение PWM 1 H/L уменьшает разрешение выхода ШИМ, но повышает максимальную выходную частоту ШИМ (т. е. , установка PWM 1 H/L в 65536 дает 16 -разрядный ШИМ с максимальной выходной частотой 266 Гц (16. 777 МГц/65536). Установка PWM 1 H/L в 4096 дает 12 -разрядный ШИМ с максимальной выходной частотой 4096 Гц (16. 777 MГц/4096)). PWM 0 H/L устанавливает рабочий цикл выходного сигнала ШИМ как показано на Рисунке.

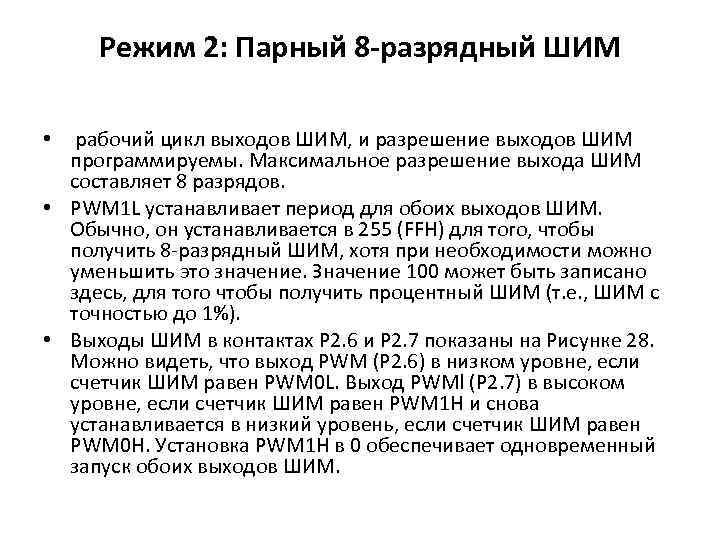

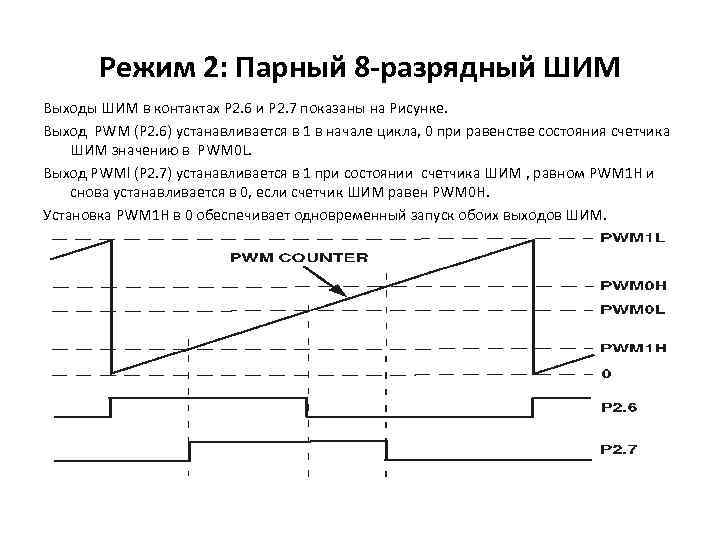

Режим 2: Парный 8 -разрядный ШИМ • рабочий цикл выходов ШИМ, и разрешение выходов ШИМ программируемы. Максимальное разрешение выхода ШИМ составляет 8 разрядов. • PWM 1 L устанавливает период для обоих выходов ШИМ. Обычно, он устанавливается в 255 (FFH) для того, чтобы получить 8 -разрядный ШИМ, хотя при необходимости можно уменьшить это значение. Значение 100 может быть записано здесь, для того чтобы получить процентный ШИМ (т. е. , ШИМ с точностью до 1%). • Выходы ШИМ в контактах P 2. 6 и P 2. 7 показаны на Рисунке 28. Можно видеть, что выход PWM (P 2. 6) в низком уровне, если счетчик ШИМ равен PWM 0 L. Выход PWMl (P 2. 7) в высоком уровне, если счетчик ШИМ равен PWM 1 H и снова устанавливается в низкий уровень, если счетчик ШИМ равен PWM 0 H. Установка PWM 1 H в 0 обеспечивает одновременный запуск обоих выходов ШИМ.

Режим 2: Парный 8 -разрядный ШИМ Выходы ШИМ в контактах P 2. 6 и P 2. 7 показаны на Рисунке. Выход PWM (P 2. 6) устанавливается в 1 в начале цикла, 0 при равенстве состояния счетчика ШИМ значению в PWM 0 L. Выход PWMl (P 2. 7) устанавливается в 1 при состоянии счетчика ШИМ , равном PWM 1 H и снова устанавливается в 0, если счетчик ШИМ равен PWM 0 H. Установка PWM 1 H в 0 обеспечивает одновременный запуск обоих выходов ШИМ.

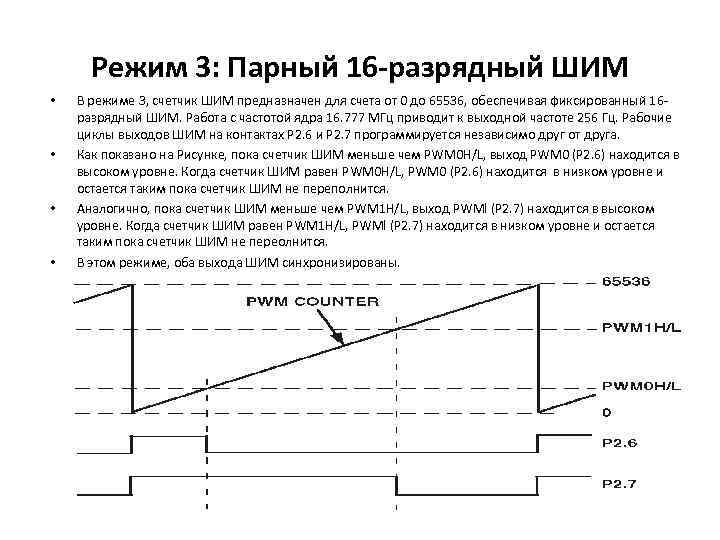

Режим 3: Парный 16 -разрядный ШИМ • • В режиме 3, счетчик ШИМ предназначен для счета от 0 до 65536, обеспечивая фиксированный 16 разрядный ШИМ. Работа с частотой ядра 16. 777 MГц приводит к выходной частоте 256 Гц. Рабочие циклы выходов ШИМ на контактах P 2. 6 и P 2. 7 программируется независимо друг от друга. Как показано на Рисунке, пока счетчик ШИМ меньше чем PWM 0 H/L, выход PWM 0 (P 2. 6) находится в высоком уровне. Когда счетчик ШИМ равен PWM 0 H/L, PWM 0 (P 2. 6) находится в низком уровне и остается таким пока счетчик ШИМ не переполнится. Аналогично, пока счетчик ШИМ меньше чем PWM 1 H/L, выход PWMl (P 2. 7) находится в высоком уровне. Когда счетчик ШИМ равен PWM 1 H/L, PWMl (P 2. 7) находится в низком уровне и остается таким пока счетчик ШИМ не переолнится. В этом режиме, оба выхода ШИМ синхронизированы.

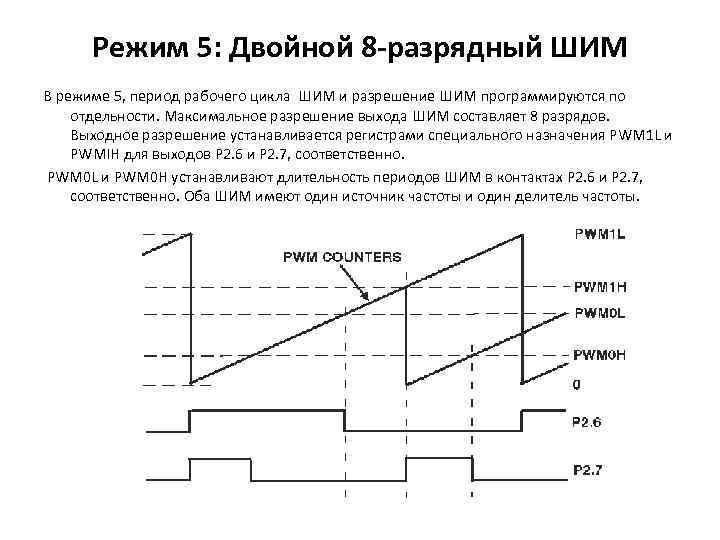

Режим 5: Двойной 8 -разрядный ШИМ В режиме 5, период рабочего цикла ШИМ и разрешение ШИМ программируются по отдельности. Максимальное разрешение выхода ШИМ составляет 8 разрядов. Выходное разрешение устанавливается регистрами специального назначения PWM 1 L и PWMIH для выходов P 2. 6 и P 2. 7, соответственно. PWM 0 L и PWM 0 H устанавливают длительность периодов ШИМ в контактах P 2. 6 и P 2. 7, соответственно. Оба ШИМ имеют один источник частоты и один делитель частоты.

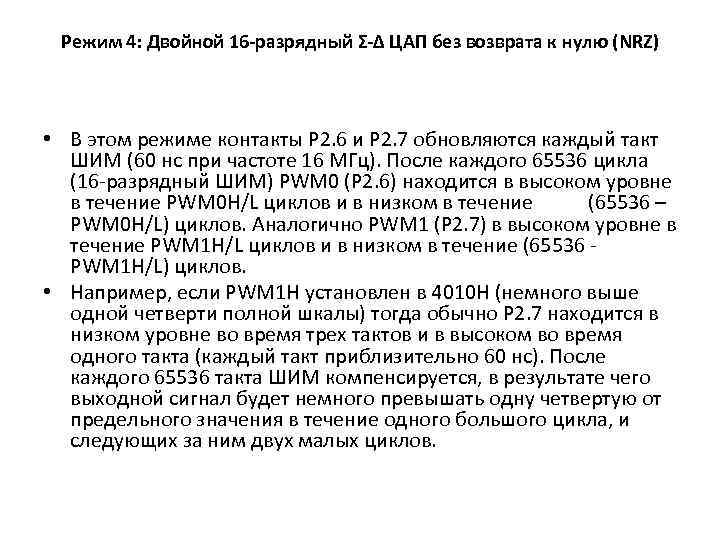

Режим 4: Двойной 16 -разрядный Σ-Δ ЦАП без возврата к нулю (NRZ) • В этом режиме контакты P 2. 6 и P 2. 7 обновляются каждый такт ШИМ (60 нс при частоте 16 MГц). После каждого 65536 цикла (16 -разрядный ШИМ) PWM 0 (P 2. 6) находится в высоком уровне в течение PWM 0 H/L циклов и в низком в течение (65536 – PWM 0 H/L) циклов. Аналогично PWM 1 (P 2. 7) в высоком уровне в течение PWM 1 H/L циклов и в низком в течение (65536 - PWM 1 H/L) циклов. • Например, если PWM 1 H установлен в 4010 H (немного выше одной четверти полной шкалы) тогда обычно P 2. 7 находится в низком уровне во время трех тактов и в высоком во время одного такта (каждый такт приблизительно 60 нс). После каждого 65536 такта ШИМ компенсируется, в результате чего выходной сигнал будет немного превышать одну четвертую от предельного значения в течение одного большого цикла, и следующих за ним двух малых циклов.

Режим 4: Двойной 16 -разрядный Σ-Δ ЦАП без возврата к нулю (NRZ)

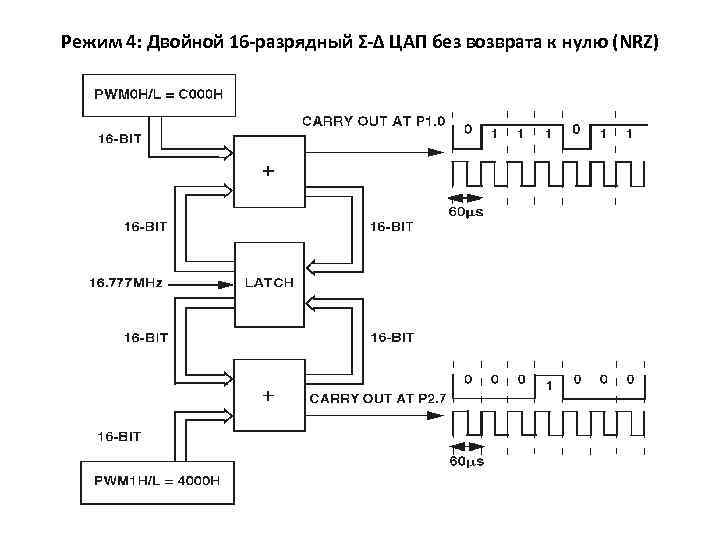

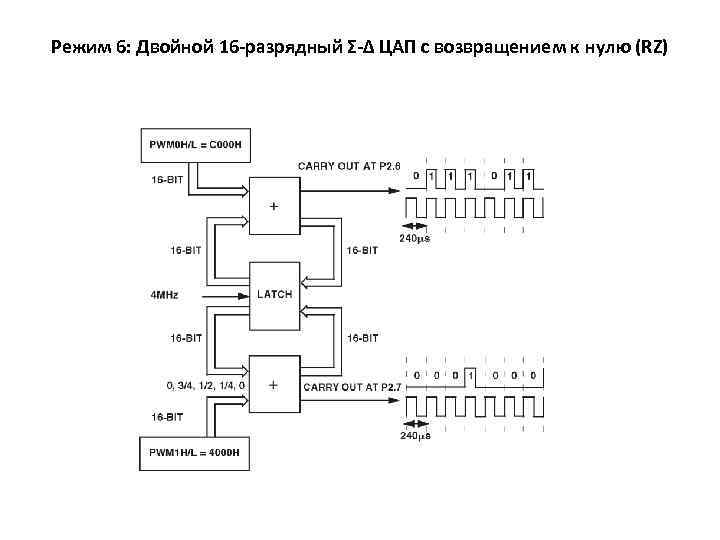

Режим 6: Двойной 16 -разрядный Σ-Δ ЦАП с возвращением к нулю (RZ) • Режим 6 обеспечивает высокую скорость выхода ШИМ подобно скорости Σ-Δ ЦАП. Режим 6 работает идентично Режиму 4. Однако, разница в том, что Режим 6 обеспечивает выход Σ-Δ ЦАП с возвращением к нулю (RZ). Режим 4 обеспечивает выход Σ-Δ ЦАП без возврата к нулю (NRZ). RZ режим гарантирует, что любое различие во времени нарастания и времени спада не приведет к инициализации Σ-Δ ЦАП. Однако, RZ режим уменьшает на половину динамический диапазон выходов Σ-Δ ЦАП с 0 -AVDD до 0 -AVDD/2. Для наилучшего результата режим следует использовать с делителем частоты ШИМ на четыре. • • Если PWM 1 H установлен в 4010 H (немного выше одной четвертой от предельного значения) тогда обычно P 2. 7 находится в низком уровне в течение трех полных тактов (3 цикла по 60 нс каждый), затем в высоком в течение половины такта (30 нс), и затем снова в низком в течение полутакта (30 нс), после этого описанный выше процесс повторится. После каждого 65536 такта, ШИМ будет компенсироваться, в результате этого выходной сигнал будет немного выше одной четвертой от предельного значения, и на выходе останется сигнал высокого уровня в течение двух полутактов by leaving the output high for two half clocks in four every so often.

Режим 6: Двойной 16 -разрядный Σ-Δ ЦАП с возвращением к нулю (RZ)

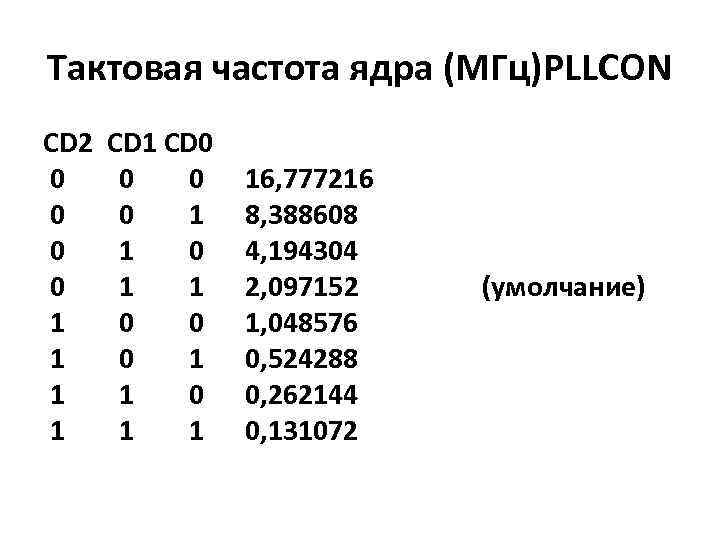

Тактовая частота ядра (МГц)PLLCON CD 2 0 0 1 1 CD 0 0 1 1 0 0 0 1 1 16, 777216 8, 388608 4, 194304 2, 097152 1, 048576 0, 524288 0, 262144 0, 131072 (умолчание)

ЦАП_ADuC.pptx