47bc489ac26363f82202ad0335ac4c5a.ppt

- Количество слайдов: 50

Chapter 6 a IC/Package Co-Design for Power Integrity Prof. Lei He Electrical Engineering Department University of California, Los Angeles URL: eda. ee. ucla. edu Email: lhe@ee. ucla. edu

Chapter 6 a IC/Package Co-Design for Power Integrity Prof. Lei He Electrical Engineering Department University of California, Los Angeles URL: eda. ee. ucla. edu Email: lhe@ee. ucla. edu

Outline p Overview of Chip Package Co-design p IO planning and placement n n p Design constraints Multi-stage solutions Power integrity in package

Outline p Overview of Chip Package Co-design p IO planning and placement n n p Design constraints Multi-stage solutions Power integrity in package

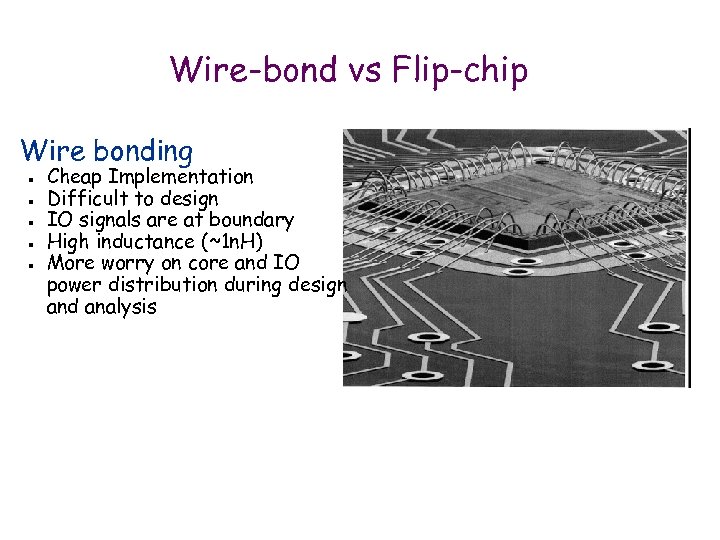

Wire-bond vs Flip-chip Wire bonding n n n Cheap Implementation Difficult to design IO signals are at boundary High inductance (~1 n. H) More worry on core and IO power distribution during design and analysis

Wire-bond vs Flip-chip Wire bonding n n n Cheap Implementation Difficult to design IO signals are at boundary High inductance (~1 n. H) More worry on core and IO power distribution during design and analysis

Wire-bond vs Flip-chip • n n Flip-chip IO cells can be over entire of chip area Low inductance (~0. 1 n. H) High pin count, high cost Less worry on power delivery 4

Wire-bond vs Flip-chip • n n Flip-chip IO cells can be over entire of chip area Low inductance (~0. 1 n. H) High pin count, high cost Less worry on power delivery 4

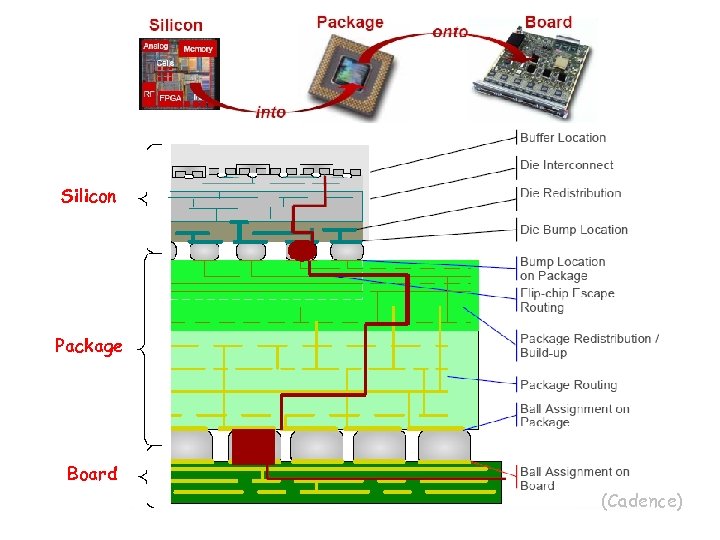

Silicon Package Board (Cadence)

Silicon Package Board (Cadence)

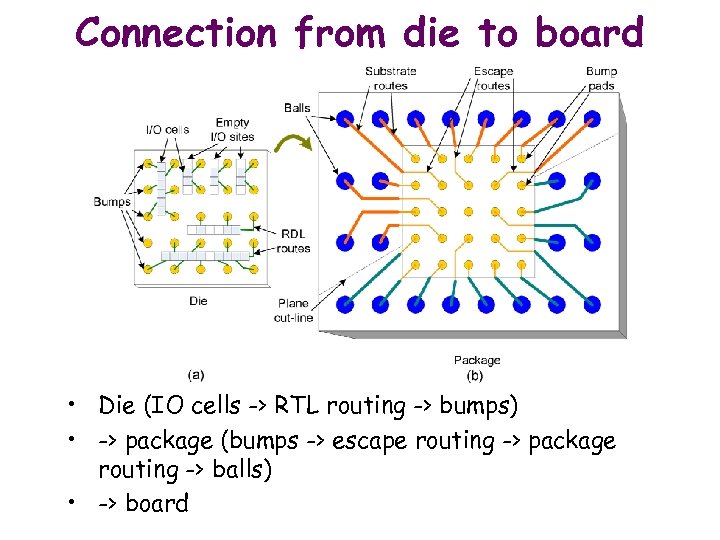

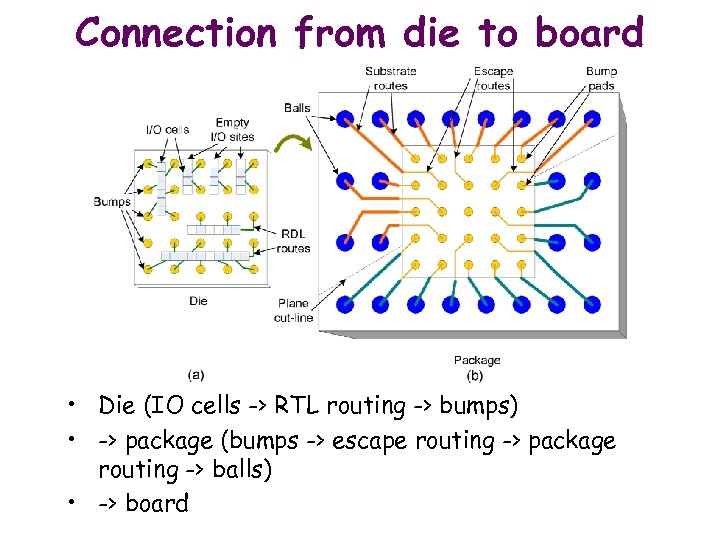

Connection from die to board • Die (IO cells -> RTL routing -> bumps) • -> package (bumps -> escape routing -> package routing -> balls) • -> board

Connection from die to board • Die (IO cells -> RTL routing -> bumps) • -> package (bumps -> escape routing -> package routing -> balls) • -> board

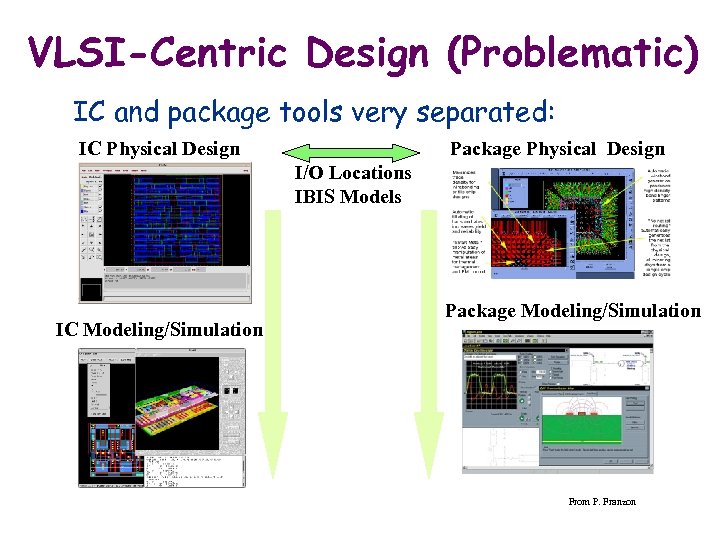

VLSI-Centric Design (Problematic) IC and package tools very separated: IC Physical Design Package Physical Design I/O Locations IBIS Models IC Modeling/Simulation Package Modeling/Simulation (From P. Franzon)

VLSI-Centric Design (Problematic) IC and package tools very separated: IC Physical Design Package Physical Design I/O Locations IBIS Models IC Modeling/Simulation Package Modeling/Simulation (From P. Franzon)

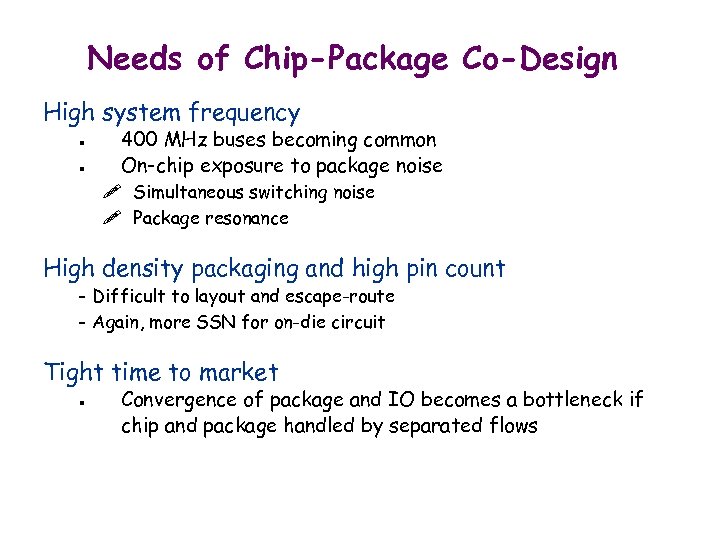

Needs of Chip-Package Co-Design High system frequency n n 400 MHz buses becoming common On-chip exposure to package noise ! Simultaneous switching noise ! Package resonance High density packaging and high pin count Difficult to layout and escape-route – Again, more SSN for on-die circuit – Tight time to market n Convergence of package and IO becomes a bottleneck if chip and package handled by separated flows

Needs of Chip-Package Co-Design High system frequency n n 400 MHz buses becoming common On-chip exposure to package noise ! Simultaneous switching noise ! Package resonance High density packaging and high pin count Difficult to layout and escape-route – Again, more SSN for on-die circuit – Tight time to market n Convergence of package and IO becomes a bottleneck if chip and package handled by separated flows

Keys Problems to Solve Chip and package co-extraction and co-simulation n Difficult to obtain accuracy for sign-off More difficult to achieve efficiency with accuracy or fidelity for planning and design Challenging to handle mutual inductance and large number of ports Co-design focuses on important links between chip and package n n n Chip side: IO buffer design, noise isolation circuitry, P/G network, IO pad macro-placement, RDL estimation, Package side: Package stack-up, P/G plane design, macroplacement of balls and pins, and estimation of escape routing key issues: – IO planning and placement, power delivery system

Keys Problems to Solve Chip and package co-extraction and co-simulation n Difficult to obtain accuracy for sign-off More difficult to achieve efficiency with accuracy or fidelity for planning and design Challenging to handle mutual inductance and large number of ports Co-design focuses on important links between chip and package n n n Chip side: IO buffer design, noise isolation circuitry, P/G network, IO pad macro-placement, RDL estimation, Package side: Package stack-up, P/G plane design, macroplacement of balls and pins, and estimation of escape routing key issues: – IO planning and placement, power delivery system

Outline p Overview of Chip Package Co-design p IO planning and placement n n p Design constraints Multi-stage solutions Power integrity in package

Outline p Overview of Chip Package Co-design p IO planning and placement n n p Design constraints Multi-stage solutions Power integrity in package

Design Constraints for IO Planning and Placement • • Power integrity Timing I/O standards Core and board floorplanning

Design Constraints for IO Planning and Placement • • Power integrity Timing I/O standards Core and board floorplanning

Power Integrity Constraints Power domain constraint • n n I/O cell voltage specification Cells from same domain prefer physically closer Minimize power plane cut lines in the package Provide proper power reference plane for traces Depend on physical locations of I/O cells Proper signal-power-ground (SPG) ratio Primary and secondary P/G driver cells Minimize voltage drop and Ldi/dt noise

Power Integrity Constraints Power domain constraint • n n I/O cell voltage specification Cells from same domain prefer physically closer Minimize power plane cut lines in the package Provide proper power reference plane for traces Depend on physical locations of I/O cells Proper signal-power-ground (SPG) ratio Primary and secondary P/G driver cells Minimize voltage drop and Ldi/dt noise

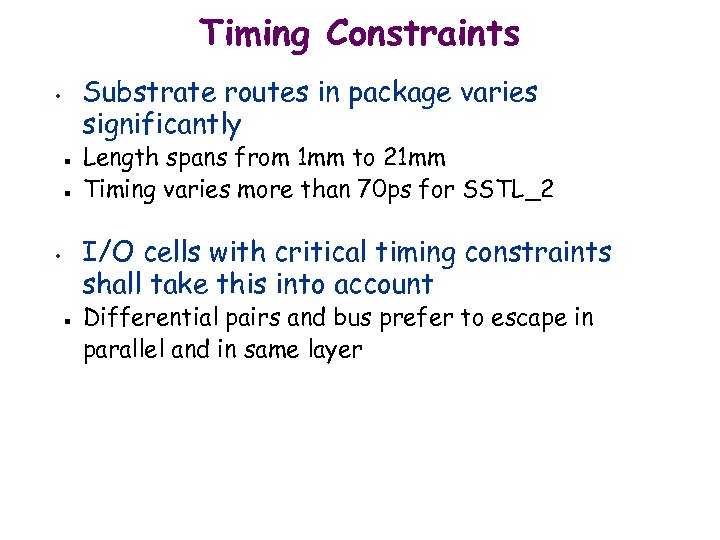

Timing Constraints Substrate routes in package varies significantly • n n Length spans from 1 mm to 21 mm Timing varies more than 70 ps for SSTL_2 I/O cells with critical timing constraints shall take this into account • n Differential pairs and bus prefer to escape in parallel and in same layer

Timing Constraints Substrate routes in package varies significantly • n n Length spans from 1 mm to 21 mm Timing varies more than 70 ps for SSTL_2 I/O cells with critical timing constraints shall take this into account • n Differential pairs and bus prefer to escape in parallel and in same layer

I/O Standard Related Constraints High-speed design high-speed I/O standard requirements • • n n Closeness constraint • n • Relative timing requirements on signals Likely to be connected to the same interface at other chips, so prefer to keep relative order to ease routing Less process variation Bump assignment feasibility constraint

I/O Standard Related Constraints High-speed design high-speed I/O standard requirements • • n n Closeness constraint • n • Relative timing requirements on signals Likely to be connected to the same interface at other chips, so prefer to keep relative order to ease routing Less process variation Bump assignment feasibility constraint

Floorplan Induced Region Constraints Top-down design flow PCB floorplan p Bottom-up design Chip floorplan p I/O cells have region preference Which side? What location? p n n

Floorplan Induced Region Constraints Top-down design flow PCB floorplan p Bottom-up design Chip floorplan p I/O cells have region preference Which side? What location? p n n

Connection from die to board • Die (IO cells -> RTL routing -> bumps) • -> package (bumps -> escape routing -> package routing -> balls) • -> board

Connection from die to board • Die (IO cells -> RTL routing -> bumps) • -> package (bumps -> escape routing -> package routing -> balls) • -> board

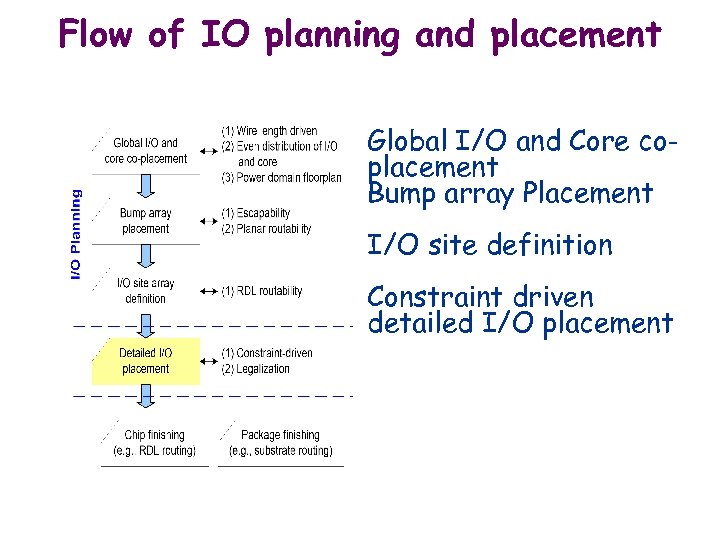

Flow of IO planning and placement Global I/O and Core coplacement Bump array Placement I/O site definition Constraint driven detailed I/O placement

Flow of IO planning and placement Global I/O and Core coplacement Bump array Placement I/O site definition Constraint driven detailed I/O placement

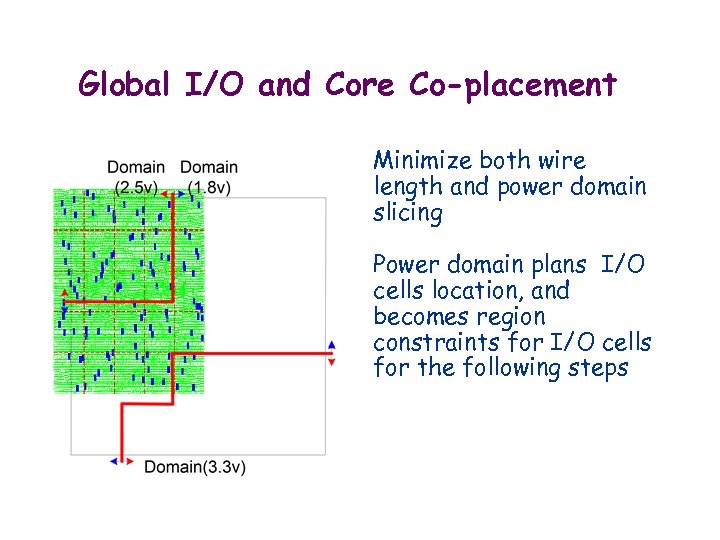

Global I/O and Core Co-placement Minimize both wire length and power domain slicing Power domain plans I/O cells location, and becomes region constraints for I/O cells for the following steps

Global I/O and Core Co-placement Minimize both wire length and power domain slicing Power domain plans I/O cells location, and becomes region constraints for I/O cells for the following steps

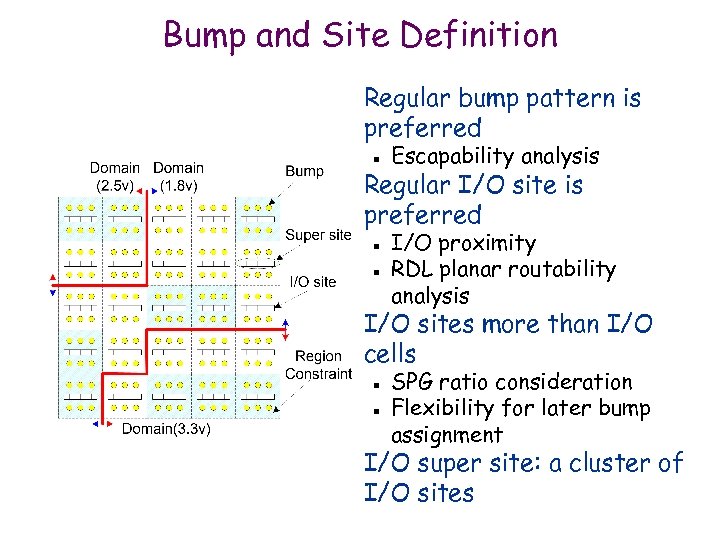

Bump and Site Definition Regular bump pattern is preferred n Escapability analysis Regular I/O site is preferred n n I/O proximity RDL planar routability analysis I/O sites more than I/O cells n n SPG ratio consideration Flexibility for later bump assignment I/O super site: a cluster of I/O sites

Bump and Site Definition Regular bump pattern is preferred n Escapability analysis Regular I/O site is preferred n n I/O proximity RDL planar routability analysis I/O sites more than I/O cells n n SPG ratio consideration Flexibility for later bump assignment I/O super site: a cluster of I/O sites

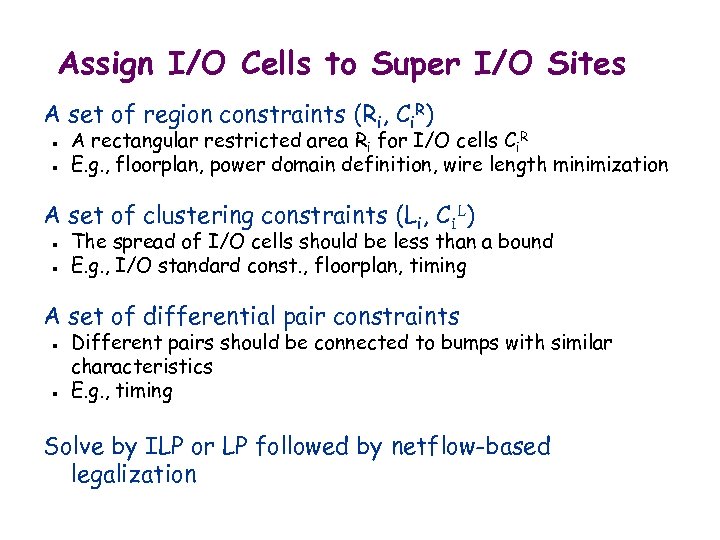

Assign I/O Cells to Super I/O Sites A set of region constraints (Ri, Ci. R) n n A rectangular restricted area Ri for I/O cells Ci. R E. g. , floorplan, power domain definition, wire length minimization A set of clustering constraints (Li, Ci. L) n n The spread of I/O cells should be less than a bound E. g. , I/O standard const. , floorplan, timing A set of differential pair constraints n n Different pairs should be connected to bumps with similar characteristics E. g. , timing Solve by ILP or LP followed by netflow-based legalization

Assign I/O Cells to Super I/O Sites A set of region constraints (Ri, Ci. R) n n A rectangular restricted area Ri for I/O cells Ci. R E. g. , floorplan, power domain definition, wire length minimization A set of clustering constraints (Li, Ci. L) n n The spread of I/O cells should be less than a bound E. g. , I/O standard const. , floorplan, timing A set of differential pair constraints n n Different pairs should be connected to bumps with similar characteristics E. g. , timing Solve by ILP or LP followed by netflow-based legalization

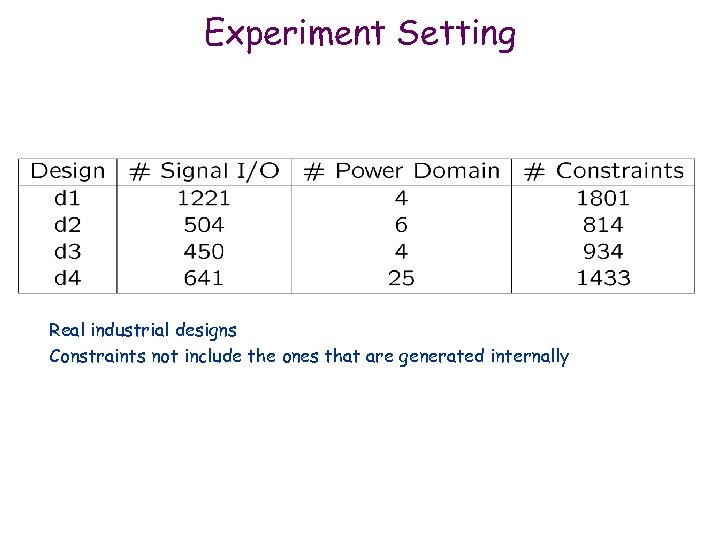

Experiment Setting Real industrial designs Constraints not include the ones that are generated internally

Experiment Setting Real industrial designs Constraints not include the ones that are generated internally

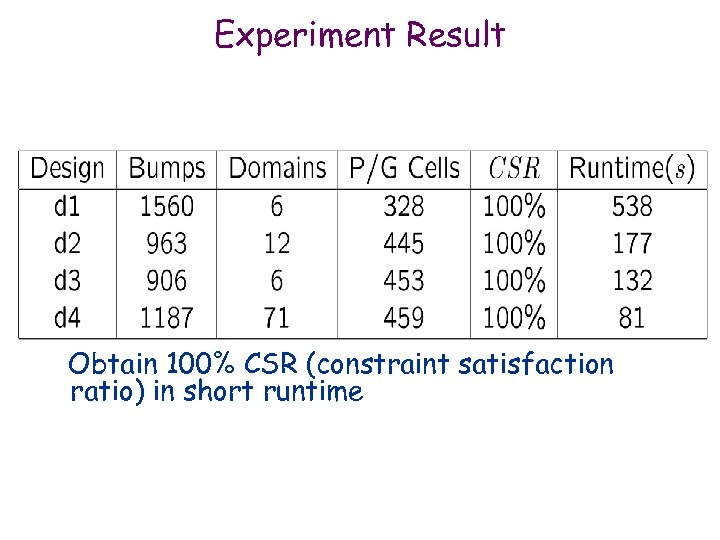

Experiment Result Obtain 100% CSR (constraint satisfaction ratio) in short runtime

Experiment Result Obtain 100% CSR (constraint satisfaction ratio) in short runtime

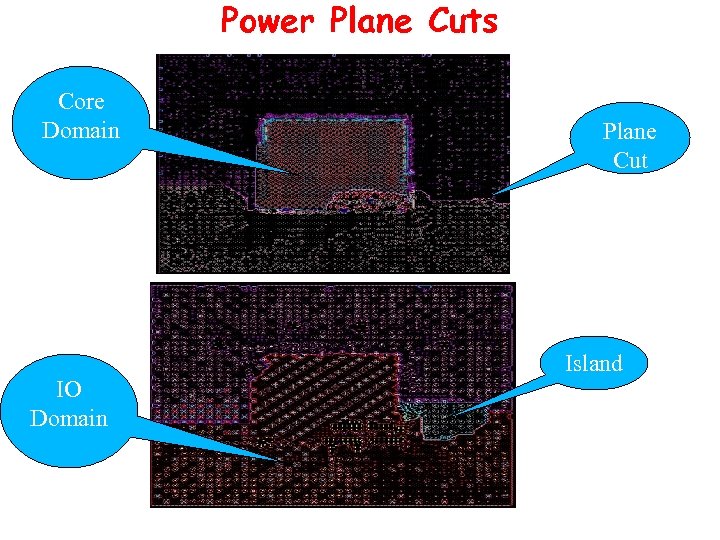

Power Plane Cuts Core Domain Plane Cut Island IO Domain

Power Plane Cuts Core Domain Plane Cut Island IO Domain

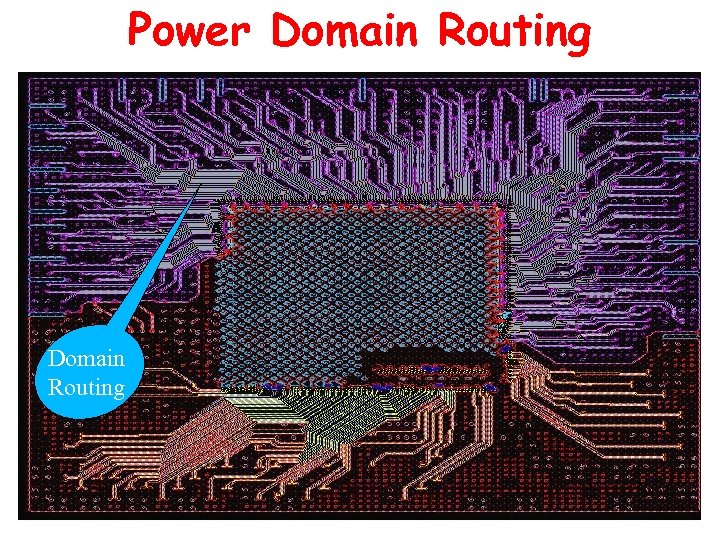

Power Domain Routing

Power Domain Routing

Outline p Chip Package Co-design Flow p IO planning and placement p Power integrity in package n n Overview and modeling Decap insertion Impedance based – Noise-based –

Outline p Chip Package Co-design Flow p IO planning and placement p Power integrity in package n n Overview and modeling Decap insertion Impedance based – Noise-based –

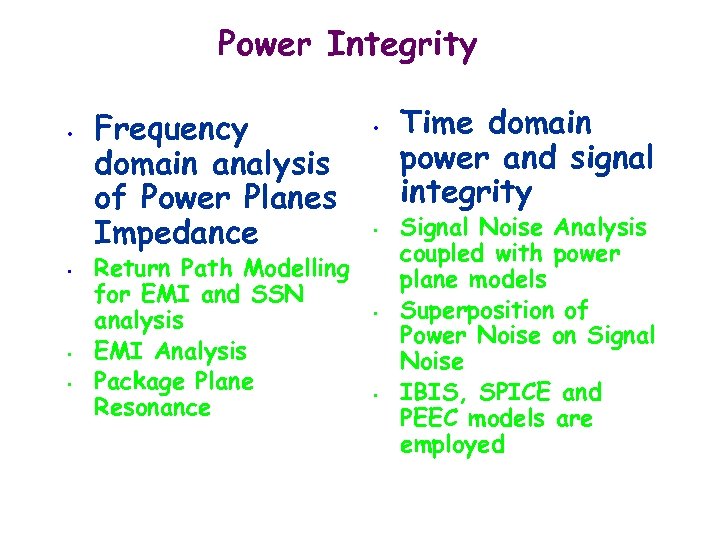

Power Integrity • • Frequency domain analysis of Power Planes Impedance Return Path Modelling for EMI and SSN analysis EMI Analysis Package Plane Resonance • • Time domain power and signal integrity Signal Noise Analysis coupled with power plane models Superposition of Power Noise on Signal Noise IBIS, SPICE and PEEC models are employed

Power Integrity • • Frequency domain analysis of Power Planes Impedance Return Path Modelling for EMI and SSN analysis EMI Analysis Package Plane Resonance • • Time domain power and signal integrity Signal Noise Analysis coupled with power plane models Superposition of Power Noise on Signal Noise IBIS, SPICE and PEEC models are employed

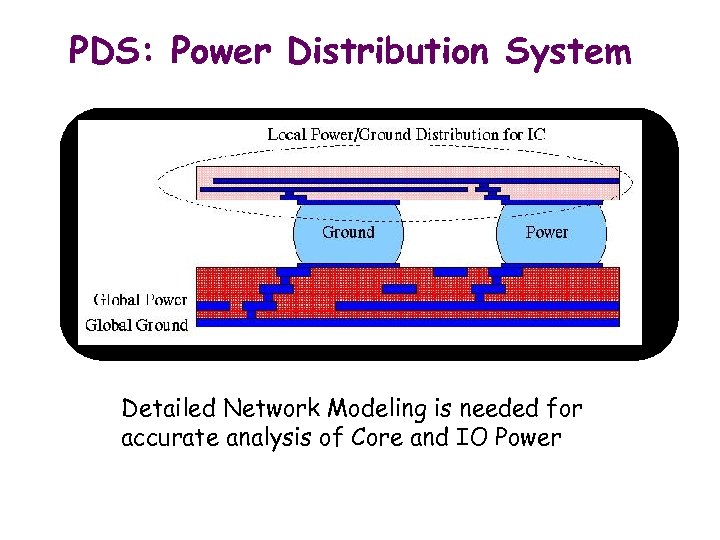

PDS: Power Distribution System Detailed Network Modeling is needed for accurate analysis of Core and IO Power

PDS: Power Distribution System Detailed Network Modeling is needed for accurate analysis of Core and IO Power

Ideal Package Power Planes Early Package Design Exploration ØPlanes have no holes or perforations ØPerfect Microstrip or Stripline Patterns ØImpedance is well conditioned

Ideal Package Power Planes Early Package Design Exploration ØPlanes have no holes or perforations ØPerfect Microstrip or Stripline Patterns ØImpedance is well conditioned

Non-ideal Package Power Planes Detailed Plane Modeling ØPlanes are split for different voltage domains ØPlanes could have any number of holes / perforations ØMicrostrip or Stripline Patterns: imperfect

Non-ideal Package Power Planes Detailed Plane Modeling ØPlanes are split for different voltage domains ØPlanes could have any number of holes / perforations ØMicrostrip or Stripline Patterns: imperfect

PDS Modelling Wire capacitance can be extraction using 2. 5 D model [He-et al, DAC’ 97] • n With extension to arbitrary routing angle Plane capacitance needs to consider impact of wires in between • Inductance is must and can be formula based • n Bonding wires have well controlled shapes • Susceptance (L-1) makes sparsification easier • But sign-off often needs 3 D field solver

PDS Modelling Wire capacitance can be extraction using 2. 5 D model [He-et al, DAC’ 97] • n With extension to arbitrary routing angle Plane capacitance needs to consider impact of wires in between • Inductance is must and can be formula based • n Bonding wires have well controlled shapes • Susceptance (L-1) makes sparsification easier • But sign-off often needs 3 D field solver

PDS Design Assign power planes in package stackup Assign power domains: V 18, V 25, Vanalog, … Decide via stapling • • • Improve power delivery Reduce current loop and eliminate noise Assign P/G balls

PDS Design Assign power planes in package stackup Assign power domains: V 18, V 25, Vanalog, … Decide via stapling • • • Improve power delivery Reduce current loop and eliminate noise Assign P/G balls

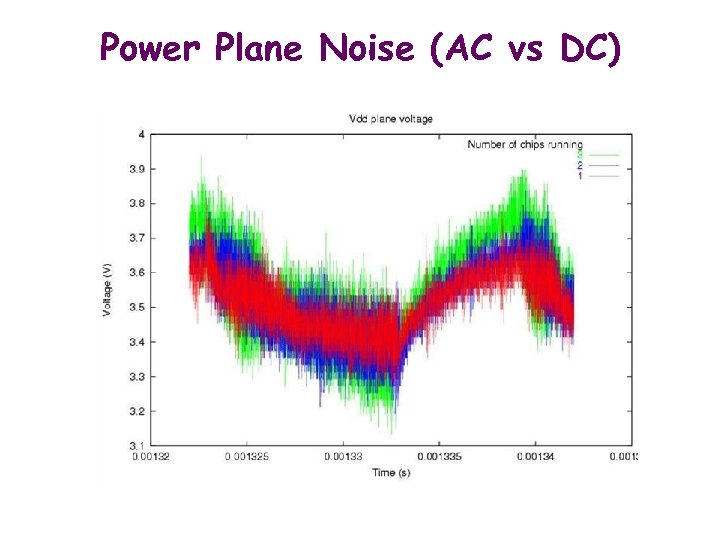

PDS Concerns DC Concerns • Ø On-Chip IR Drop Ø Not Ø a big concern in Flip-chip Designs In-Package IR Drop Ø Important Ø but still very small In-PCB IR Drop Ø Can be ignored AC Concerns • Ø Ø Ø Low impedance Network across a broad frequency spectrum Reduce inductive effective to reduce SSN Control Chip/Package resonance

PDS Concerns DC Concerns • Ø On-Chip IR Drop Ø Not Ø a big concern in Flip-chip Designs In-Package IR Drop Ø Important Ø but still very small In-PCB IR Drop Ø Can be ignored AC Concerns • Ø Ø Ø Low impedance Network across a broad frequency spectrum Reduce inductive effective to reduce SSN Control Chip/Package resonance

Power Plane Noise (AC vs DC)

Power Plane Noise (AC vs DC)

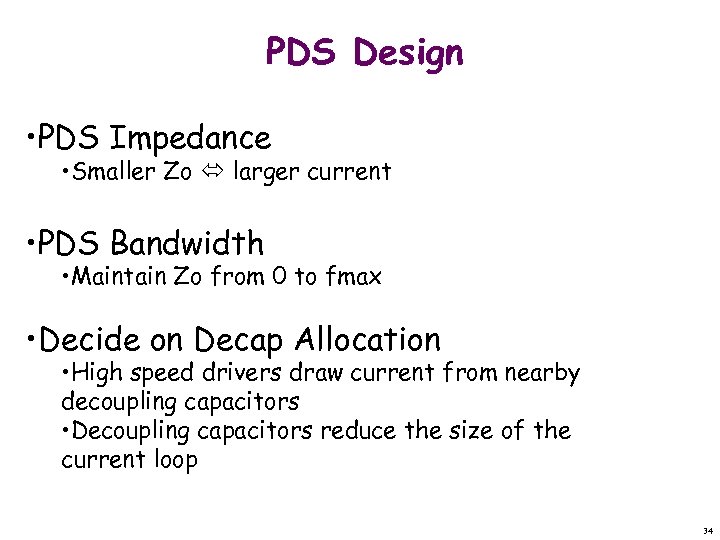

PDS Design • PDS Impedance • Smaller Zo larger current • PDS Bandwidth • Maintain Zo from 0 to fmax • Decide on Decap Allocation • High speed drivers draw current from nearby decoupling capacitors • Decoupling capacitors reduce the size of the current loop 34

PDS Design • PDS Impedance • Smaller Zo larger current • PDS Bandwidth • Maintain Zo from 0 to fmax • Decide on Decap Allocation • High speed drivers draw current from nearby decoupling capacitors • Decoupling capacitors reduce the size of the current loop 34

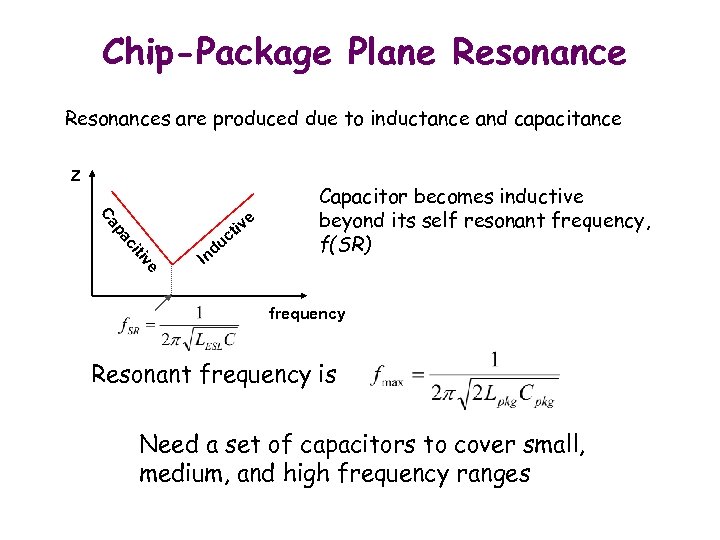

Chip-Package Plane Resonances are produced due to inductance and capacitance Z e tiv ci pa Ca e iv ct u nd I Capacitor becomes inductive beyond its self resonant frequency, f(SR) frequency Resonant frequency is Need a set of capacitors to cover small, medium, and high frequency ranges

Chip-Package Plane Resonances are produced due to inductance and capacitance Z e tiv ci pa Ca e iv ct u nd I Capacitor becomes inductive beyond its self resonant frequency, f(SR) frequency Resonant frequency is Need a set of capacitors to cover small, medium, and high frequency ranges

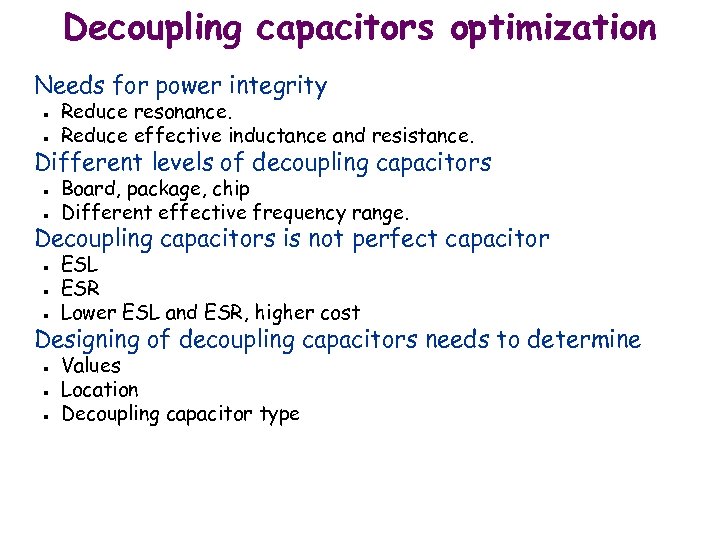

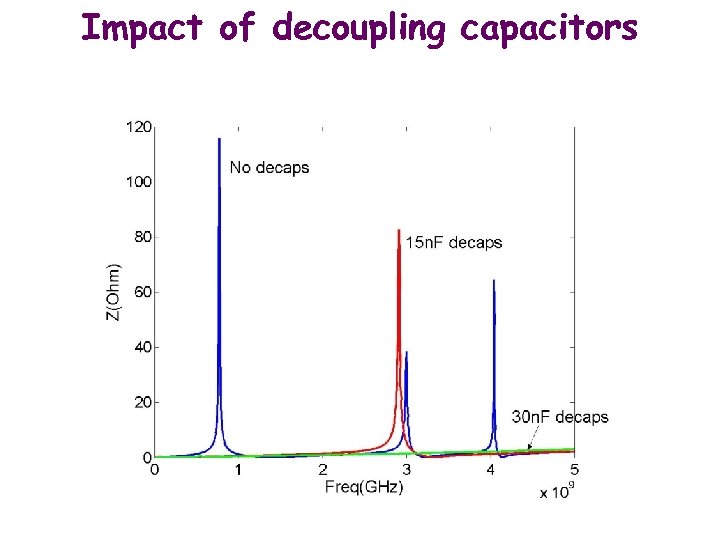

Decoupling capacitors optimization Needs for power integrity n n Reduce resonance. Reduce effective inductance and resistance. Different levels of decoupling capacitors n n Board, package, chip Different effective frequency range. Decoupling capacitors is not perfect capacitor n n n ESL ESR Lower ESL and ESR, higher cost Designing of decoupling capacitors needs to determine n n n Values Location Decoupling capacitor type

Decoupling capacitors optimization Needs for power integrity n n Reduce resonance. Reduce effective inductance and resistance. Different levels of decoupling capacitors n n Board, package, chip Different effective frequency range. Decoupling capacitors is not perfect capacitor n n n ESL ESR Lower ESL and ESR, higher cost Designing of decoupling capacitors needs to determine n n n Values Location Decoupling capacitor type

Impact of decoupling capacitors

Impact of decoupling capacitors

![Existing Solutions Manual trial-and-error approaches n n [Chen et al. , ECTC ’ 96] Existing Solutions Manual trial-and-error approaches n n [Chen et al. , ECTC ’ 96]](https://present5.com/presentation/47bc489ac26363f82202ad0335ac4c5a/image-38.jpg) Existing Solutions Manual trial-and-error approaches n n [Chen et al. , ECTC ’ 96] [Yang et al. , EPEP 2002] Automatic optimization n [Kamo et al. , EPEP 2000], [Hattori et al. , EPEP 2002] – – n n Ignore ESL and ESR. Use impedance as noise metric – Noise driven decap insertion [Zheng et al. , CICC 2003] [Chen et al. , ISPD 2006]

Existing Solutions Manual trial-and-error approaches n n [Chen et al. , ECTC ’ 96] [Yang et al. , EPEP 2002] Automatic optimization n [Kamo et al. , EPEP 2000], [Hattori et al. , EPEP 2002] – – n n Ignore ESL and ESR. Use impedance as noise metric – Noise driven decap insertion [Zheng et al. , CICC 2003] [Chen et al. , ISPD 2006]

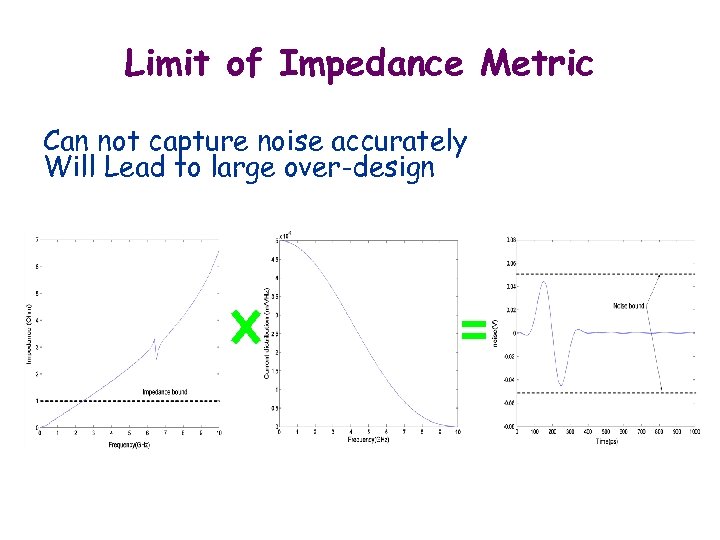

Limit of Impedance Metric Can not capture noise accurately Will Lead to large over-design

Limit of Impedance Metric Can not capture noise accurately Will Lead to large over-design

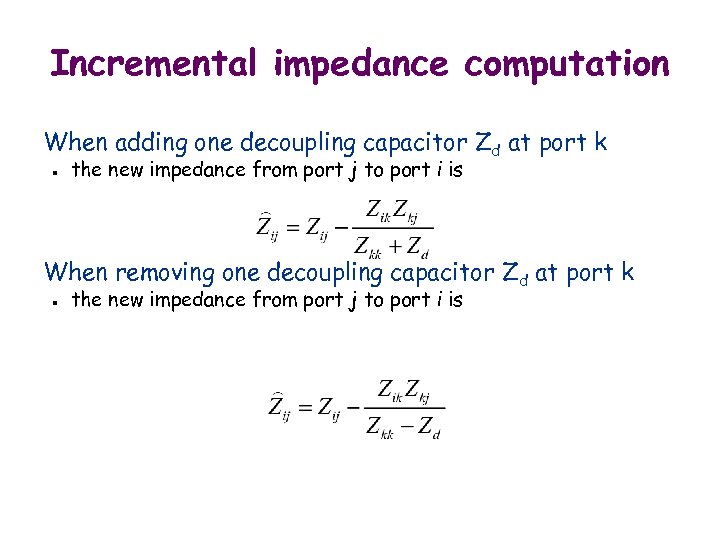

Incremental impedance computation When adding one decoupling capacitor Zd at port k n the new impedance from port j to port i is When removing one decoupling capacitor Zd at port k n the new impedance from port j to port i is

Incremental impedance computation When adding one decoupling capacitor Zd at port k n the new impedance from port j to port i is When removing one decoupling capacitor Zd at port k n the new impedance from port j to port i is

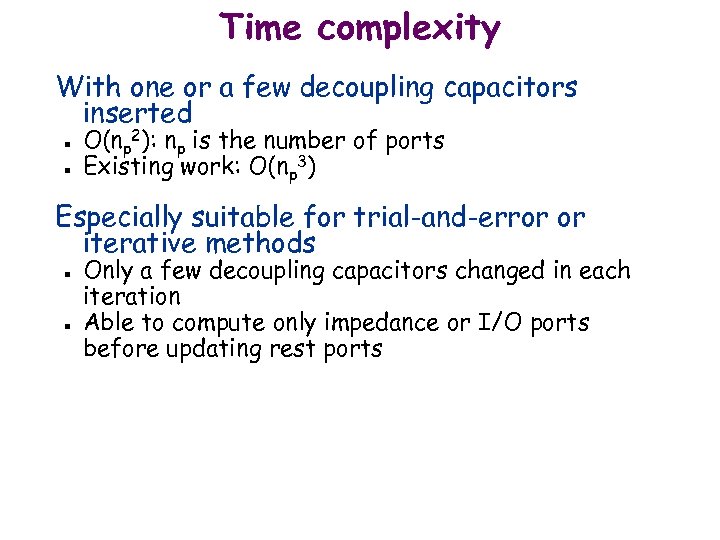

Time complexity With one or a few decoupling capacitors inserted n n O(np 2): np is the number of ports Existing work: O(np 3) Especially suitable for trial-and-error or iterative methods n n Only a few decoupling capacitors changed in each iteration Able to compute only impedance or I/O ports before updating rest ports

Time complexity With one or a few decoupling capacitors inserted n n O(np 2): np is the number of ports Existing work: O(np 3) Especially suitable for trial-and-error or iterative methods n n Only a few decoupling capacitors changed in each iteration Able to compute only impedance or I/O ports before updating rest ports

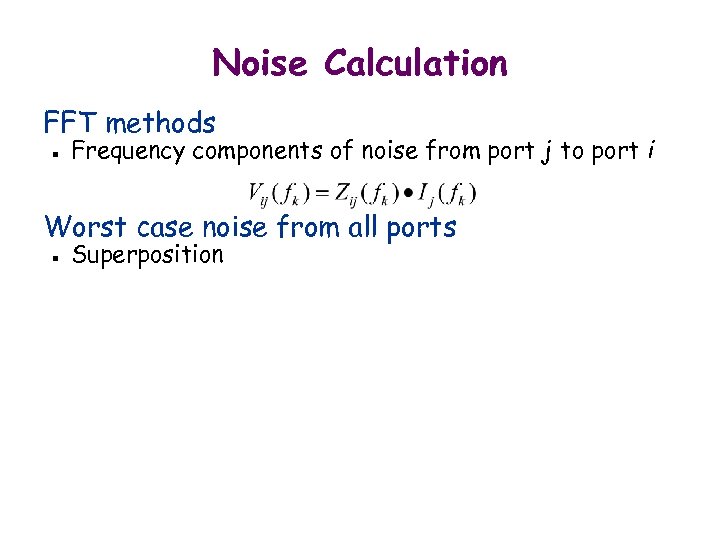

Noise Calculation FFT methods n Frequency components of noise from port j to port i Worst case noise from all ports n Superposition

Noise Calculation FFT methods n Frequency components of noise from port j to port i Worst case noise from all ports n Superposition

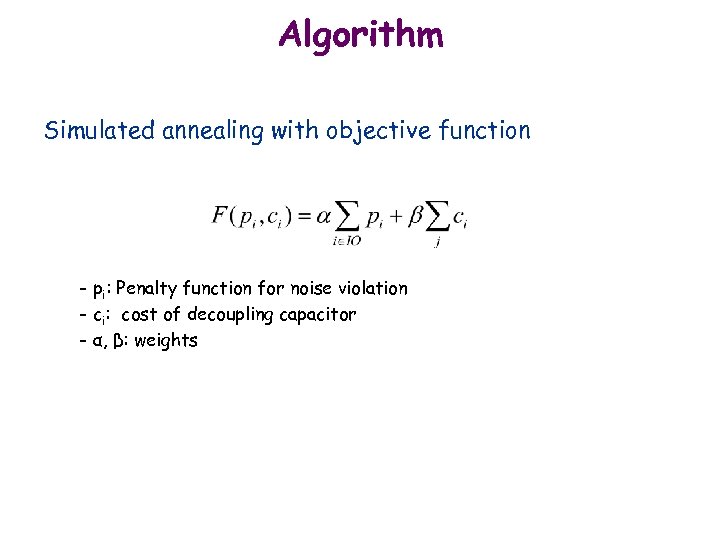

Algorithm Simulated annealing with objective function pi: Penalty function for noise violation – ci: cost of decoupling capacitor – α, β: weights –

Algorithm Simulated annealing with objective function pi: Penalty function for noise violation – ci: cost of decoupling capacitor – α, β: weights –

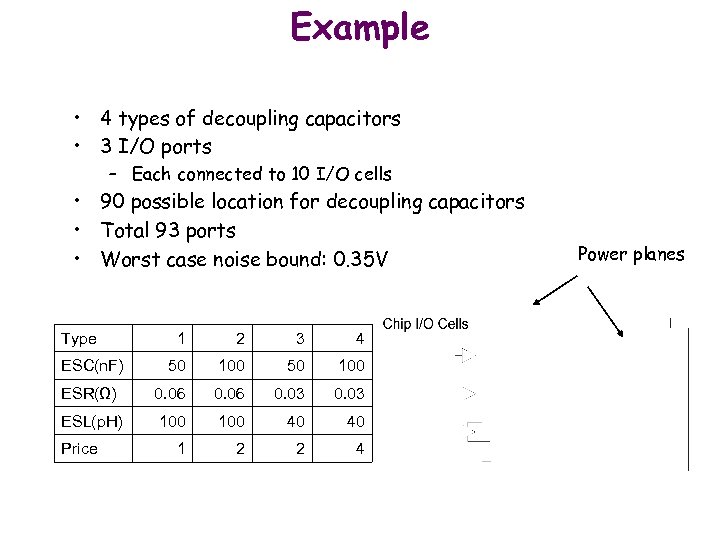

Example • 4 types of decoupling capacitors • 3 I/O ports – Each connected to 10 I/O cells • 90 possible location for decoupling capacitors • Total 93 ports • Worst case noise bound: 0. 35 V Type 1 2 3 4 50 100 ESR(Ω) 0. 06 0. 03 ESL(p. H) 100 40 40 1 2 2 4 ESC(n. F) Price Power planes

Example • 4 types of decoupling capacitors • 3 I/O ports – Each connected to 10 I/O cells • 90 possible location for decoupling capacitors • Total 93 ports • Worst case noise bound: 0. 35 V Type 1 2 3 4 50 100 ESR(Ω) 0. 06 0. 03 ESL(p. H) 100 40 40 1 2 2 4 ESC(n. F) Price Power planes

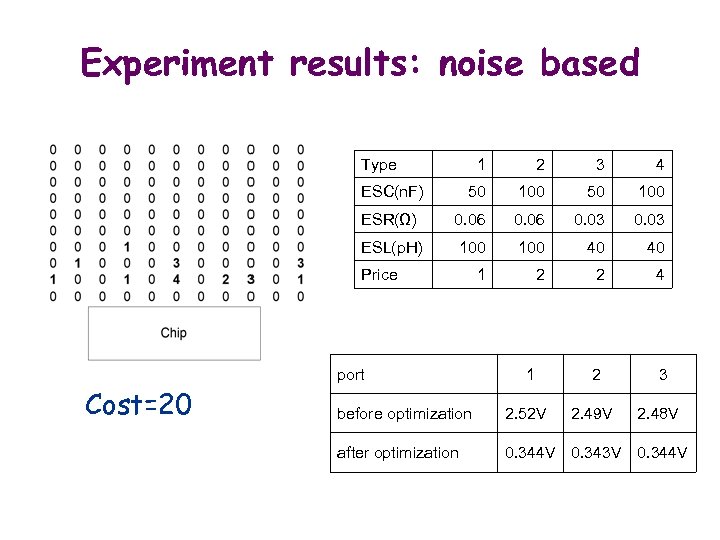

Experiment results: noise based Type 1 2 3 4 50 100 ESR(Ω) 0. 06 0. 03 ESL(p. H) 100 40 40 1 2 2 4 2 3 ESC(n. F) Price port Cost=20 1 before optimization 2. 52 V 2. 49 V 2. 48 V after optimization 0. 344 V 0. 343 V 0. 344 V

Experiment results: noise based Type 1 2 3 4 50 100 ESR(Ω) 0. 06 0. 03 ESL(p. H) 100 40 40 1 2 2 4 2 3 ESC(n. F) Price port Cost=20 1 before optimization 2. 52 V 2. 49 V 2. 48 V after optimization 0. 344 V 0. 343 V 0. 344 V

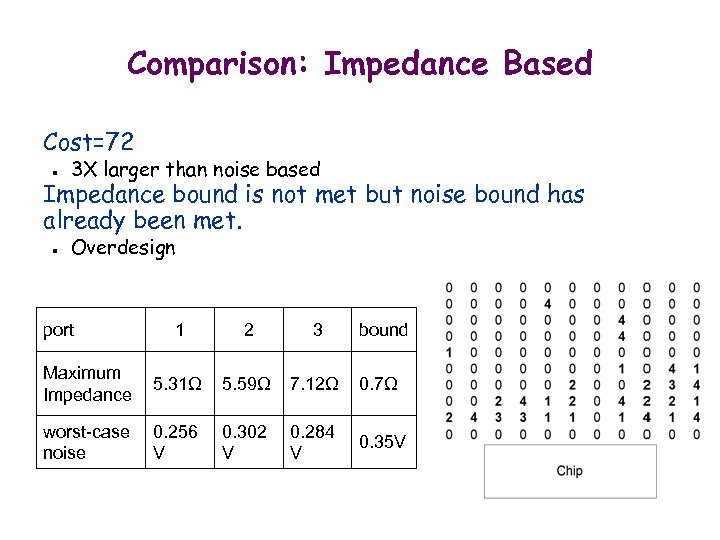

Comparison: Impedance Based Cost=72 n 3 X larger than noise based Impedance bound is not met but noise bound has already been met. n Overdesign port 1 2 3 bound Maximum Impedance 5. 31Ω 5. 59Ω 7. 12Ω 0. 7Ω worst-case noise 0. 256 V 0. 302 V 0. 284 V 0. 35 V

Comparison: Impedance Based Cost=72 n 3 X larger than noise based Impedance bound is not met but noise bound has already been met. n Overdesign port 1 2 3 bound Maximum Impedance 5. 31Ω 5. 59Ω 7. 12Ω 0. 7Ω worst-case noise 0. 256 V 0. 302 V 0. 284 V 0. 35 V

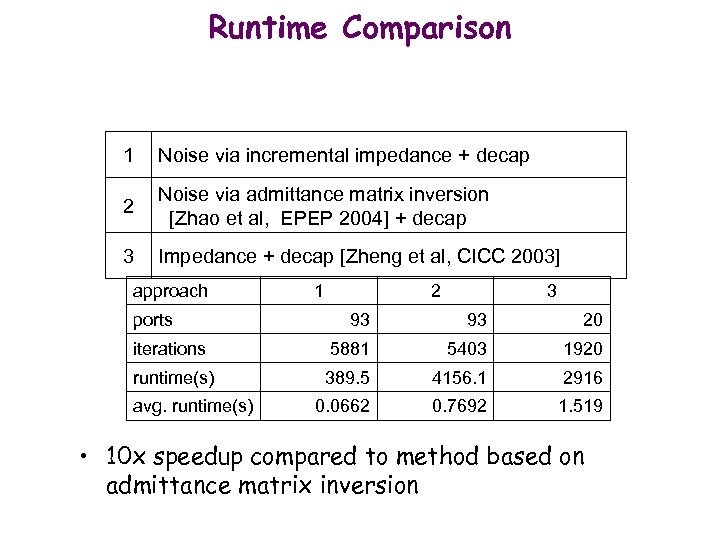

Runtime Comparison 1 Noise via incremental impedance + decap 2 Noise via admittance matrix inversion [Zhao et al, EPEP 2004] + decap 3 Impedance + decap [Zheng et al, CICC 2003] approach ports 1 2 3 93 93 20 iterations 5881 5403 1920 runtime(s) 389. 5 4156. 1 2916 0. 0662 0. 7692 1. 519 avg. runtime(s) • 10 x speedup compared to method based on admittance matrix inversion

Runtime Comparison 1 Noise via incremental impedance + decap 2 Noise via admittance matrix inversion [Zhao et al, EPEP 2004] + decap 3 Impedance + decap [Zheng et al, CICC 2003] approach ports 1 2 3 93 93 20 iterations 5881 5403 1920 runtime(s) 389. 5 4156. 1 2916 0. 0662 0. 7692 1. 519 avg. runtime(s) • 10 x speedup compared to method based on admittance matrix inversion

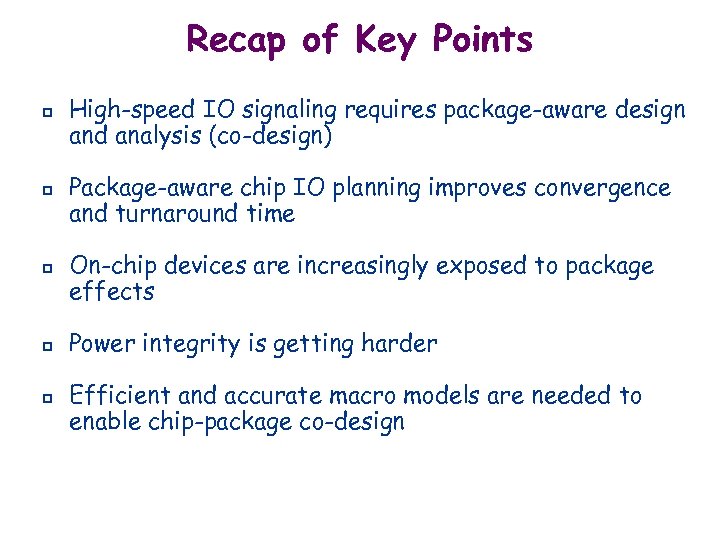

Recap of Key Points p p p High-speed IO signaling requires package-aware design and analysis (co-design) Package-aware chip IO planning improves convergence and turnaround time On-chip devices are increasingly exposed to package effects Power integrity is getting harder Efficient and accurate macro models are needed to enable chip-package co-design

Recap of Key Points p p p High-speed IO signaling requires package-aware design and analysis (co-design) Package-aware chip IO planning improves convergence and turnaround time On-chip devices are increasingly exposed to package effects Power integrity is getting harder Efficient and accurate macro models are needed to enable chip-package co-design

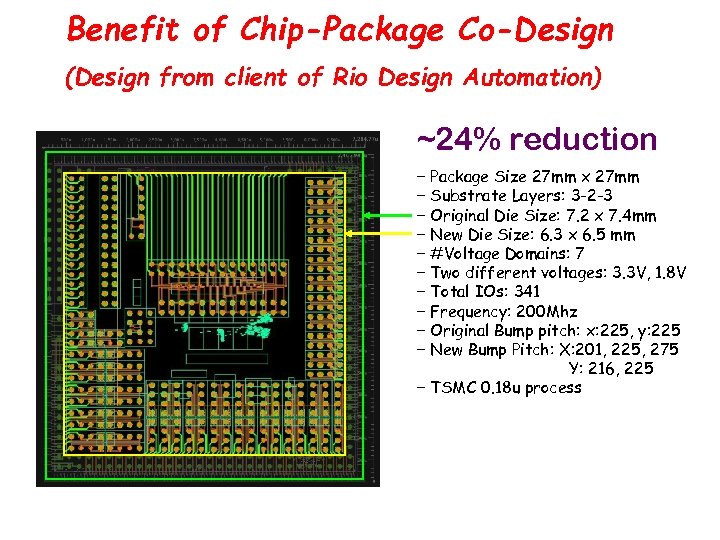

Benefit of Chip-Package Co-Design (Design from client of Rio Design Automation) ~24% reduction − Package Size 27 mm x 27 mm − Substrate Layers: 3 -2 -3 − Original Die Size: 7. 2 x 7. 4 mm − New Die Size: 6. 3 x 6. 5 mm − #Voltage Domains: 7 − Two different voltages: 3. 3 V, 1. 8 V − Total IOs: 341 − Frequency: 200 Mhz − Original Bump pitch: x: 225, y: 225 − New Bump Pitch: X: 201, 225, 275 Y: 216, 225 − TSMC 0. 18 u process

Benefit of Chip-Package Co-Design (Design from client of Rio Design Automation) ~24% reduction − Package Size 27 mm x 27 mm − Substrate Layers: 3 -2 -3 − Original Die Size: 7. 2 x 7. 4 mm − New Die Size: 6. 3 x 6. 5 mm − #Voltage Domains: 7 − Two different voltages: 3. 3 V, 1. 8 V − Total IOs: 341 − Frequency: 200 Mhz − Original Bump pitch: x: 225, y: 225 − New Bump Pitch: X: 201, 225, 275 Y: 216, 225 − TSMC 0. 18 u process

References p p Jinjun Xiong, YC Wong, Egino Sarto, Lei He, "Constraint Driven I/O Planning and Placement for Chip-package Codesign, " IEEE/ACM Asia and South Pacific Design Automation Conference , 2006. Jun Chen, Lei He, "Noise-Driven In-Package Decoupling Capacitance Insertion, " IEEE/ACM International Symposium on Physical Design , 2006.

References p p Jinjun Xiong, YC Wong, Egino Sarto, Lei He, "Constraint Driven I/O Planning and Placement for Chip-package Codesign, " IEEE/ACM Asia and South Pacific Design Automation Conference , 2006. Jun Chen, Lei He, "Noise-Driven In-Package Decoupling Capacitance Insertion, " IEEE/ACM International Symposium on Physical Design , 2006.