55651804f3dadd11ffb8830aedcbe231.ppt

- Количество слайдов: 99

Chapter 10 Differential Amplifiers Ø Ø Ø 10. 1 10. 2 10. 3 10. 4 10. 5 10. 6 General Considerations Bipolar Differential Pair MOS Differential Pair Cascode Differential Amplifiers Common-Mode Rejection Differential Pair with Active Load 1

Chapter 10 Differential Amplifiers Ø Ø Ø 10. 1 10. 2 10. 3 10. 4 10. 5 10. 6 General Considerations Bipolar Differential Pair MOS Differential Pair Cascode Differential Amplifiers Common-Mode Rejection Differential Pair with Active Load 1

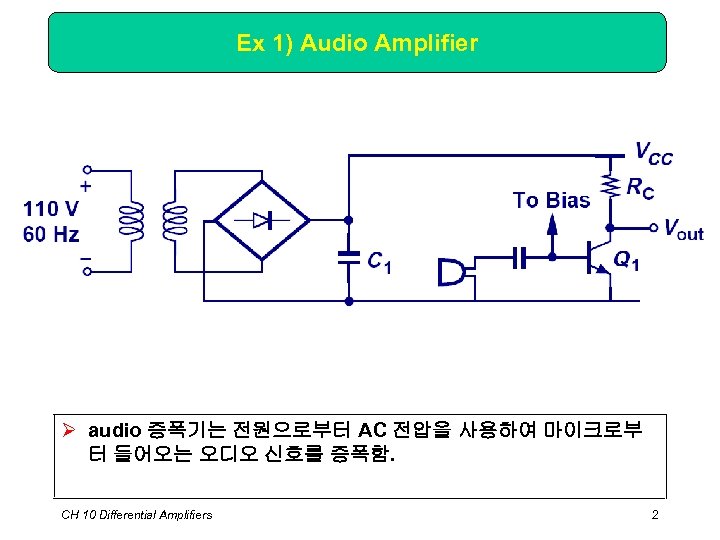

Ex 1) Audio Amplifier Ø audio 증폭기는 전원으로부터 AC 전압을 사용하여 마이크로부 터 들어오는 오디오 신호를 증폭함. CH 10 Differential Amplifiers 2

Ex 1) Audio Amplifier Ø audio 증폭기는 전원으로부터 AC 전압을 사용하여 마이크로부 터 들어오는 오디오 신호를 증폭함. CH 10 Differential Amplifiers 2

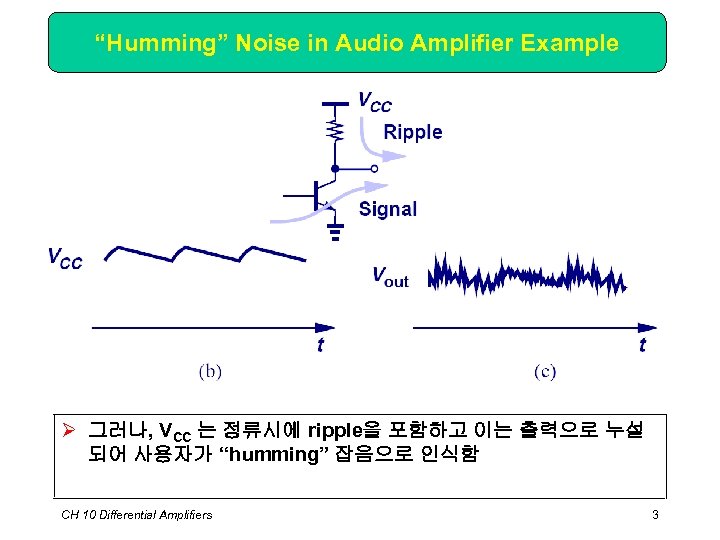

“Humming” Noise in Audio Amplifier Example Ø 그러나, VCC 는 정류시에 ripple을 포함하고 이는 출력으로 누설 되어 사용자가 “humming” 잡음으로 인식함 CH 10 Differential Amplifiers 3

“Humming” Noise in Audio Amplifier Example Ø 그러나, VCC 는 정류시에 ripple을 포함하고 이는 출력으로 누설 되어 사용자가 “humming” 잡음으로 인식함 CH 10 Differential Amplifiers 3

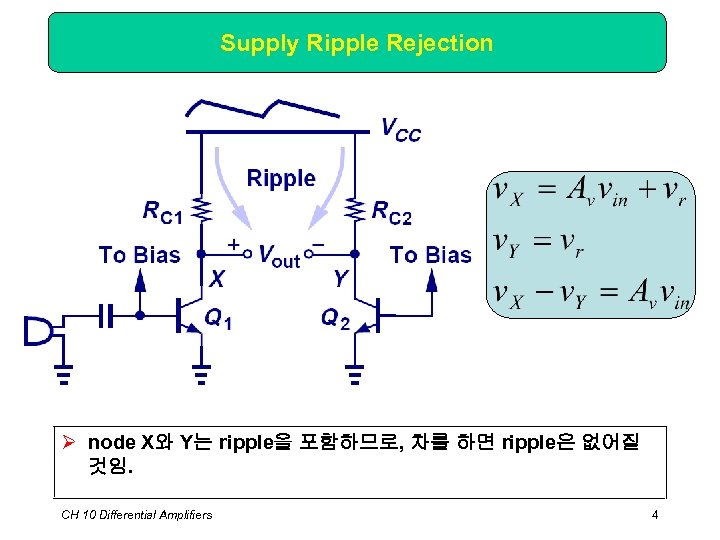

Supply Ripple Rejection Ø node X와 Y는 ripple을 포함하므로, 차를 하면 ripple은 없어질 것임. CH 10 Differential Amplifiers 4

Supply Ripple Rejection Ø node X와 Y는 ripple을 포함하므로, 차를 하면 ripple은 없어질 것임. CH 10 Differential Amplifiers 4

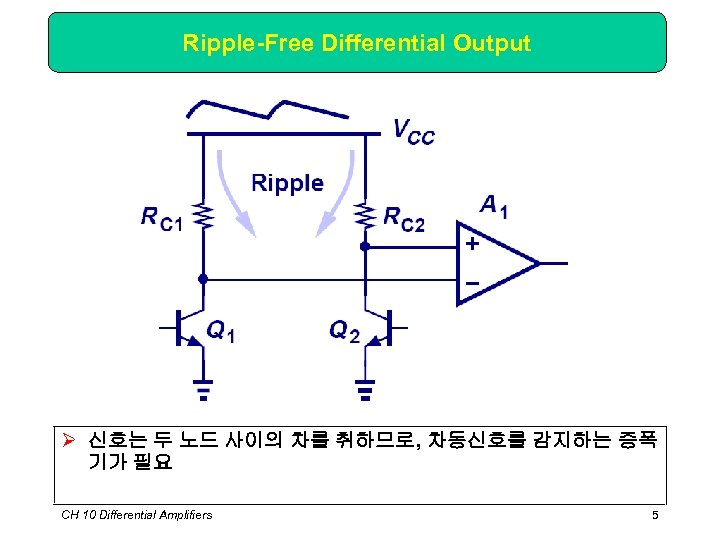

Ripple-Free Differential Output Ø 신호는 두 노드 사이의 차를 취하므로, 차동신호를 감지하는 증폭 기가 필요 CH 10 Differential Amplifiers 5

Ripple-Free Differential Output Ø 신호는 두 노드 사이의 차를 취하므로, 차동신호를 감지하는 증폭 기가 필요 CH 10 Differential Amplifiers 5

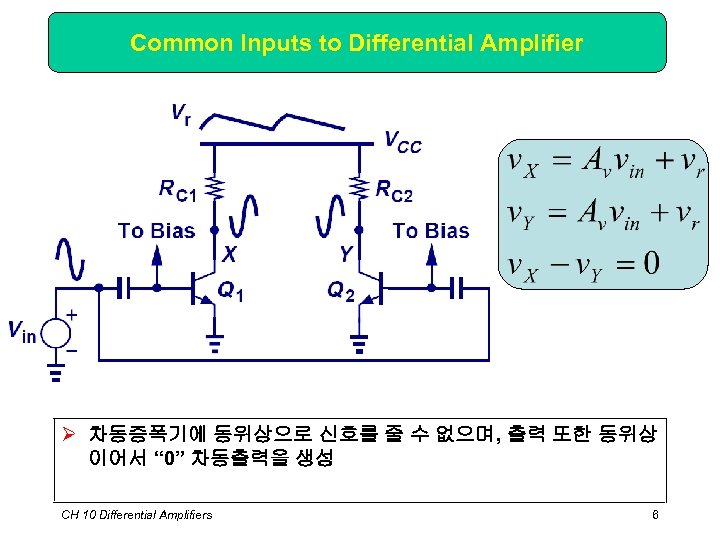

Common Inputs to Differential Amplifier Ø 차동증폭기에 동위상으로 신호를 줄 수 없으며, 출력 또한 동위상 이어서 “ 0” 차동출력을 생성 CH 10 Differential Amplifiers 6

Common Inputs to Differential Amplifier Ø 차동증폭기에 동위상으로 신호를 줄 수 없으며, 출력 또한 동위상 이어서 “ 0” 차동출력을 생성 CH 10 Differential Amplifiers 6

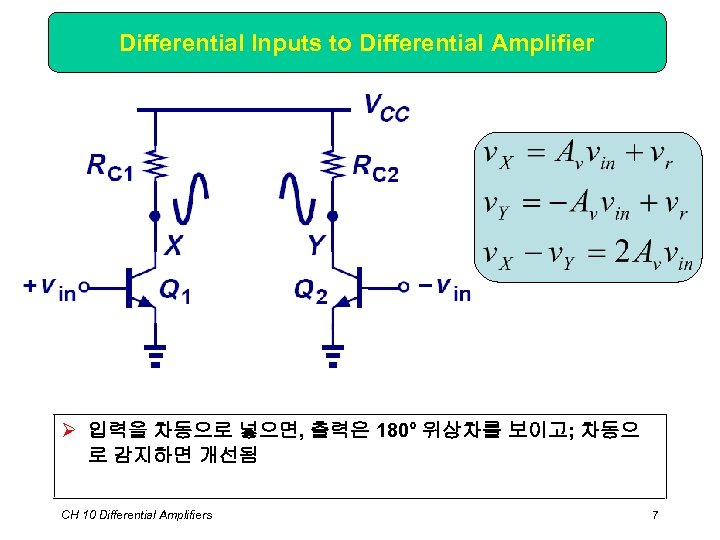

Differential Inputs to Differential Amplifier Ø 입력을 차동으로 넣으면, 출력은 180° 위상차를 보이고; 차동으 로 감지하면 개선됨 CH 10 Differential Amplifiers 7

Differential Inputs to Differential Amplifier Ø 입력을 차동으로 넣으면, 출력은 180° 위상차를 보이고; 차동으 로 감지하면 개선됨 CH 10 Differential Amplifiers 7

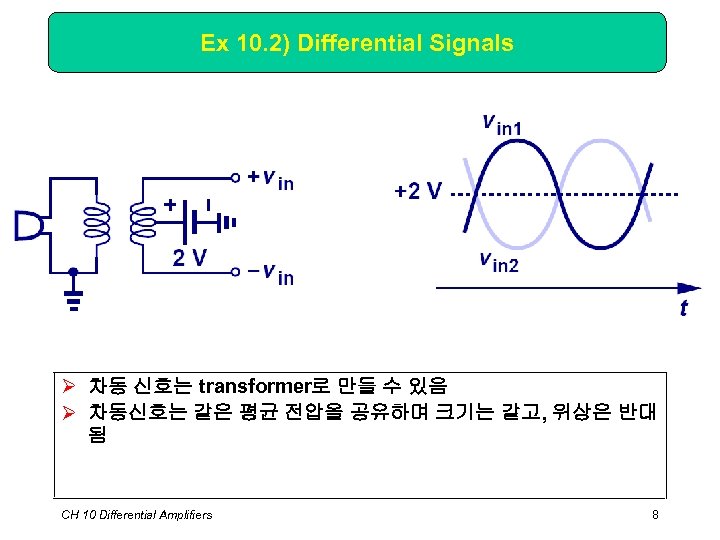

Ex 10. 2) Differential Signals Ø 차동 신호는 transformer로 만들 수 있음 Ø 차동신호는 같은 평균 전압을 공유하며 크기는 같고, 위상은 반대 됨 CH 10 Differential Amplifiers 8

Ex 10. 2) Differential Signals Ø 차동 신호는 transformer로 만들 수 있음 Ø 차동신호는 같은 평균 전압을 공유하며 크기는 같고, 위상은 반대 됨 CH 10 Differential Amplifiers 8

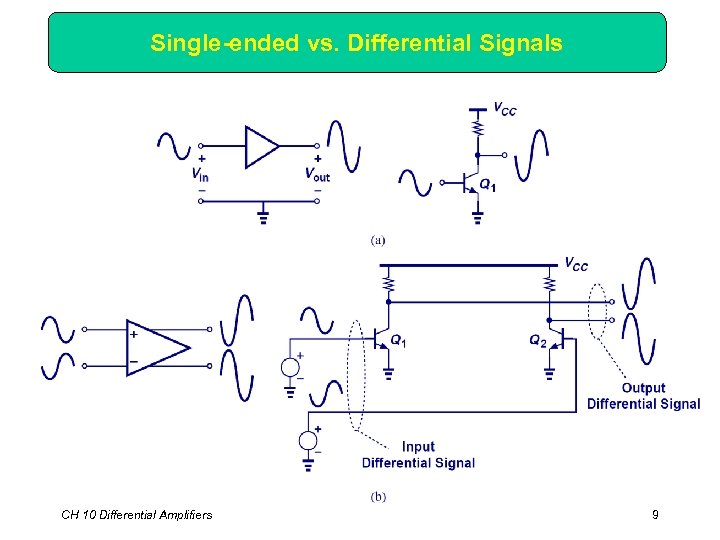

Single-ended vs. Differential Signals CH 10 Differential Amplifiers 9

Single-ended vs. Differential Signals CH 10 Differential Amplifiers 9

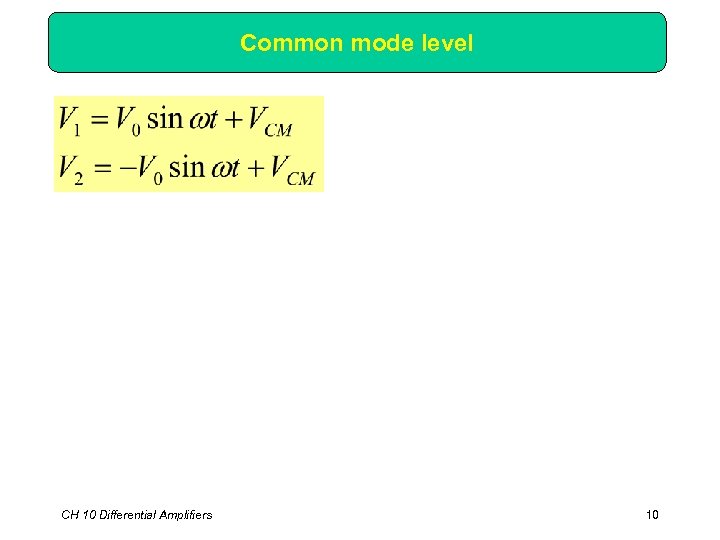

Common mode level CH 10 Differential Amplifiers 10

Common mode level CH 10 Differential Amplifiers 10

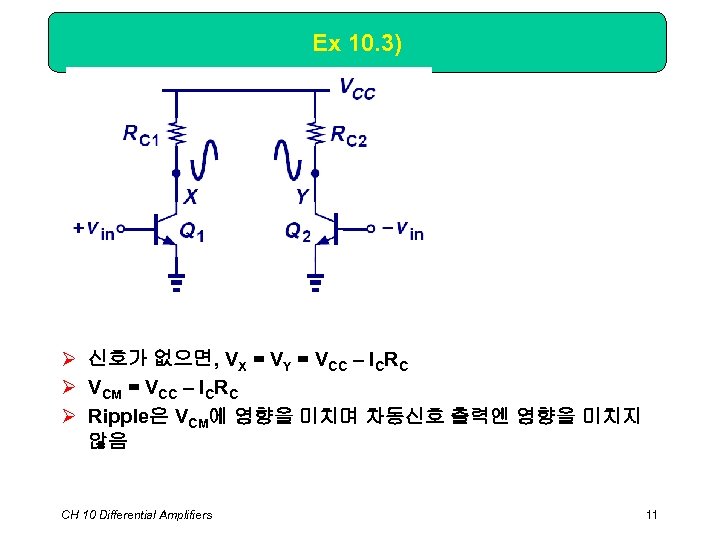

Ex 10. 3) Ø 신호가 없으면, VX = VY = VCC – ICRC Ø VCM = VCC – ICRC Ø Ripple은 VCM에 영향을 미치며 차동신호 출력엔 영향을 미치지 않음 CH 10 Differential Amplifiers 11

Ex 10. 3) Ø 신호가 없으면, VX = VY = VCC – ICRC Ø VCM = VCC – ICRC Ø Ripple은 VCM에 영향을 미치며 차동신호 출력엔 영향을 미치지 않음 CH 10 Differential Amplifiers 11

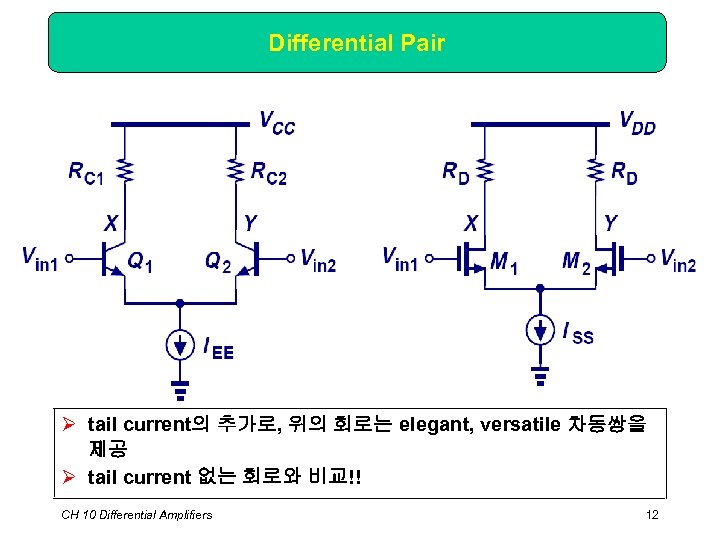

Differential Pair Ø tail current의 추가로, 위의 회로는 elegant, versatile 차동쌍을 제공 Ø tail current 없는 회로와 비교!! CH 10 Differential Amplifiers 12

Differential Pair Ø tail current의 추가로, 위의 회로는 elegant, versatile 차동쌍을 제공 Ø tail current 없는 회로와 비교!! CH 10 Differential Amplifiers 12

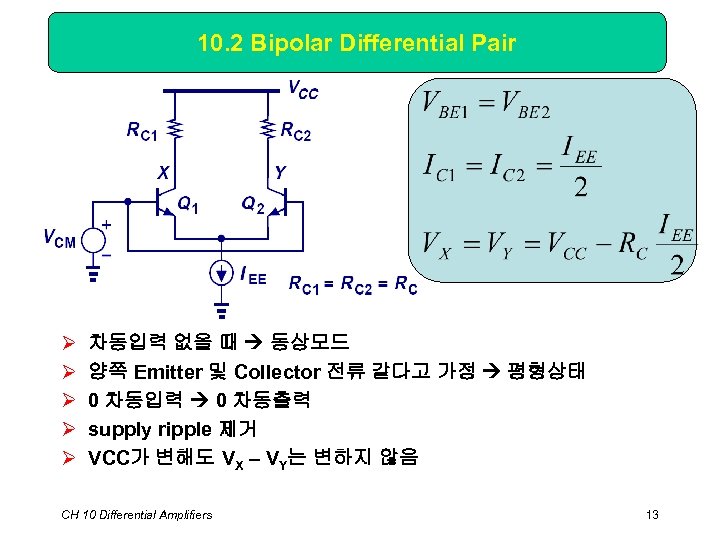

10. 2 Bipolar Differential Pair Ø Ø Ø 차동입력 없을 때 동상모드 양쪽 Emitter 및 Collector 전류 같다고 가정 평형상태 0 차동입력 0 차동출력 supply ripple 제거 VCC가 변해도 VX – VY는 변하지 않음 CH 10 Differential Amplifiers 13

10. 2 Bipolar Differential Pair Ø Ø Ø 차동입력 없을 때 동상모드 양쪽 Emitter 및 Collector 전류 같다고 가정 평형상태 0 차동입력 0 차동출력 supply ripple 제거 VCC가 변해도 VX – VY는 변하지 않음 CH 10 Differential Amplifiers 13

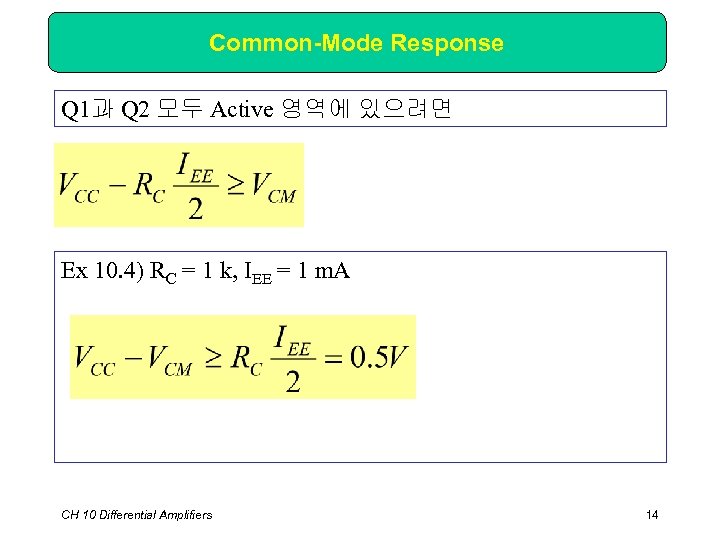

Common-Mode Response Q 1과 Q 2 모두 Active 영역에 있으려면 Ex 10. 4) RC = 1 k, IEE = 1 m. A CH 10 Differential Amplifiers 14

Common-Mode Response Q 1과 Q 2 모두 Active 영역에 있으려면 Ex 10. 4) RC = 1 k, IEE = 1 m. A CH 10 Differential Amplifiers 14

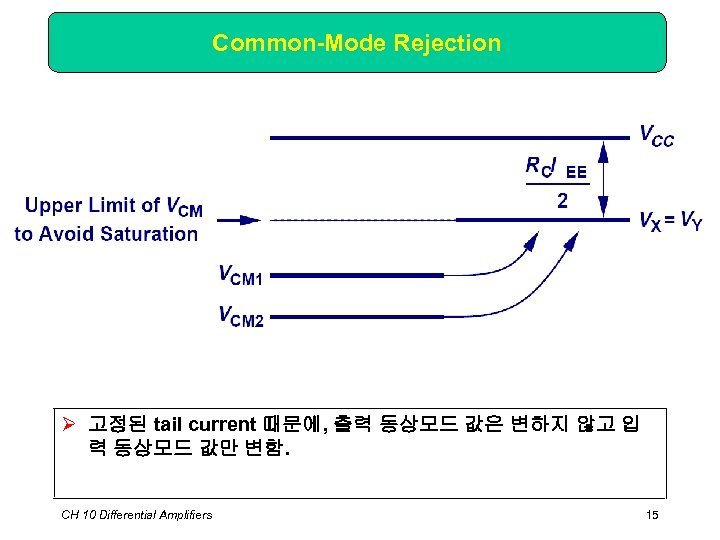

Common-Mode Rejection Ø 고정된 tail current 때문에, 출력 동상모드 값은 변하지 않고 입 력 동상모드 값만 변함. CH 10 Differential Amplifiers 15

Common-Mode Rejection Ø 고정된 tail current 때문에, 출력 동상모드 값은 변하지 않고 입 력 동상모드 값만 변함. CH 10 Differential Amplifiers 15

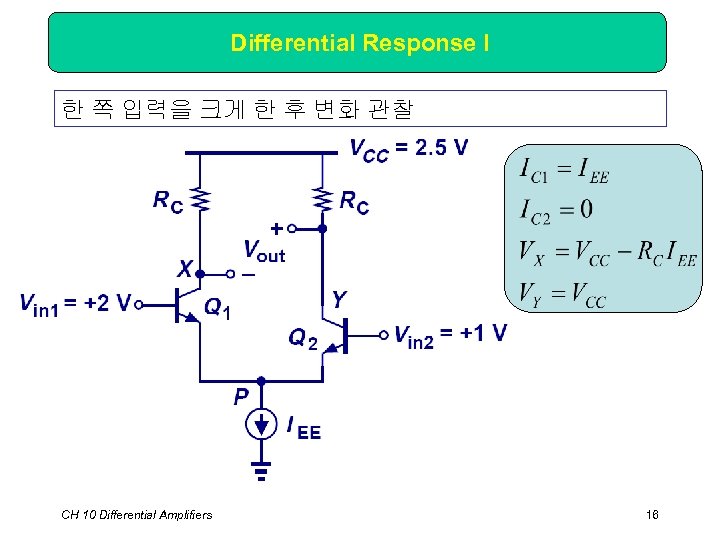

Differential Response I 한 쪽 입력을 크게 한 후 변화 관찰 CH 10 Differential Amplifiers 16

Differential Response I 한 쪽 입력을 크게 한 후 변화 관찰 CH 10 Differential Amplifiers 16

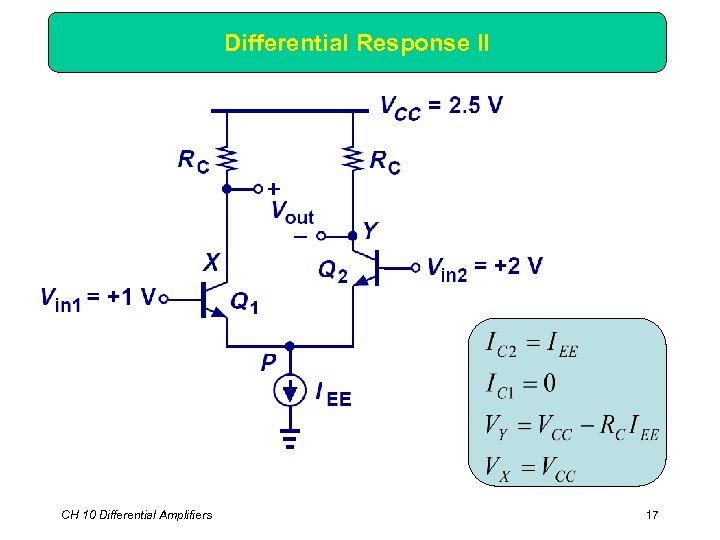

Differential Response II CH 10 Differential Amplifiers 17

Differential Response II CH 10 Differential Amplifiers 17

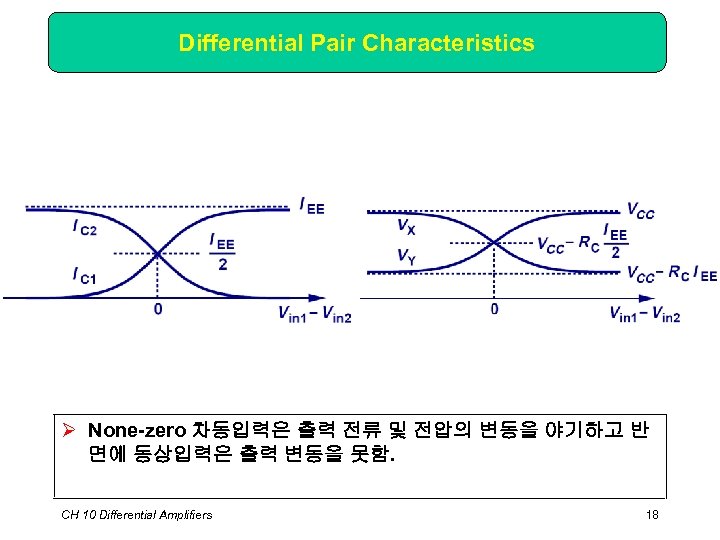

Differential Pair Characteristics Ø None-zero 차동입력은 출력 전류 및 전압의 변동을 야기하고 반 면에 동상입력은 출력 변동을 못함. CH 10 Differential Amplifiers 18

Differential Pair Characteristics Ø None-zero 차동입력은 출력 전류 및 전압의 변동을 야기하고 반 면에 동상입력은 출력 변동을 못함. CH 10 Differential Amplifiers 18

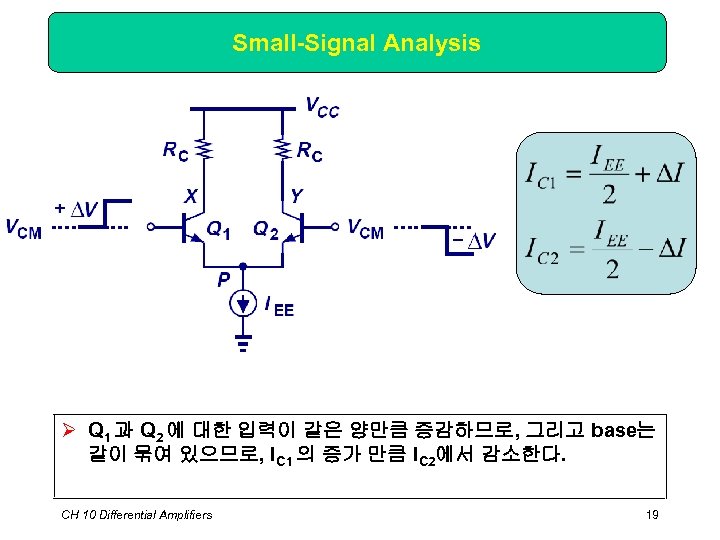

Small-Signal Analysis Ø Q 1 과 Q 2 에 대한 입력이 같은 양만큼 증감하므로, 그리고 base는 같이 묶여 있으므로, IC 1 의 증가 만큼 IC 2에서 감소한다. CH 10 Differential Amplifiers 19

Small-Signal Analysis Ø Q 1 과 Q 2 에 대한 입력이 같은 양만큼 증감하므로, 그리고 base는 같이 묶여 있으므로, IC 1 의 증가 만큼 IC 2에서 감소한다. CH 10 Differential Amplifiers 19

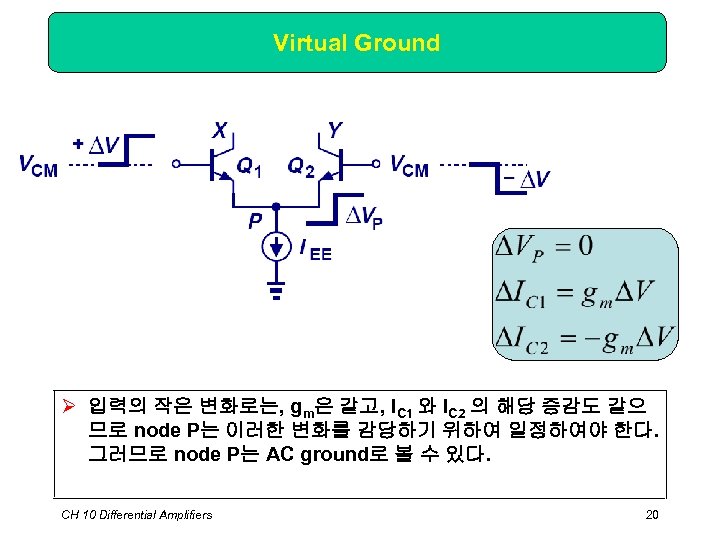

Virtual Ground Ø 입력의 작은 변화로는, gm은 같고, IC 1 와 IC 2 의 해당 증감도 같으 므로 node P는 이러한 변화를 감당하기 위하여 일정하여야 한다. 그러므로 node P는 AC ground로 볼 수 있다. CH 10 Differential Amplifiers 20

Virtual Ground Ø 입력의 작은 변화로는, gm은 같고, IC 1 와 IC 2 의 해당 증감도 같으 므로 node P는 이러한 변화를 감당하기 위하여 일정하여야 한다. 그러므로 node P는 AC ground로 볼 수 있다. CH 10 Differential Amplifiers 20

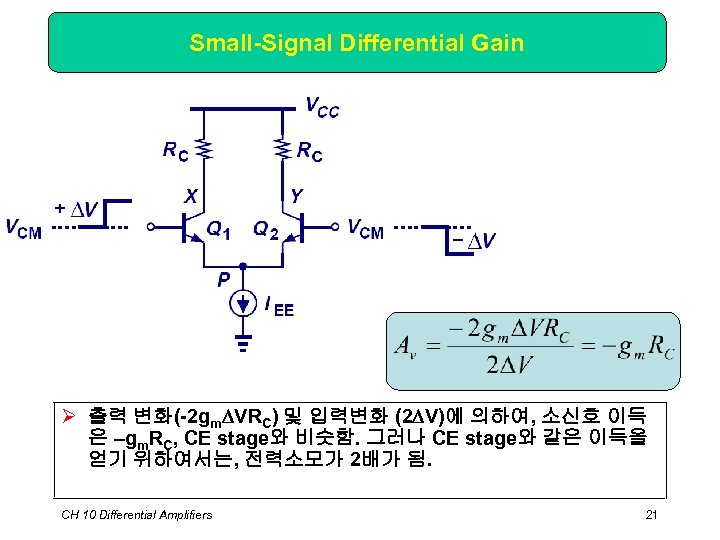

Small-Signal Differential Gain Ø 출력 변화(-2 gm VRC) 및 입력변화 (2 V)에 의하여, 소신호 이득 은 –gm. RC, CE stage와 비슷함. 그러나 CE stage와 같은 이득을 얻기 위하여서는, 전력소모가 2배가 됨. CH 10 Differential Amplifiers 21

Small-Signal Differential Gain Ø 출력 변화(-2 gm VRC) 및 입력변화 (2 V)에 의하여, 소신호 이득 은 –gm. RC, CE stage와 비슷함. 그러나 CE stage와 같은 이득을 얻기 위하여서는, 전력소모가 2배가 됨. CH 10 Differential Amplifiers 21

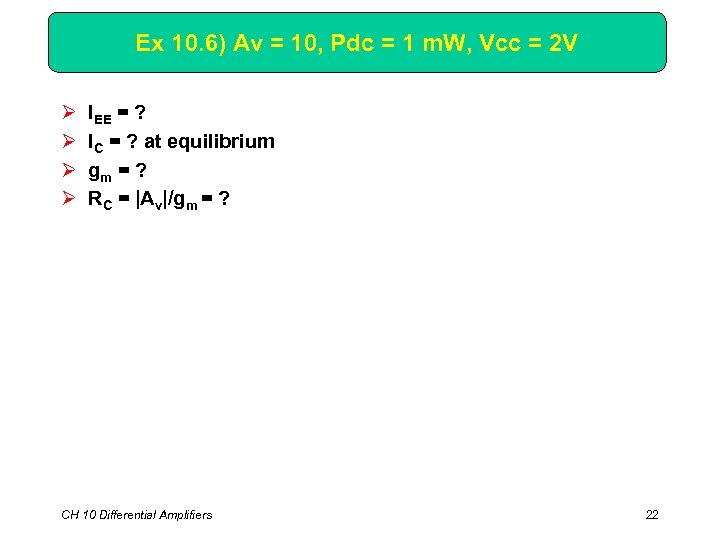

Ex 10. 6) Av = 10, Pdc = 1 m. W, Vcc = 2 V Ø Ø IEE = ? IC = ? at equilibrium gm = ? RC = |Av|/gm = ? CH 10 Differential Amplifiers 22

Ex 10. 6) Av = 10, Pdc = 1 m. W, Vcc = 2 V Ø Ø IEE = ? IC = ? at equilibrium gm = ? RC = |Av|/gm = ? CH 10 Differential Amplifiers 22

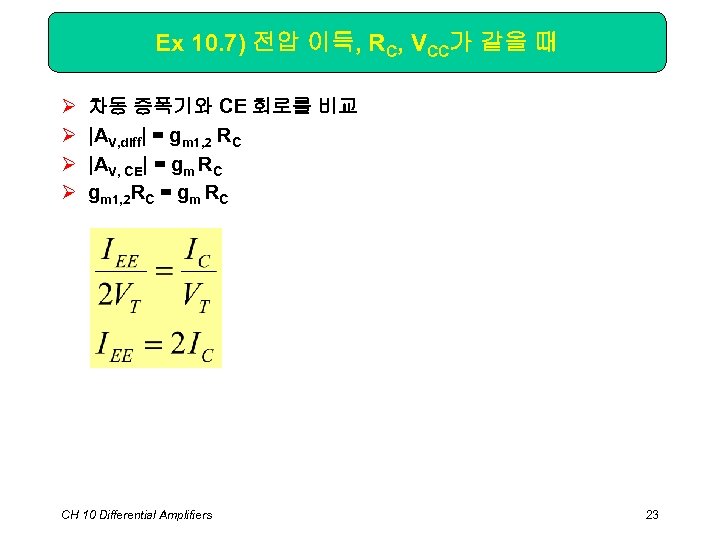

Ex 10. 7) 전압 이득, RC, VCC가 같을 때 Ø Ø 차동 증폭기와 CE 회로를 비교 |AV, diff| = gm 1, 2 RC |AV, CE| = gm RC gm 1, 2 RC = gm RC CH 10 Differential Amplifiers 23

Ex 10. 7) 전압 이득, RC, VCC가 같을 때 Ø Ø 차동 증폭기와 CE 회로를 비교 |AV, diff| = gm 1, 2 RC |AV, CE| = gm RC gm 1, 2 RC = gm RC CH 10 Differential Amplifiers 23

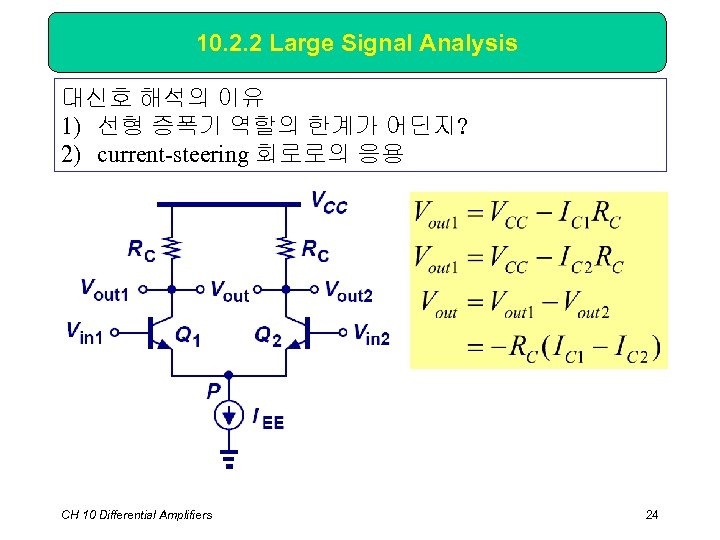

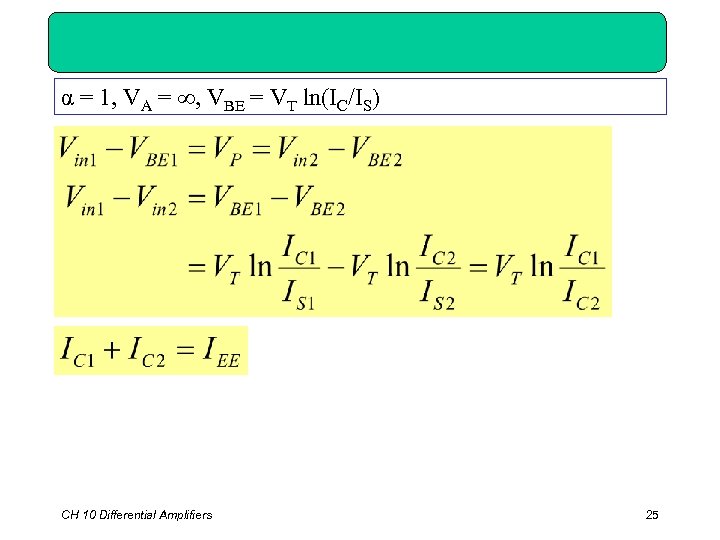

10. 2. 2 Large Signal Analysis 대신호 해석의 이유 1) 선형 증폭기 역할의 한계가 어딘지? 2) current-steering 회로로의 응용 CH 10 Differential Amplifiers 24

10. 2. 2 Large Signal Analysis 대신호 해석의 이유 1) 선형 증폭기 역할의 한계가 어딘지? 2) current-steering 회로로의 응용 CH 10 Differential Amplifiers 24

α = 1, VA = ∞, VBE = VT ln(IC/IS) CH 10 Differential Amplifiers 25

α = 1, VA = ∞, VBE = VT ln(IC/IS) CH 10 Differential Amplifiers 25

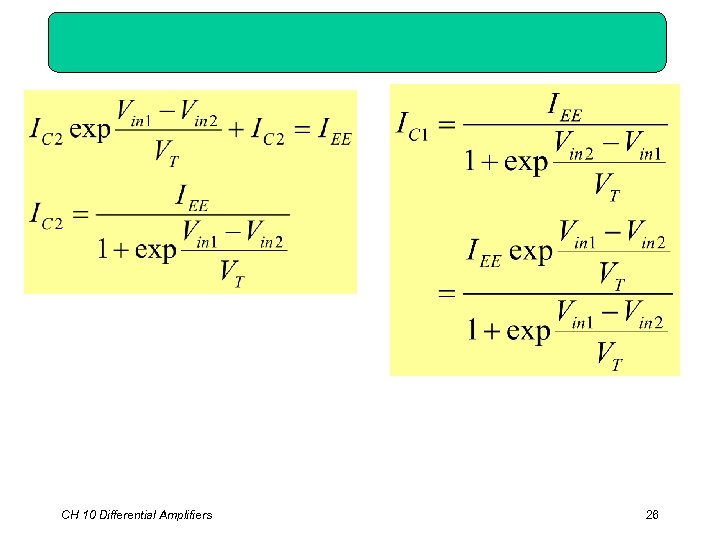

CH 10 Differential Amplifiers 26

CH 10 Differential Amplifiers 26

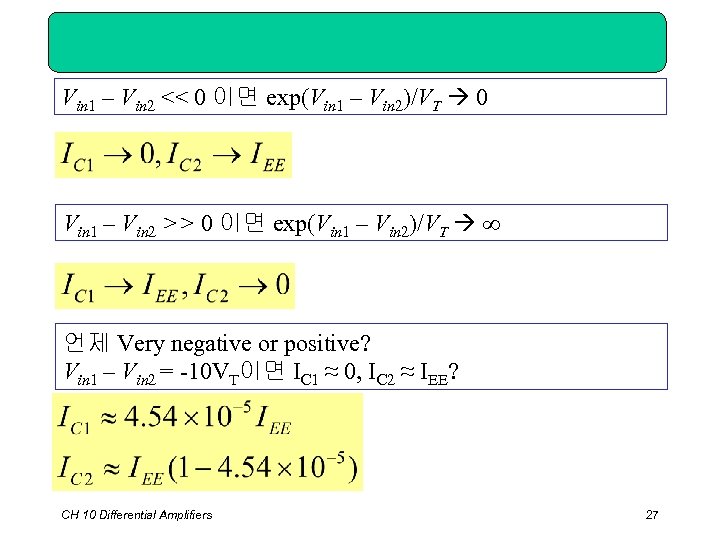

Vin 1 – Vin 2 << 0 이면 exp(Vin 1 – Vin 2)/VT 0 Vin 1 – Vin 2 >> 0 이면 exp(Vin 1 – Vin 2)/VT ∞ 언제 Very negative or positive? Vin 1 – Vin 2 = -10 VT이면 IC 1 ≈ 0, IC 2 ≈ IEE? CH 10 Differential Amplifiers 27

Vin 1 – Vin 2 << 0 이면 exp(Vin 1 – Vin 2)/VT 0 Vin 1 – Vin 2 >> 0 이면 exp(Vin 1 – Vin 2)/VT ∞ 언제 Very negative or positive? Vin 1 – Vin 2 = -10 VT이면 IC 1 ≈ 0, IC 2 ≈ IEE? CH 10 Differential Amplifiers 27

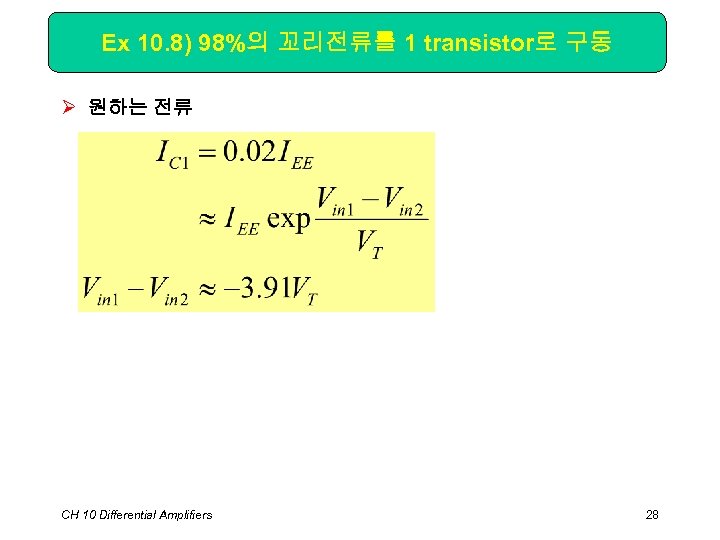

Ex 10. 8) 98%의 꼬리전류를 1 transistor로 구동 Ø 원하는 전류 CH 10 Differential Amplifiers 28

Ex 10. 8) 98%의 꼬리전류를 1 transistor로 구동 Ø 원하는 전류 CH 10 Differential Amplifiers 28

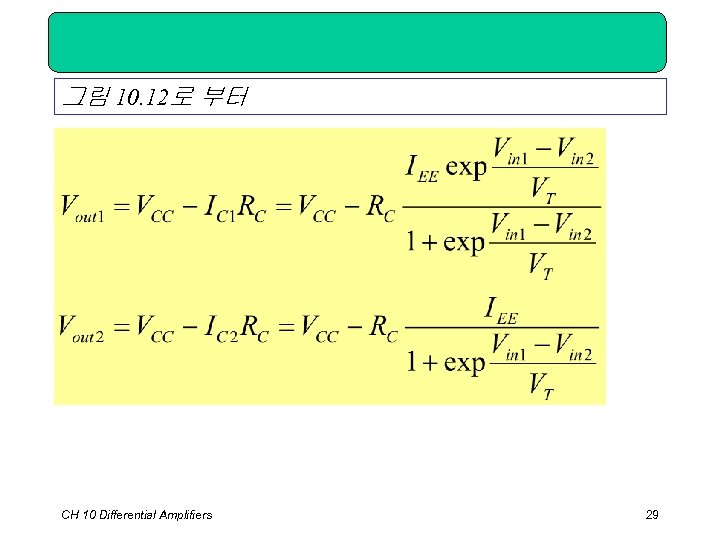

그림 10. 12로 부터 CH 10 Differential Amplifiers 29

그림 10. 12로 부터 CH 10 Differential Amplifiers 29

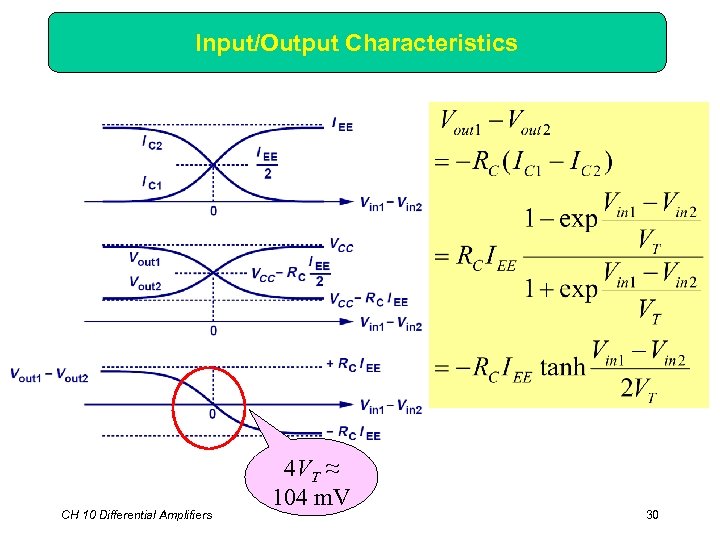

Input/Output Characteristics CH 10 Differential Amplifiers 4 VT ≈ 104 m. V 30

Input/Output Characteristics CH 10 Differential Amplifiers 4 VT ≈ 104 m. V 30

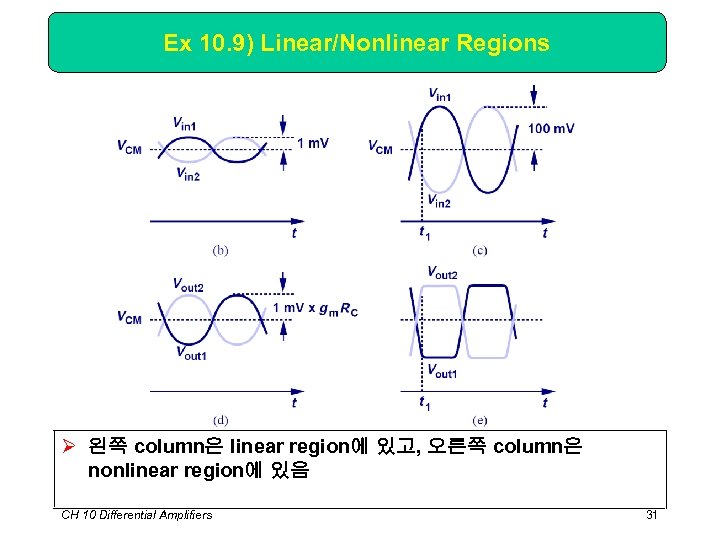

Ex 10. 9) Linear/Nonlinear Regions Ø 왼쪽 column은 linear region에 있고, 오른쪽 column은 nonlinear region에 있음 CH 10 Differential Amplifiers 31

Ex 10. 9) Linear/Nonlinear Regions Ø 왼쪽 column은 linear region에 있고, 오른쪽 column은 nonlinear region에 있음 CH 10 Differential Amplifiers 31

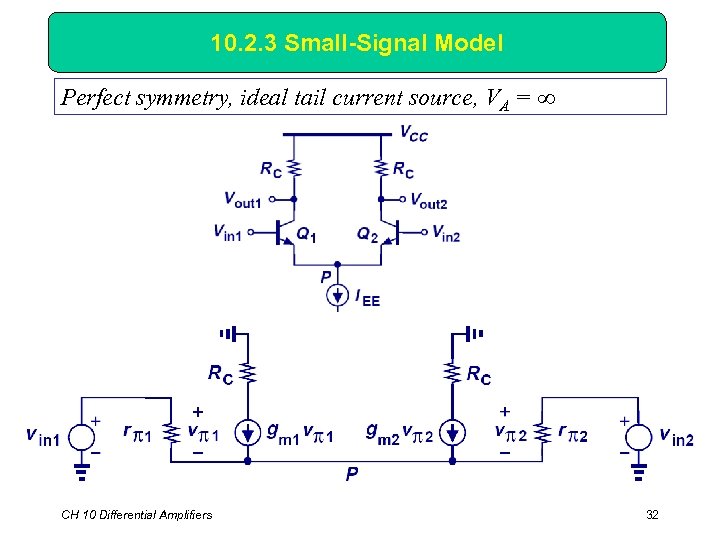

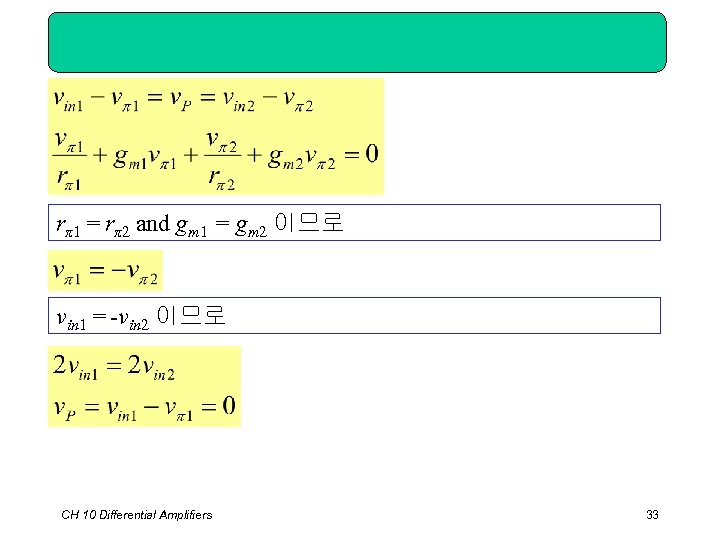

10. 2. 3 Small-Signal Model Perfect symmetry, ideal tail current source, VA = ∞ CH 10 Differential Amplifiers 32

10. 2. 3 Small-Signal Model Perfect symmetry, ideal tail current source, VA = ∞ CH 10 Differential Amplifiers 32

rπ1 = rπ2 and gm 1 = gm 2 이므로 vin 1 = -vin 2 이므로 CH 10 Differential Amplifiers 33

rπ1 = rπ2 and gm 1 = gm 2 이므로 vin 1 = -vin 2 이므로 CH 10 Differential Amplifiers 33

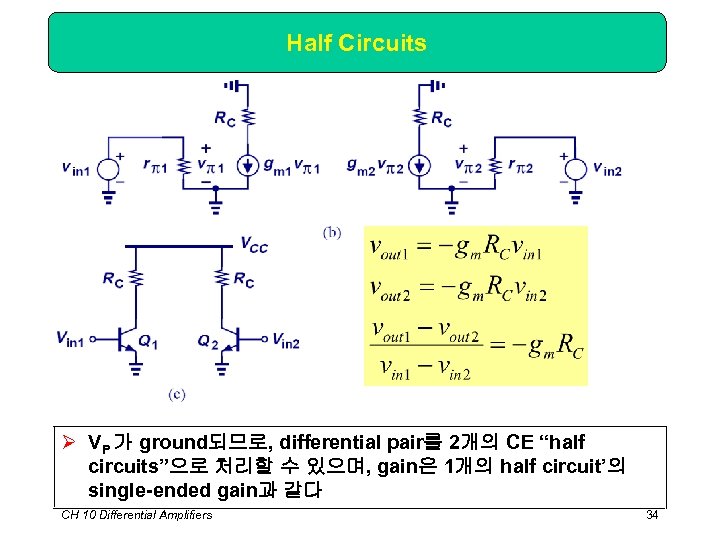

Half Circuits Ø VP 가 ground되므로, differential pair를 2개의 CE “half circuits”으로 처리할 수 있으며, gain은 1개의 half circuit’의 single-ended gain과 같다 CH 10 Differential Amplifiers 34

Half Circuits Ø VP 가 ground되므로, differential pair를 2개의 CE “half circuits”으로 처리할 수 있으며, gain은 1개의 half circuit’의 single-ended gain과 같다 CH 10 Differential Amplifiers 34

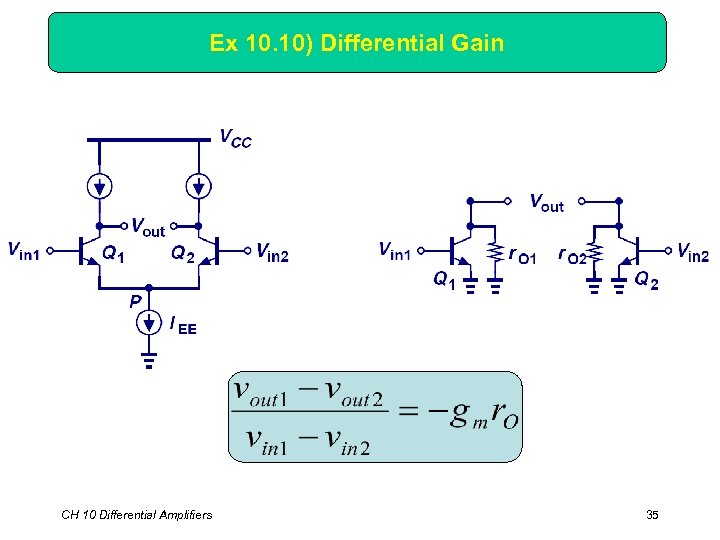

Ex 10. 10) Differential Gain CH 10 Differential Amplifiers 35

Ex 10. 10) Differential Gain CH 10 Differential Amplifiers 35

Ex 10. 11) 차동 전압 이득 CH 10 Differential Amplifiers 36

Ex 10. 11) 차동 전압 이득 CH 10 Differential Amplifiers 36

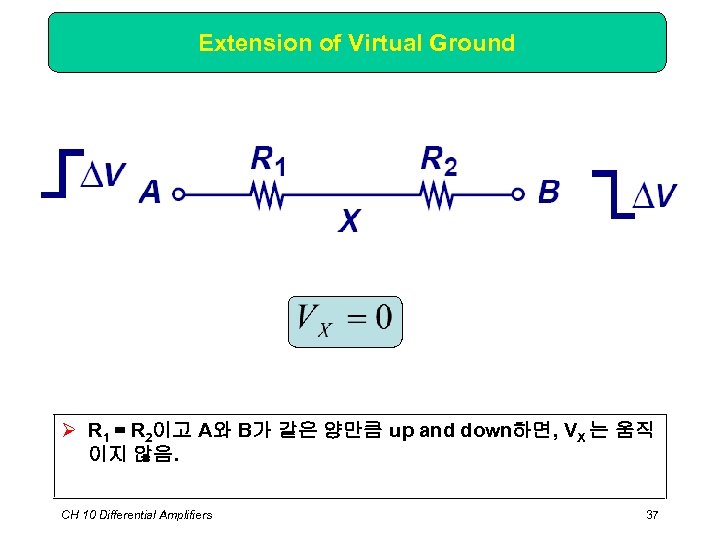

Extension of Virtual Ground Ø R 1 = R 2이고 A와 B가 같은 양만큼 up and down하면, VX 는 움직 이지 않음. CH 10 Differential Amplifiers 37

Extension of Virtual Ground Ø R 1 = R 2이고 A와 B가 같은 양만큼 up and down하면, VX 는 움직 이지 않음. CH 10 Differential Amplifiers 37

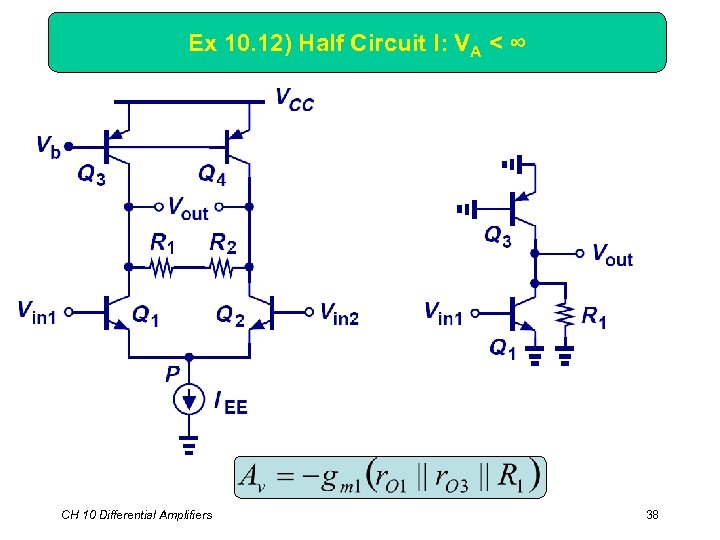

Ex 10. 12) Half Circuit I: VA < ∞ CH 10 Differential Amplifiers 38

Ex 10. 12) Half Circuit I: VA < ∞ CH 10 Differential Amplifiers 38

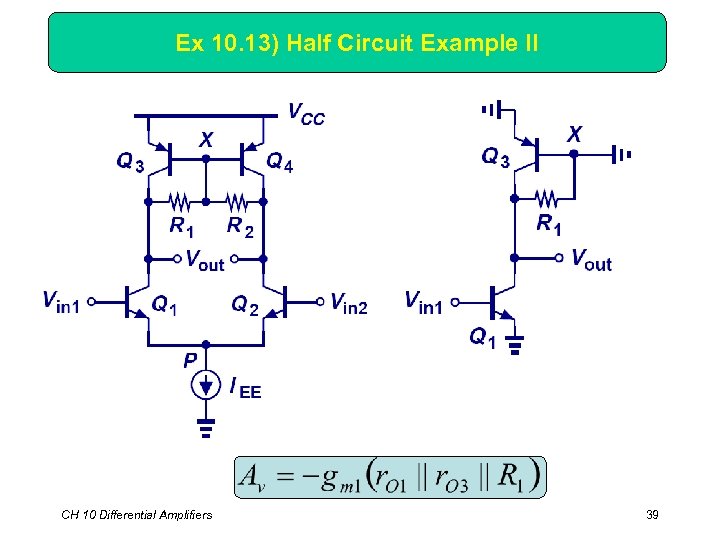

Ex 10. 13) Half Circuit Example II CH 10 Differential Amplifiers 39

Ex 10. 13) Half Circuit Example II CH 10 Differential Amplifiers 39

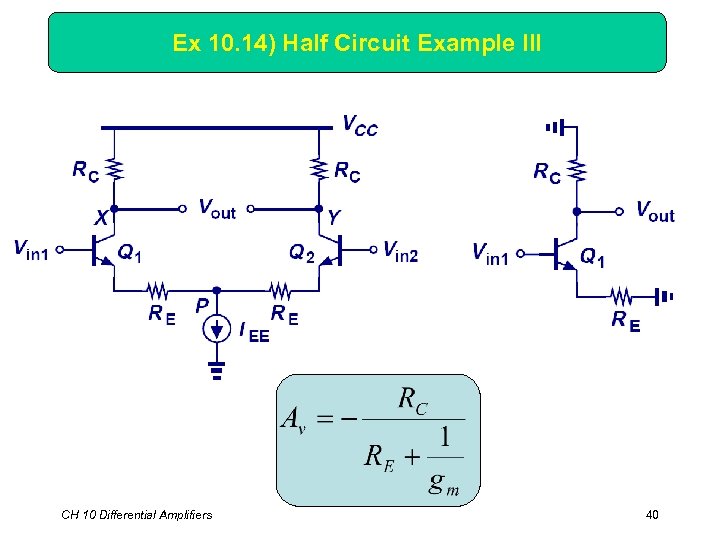

Ex 10. 14) Half Circuit Example III CH 10 Differential Amplifiers 40

Ex 10. 14) Half Circuit Example III CH 10 Differential Amplifiers 40

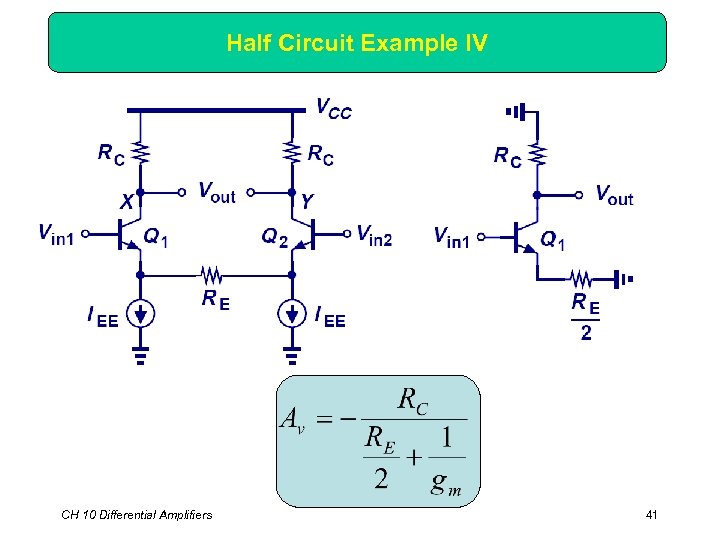

Half Circuit Example IV CH 10 Differential Amplifiers 41

Half Circuit Example IV CH 10 Differential Amplifiers 41

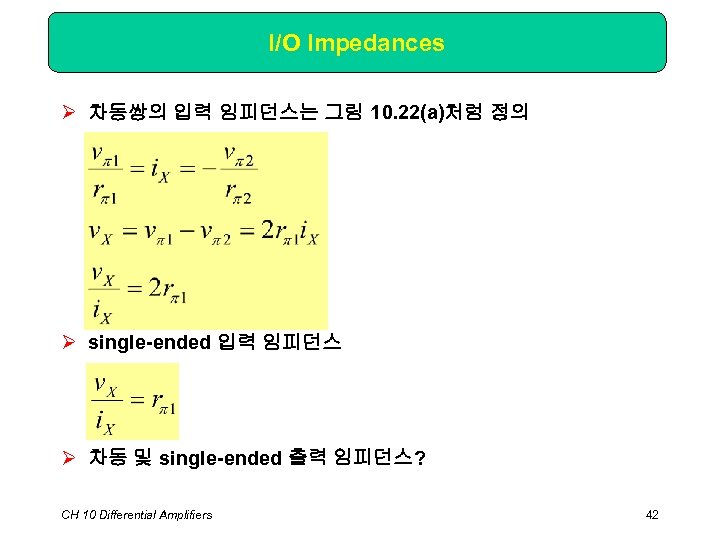

I/O Impedances Ø 차동쌍의 입력 임피던스는 그림 10. 22(a)처럼 정의 Ø single-ended 입력 임피던스 Ø 차동 및 single-ended 출력 임피던스? CH 10 Differential Amplifiers 42

I/O Impedances Ø 차동쌍의 입력 임피던스는 그림 10. 22(a)처럼 정의 Ø single-ended 입력 임피던스 Ø 차동 및 single-ended 출력 임피던스? CH 10 Differential Amplifiers 42

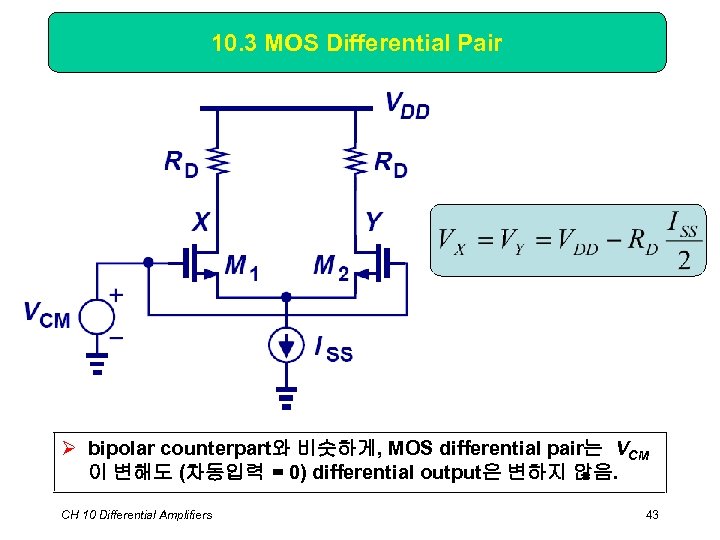

10. 3 MOS Differential Pair Ø bipolar counterpart와 비슷하게, MOS differential pair는 VCM 이 변해도 (차동입력 = 0) differential output은 변하지 않음. CH 10 Differential Amplifiers 43

10. 3 MOS Differential Pair Ø bipolar counterpart와 비슷하게, MOS differential pair는 VCM 이 변해도 (차동입력 = 0) differential output은 변하지 않음. CH 10 Differential Amplifiers 43

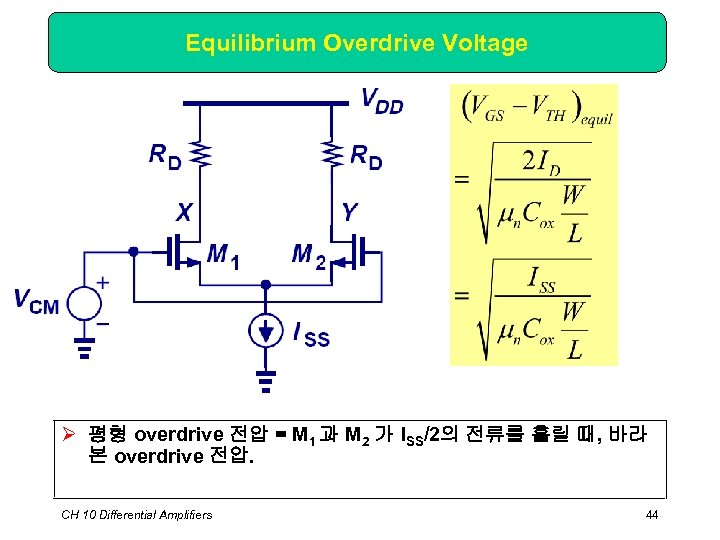

Equilibrium Overdrive Voltage Ø 평형 overdrive 전압 = M 1 과 M 2 가 ISS/2의 전류를 흘릴 때, 바라 본 overdrive 전압. CH 10 Differential Amplifiers 44

Equilibrium Overdrive Voltage Ø 평형 overdrive 전압 = M 1 과 M 2 가 ISS/2의 전류를 흘릴 때, 바라 본 overdrive 전압. CH 10 Differential Amplifiers 44

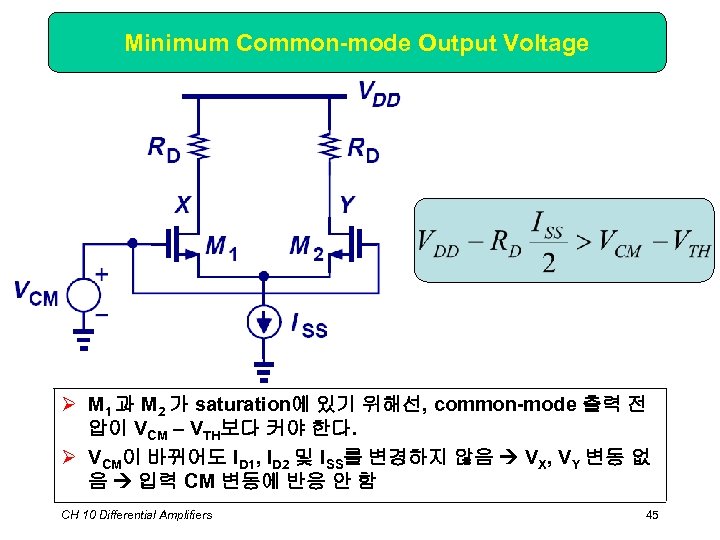

Minimum Common-mode Output Voltage Ø M 1 과 M 2 가 saturation에 있기 위해선, common-mode 출력 전 압이 VCM – VTH보다 커야 한다. Ø VCM이 바뀌어도 ID 1, ID 2 및 ISS를 변경하지 않음 VX, VY 변동 없 음 입력 CM 변동에 반응 안 함 CH 10 Differential Amplifiers 45

Minimum Common-mode Output Voltage Ø M 1 과 M 2 가 saturation에 있기 위해선, common-mode 출력 전 압이 VCM – VTH보다 커야 한다. Ø VCM이 바뀌어도 ID 1, ID 2 및 ISS를 변경하지 않음 VX, VY 변동 없 음 입력 CM 변동에 반응 안 함 CH 10 Differential Amplifiers 45

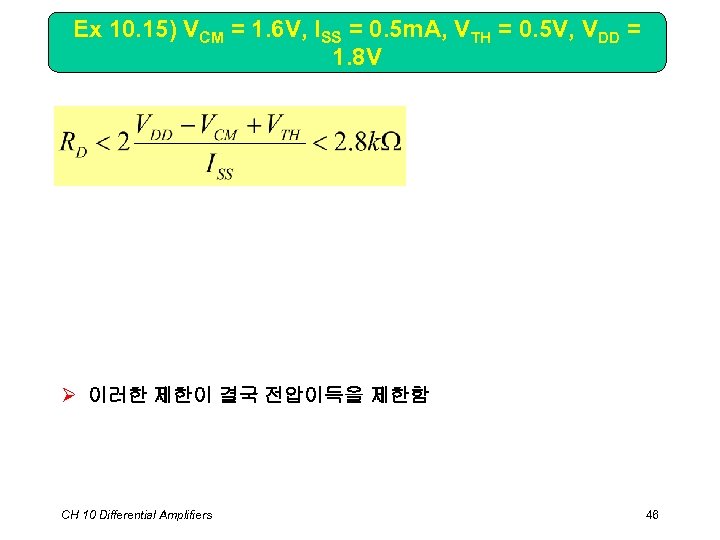

Ex 10. 15) VCM = 1. 6 V, ISS = 0. 5 m. A, VTH = 0. 5 V, VDD = 1. 8 V Ø 이러한 제한이 결국 전압이득을 제한함 CH 10 Differential Amplifiers 46

Ex 10. 15) VCM = 1. 6 V, ISS = 0. 5 m. A, VTH = 0. 5 V, VDD = 1. 8 V Ø 이러한 제한이 결국 전압이득을 제한함 CH 10 Differential Amplifiers 46

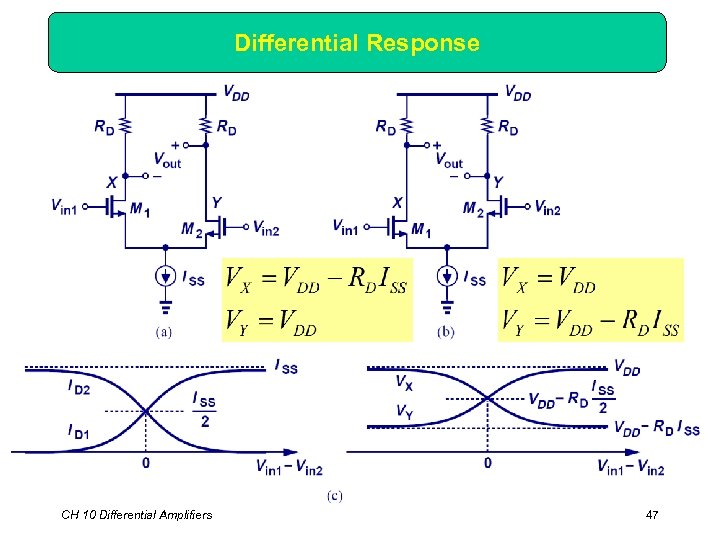

Differential Response CH 10 Differential Amplifiers 47

Differential Response CH 10 Differential Amplifiers 47

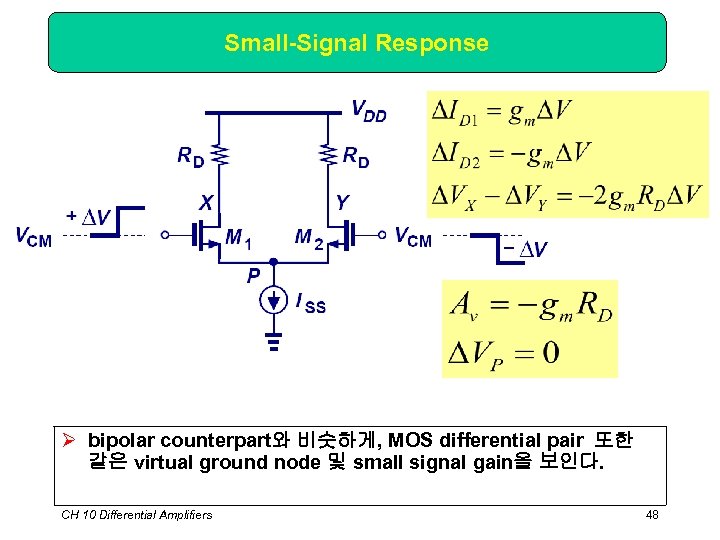

Small-Signal Response Ø bipolar counterpart와 비슷하게, MOS differential pair 또한 같은 virtual ground node 및 small signal gain을 보인다. CH 10 Differential Amplifiers 48

Small-Signal Response Ø bipolar counterpart와 비슷하게, MOS differential pair 또한 같은 virtual ground node 및 small signal gain을 보인다. CH 10 Differential Amplifiers 48

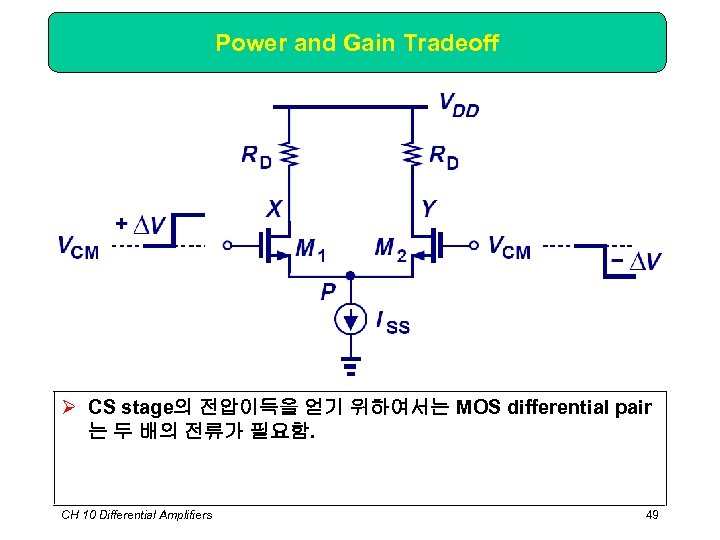

Power and Gain Tradeoff Ø CS stage의 전압이득을 얻기 위하여서는 MOS differential pair 는 두 배의 전류가 필요함. CH 10 Differential Amplifiers 49

Power and Gain Tradeoff Ø CS stage의 전압이득을 얻기 위하여서는 MOS differential pair 는 두 배의 전류가 필요함. CH 10 Differential Amplifiers 49

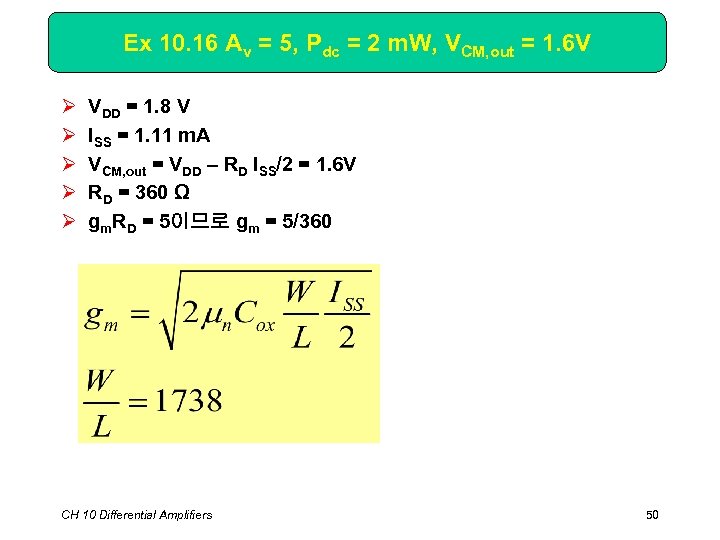

Ex 10. 16 Av = 5, Pdc = 2 m. W, VCM, out = 1. 6 V Ø Ø Ø VDD = 1. 8 V ISS = 1. 11 m. A VCM, out = VDD – RD ISS/2 = 1. 6 V RD = 360 Ω gm. RD = 5이므로 gm = 5/360 CH 10 Differential Amplifiers 50

Ex 10. 16 Av = 5, Pdc = 2 m. W, VCM, out = 1. 6 V Ø Ø Ø VDD = 1. 8 V ISS = 1. 11 m. A VCM, out = VDD – RD ISS/2 = 1. 6 V RD = 360 Ω gm. RD = 5이므로 gm = 5/360 CH 10 Differential Amplifiers 50

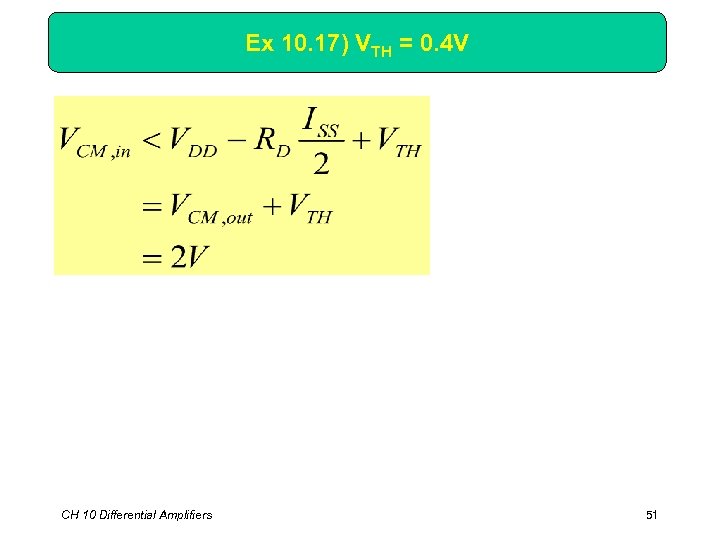

Ex 10. 17) VTH = 0. 4 V CH 10 Differential Amplifiers 51

Ex 10. 17) VTH = 0. 4 V CH 10 Differential Amplifiers 51

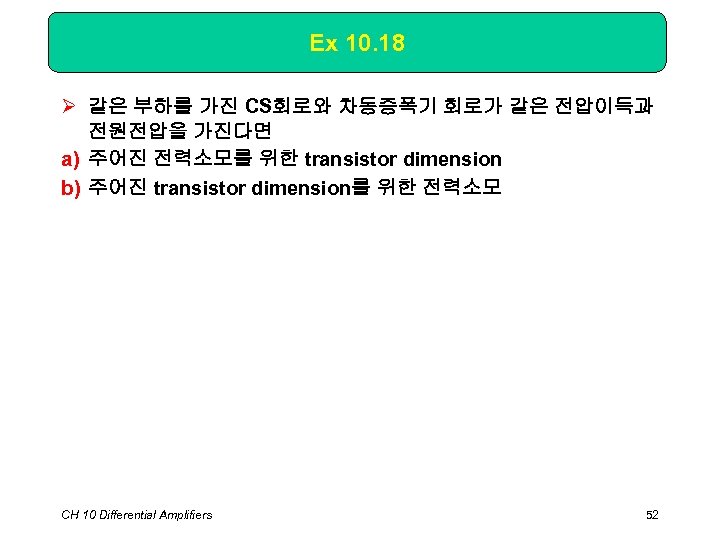

Ex 10. 18 Ø 같은 부하를 가진 CS회로와 차동증폭기 회로가 같은 전압이득과 전원전압을 가진다면 a) 주어진 전력소모를 위한 transistor dimension b) 주어진 transistor dimension를 위한 전력소모 CH 10 Differential Amplifiers 52

Ex 10. 18 Ø 같은 부하를 가진 CS회로와 차동증폭기 회로가 같은 전압이득과 전원전압을 가진다면 a) 주어진 전력소모를 위한 transistor dimension b) 주어진 transistor dimension를 위한 전력소모 CH 10 Differential Amplifiers 52

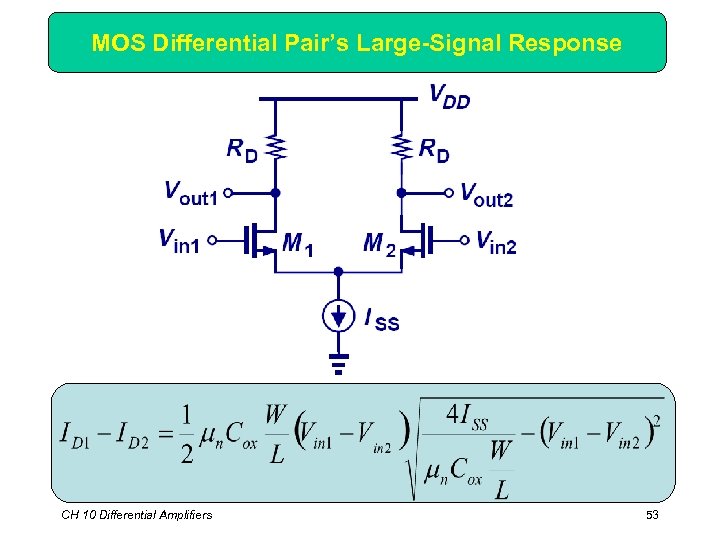

MOS Differential Pair’s Large-Signal Response CH 10 Differential Amplifiers 53

MOS Differential Pair’s Large-Signal Response CH 10 Differential Amplifiers 53

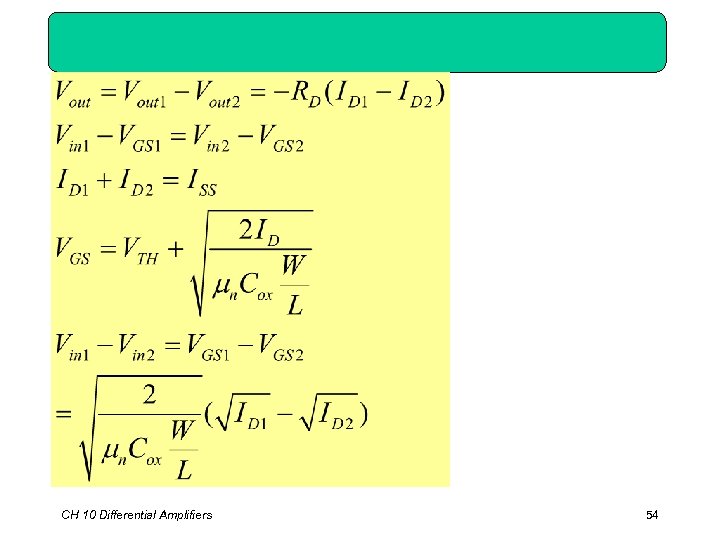

CH 10 Differential Amplifiers 54

CH 10 Differential Amplifiers 54

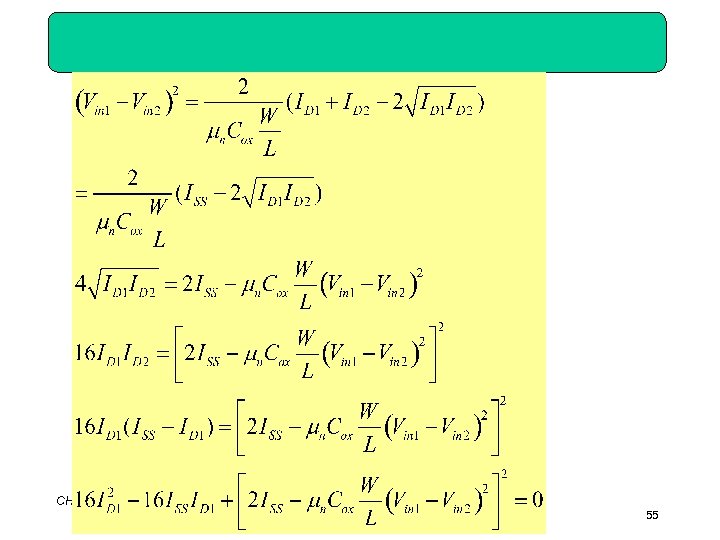

CH 10 Differential Amplifiers 55

CH 10 Differential Amplifiers 55

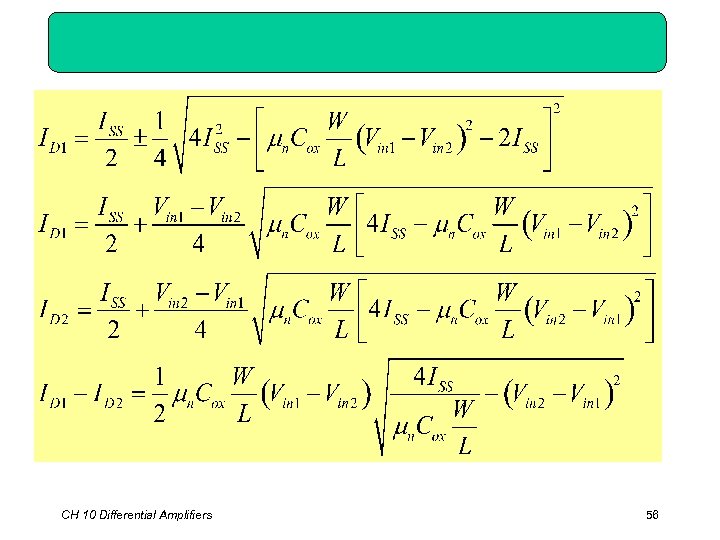

CH 10 Differential Amplifiers 56

CH 10 Differential Amplifiers 56

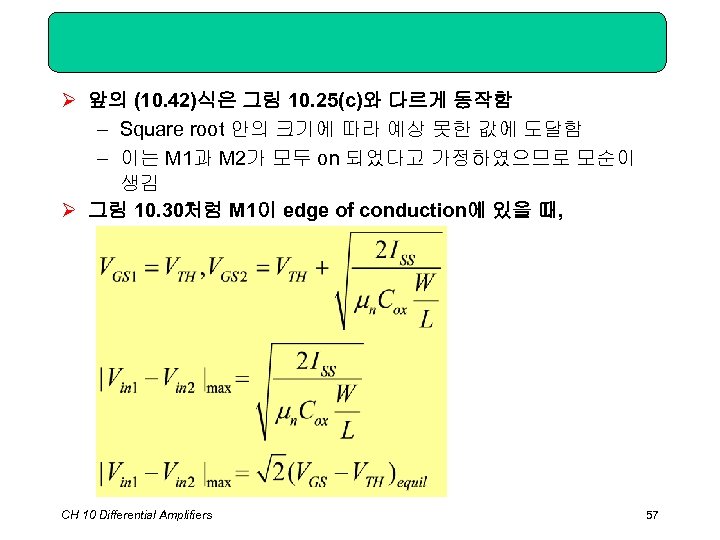

Ø 앞의 (10. 42)식은 그림 10. 25(c)와 다르게 동작함 – Square root 안의 크기에 따라 예상 못한 값에 도달함 – 이는 M 1과 M 2가 모두 on 되었다고 가정하였으므로 모순이 생김 Ø 그림 10. 30처럼 M 1이 edge of conduction에 있을 때, CH 10 Differential Amplifiers 57

Ø 앞의 (10. 42)식은 그림 10. 25(c)와 다르게 동작함 – Square root 안의 크기에 따라 예상 못한 값에 도달함 – 이는 M 1과 M 2가 모두 on 되었다고 가정하였으므로 모순이 생김 Ø 그림 10. 30처럼 M 1이 edge of conduction에 있을 때, CH 10 Differential Amplifiers 57

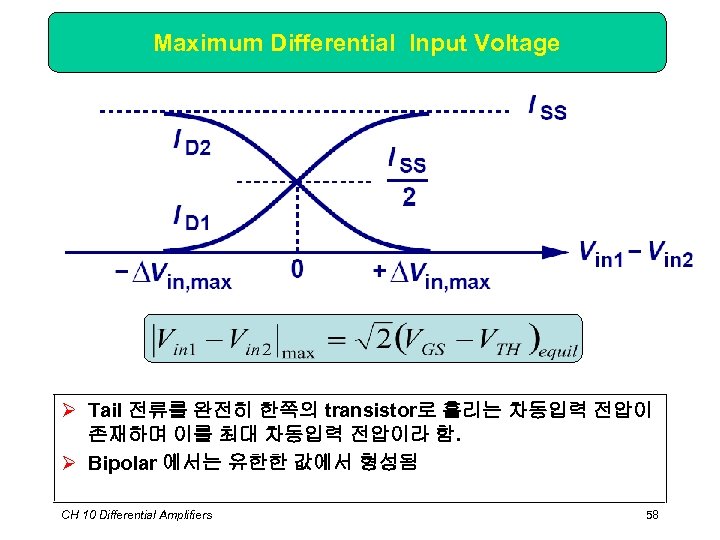

Maximum Differential Input Voltage Ø Tail 전류를 완전히 한쪽의 transistor로 흘리는 차동입력 전압이 존재하며 이를 최대 차동입력 전압이라 함. Ø Bipolar 에서는 유한한 값에서 형성됨 CH 10 Differential Amplifiers 58

Maximum Differential Input Voltage Ø Tail 전류를 완전히 한쪽의 transistor로 흘리는 차동입력 전압이 존재하며 이를 최대 차동입력 전압이라 함. Ø Bipolar 에서는 유한한 값에서 형성됨 CH 10 Differential Amplifiers 58

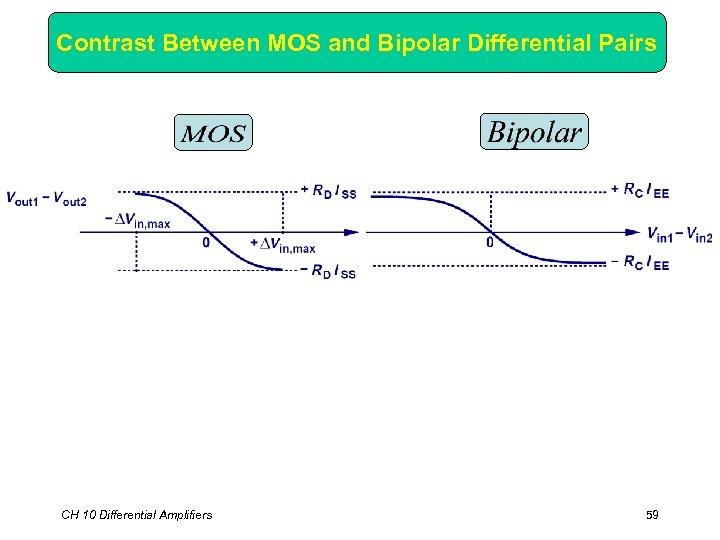

Contrast Between MOS and Bipolar Differential Pairs CH 10 Differential Amplifiers 59

Contrast Between MOS and Bipolar Differential Pairs CH 10 Differential Amplifiers 59

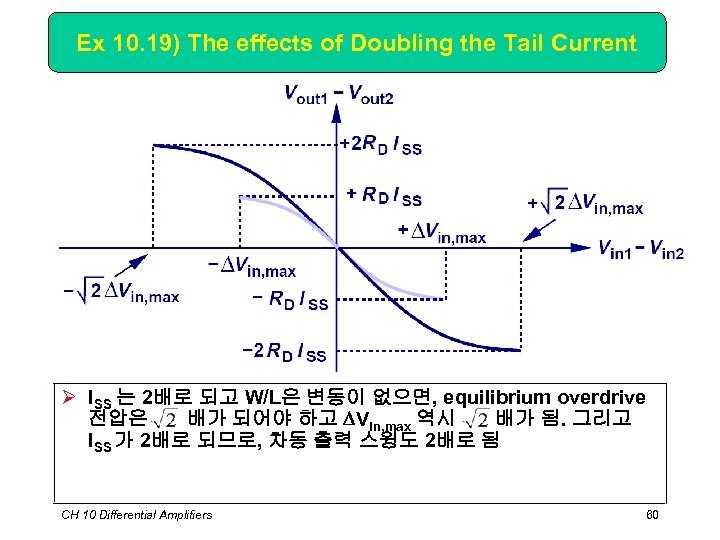

Ex 10. 19) The effects of Doubling the Tail Current Ø ISS 는 2배로 되고 W/L은 변동이 없으면, equilibrium overdrive 전압은 배가 되어야 하고 Vin, max 역시 배가 됨. 그리고 ISS 가 2배로 되므로, 차동 출력 스윙도 2배로 됨 CH 10 Differential Amplifiers 60

Ex 10. 19) The effects of Doubling the Tail Current Ø ISS 는 2배로 되고 W/L은 변동이 없으면, equilibrium overdrive 전압은 배가 되어야 하고 Vin, max 역시 배가 됨. 그리고 ISS 가 2배로 되므로, 차동 출력 스윙도 2배로 됨 CH 10 Differential Amplifiers 60

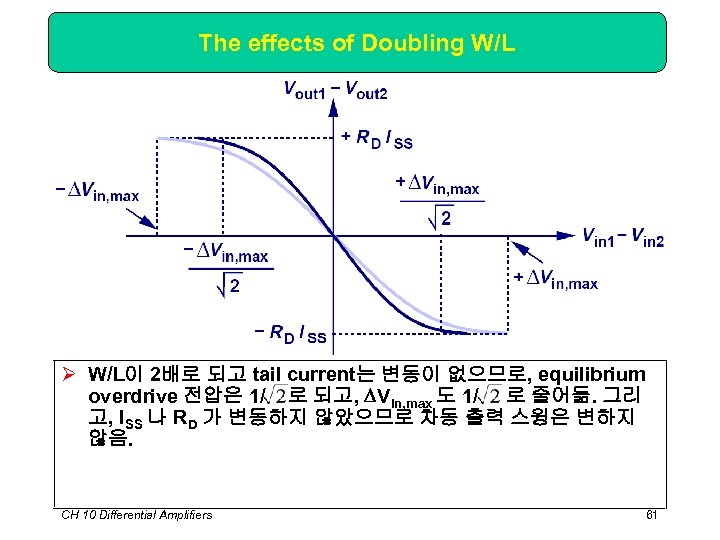

The effects of Doubling W/L Ø W/L이 2배로 되고 tail current는 변동이 없으므로, equilibrium overdrive 전압은 1/ 로 되고, Vin, max 도 1/ 로 줄어듦. 그리 고, ISS 나 RD 가 변동하지 않았으므로 차동 출력 스윙은 변하지 않음. CH 10 Differential Amplifiers 61

The effects of Doubling W/L Ø W/L이 2배로 되고 tail current는 변동이 없으므로, equilibrium overdrive 전압은 1/ 로 되고, Vin, max 도 1/ 로 줄어듦. 그리 고, ISS 나 RD 가 변동하지 않았으므로 차동 출력 스윙은 변하지 않음. CH 10 Differential Amplifiers 61

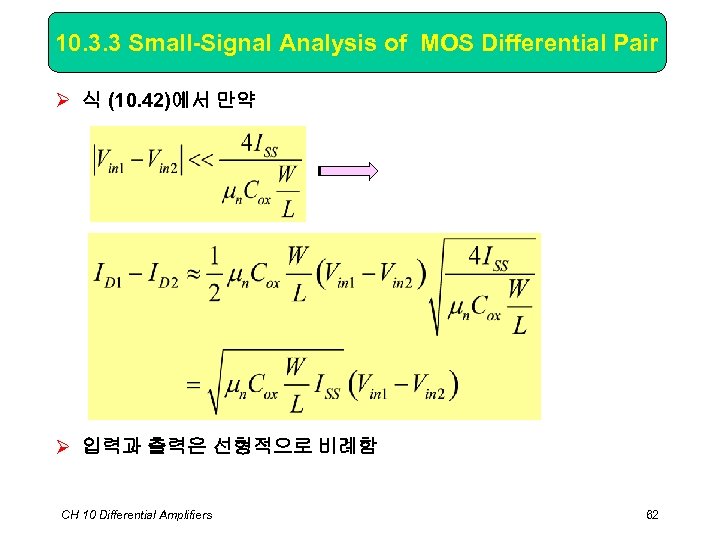

10. 3. 3 Small-Signal Analysis of MOS Differential Pair Ø 식 (10. 42)에서 만약 Ø 입력과 출력은 선형적으로 비례함 CH 10 Differential Amplifiers 62

10. 3. 3 Small-Signal Analysis of MOS Differential Pair Ø 식 (10. 42)에서 만약 Ø 입력과 출력은 선형적으로 비례함 CH 10 Differential Amplifiers 62

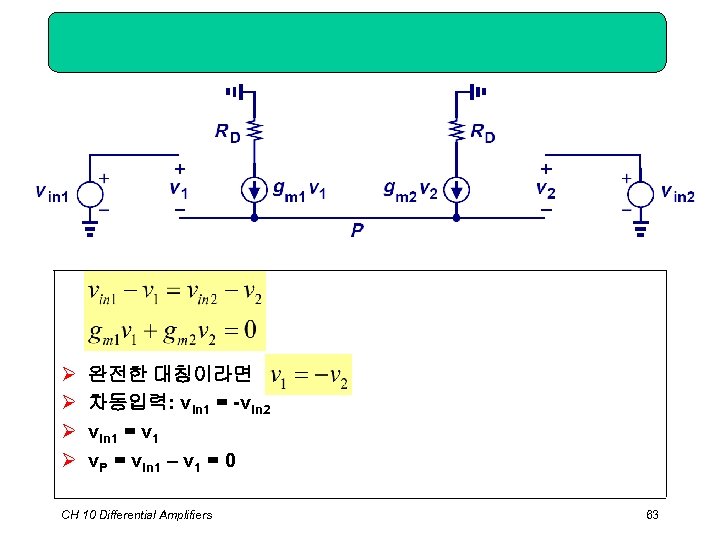

Ø Ø 완전한 대칭이라면 차동입력: vin 1 = -vin 2 vin 1 = v 1 v. P = vin 1 – v 1 = 0 CH 10 Differential Amplifiers 63

Ø Ø 완전한 대칭이라면 차동입력: vin 1 = -vin 2 vin 1 = v 1 v. P = vin 1 – v 1 = 0 CH 10 Differential Amplifiers 63

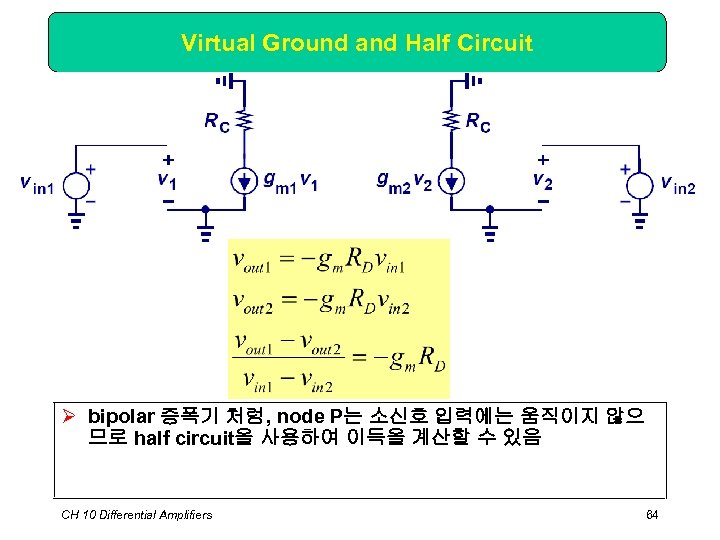

Virtual Ground and Half Circuit Ø bipolar 증폭기 처럼, node P는 소신호 입력에는 움직이지 않으 므로 half circuit을 사용하여 이득을 계산할 수 있음 CH 10 Differential Amplifiers 64

Virtual Ground and Half Circuit Ø bipolar 증폭기 처럼, node P는 소신호 입력에는 움직이지 않으 므로 half circuit을 사용하여 이득을 계산할 수 있음 CH 10 Differential Amplifiers 64

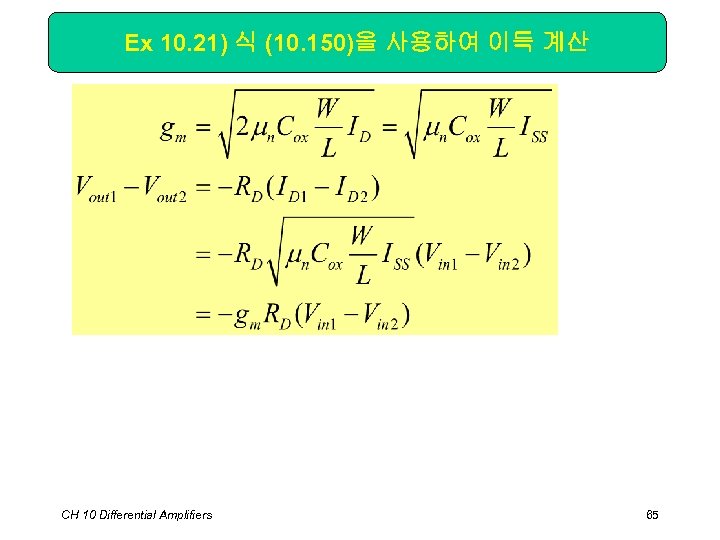

Ex 10. 21) 식 (10. 150)을 사용하여 이득 계산 CH 10 Differential Amplifiers 65

Ex 10. 21) 식 (10. 150)을 사용하여 이득 계산 CH 10 Differential Amplifiers 65

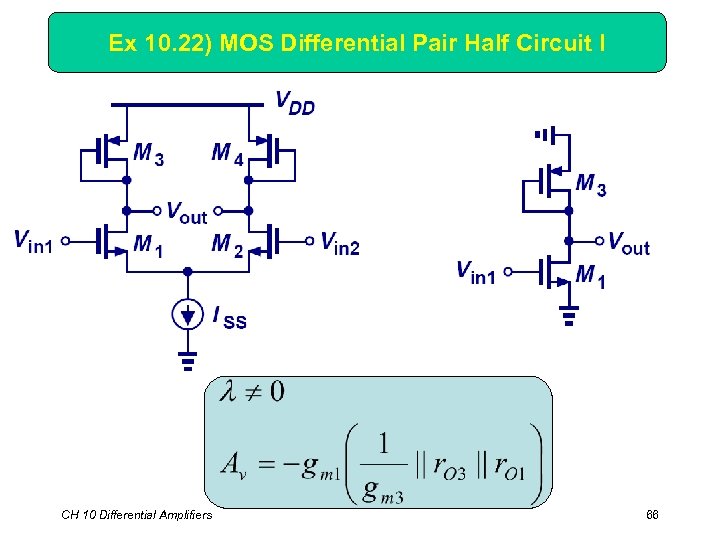

Ex 10. 22) MOS Differential Pair Half Circuit I CH 10 Differential Amplifiers 66

Ex 10. 22) MOS Differential Pair Half Circuit I CH 10 Differential Amplifiers 66

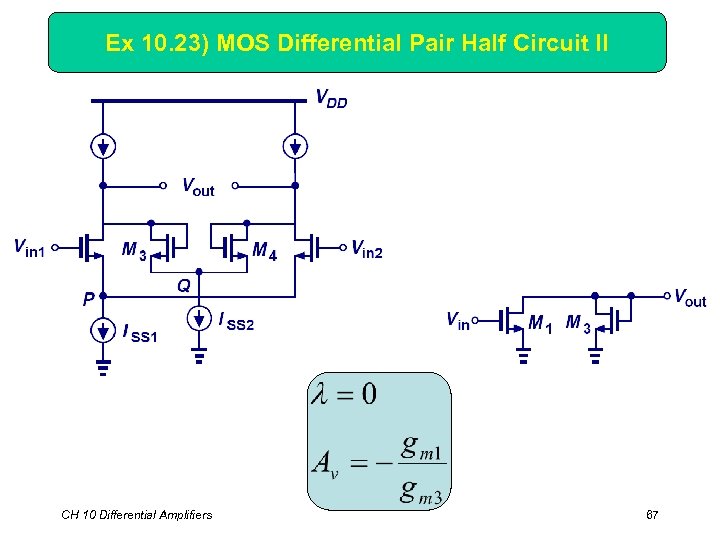

Ex 10. 23) MOS Differential Pair Half Circuit II CH 10 Differential Amplifiers 67

Ex 10. 23) MOS Differential Pair Half Circuit II CH 10 Differential Amplifiers 67

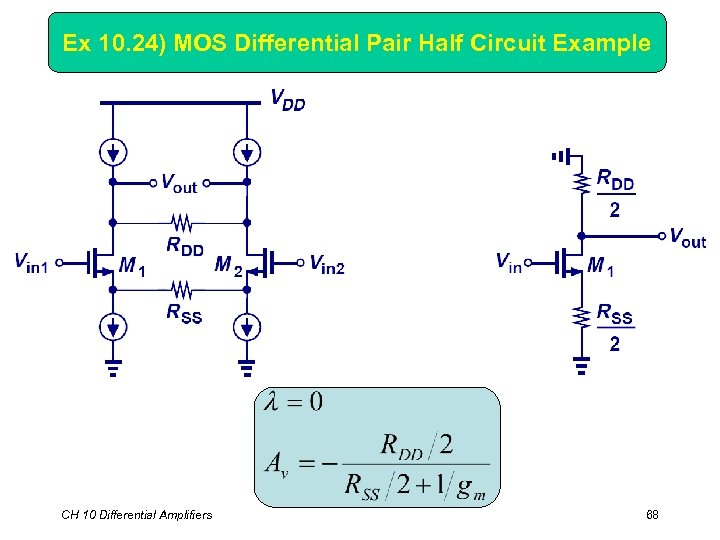

Ex 10. 24) MOS Differential Pair Half Circuit Example CH 10 Differential Amplifiers 68

Ex 10. 24) MOS Differential Pair Half Circuit Example CH 10 Differential Amplifiers 68

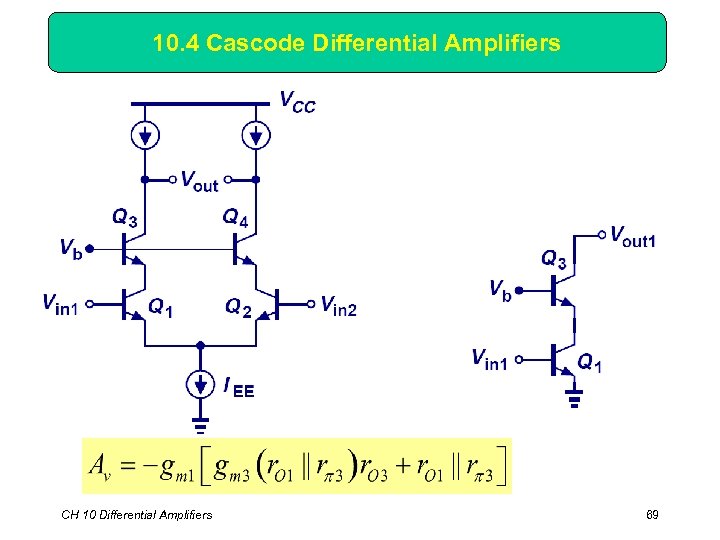

10. 4 Cascode Differential Amplifiers CH 10 Differential Amplifiers 69

10. 4 Cascode Differential Amplifiers CH 10 Differential Amplifiers 69

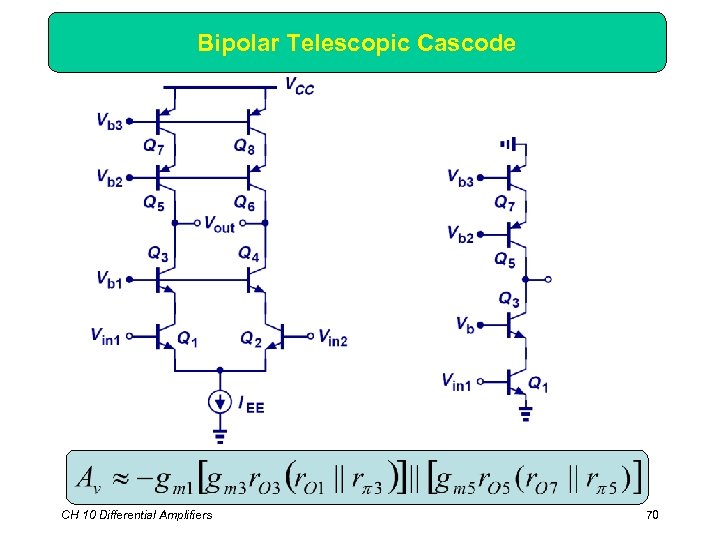

Bipolar Telescopic Cascode CH 10 Differential Amplifiers 70

Bipolar Telescopic Cascode CH 10 Differential Amplifiers 70

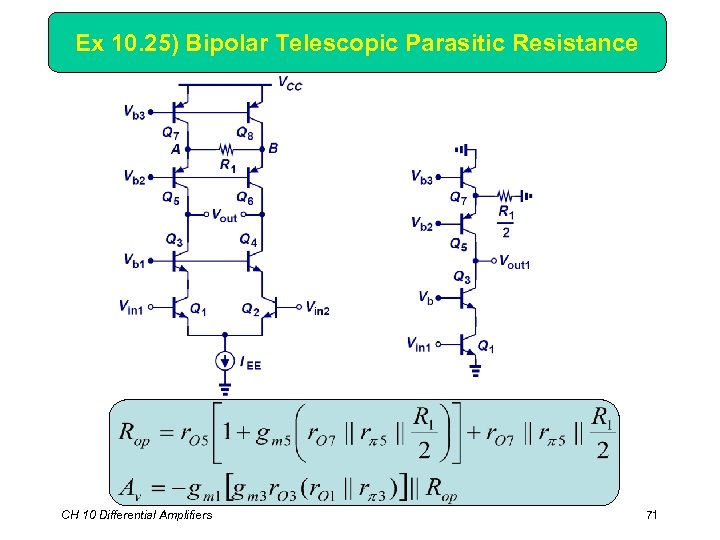

Ex 10. 25) Bipolar Telescopic Parasitic Resistance CH 10 Differential Amplifiers 71

Ex 10. 25) Bipolar Telescopic Parasitic Resistance CH 10 Differential Amplifiers 71

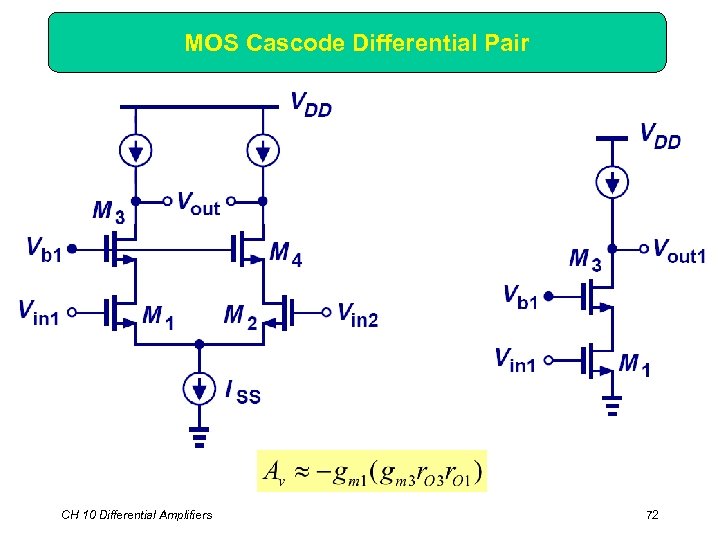

MOS Cascode Differential Pair CH 10 Differential Amplifiers 72

MOS Cascode Differential Pair CH 10 Differential Amplifiers 72

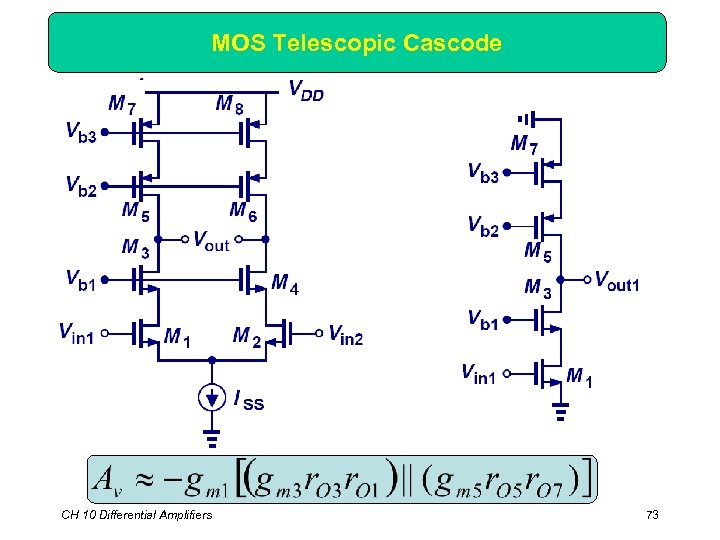

MOS Telescopic Cascode CH 10 Differential Amplifiers 73

MOS Telescopic Cascode CH 10 Differential Amplifiers 73

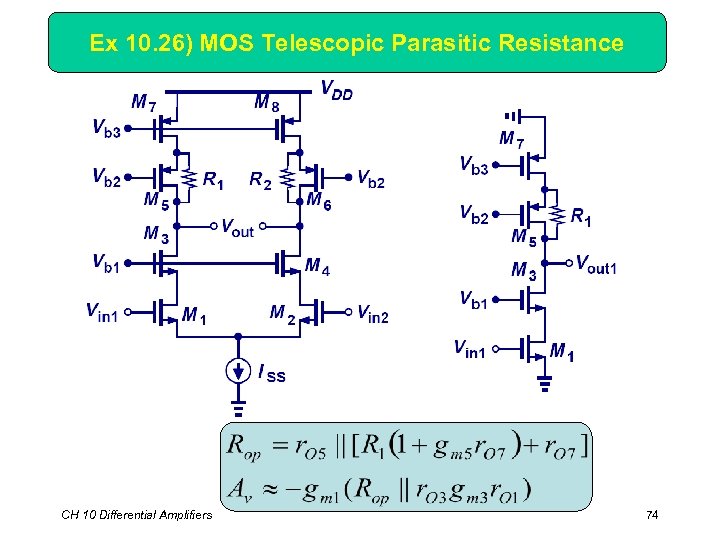

Ex 10. 26) MOS Telescopic Parasitic Resistance CH 10 Differential Amplifiers 74

Ex 10. 26) MOS Telescopic Parasitic Resistance CH 10 Differential Amplifiers 74

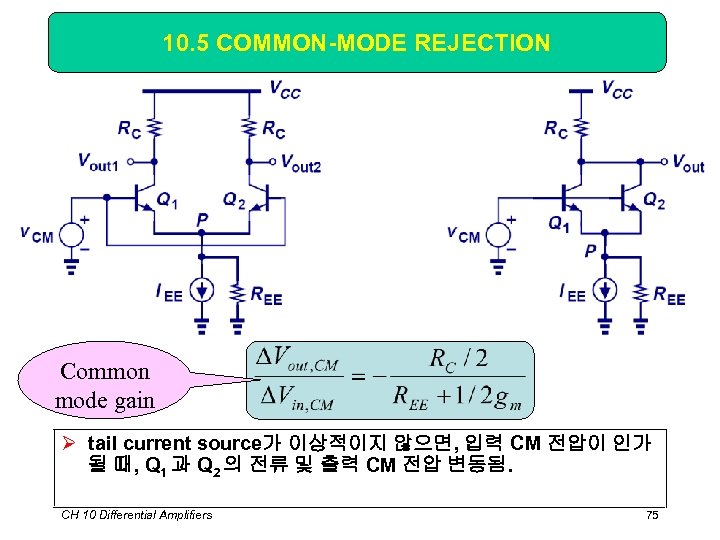

10. 5 COMMON-MODE REJECTION Common mode gain Ø tail current source가 이상적이지 않으면, 입력 CM 전압이 인가 될 때, Q 1 과 Q 2 의 전류 및 출력 CM 전압 변동됨. CH 10 Differential Amplifiers 75

10. 5 COMMON-MODE REJECTION Common mode gain Ø tail current source가 이상적이지 않으면, 입력 CM 전압이 인가 될 때, Q 1 과 Q 2 의 전류 및 출력 CM 전압 변동됨. CH 10 Differential Amplifiers 75

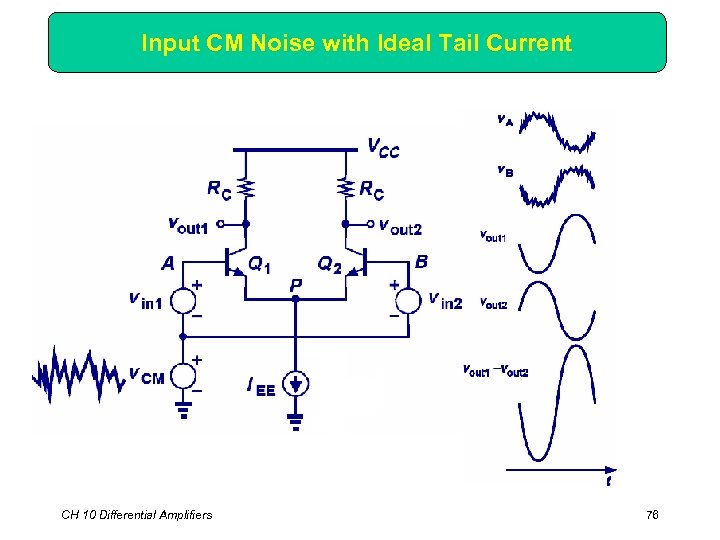

Input CM Noise with Ideal Tail Current CH 10 Differential Amplifiers 76

Input CM Noise with Ideal Tail Current CH 10 Differential Amplifiers 76

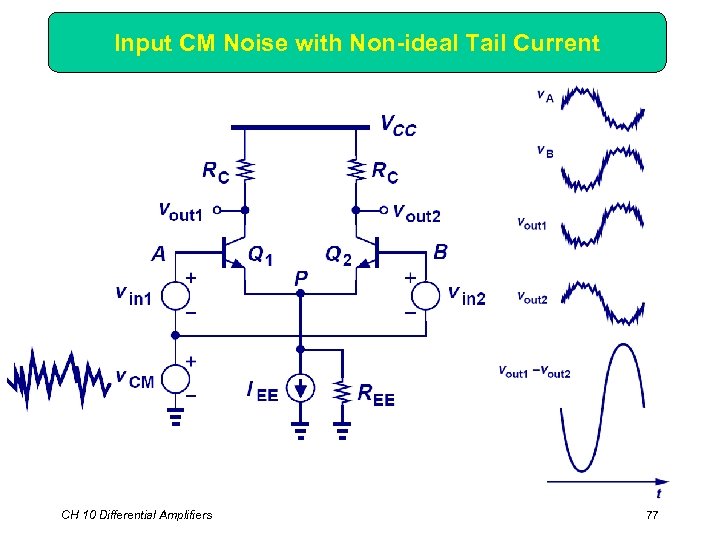

Input CM Noise with Non-ideal Tail Current CH 10 Differential Amplifiers 77

Input CM Noise with Non-ideal Tail Current CH 10 Differential Amplifiers 77

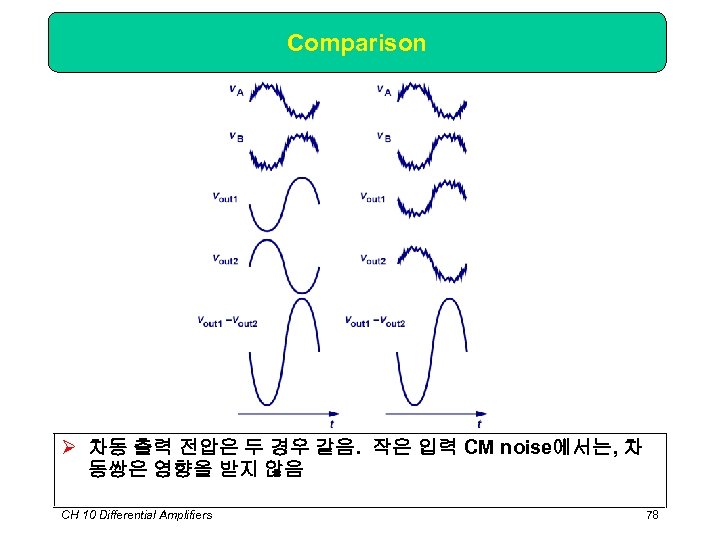

Comparison Ø 차동 출력 전압은 두 경우 같음. 작은 입력 CM noise에서는, 차 동쌍은 영향을 받지 않음 CH 10 Differential Amplifiers 78

Comparison Ø 차동 출력 전압은 두 경우 같음. 작은 입력 CM noise에서는, 차 동쌍은 영향을 받지 않음 CH 10 Differential Amplifiers 78

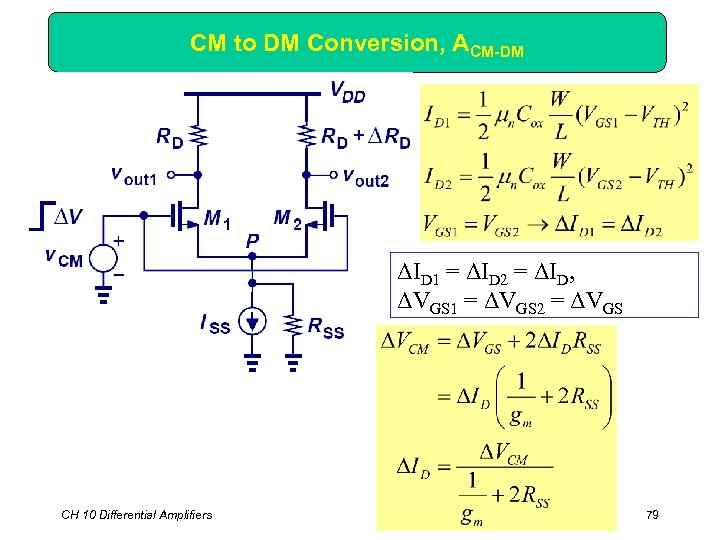

CM to DM Conversion, ACM-DM ΔID 1 = ΔID 2 = ΔID, ΔVGS 1 = ΔVGS 2 = ΔVGS CH 10 Differential Amplifiers 79

CM to DM Conversion, ACM-DM ΔID 1 = ΔID 2 = ΔID, ΔVGS 1 = ΔVGS 2 = ΔVGS CH 10 Differential Amplifiers 79

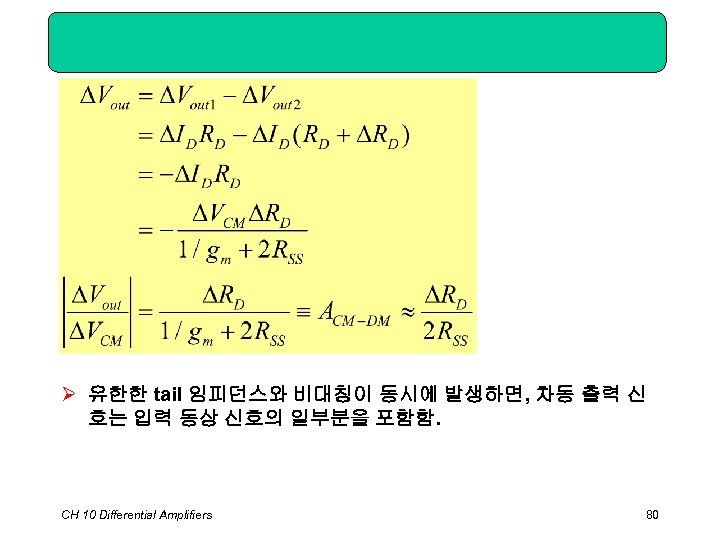

Ø 유한한 tail 임피던스와 비대칭이 동시에 발생하면, 차동 출력 신 호는 입력 동상 신호의 일부분을 포함함. CH 10 Differential Amplifiers 80

Ø 유한한 tail 임피던스와 비대칭이 동시에 발생하면, 차동 출력 신 호는 입력 동상 신호의 일부분을 포함함. CH 10 Differential Amplifiers 80

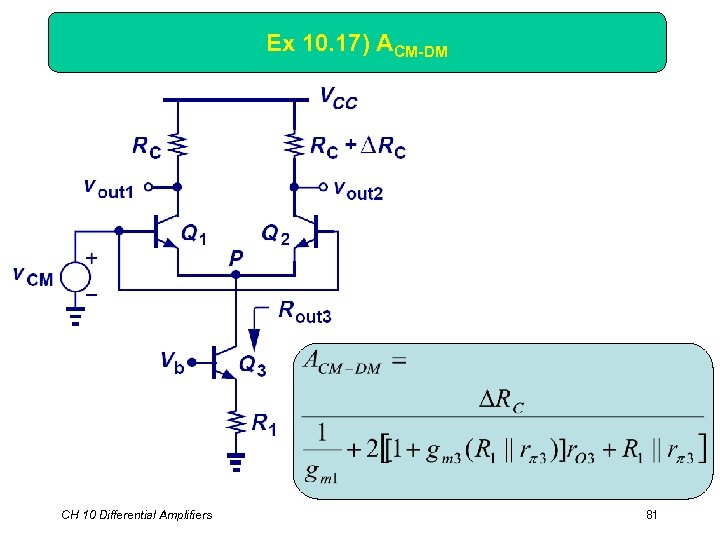

Ex 10. 17) ACM-DM CH 10 Differential Amplifiers 81

Ex 10. 17) ACM-DM CH 10 Differential Amplifiers 81

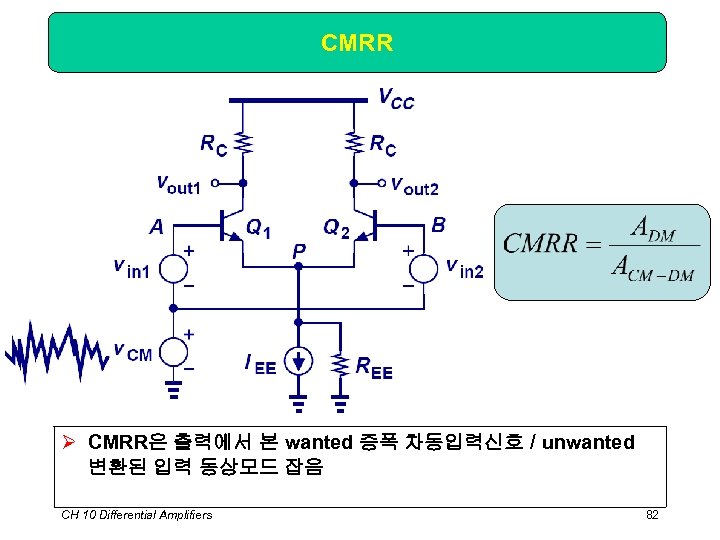

CMRR Ø CMRR은 출력에서 본 wanted 증폭 차동입력신호 / unwanted 변환된 입력 동상모드 잡음 CH 10 Differential Amplifiers 82

CMRR Ø CMRR은 출력에서 본 wanted 증폭 차동입력신호 / unwanted 변환된 입력 동상모드 잡음 CH 10 Differential Amplifiers 82

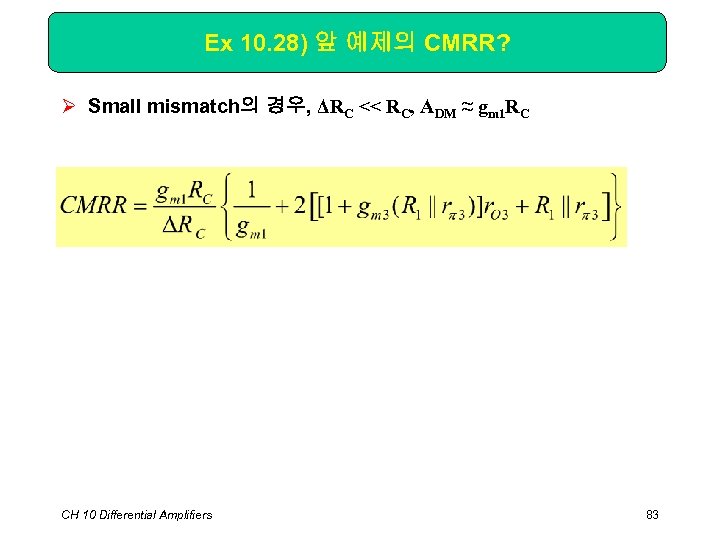

Ex 10. 28) 앞 예제의 CMRR? Ø Small mismatch의 경우, ΔRC << RC, ADM ≈ gm 1 RC CH 10 Differential Amplifiers 83

Ex 10. 28) 앞 예제의 CMRR? Ø Small mismatch의 경우, ΔRC << RC, ADM ≈ gm 1 RC CH 10 Differential Amplifiers 83

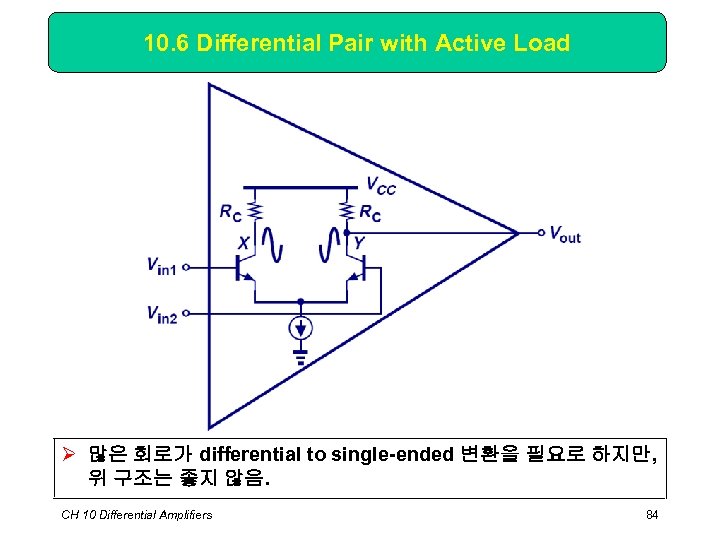

10. 6 Differential Pair with Active Load Ø 많은 회로가 differential to single-ended 변환을 필요로 하지만, 위 구조는 좋지 않음. CH 10 Differential Amplifiers 84

10. 6 Differential Pair with Active Load Ø 많은 회로가 differential to single-ended 변환을 필요로 하지만, 위 구조는 좋지 않음. CH 10 Differential Amplifiers 84

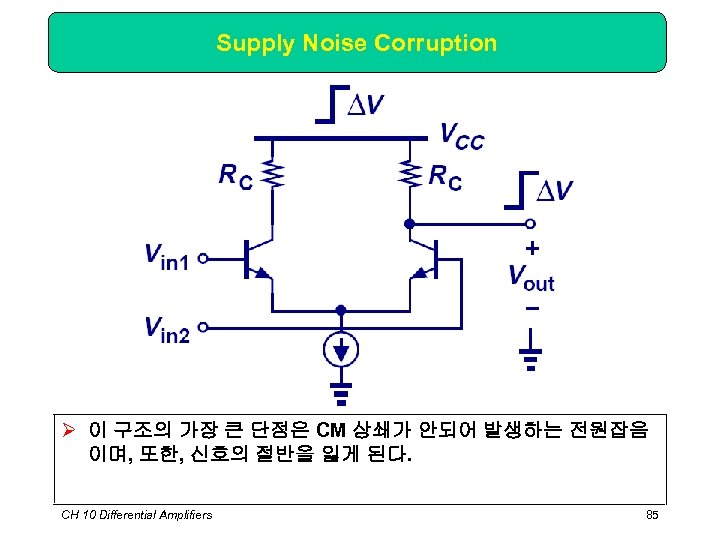

Supply Noise Corruption Ø 이 구조의 가장 큰 단점은 CM 상쇄가 안되어 발생하는 전원잡음 이며, 또한, 신호의 절반을 잃게 된다. CH 10 Differential Amplifiers 85

Supply Noise Corruption Ø 이 구조의 가장 큰 단점은 CM 상쇄가 안되어 발생하는 전원잡음 이며, 또한, 신호의 절반을 잃게 된다. CH 10 Differential Amplifiers 85

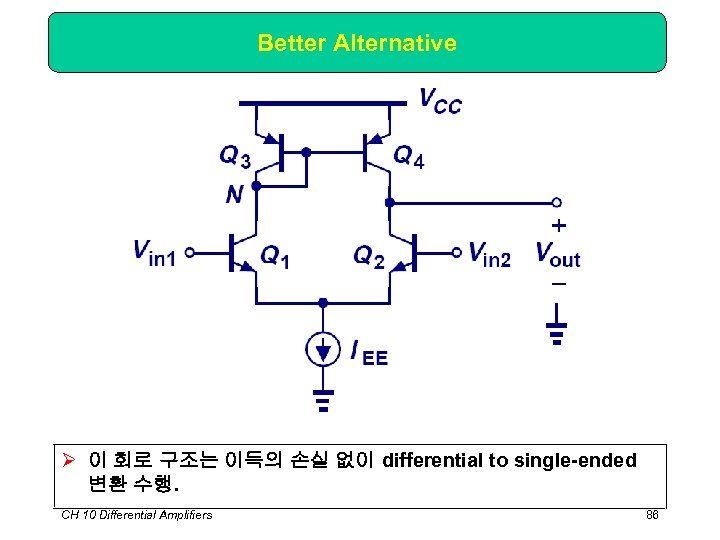

Better Alternative Ø 이 회로 구조는 이득의 손실 없이 differential to single-ended 변환 수행. CH 10 Differential Amplifiers 86

Better Alternative Ø 이 회로 구조는 이득의 손실 없이 differential to single-ended 변환 수행. CH 10 Differential Amplifiers 86

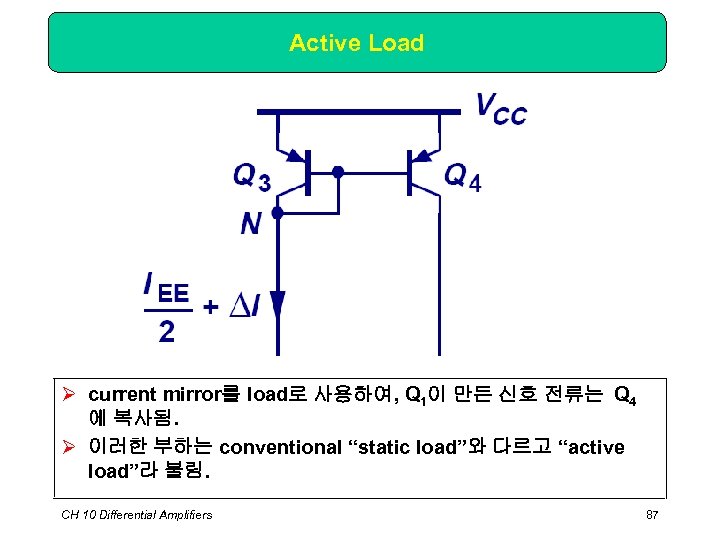

Active Load Ø current mirror를 load로 사용하여, Q 1이 만든 신호 전류는 Q 4 에 복사됨. Ø 이러한 부하는 conventional “static load”와 다르고 “active load”라 불림. CH 10 Differential Amplifiers 87

Active Load Ø current mirror를 load로 사용하여, Q 1이 만든 신호 전류는 Q 4 에 복사됨. Ø 이러한 부하는 conventional “static load”와 다르고 “active load”라 불림. CH 10 Differential Amplifiers 87

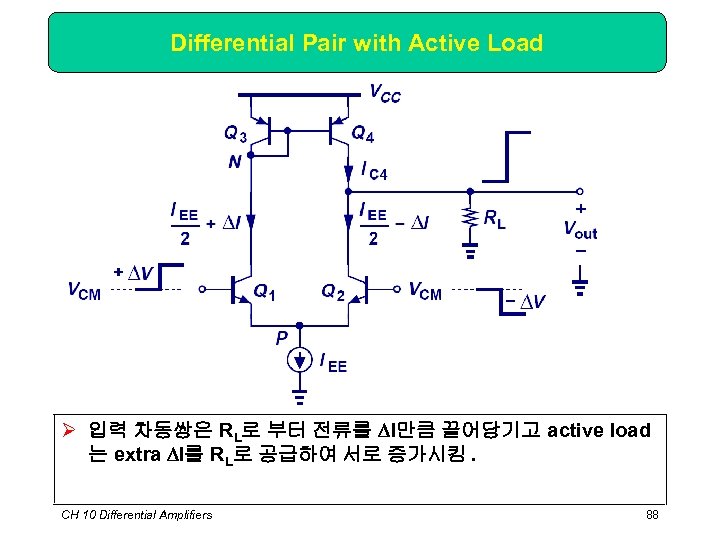

Differential Pair with Active Load Ø 입력 차동쌍은 RL로 부터 전류를 I만큼 끌어당기고 active load 는 extra I를 RL로 공급하여 서로 증가시킴. CH 10 Differential Amplifiers 88

Differential Pair with Active Load Ø 입력 차동쌍은 RL로 부터 전류를 I만큼 끌어당기고 active load 는 extra I를 RL로 공급하여 서로 증가시킴. CH 10 Differential Amplifiers 88

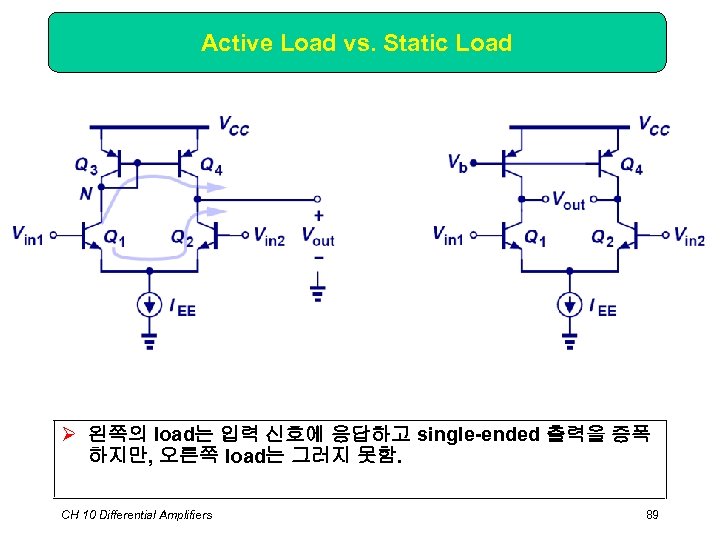

Active Load vs. Static Load Ø 왼쪽의 load는 입력 신호에 응답하고 single-ended 출력을 증폭 하지만, 오른쪽 load는 그러지 못함. CH 10 Differential Amplifiers 89

Active Load vs. Static Load Ø 왼쪽의 load는 입력 신호에 응답하고 single-ended 출력을 증폭 하지만, 오른쪽 load는 그러지 못함. CH 10 Differential Amplifiers 89

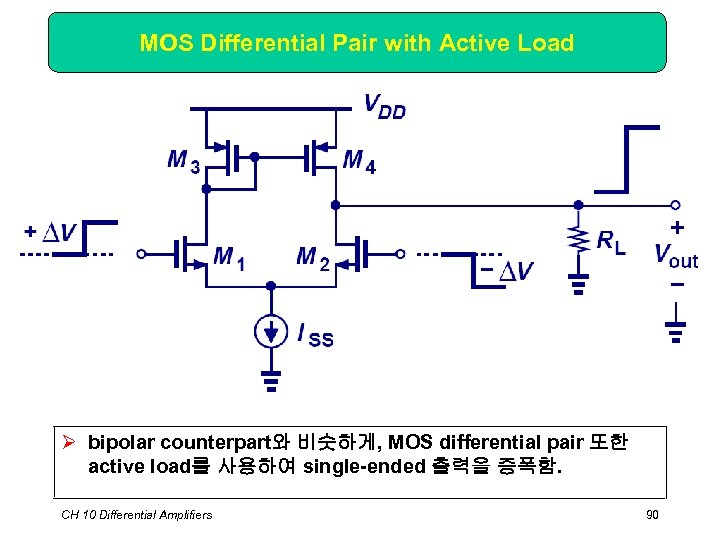

MOS Differential Pair with Active Load Ø bipolar counterpart와 비슷하게, MOS differential pair 또한 active load를 사용하여 single-ended 출력을 증폭함. CH 10 Differential Amplifiers 90

MOS Differential Pair with Active Load Ø bipolar counterpart와 비슷하게, MOS differential pair 또한 active load를 사용하여 single-ended 출력을 증폭함. CH 10 Differential Amplifiers 90

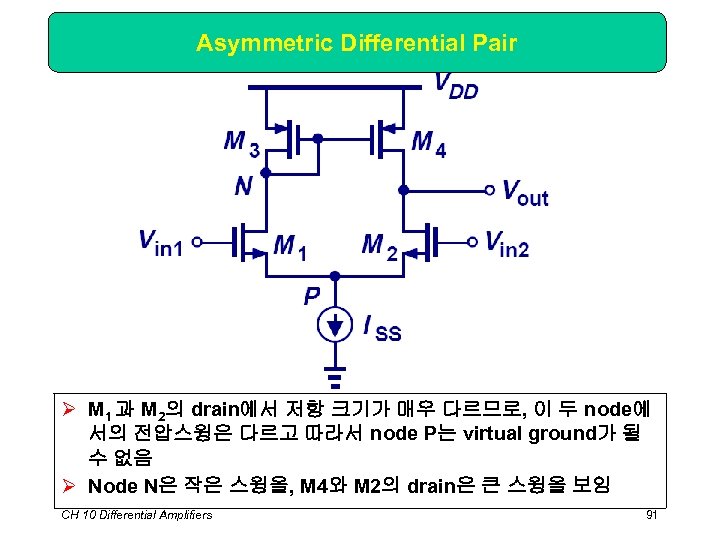

Asymmetric Differential Pair Ø M 1 과 M 2의 drain에서 저항 크기가 매우 다르므로, 이 두 node에 서의 전압스윙은 다르고 따라서 node P는 virtual ground가 될 수 없음 Ø Node N은 작은 스윙을, M 4와 M 2의 drain은 큰 스윙을 보임 CH 10 Differential Amplifiers 91

Asymmetric Differential Pair Ø M 1 과 M 2의 drain에서 저항 크기가 매우 다르므로, 이 두 node에 서의 전압스윙은 다르고 따라서 node P는 virtual ground가 될 수 없음 Ø Node N은 작은 스윙을, M 4와 M 2의 drain은 큰 스윙을 보임 CH 10 Differential Amplifiers 91

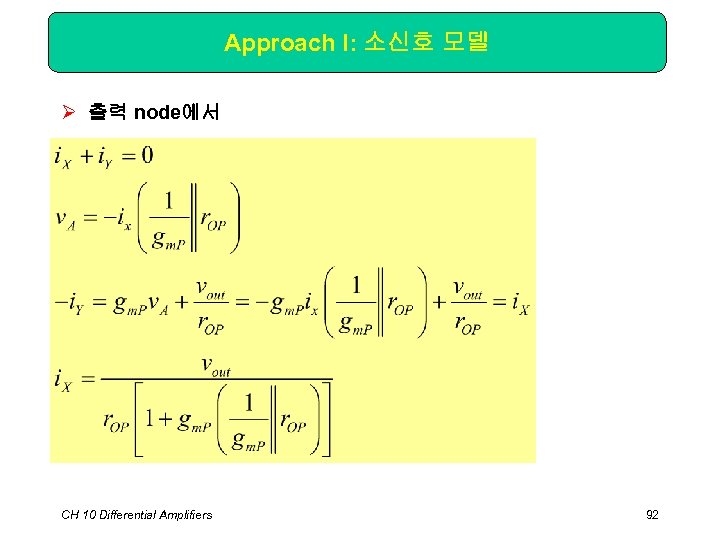

Approach I: 소신호 모델 Ø 출력 node에서 CH 10 Differential Amplifiers 92

Approach I: 소신호 모델 Ø 출력 node에서 CH 10 Differential Amplifiers 92

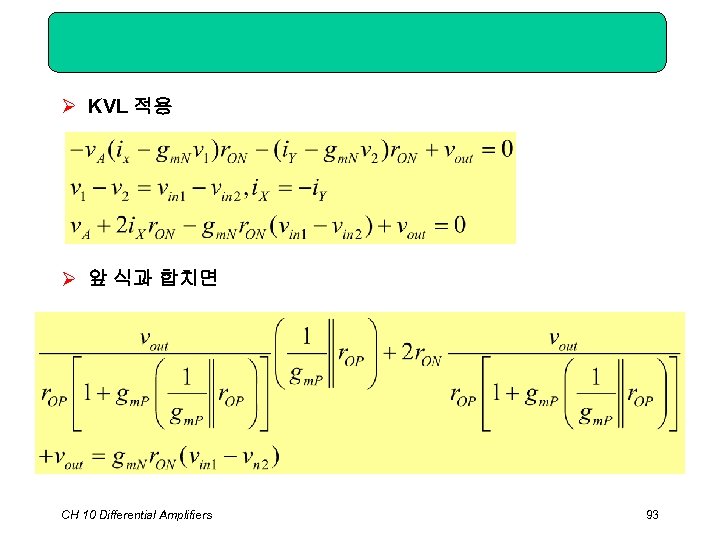

Ø KVL 적용 Ø 앞 식과 합치면 CH 10 Differential Amplifiers 93

Ø KVL 적용 Ø 앞 식과 합치면 CH 10 Differential Amplifiers 93

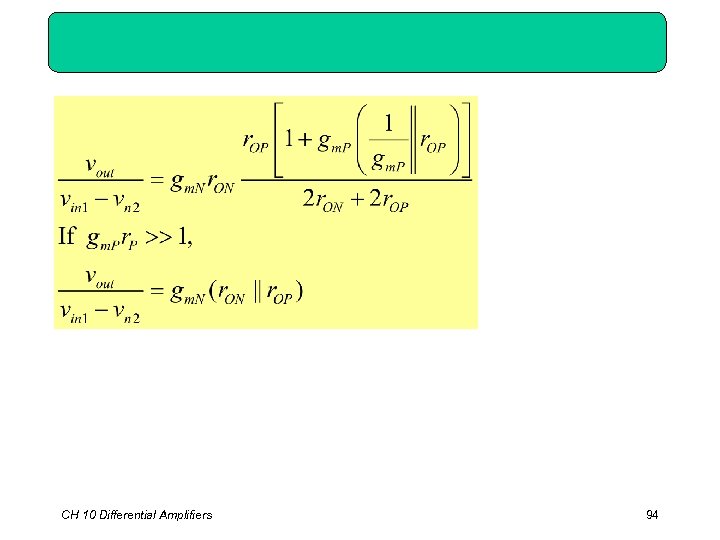

CH 10 Differential Amplifiers 94

CH 10 Differential Amplifiers 94

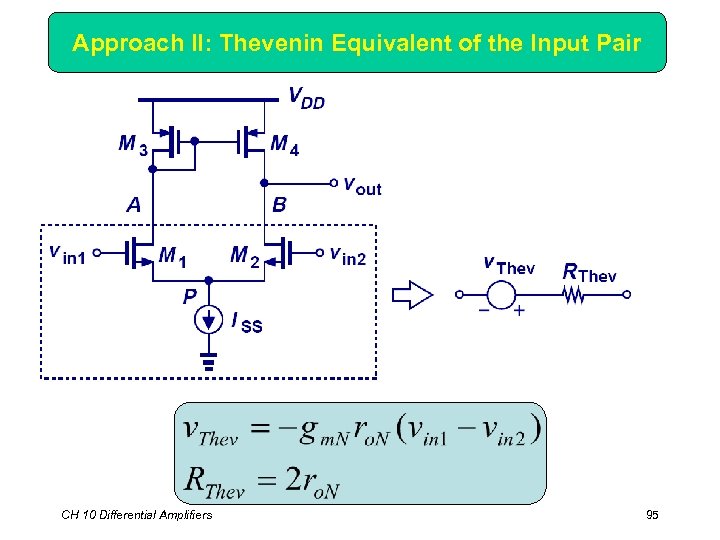

Approach II: Thevenin Equivalent of the Input Pair CH 10 Differential Amplifiers 95

Approach II: Thevenin Equivalent of the Input Pair CH 10 Differential Amplifiers 95

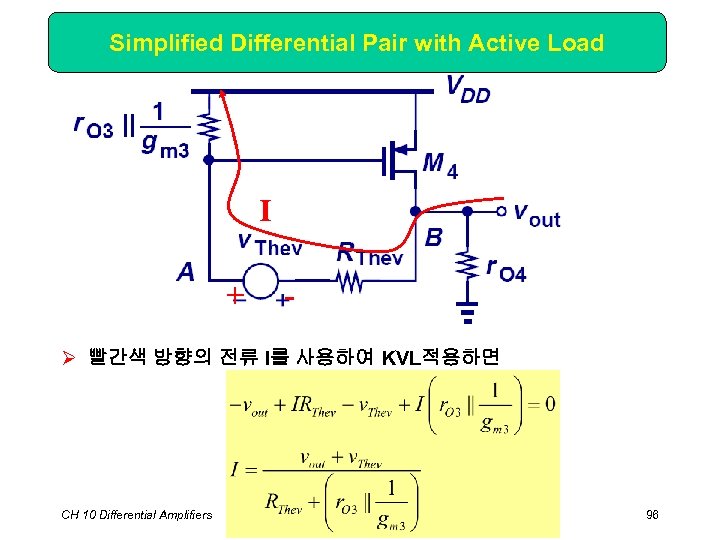

Simplified Differential Pair with Active Load I + - Ø 빨간색 방향의 전류 I를 사용하여 KVL적용하면 CH 10 Differential Amplifiers 96

Simplified Differential Pair with Active Load I + - Ø 빨간색 방향의 전류 I를 사용하여 KVL적용하면 CH 10 Differential Amplifiers 96

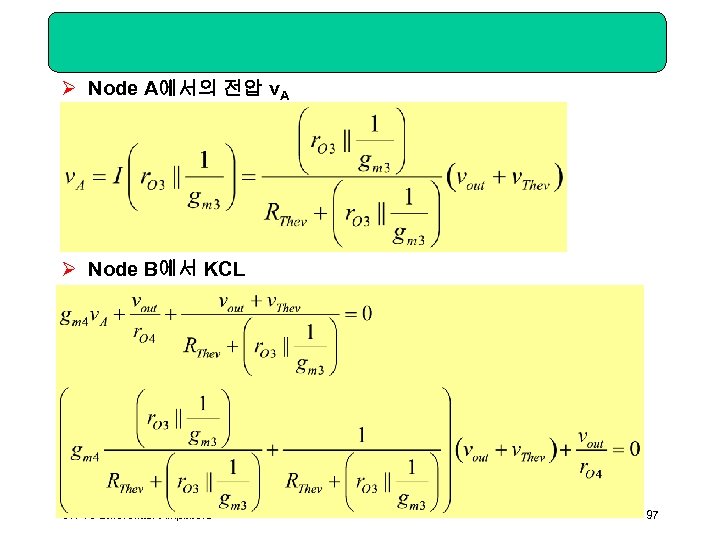

Ø Node A에서의 전압 v. A Ø Node B에서 KCL CH 10 Differential Amplifiers 97

Ø Node A에서의 전압 v. A Ø Node B에서 KCL CH 10 Differential Amplifiers 97

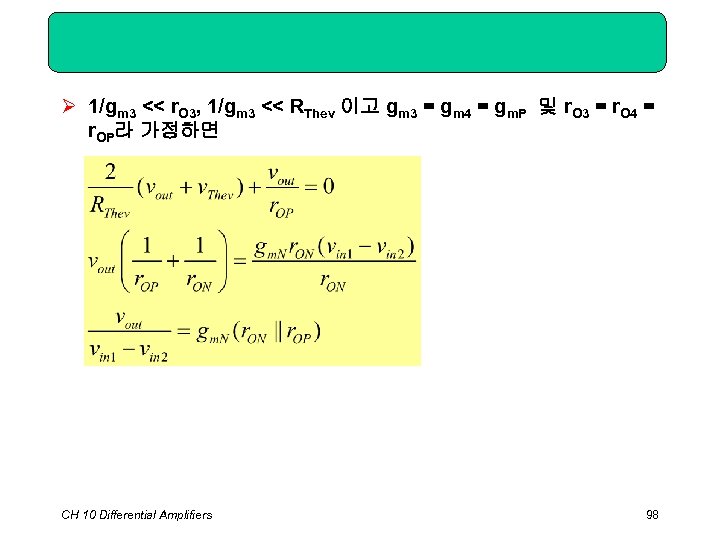

Ø 1/gm 3 << r. O 3, 1/gm 3 << RThev 이고 gm 3 = gm 4 = gm. P 및 r. O 3 = r. O 4 = r. OP라 가정하면 CH 10 Differential Amplifiers 98

Ø 1/gm 3 << r. O 3, 1/gm 3 << RThev 이고 gm 3 = gm 4 = gm. P 및 r. O 3 = r. O 4 = r. OP라 가정하면 CH 10 Differential Amplifiers 98

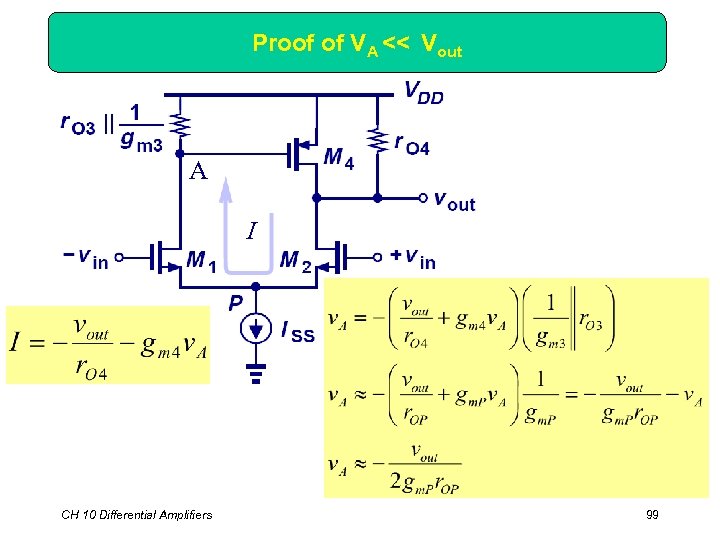

Proof of VA << Vout A I CH 10 Differential Amplifiers 99

Proof of VA << Vout A I CH 10 Differential Amplifiers 99