ОТМП_3у-2011.ppt

- Количество слайдов: 29

Ч 1. Лекция 3 КОМБИНАЦИОННЫЕ УСТРОЙСТВА Лектор: Люличева И. А. 1

Рассматриваются вопросы n n n Дешифраторы Шифраторы Сумматоры Этапы и проблемы синтеза комбинационных устройств Синтез комбинационного устройства преобразователя кода 2

3. 1 Дешифраторы n n n Дешифратор - это устройство, предназначенное для преобразования параллельного двоичного кода в унитарный код. Обычно, указанный в схеме номер вывода дешифратора соответствует десятичному эквиваленту двоичного кода, подаваемого на вход дешифратора в качестве входных переменных, вернее сказать, что при подаче на вход устройства параллельного двоичного кода на выходе дешифратора появится сигнал на том выходе, номер которого соответствует десятичному эквиваленту двоичного кода.

3. 3 Дешифраторы n n n В любой момент времени выходной сигнал будет иметь место только на одном выходе дешифратора. В зависимости от типа дешифратора, этот сигнал может иметь как уровень логической единицы (при этом на всех остальных выходах уровень логического 0), так и уровень логического 0 (при этом на всех остальных выходах уровень логической 1). Существуют дешифраторы 2 ® 4, 3 ® 8, 4 ® 16 и т. д. Рассмотрим пример синтеза дешифратора (полного) 3 ® 8, следовательно, количество разрядов двоичного числа - 3, количество выходов - 8.

Таблица состояний дешифратора 3 “ 8 X 1 Х 2 Х 3 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 Y 8 0 0 1 1 0 1 0 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

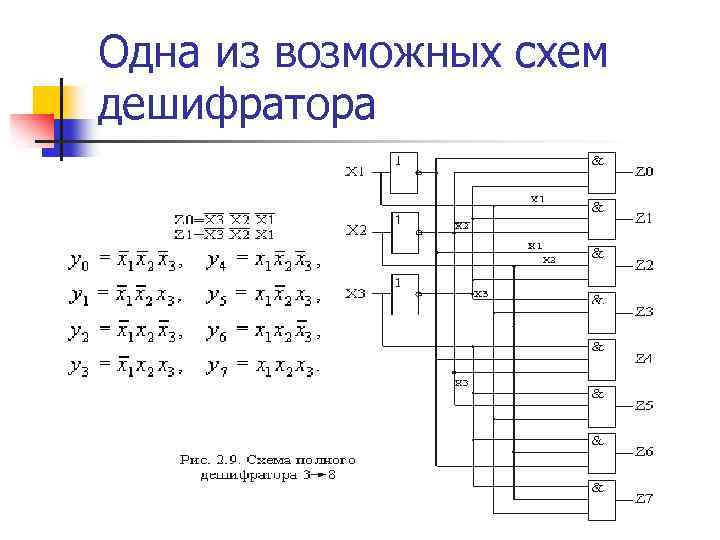

Одна из возможных схем дешифратора

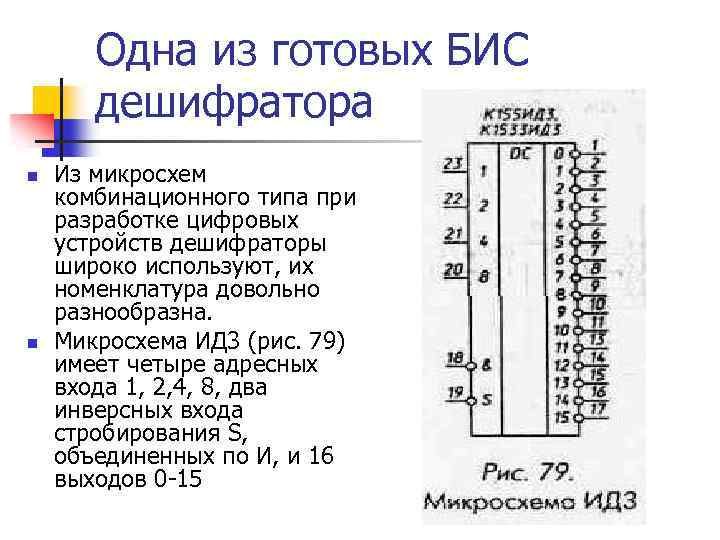

Одна из готовых БИС дешифратора n n Из микросхем комбинационного типа при разработке цифровых устройств дешифраторы широко используют, их номенклатура довольно разнообразна. Микросхема ИД 3 (рис. 79) имеет четыре адресных входа 1, 2, 4, 8, два инверсных входа стробирования S, объединенных по И, и 16 выходов 0 -15

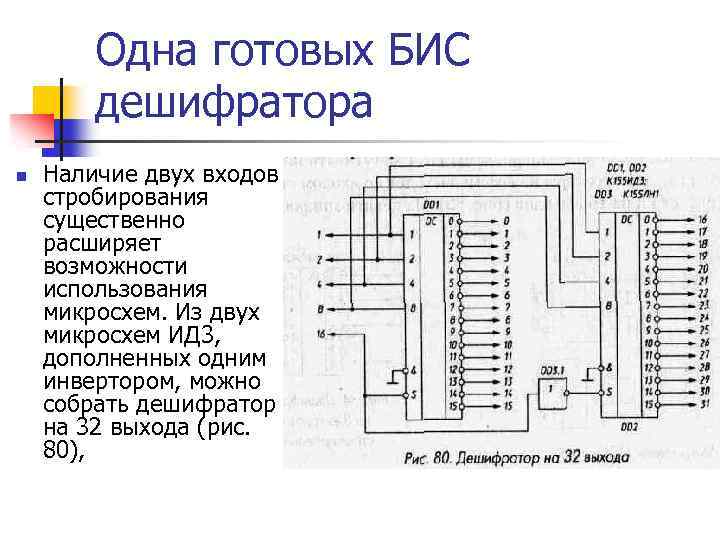

Одна готовых БИС дешифратора n Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем ИД 3, дополненных одним инвертором, можно собрать дешифратор на 32 выхода (рис. 80),

Одна готовых БИС дешифратора n а дешифратор на 256 выходов - из 17 микросхем ИД 3 (рис 82)

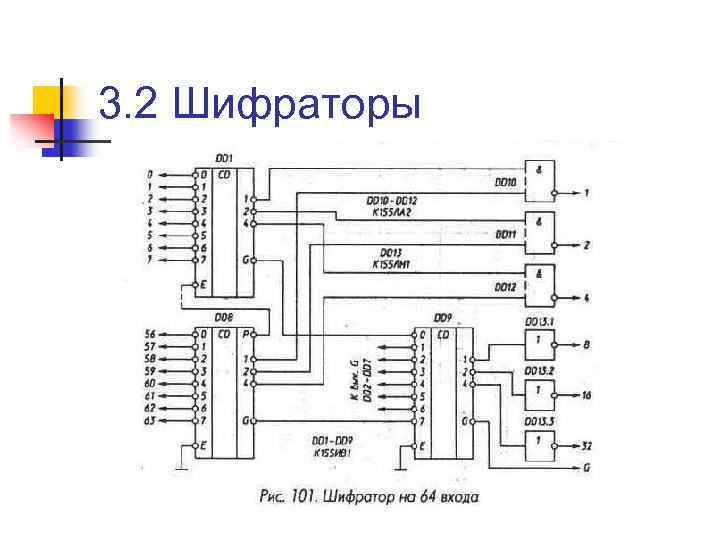

3. 2 Шифраторы n n n Шифратор — логическое устройство, выполняющее преобразование позиционного (унитарного) кода в n-разрядный двоичный код. Таким образом, шифратор - это комбинационное устройство, реализующее обратную дешифратору функцию. Шифраторы (телекоммуникации) http: //www. vizir-company. com/scrembler. html Шифраторы(защита инф. ) – др. дисциплины!

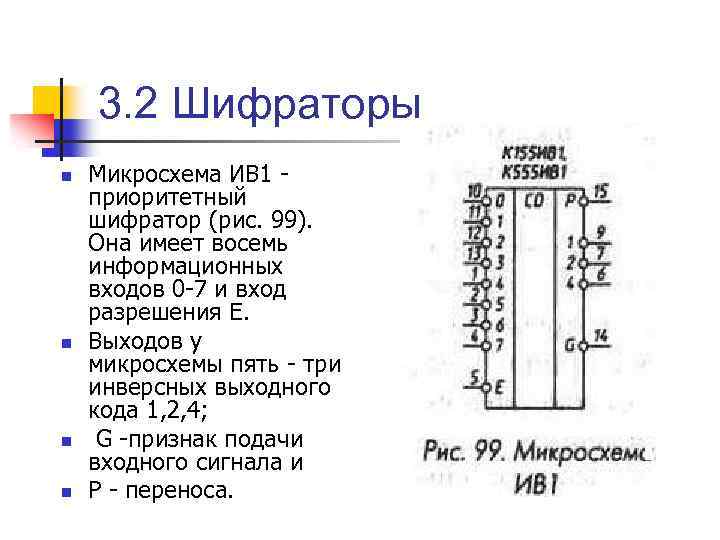

3. 2 Шифраторы n n Микросхема ИВ 1 - приоритетный шифратор (рис. 99). Она имеет восемь информационных входов 0 -7 и вход разрешения Е. Выходов у микросхемы пять - три инверсных выходного кода 1, 2, 4; G -признак подачи входного сигнала и Р - переноса.

3. 2 Шифраторы

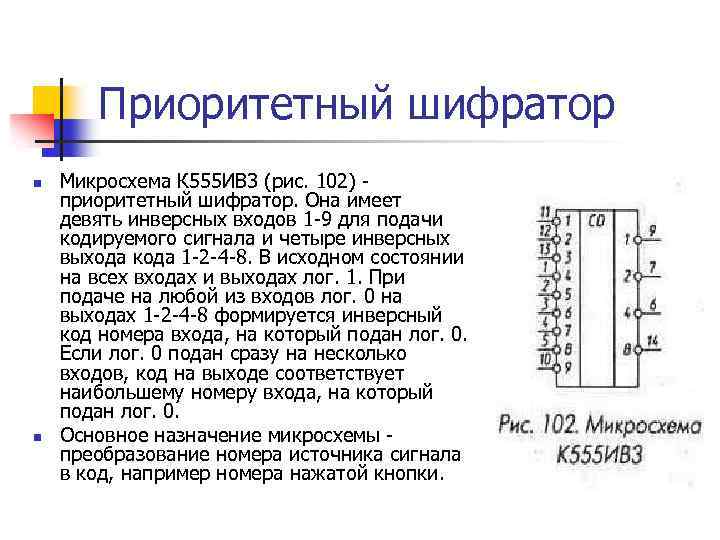

Приоритетный шифратор n n Микросхема К 555 ИВ 3 (рис. 102) - приоритетный шифратор. Она имеет девять инверсных входов 1 -9 для подачи кодируемого сигнала и четыре инверсных выхода кода 1 -2 -4 -8. В исходном состоянии на всех входах и выходах лог. 1. При подаче на любой из входов лог. 0 на выходах 1 -2 -4 -8 формируется инверсный код номера входа, на который подан лог. 0. Если лог. 0 подан сразу на несколько входов, код на выходе соответствует наибольшему номеру входа, на который подан лог. 0. Основное назначение микросхемы - преобразование номера источника сигнала в код, например номера нажатой кнопки.

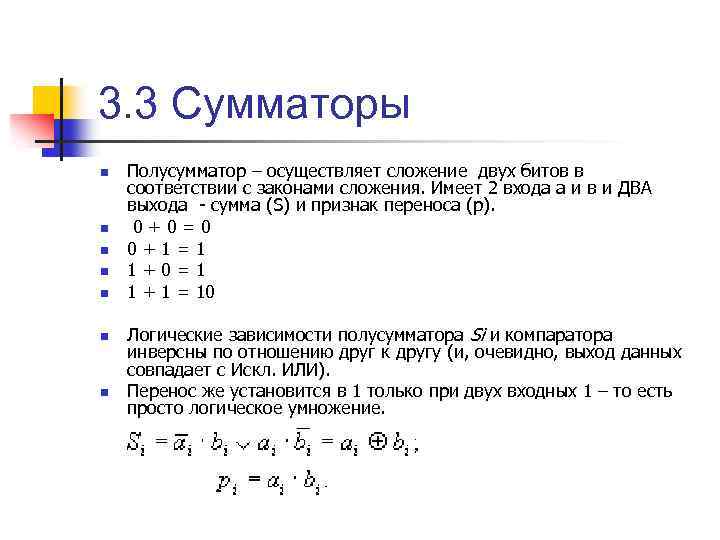

3. 3 Сумматоры n n n n Полусумматор – осуществляет сложение двух битов в соответствии с законами сложения. Имеет 2 входа а и в и ДВА выхода - сумма (S) и признак переноса (р). 0 + 0 = 0 0 + 1 = 1 1 + 0 = 1 1 + 1 = 10 Логические зависимости полусумматора Si и компаратора инверсны по отношению друг к другу (и, очевидно, выход данных совпадает с Искл. ИЛИ). Перенос же установится в 1 только при двух входных 1 – то есть просто логическое умножение.

3. 3 Сумматоры n Внизу приведена одна из возможных схм реализации полусумматора и ее графическое обозначение.

3. 3 Сумматоры Уравнения, положенные в основу одноразрядного сумматора, используются и при построении многоразрядных сумматоров. Логика работы каждого разряда сумматора описывается таблицей, приведенной на следующем слайде, которую можно считать его таблицей истинности.

Таблица истинности сумматора ai bi Pi-1 S Pi 0 0 0 1 1 0 0 1 … 1 1 0 0 1 1 … 1

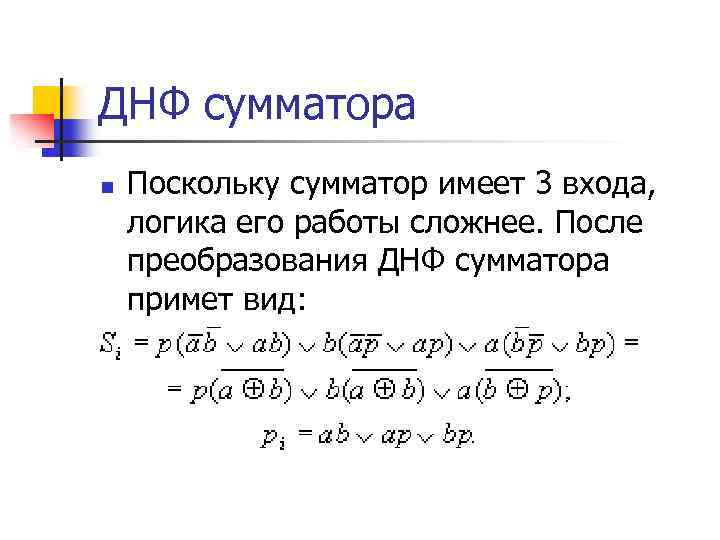

ДНФ сумматора n Поскольку сумматор имеет 3 входа, логика его работы сложнее. После преобразования ДНФ сумматора примет вид:

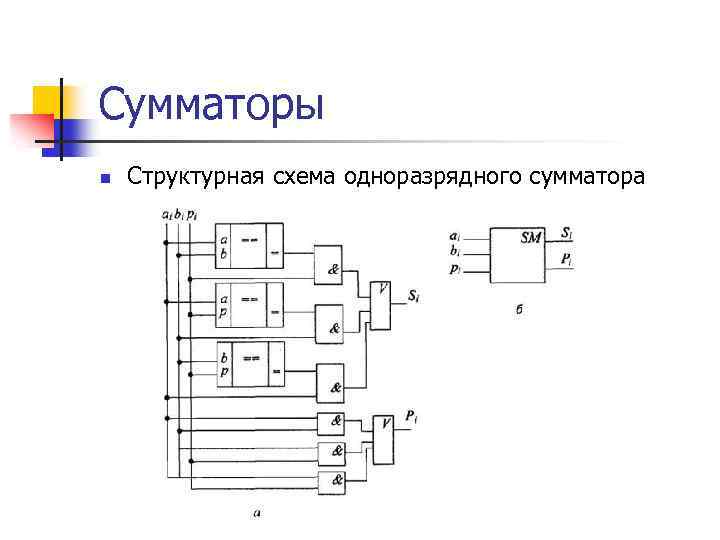

Сумматоры n Структурная схема одноразрядного сумматора

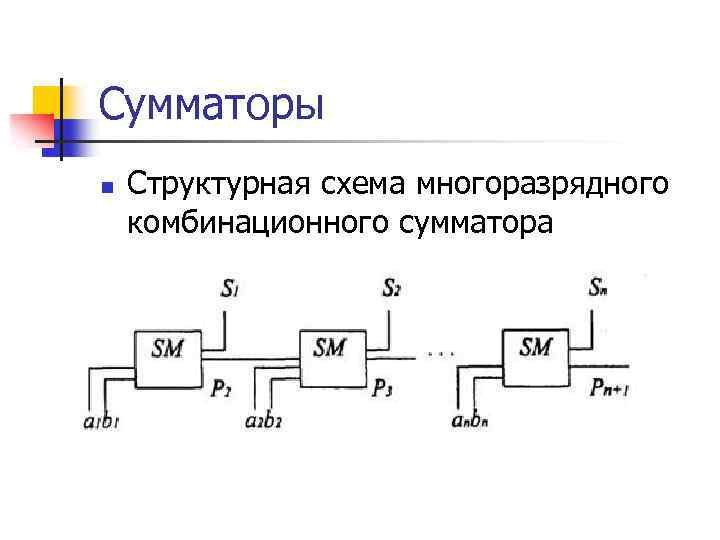

Сумматоры n Структурная схема многоразрядного комбинационного сумматора

3. 4 Основные этапы синтеза комбинационных устройств В задачу синтеза комбинационных устройств входит построение схемы устройства по заданным условиям его работы и при заданном базисе элементов. Задание комбинационного устройства сводится к заданию тех функций, которые оно должно реализовать. Число функций определяется числом выходов комбинационного устройства. Процесс синтеза состоит из 2 -х этапов. 1. Абстрактный синтез n формирование задачи, определение типа устройства; n описание устройства на формализованных языках: таблица истинности, карта Карно, аналитическое выражение и т. д. ; n минимизация булевых функций; n построение логической схемы устройства. 2. Схемный синтез n

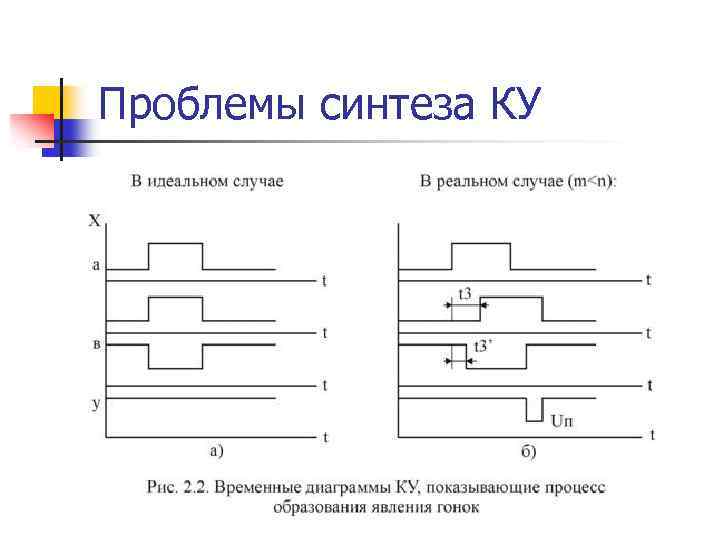

Проблемы синтеза КУ n n Комбинационное устройство (КУ) - это устройство с m входами и n выходами. Если КУ выполнено на базе идеальных, элементов, состояние выходов однозначно определяется состоянием входов в тот же момент времени. Однако, инерционность элементов и наличие различных факторов, приводящих к задержке распространения сигнала, приводят к задержке появления выходных сигналов КУ, т. е. сигналы на выходе КУ, появляются не сразу, а с некоторой задержкой. При этом в переходный период возможно появление на выходах устройства некоторых промежуточных значений сигналов, не соответствующих заданному состоянию устройства. Такое явление получило название состязаний или гонок. Обычно, вырабатываемые узлами КУ промежуточные значения сигналов, представляют собой импульсы очень малой длительности. Они могут запускать непредусмотренное срабатывание триггеров, счетчиков и осуществлять нежелательные записи в регистры.

Проблемы синтеза КУ

Проблемы синтеза КУ

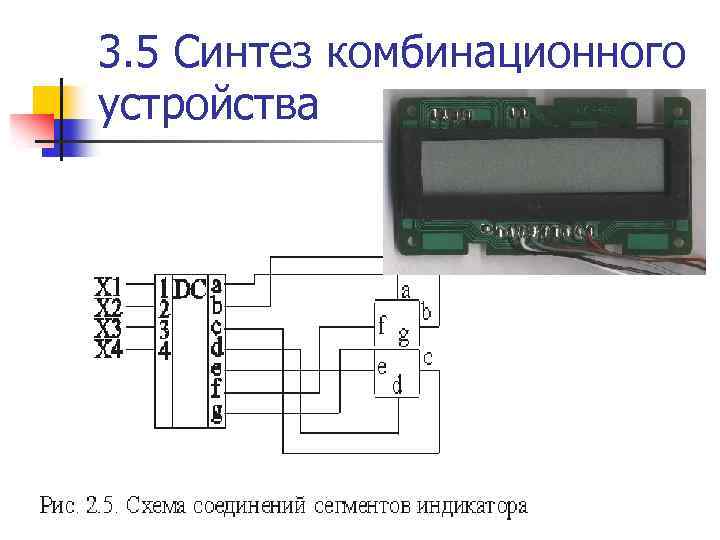

3. 5 Синтез комбинационного устройства n n n Рассмотрим пример реализации преобразователя кода для семисегментных индикаторов. Будем считать, что светодиодные семисегментные индикаторы выполнены с общим катодом, т. е. сегменты высвечиваются при подаче на них уровня логической единицы. Преобразователь кода представим в виде дешифратора с семью выходами (количество выходов КУ равно количеству реализуемых функций). Обозначение сегментов индикатора стандартное (от а до g).

3. 5 Синтез комбинационного устройства

3. 5 Синтез комбинационного устройства n n n Для зажигания цифры 1 необходимо подать уровни логической “ 1” на сегменты “b” и “c” и т. д. Преобразователь предназначен для индикации цифр десятичной системы счисления, и поэтому значения функций для наборов переменных, начиная с номера 10, для индикатора безразличны. Безразличные значения функций обозначены знаком ~ (тильда). После заполнения таблицы состояния устройства составляются аналитические выражения (СНДФ) для каждой функции и строятся карты Карно.

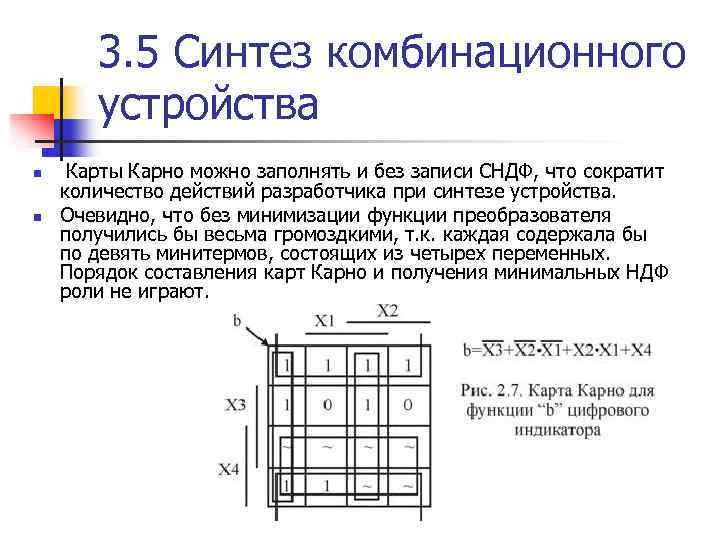

3. 5 Синтез комбинационного устройства n n Карты Карно можно заполнять и без записи СНДФ, что сократит количество действий разработчика при синтезе устройства. Очевидно, что без минимизации функции преобразователя получились бы весьма громоздкими, т. к. каждая содержала бы по девять минитермов, состоящих из четырех переменных. Порядок составления карт Карно и получения минимальных НДФ роли не играют.

Вопросы для самоконтроля 1. Что такое гонки при синтезе КУ? 2. Для чего применяются карты Карно? 3. Приведите таблицу истинности дешифратора 2 на 4. 4. Какие комбинационные устройства вам известны? 5. Отличие полусумматора от сумматора. 6. Таблица истинности сумматора. 29

ОТМП_3у-2011.ppt