7ae8a660807b6bc8f886b345ca69a089.ppt

- Количество слайдов: 28

CENTRE FORMAL DESIGN AND VERIFICATION OF SOFTWARE INDIAN INSTITUTE OF TECHNOLOGY, BOMBAY

CENTRE FORMAL DESIGN AND VERIFICATION OF SOFTWARE INDIAN INSTITUTE OF TECHNOLOGY, BOMBAY

Verification & Validation (V&V) n n Computers everywhere Safety-critical Systems § Aircrafts, Trains, Nuclear & Industrial Plants, Avionics § Life Support Systems n Quality of Computational Systems = Quality of life

Verification & Validation (V&V) n n Computers everywhere Safety-critical Systems § Aircrafts, Trains, Nuclear & Industrial Plants, Avionics § Life Support Systems n Quality of Computational Systems = Quality of life

Bugs are costly n Pentium bug n n n ARIANE Failure n n n Intel Pentium chip, released in 1994 produced error in floating point division Cost : $475 million In December 1996, the Ariane 5 rocket exploded 40 seconds after take off. A software components threw an exception Cost : $400 million payload. Therac-25 Accident : n n A software failure caused wrong dosages of x-rays. Cost: Human Loss. Rigorous V&V Essential

Bugs are costly n Pentium bug n n n ARIANE Failure n n n Intel Pentium chip, released in 1994 produced error in floating point division Cost : $475 million In December 1996, the Ariane 5 rocket exploded 40 seconds after take off. A software components threw an exception Cost : $400 million payload. Therac-25 Accident : n n A software failure caused wrong dosages of x-rays. Cost: Human Loss. Rigorous V&V Essential

Traditional V & V n n n Industrial Practices far from satisfactory Testing, Simulation, Reviews & Walkthroughs Inadequate for safety-critical systems Late Detection of bugs Detects presence of bugs not absence When to stop testing n n Coverage criteria ~70% of time spent on V&V

Traditional V & V n n n Industrial Practices far from satisfactory Testing, Simulation, Reviews & Walkthroughs Inadequate for safety-critical systems Late Detection of bugs Detects presence of bugs not absence When to stop testing n n Coverage criteria ~70% of time spent on V&V

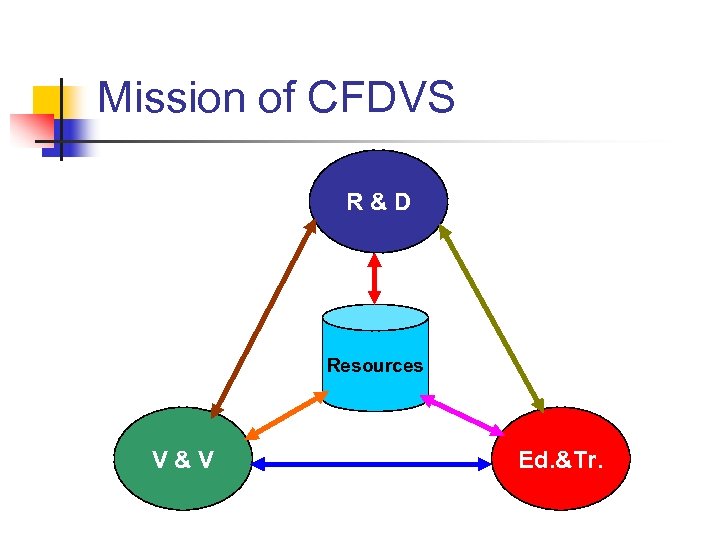

Mission of CFDVS R&D Resources V&V Ed. &Tr.

Mission of CFDVS R&D Resources V&V Ed. &Tr.

The Mission n To Enable, through R&D of new tools and Techniques, n to Support through external projects, n to Educate to develop skill base n n through courses & workshops to Develop Resource Base of tools, technologies, standards n RIGOROUS DESIGN, V & V PRACTICES

The Mission n To Enable, through R&D of new tools and Techniques, n to Support through external projects, n to Educate to develop skill base n n through courses & workshops to Develop Resource Base of tools, technologies, standards n RIGOROUS DESIGN, V & V PRACTICES

CFDVS Focus Area n n V & V based on Formal Methods Safety-critical Systems Hardware & Software Industrial Solutions

CFDVS Focus Area n n V & V based on Formal Methods Safety-critical Systems Hardware & Software Industrial Solutions

Formal Verification n n More rigorous approach Founded on Mathematical methods Proves correctness of Systems Increased confidence Early Detection of bugs n n Design Verification Complementary to traditional techniques

Formal Verification n n More rigorous approach Founded on Mathematical methods Proves correctness of Systems Increased confidence Early Detection of bugs n n Design Verification Complementary to traditional techniques

CFDVS – An R&D Centre n n Research Projects Case-studies New Tools Efficient Techniques and Novel Design Methodologies

CFDVS – An R&D Centre n n Research Projects Case-studies New Tools Efficient Techniques and Novel Design Methodologies

CFDVS – A Resource Centre n n n Specification & Verification Tools Academic & Commercial Tools Books, Papers & Reports Hardware & Software support V&V Expert consultancy National Centre

CFDVS – A Resource Centre n n n Specification & Verification Tools Academic & Commercial Tools Books, Papers & Reports Hardware & Software support V&V Expert consultancy National Centre

CFDVS – An Educational Centre n n Education & Training Courses & Seminars Workshops & Conferences Student Projects & Case studies

CFDVS – An Educational Centre n n Education & Training Courses & Seminars Workshops & Conferences Student Projects & Case studies

Resources Hardware : n n n Dec Alpha server Sun-Fire 280 R Many access stations Software: n n n Formal Check: Hardware Verification Tool(Cadence Inc. ) LDRA : Static analysis tool Rose RT and Rhapsody : UML based tools Esterel Studio and SCADE Specman: Hardware Verification tool Code Surfer: Slicing tool

Resources Hardware : n n n Dec Alpha server Sun-Fire 280 R Many access stations Software: n n n Formal Check: Hardware Verification Tool(Cadence Inc. ) LDRA : Static analysis tool Rose RT and Rhapsody : UML based tools Esterel Studio and SCADE Specman: Hardware Verification tool Code Surfer: Slicing tool

Resources (contd. ) Books : n n More than hundred books/proceedings CAV, FMCAD, CHARME

Resources (contd. ) Books : n n More than hundred books/proceedings CAV, FMCAD, CHARME

Education and Training n n n Attracted many students across different departments (CSE, IT, EE, Rel. Engg. ) Around 30 students (B. Tech and M. Tech) completed More than 10 students currently working Two BARC staff on deputation Two workshops n n n Well-attended People from DAE and other organization Tutorials in international conferences

Education and Training n n n Attracted many students across different departments (CSE, IT, EE, Rel. Engg. ) Around 30 students (B. Tech and M. Tech) completed More than 10 students currently working Two BARC staff on deputation Two workshops n n n Well-attended People from DAE and other organization Tutorials in international conferences

Industry Sponsored Projects n n n IV & V services Two projects completed Two more projects in Progress Looking forward to more Means of Resource Generation

Industry Sponsored Projects n n n IV & V services Two projects completed Two more projects in Progress Looking forward to more Means of Resource Generation

Formal Verification of Flight Software: Sponsor : ADA , Bangalore n Validation of software in LCA display unit n Verification focused on a collection of Cfunctions n In house tool ACE extensively used (jointly developed with BARC) n Verification engine : STe. P n Verification uncovered a few bugs leading to code revision n Designers convinced of utility of FV

Formal Verification of Flight Software: Sponsor : ADA , Bangalore n Validation of software in LCA display unit n Verification focused on a collection of Cfunctions n In house tool ACE extensively used (jointly developed with BARC) n Verification engine : STe. P n Verification uncovered a few bugs leading to code revision n Designers convinced of utility of FV

Verification of Cache controllers Sponsor : Texas Instruments, Bangalore n n n Verification using Model Checking of medium sized industrial design. Cache controller developed at TI, Formal. Check of Cadence Inc. - verifier

Verification of Cache controllers Sponsor : Texas Instruments, Bangalore n n n Verification using Model Checking of medium sized industrial design. Cache controller developed at TI, Formal. Check of Cadence Inc. - verifier

Verification of LV Software n n n LV – Launch Vehicle Sponsored by VSSC, Trivandrum Signal integrity checking Complex sequence of branches Code in Ada In-house tool ACE used

Verification of LV Software n n n LV – Launch Vehicle Sponsored by VSSC, Trivandrum Signal integrity checking Complex sequence of branches Code in Ada In-house tool ACE used

Verification of In-house ASICs Sponsor : BARC n Various ASICs designed at BARC n Verification of one of these n Project in the initial stages

Verification of In-house ASICs Sponsor : BARC n Various ASICs designed at BARC n Verification of one of these n Project in the initial stages

CFDVS R&D Overview n n Case-studies Tools n n n ACE TSCheck Con. SDE VE-DAC EX-PERT Research Papers and Reports

CFDVS R&D Overview n n Case-studies Tools n n n ACE TSCheck Con. SDE VE-DAC EX-PERT Research Papers and Reports

Case-Studies n n FV of Two Systems from BARC FV of a PCI implementation

Case-Studies n n FV of Two Systems from BARC FV of a PCI implementation

FV of PCI implementation n n n Understand issues involved in large hardware design Evaluate the performance of state-of-the art tools PCI implementation (10, 000 lines of VHDL code) The tool Formal Check used Models for environment designed Properties formalized in FQL

FV of PCI implementation n n n Understand issues involved in large hardware design Evaluate the performance of state-of-the art tools PCI implementation (10, 000 lines of VHDL code) The tool Formal Check used Models for environment designed Properties formalized in FQL

ACE – Assertion checker n n n Assertion-checking tool formal verification of C-Programs Translates C functions plus assertions to SPL and specifications Verification of SPL programs STe. P – Verification Engine Tool extensively used in ADA project

ACE – Assertion checker n n n Assertion-checking tool formal verification of C-Programs Translates C functions plus assertions to SPL and specifications Verification of SPL programs STe. P – Verification Engine Tool extensively used in ADA project

Design Environment for Process Control Software n n n Con. SDE: A tool for designing process control software from high level block diagrams A graphical editor A block definition language Code generation from blocks Simulation capabilities Verification capabilities planned

Design Environment for Process Control Software n n n Con. SDE: A tool for designing process control software from high level block diagrams A graphical editor A block definition language Code generation from blocks Simulation capabilities Verification capabilities planned

Verification Environment for distributed Control Applications n n n VE-DAC and EX-PERT: Tool for verification of distributed reactive applications. State machine based language Capabilities to design concurrent and hierarchical design Asynchronous communication Editor, simulator and verifier Efficient verification using slicing techniques

Verification Environment for distributed Control Applications n n n VE-DAC and EX-PERT: Tool for verification of distributed reactive applications. State machine based language Capabilities to design concurrent and hierarchical design Asynchronous communication Editor, simulator and verifier Efficient verification using slicing techniques

Probabilistic Interface Timing Verification n Efficient computation of n n Bounds on the probability of violation of timing requirements Bounds on performance metrics of the aggregate system Given statistical information about component delays and the timing requirements of ckts A dynamic programming algorithm n n n A polynomial time algorithm implemented and tested on some benchmarks bounds are fairly accurate in practice

Probabilistic Interface Timing Verification n Efficient computation of n n Bounds on the probability of violation of timing requirements Bounds on performance metrics of the aggregate system Given statistical information about component delays and the timing requirements of ckts A dynamic programming algorithm n n n A polynomial time algorithm implemented and tested on some benchmarks bounds are fairly accurate in practice

Timing Analysis and Verification of Gate-level Asynchronous Circuits n n detect potential timing violations in a timed Asynchronous circuit Useful for timing verification of practical timed ckts. n n n Polynomial-time algorithm for accurate detection of transition ordering Algorithm to compute delay parameters of generalized C-elements Algorithms faster than simulation using SPICE or IRSIM

Timing Analysis and Verification of Gate-level Asynchronous Circuits n n detect potential timing violations in a timed Asynchronous circuit Useful for timing verification of practical timed ckts. n n n Polynomial-time algorithm for accurate detection of transition ordering Algorithm to compute delay parameters of generalized C-elements Algorithms faster than simulation using SPICE or IRSIM

. . . And many more Projects n n n Efficient Verification of Synchronous Programs Model-based Verification of Object. Oriented Software Slicing of Synchronous Programs and HDLs

. . . And many more Projects n n n Efficient Verification of Synchronous Programs Model-based Verification of Object. Oriented Software Slicing of Synchronous Programs and HDLs