0dcd1d1e885de5b6f44b1403cae2dec9.ppt

- Количество слайдов: 96

Build a better life with Balsa A Hands-on Tutorial Session Andrew Bardsley John Bainbridge Amulet Group, Department of Computer Science, University of Manchester, UK ACi. D Summer School 2002 Balsa Tutorial: - 1

Balsa Tutorials n Async 2000 (Eilat) • Concentrated on language aspects • Xilinx implementation of calculator n Async 2002 (Manchester) • Larger exercise (SSEM) • Standard cell implementations n This tutorial • Language and Handshake Circuits • Much larger exercise (Spamulet 0) • Buy the book - ISBN 0 -792 -37613 -7 ACi. D Summer School 2002 Balsa Tutorial: - 2

Aims of this tutorial n To show Balsa in a large(ish) example • Simulate that example • Modify its description (? ) n Not including: • Detailed examination Handshake Circuits • Synthesis to netlists • Implementation details ACi. D Summer School 2002 Balsa Tutorial: - 3

Session Schedule Brief overview of the Balsa system n Language introduction n • hands-on examples • “Shift Registers”: small pipelines n Either: • Modify a processor description (add new instructions and simulate) • Read some Balsa examples and try a simpler example (Rotate Right) ACi. D Summer School 2002 Balsa Tutorial: - 4

The Balsa Team Doug Edwards Team Leader Luis Plana Dual Rail Back-end Andrew Bardsley Chief Architect/Implementer Will Toms 1 -of-4 Back-end Lilian Janin balsa-mgr/LARD ACi. D Summer School 2002 Balsa Tutorial: - 5

Balsa Requirements n Freely available • ftp: //ftp. cs. man. ac. uk/pub/amulet/balsa/ • http: //www. cs. man. ac. uk/amulet/ • not all back-ends available n OS requirements: • Linux • Sun Solaris 7 -8 (today’s platform) • Mac. OS X (+ X 11 R 6 …) ACi. D Summer School 2002 Balsa Tutorial: - 6

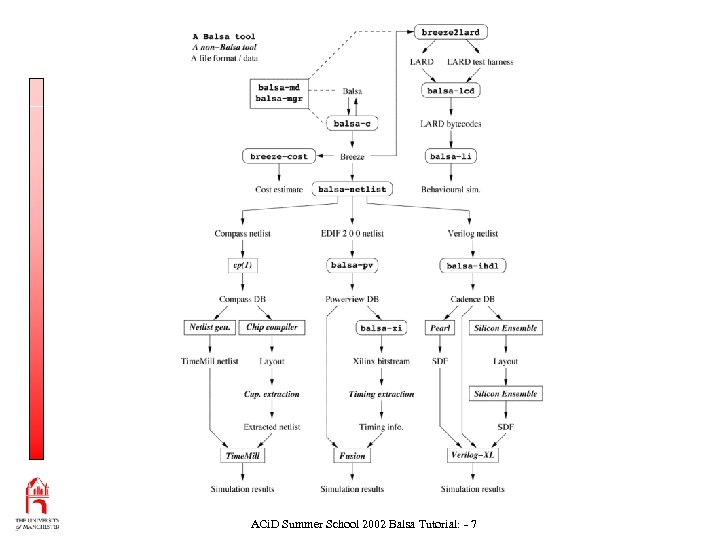

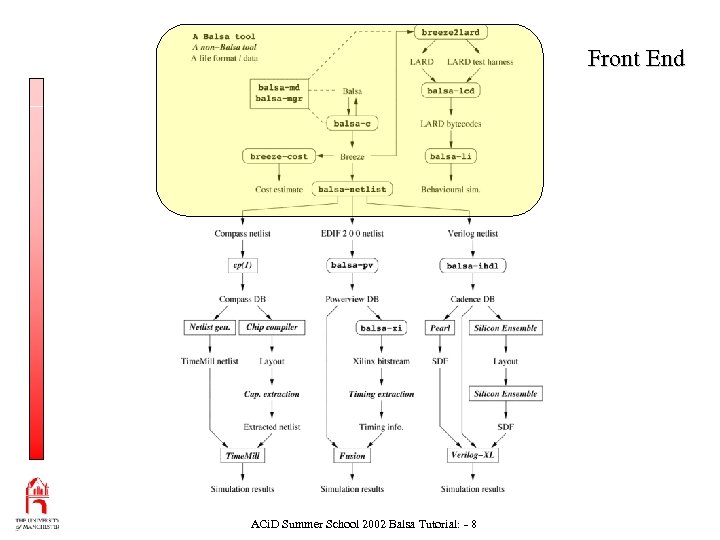

ACi. D Summer School 2002 Balsa Tutorial: - 7

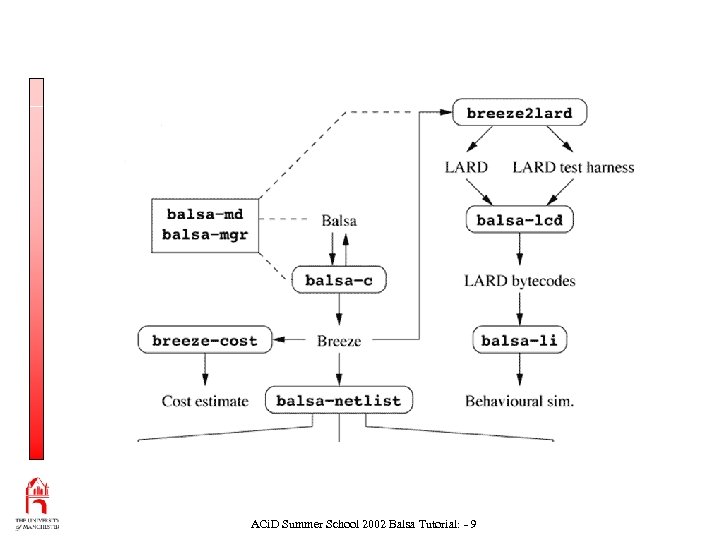

Front End ACi. D Summer School 2002 Balsa Tutorial: - 8

ACi. D Summer School 2002 Balsa Tutorial: - 9

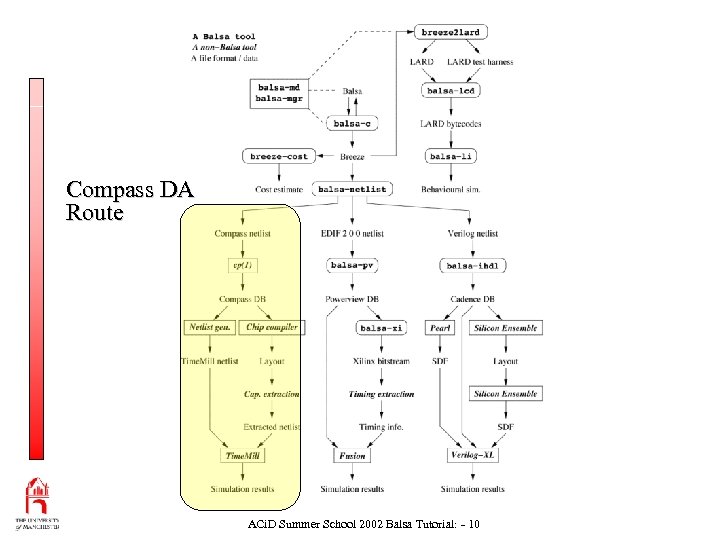

Compass DA Route ACi. D Summer School 2002 Balsa Tutorial: - 10

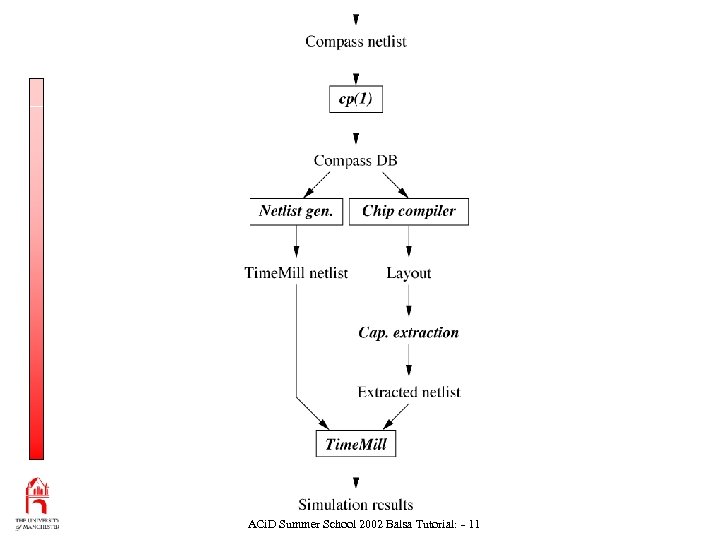

ACi. D Summer School 2002 Balsa Tutorial: - 11

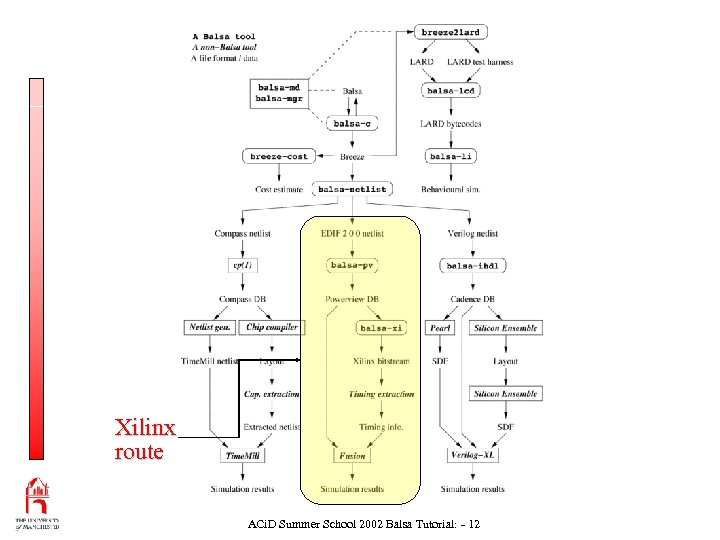

Xilinx route ACi. D Summer School 2002 Balsa Tutorial: - 12

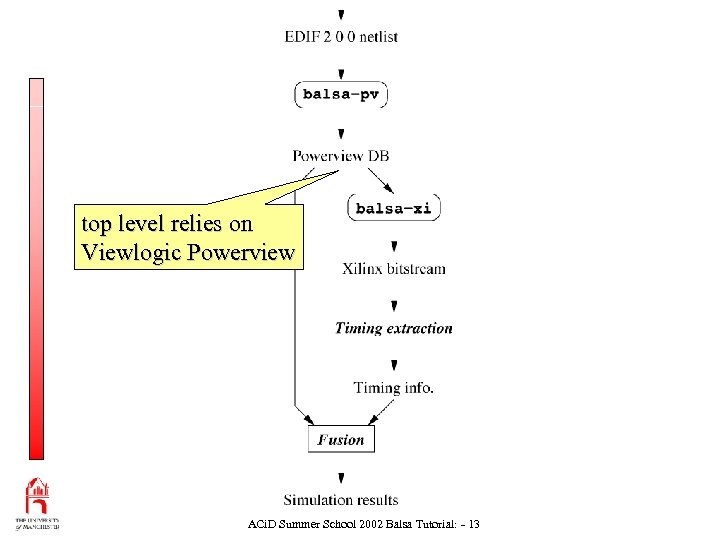

top level relies on Viewlogic Powerview ACi. D Summer School 2002 Balsa Tutorial: - 13

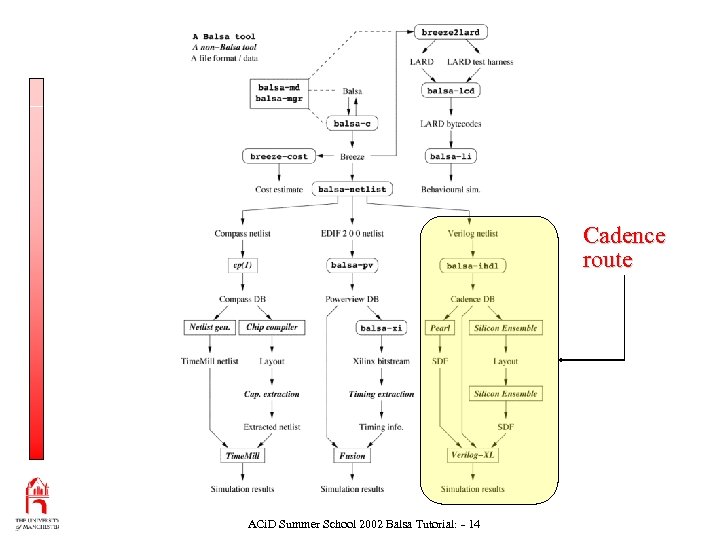

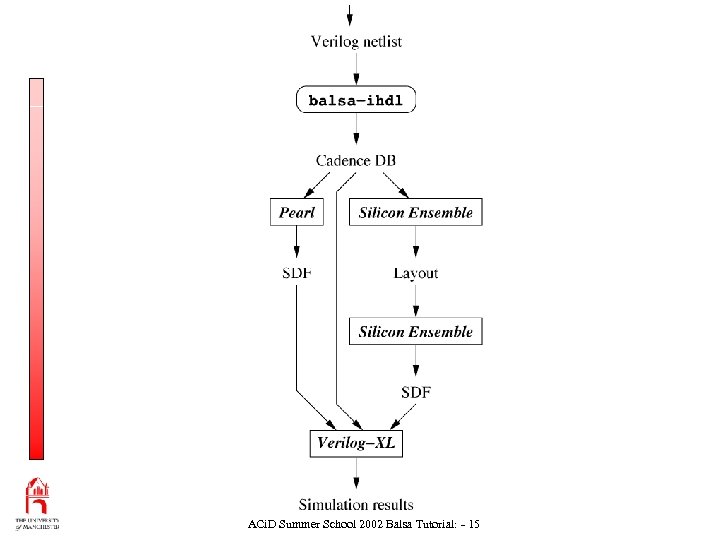

Cadence route ACi. D Summer School 2002 Balsa Tutorial: - 14

ACi. D Summer School 2002 Balsa Tutorial: - 15

Other Balsa Work n Burst-mode resynthesis • Tibi Chelcea & Steve Nowick n Faster LARD/Balsa simulation • Lilian Janin (x 50 speed up) n Datapath compilation optimisation • Andrew Bardsley n Complete Amulet implementation SPA 1 - Synthesised ARM v 5 T core • Peter Riocreux, Luis Plana et al. ACi. D Summer School 2002 Balsa Tutorial: - 16

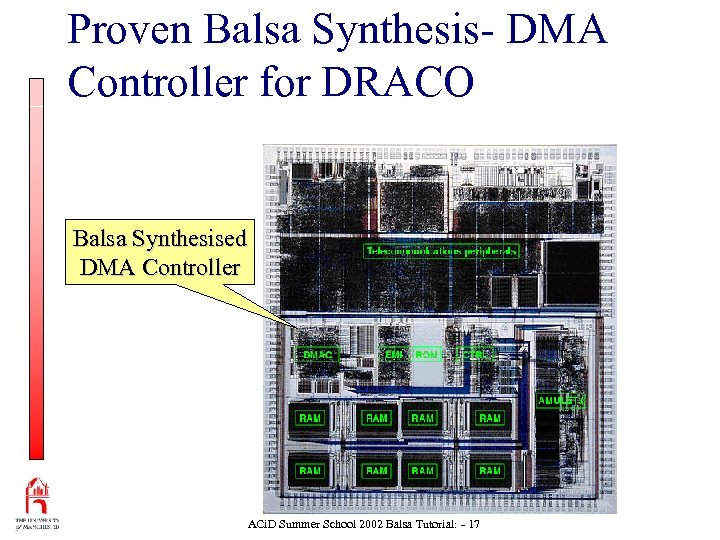

Proven Balsa Synthesis- DMA Controller for DRACO Balsa Synthesised DMA Controller ACi. D Summer School 2002 Balsa Tutorial: - 17

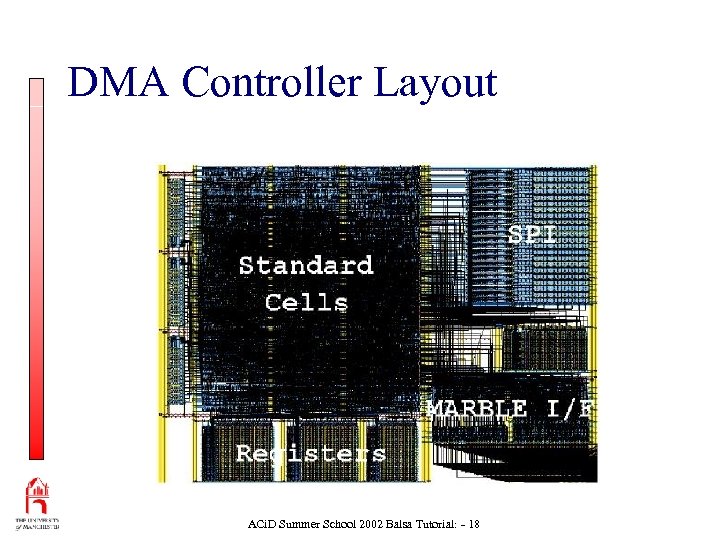

DMA Controller Layout ACi. D Summer School 2002 Balsa Tutorial: - 18

What is Balsa? Language for synthesising large async circuits & systems n CSP/OCCAM background n Tangram-like n • based on Tangram compilation function • compiles to a small, parameterisable, set of handshake components • origins: ESPRIT 6143 EXACT project ACi. D Summer School 2002 Balsa Tutorial: - 19

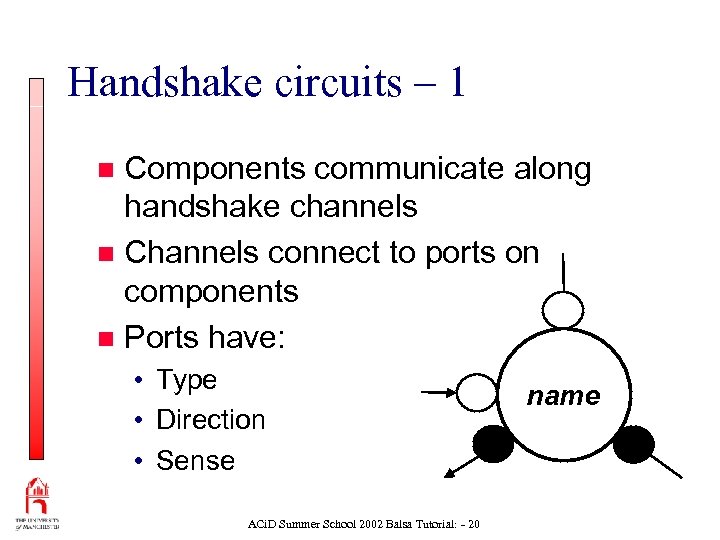

Handshake circuits – 1 Components communicate along handshake channels n Channels connect to ports on components n Ports have: n • Type • Direction • Sense ACi. D Summer School 2002 Balsa Tutorial: - 20 name

Handshake Circuits – 2 n Port type determines the number of data wires • no data wires = control only port! Port direction is input, output or control only (called sync) n Port sense n • Active: initiate transfers (source the req) • Passive: respond to requests (… the ack) ACi. D Summer School 2002 Balsa Tutorial: - 21

Balsa Language Features n Data types based on sequence of bits • Arrays and records are bit-based • Element extraction is by array slicing • Strict data typing Structural iteration n Arrayed channels n Parameterised, recursively expanded procedures n ACi. D Summer School 2002 Balsa Tutorial: - 22

Balsa Language Features n Enclosed selection semantics • Allows passive ported circuits • Allows push (micropipeline-style) circuits • Allows unbuffered (latch-free) circuits ACi. D Summer School 2002 Balsa Tutorial: - 23

![Example: Single Place Buffer import [balsa. types. basic] type word is 16 bits procedure Example: Single Place Buffer import [balsa. types. basic] type word is 16 bits procedure](https://present5.com/presentation/0dcd1d1e885de5b6f44b1403cae2dec9/image-24.jpg)

Example: Single Place Buffer import [balsa. types. basic] type word is 16 bits procedure buffer (input i : word; output o : word) is variable x : word begin loop i -> x ; -- Input communication o <- x -- Output communication end ACi. D Summer School 2002 Balsa Tutorial: - 24

![Example: Single Place Buffer import [balsa. types. basic] type word is 16 bits library Example: Single Place Buffer import [balsa. types. basic] type word is 16 bits library](https://present5.com/presentation/0dcd1d1e885de5b6f44b1403cae2dec9/image-25.jpg)

Example: Single Place Buffer import [balsa. types. basic] type word is 16 bits library type word; output mechanism (input i : declaration o procedure buffer variable x : word begin procedure implies latch loop i ; -- Input definition -> xrepeat forever communication o <- x -- Output communication end read sequential operation input channel into end local variable x output local variable x to output channel ACi. D Summer School 2002 Balsa Tutorial: - 25 : word) is channel declarations

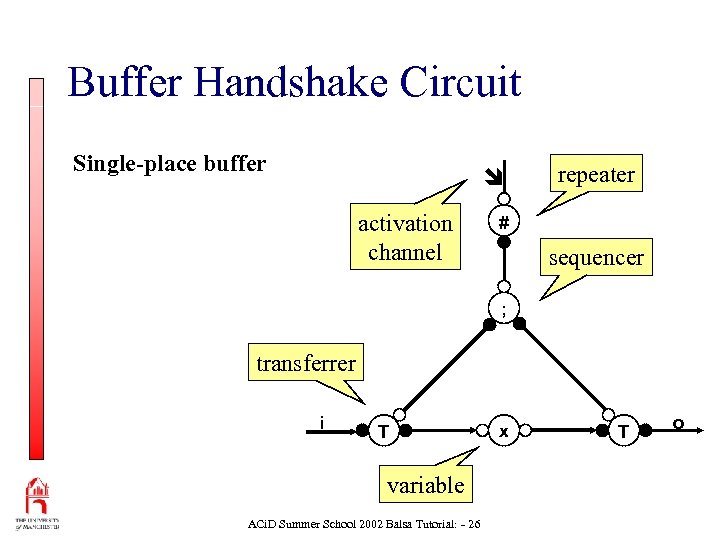

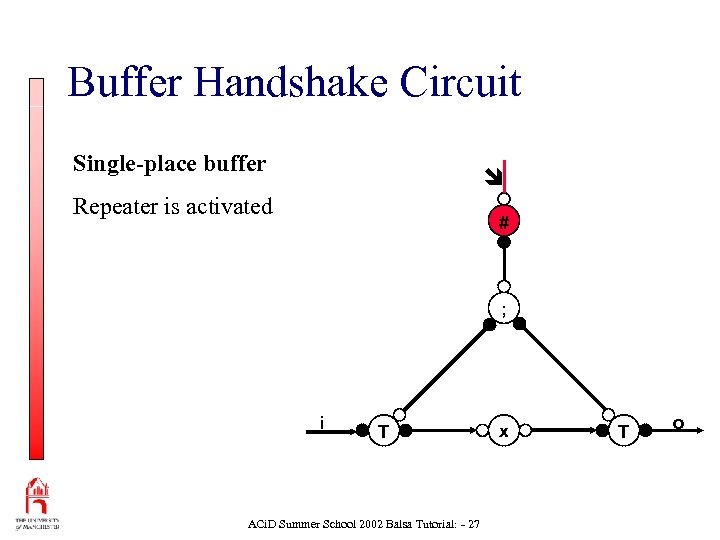

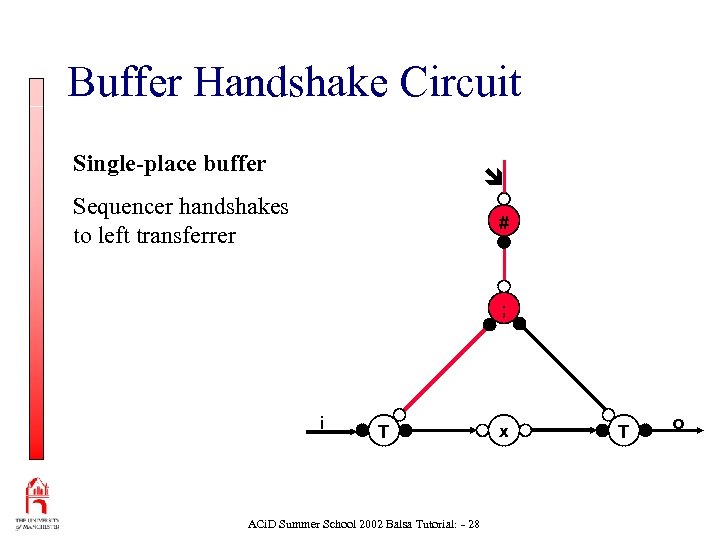

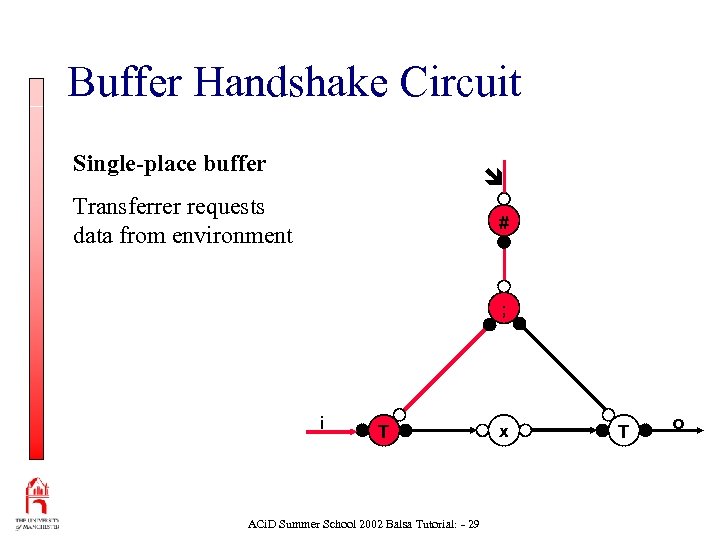

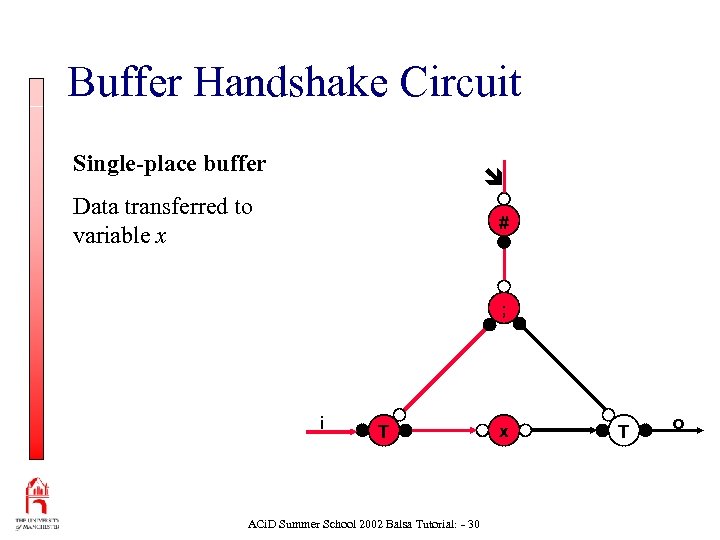

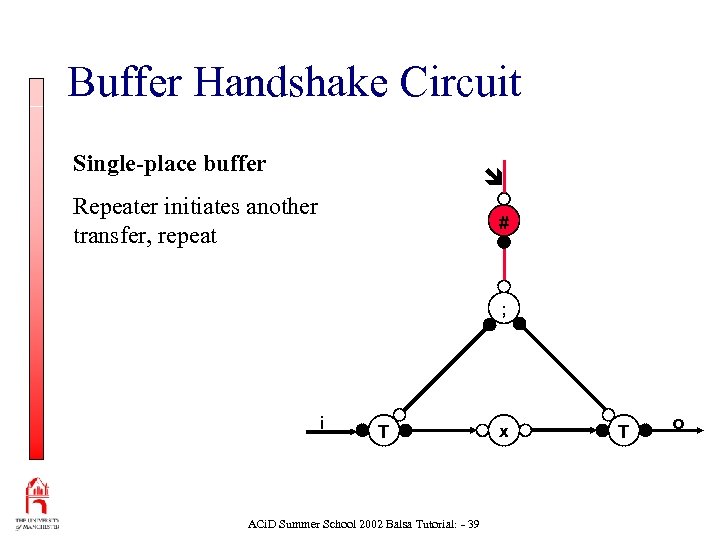

Buffer Handshake Circuit Single-place buffer activation channel repeater # sequencer ; transferrer i T variable ACi. D Summer School 2002 Balsa Tutorial: - 26 x T o

Buffer Handshake Circuit Single-place buffer Repeater is activated # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 27 x T o

Buffer Handshake Circuit Single-place buffer Sequencer handshakes to left transferrer # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 28 x T o

Buffer Handshake Circuit Single-place buffer Transferrer requests data from environment # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 29 x T o

Buffer Handshake Circuit Single-place buffer Data transferred to variable x # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 30 x T o

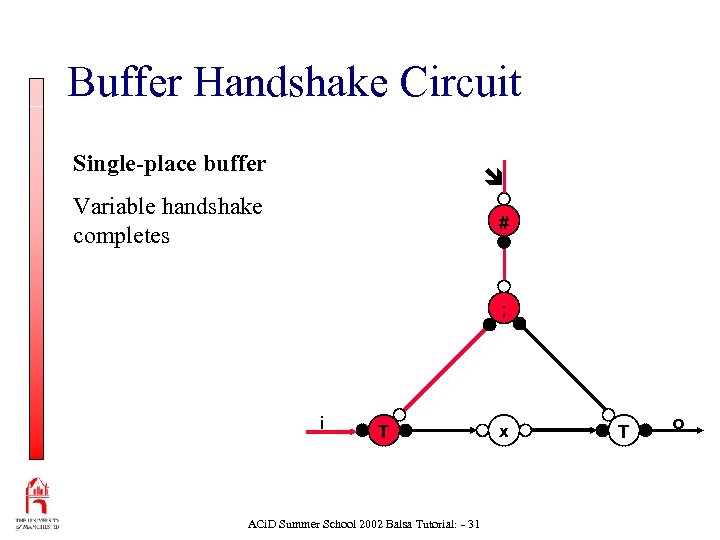

Buffer Handshake Circuit Single-place buffer Variable handshake completes # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 31 x T o

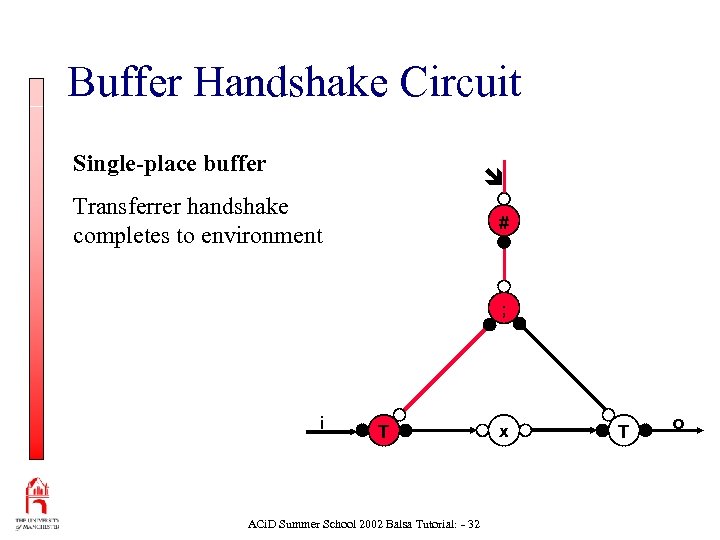

Buffer Handshake Circuit Single-place buffer Transferrer handshake completes to environment # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 32 x T o

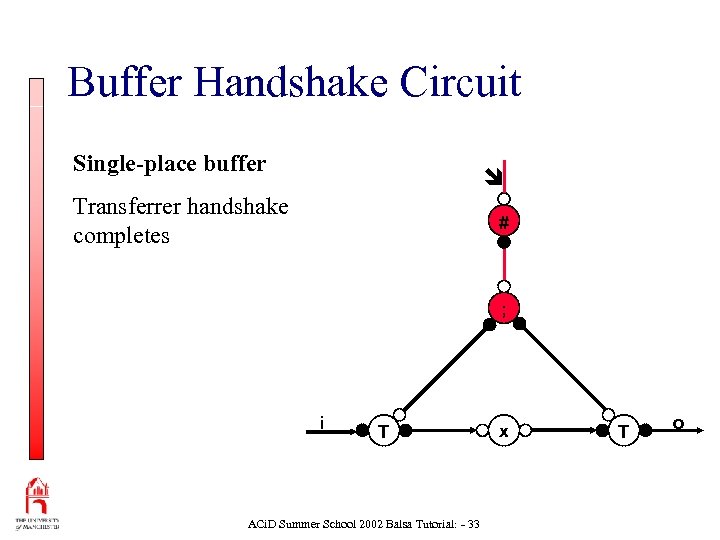

Buffer Handshake Circuit Single-place buffer Transferrer handshake completes # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 33 x T o

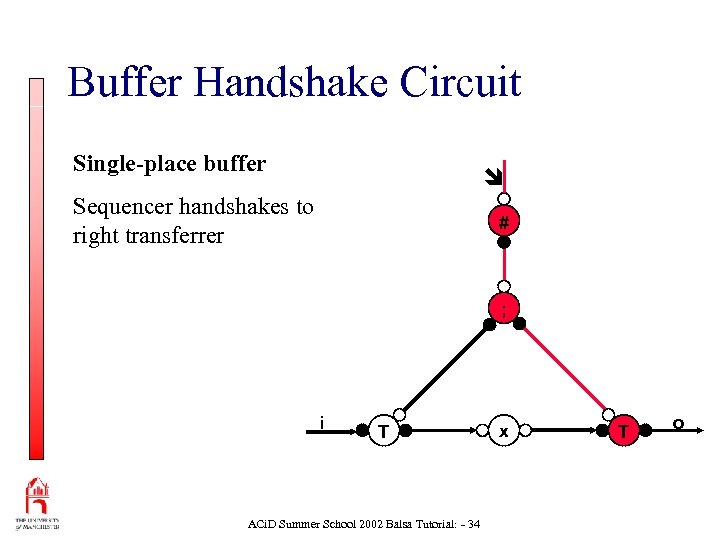

Buffer Handshake Circuit Single-place buffer Sequencer handshakes to right transferrer # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 34 x T o

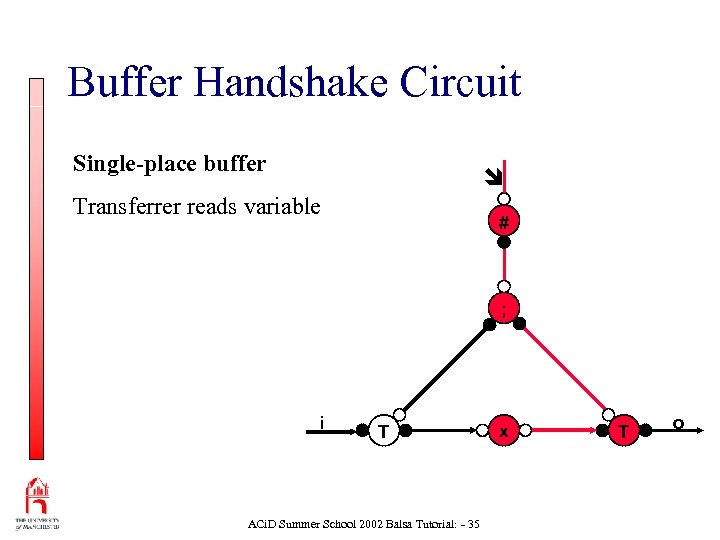

Buffer Handshake Circuit Single-place buffer Transferrer reads variable # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 35 x T o

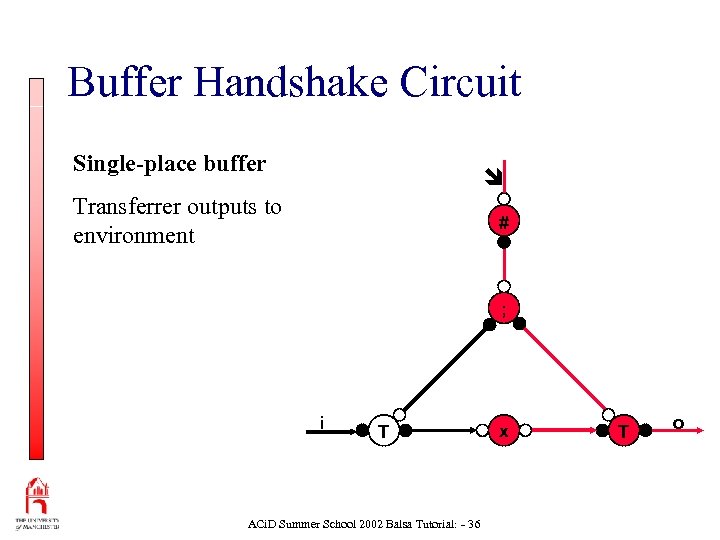

Buffer Handshake Circuit Single-place buffer Transferrer outputs to environment # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 36 x T o

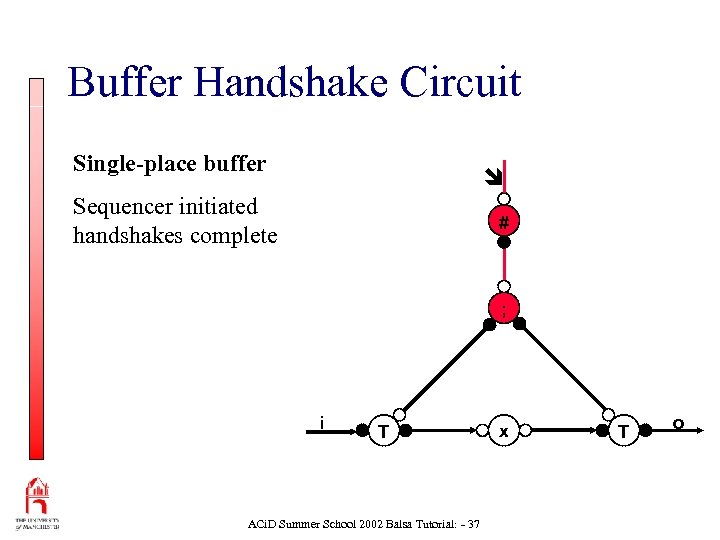

Buffer Handshake Circuit Single-place buffer Sequencer initiated handshakes complete # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 37 x T o

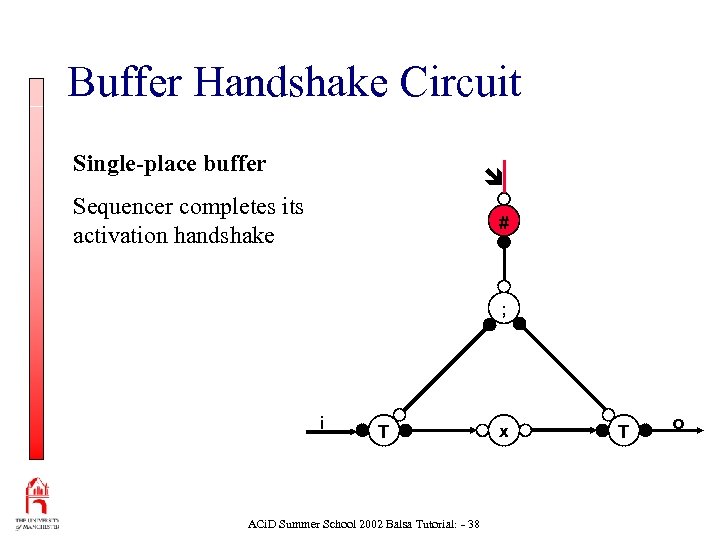

Buffer Handshake Circuit Single-place buffer Sequencer completes its activation handshake # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 38 x T o

Buffer Handshake Circuit Single-place buffer Repeater initiates another transfer, repeat # ; i T ACi. D Summer School 2002 Balsa Tutorial: - 39 x T o

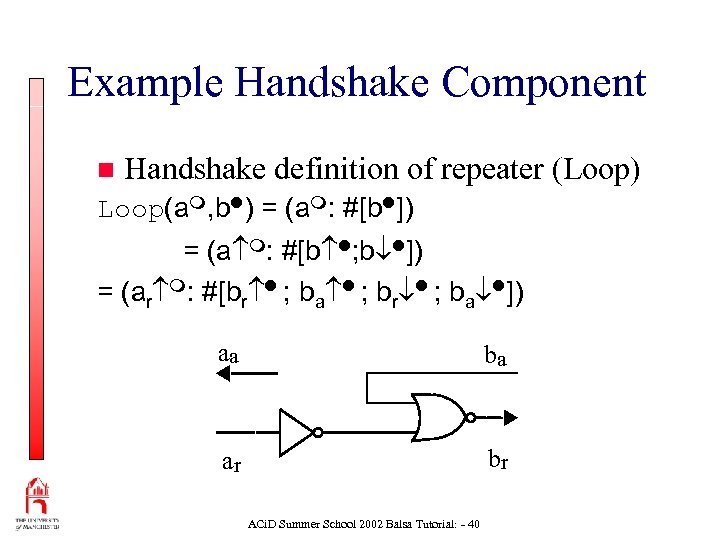

Example Handshake Component n Handshake definition of repeater (Loop) Loop(a , b ) = (a : #[b ]) = (a : #[b ; b ]) = (ar : #[br ; ba ; br ; ba ]) aa ba ar br ACi. D Summer School 2002 Balsa Tutorial: - 40

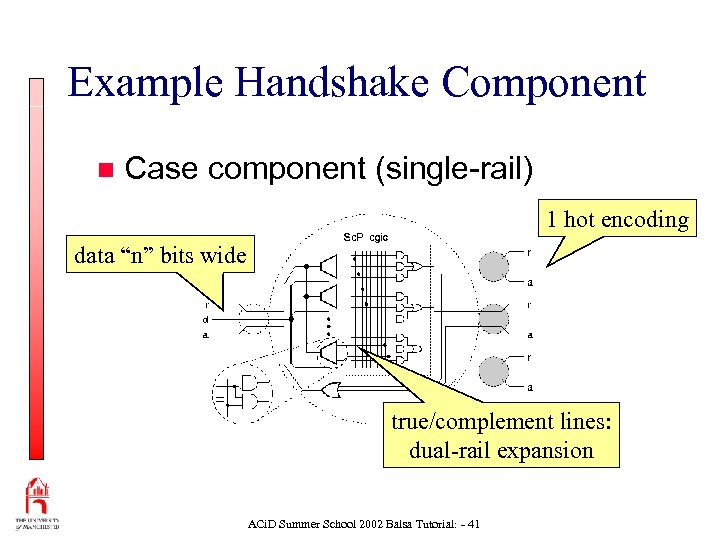

Example Handshake Component n Case component (single-rail) 1 hot encoding data “n” bits wide true/complement lines: dual-rail expansion ACi. D Summer School 2002 Balsa Tutorial: - 41

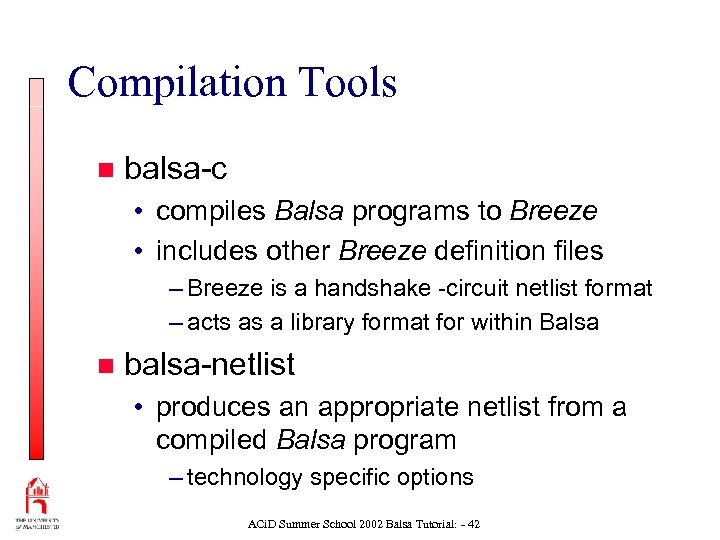

Compilation Tools n balsa-c • compiles Balsa programs to Breeze • includes other Breeze definition files – Breeze is a handshake -circuit netlist format – acts as a library format for within Balsa n balsa-netlist • produces an appropriate netlist from a compiled Balsa program – technology specific options ACi. D Summer School 2002 Balsa Tutorial: - 42

Simulation Tools n breeze 2 lard • produces a LARD simulation file n various LARD utilities • mainly hidden within the Makefile by balsa-md ACi. D Summer School 2002 Balsa Tutorial: - 43

Utilitity Tools n breeze 2 ps • creates a Post. Script HC graph n breeze-cost • enumerates the handshake circuits used and gives an approximate area cost n balsa-md • automatic Makefile maker n balsa-mgr • GUI interface to balsa-md ACi. D Summer School 2002 Balsa Tutorial: - 44

Exercise: Single Stage Shift Register Objective: introduction to balsa-mgr n n cd ~/Balsa/shift-reg balsa-mgr & • create new project: Project -> New • add SRA 1. balsa to project ACi. D Summer School 2002 Balsa Tutorial: - 45

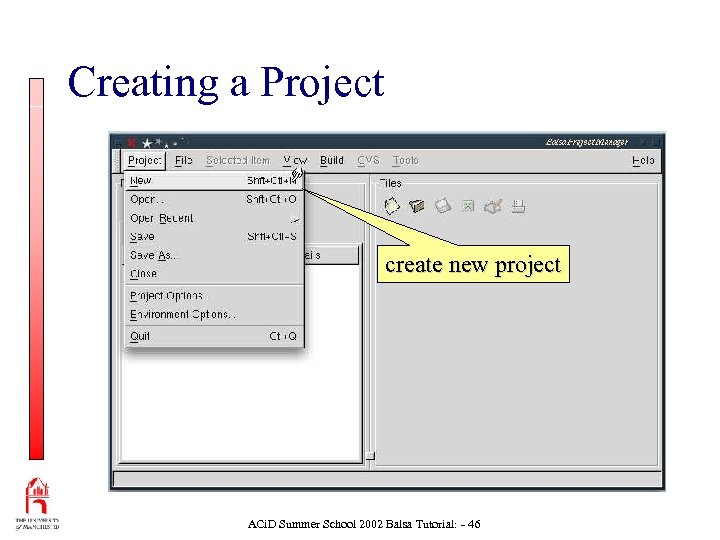

Creating a Project create new project ACi. D Summer School 2002 Balsa Tutorial: - 46

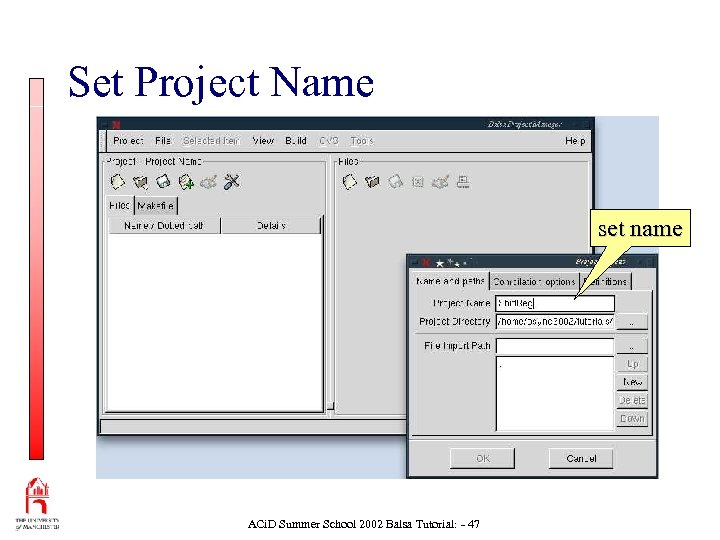

Set Project Name set name ACi. D Summer School 2002 Balsa Tutorial: - 47

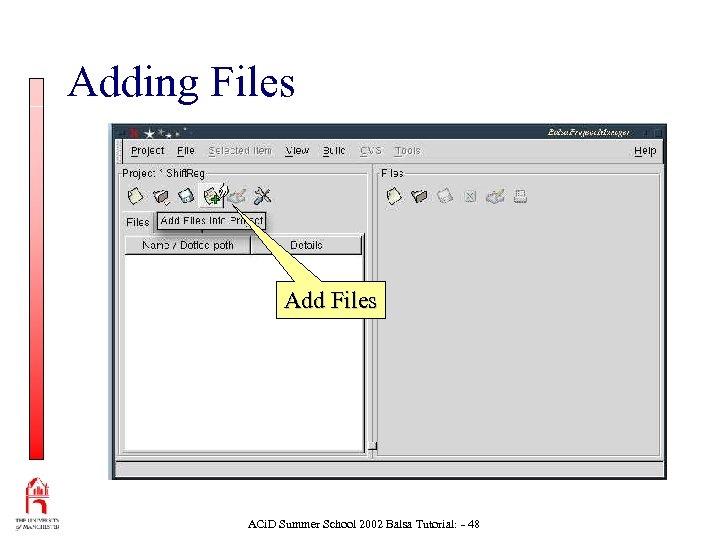

Adding Files Add Files ACi. D Summer School 2002 Balsa Tutorial: - 48

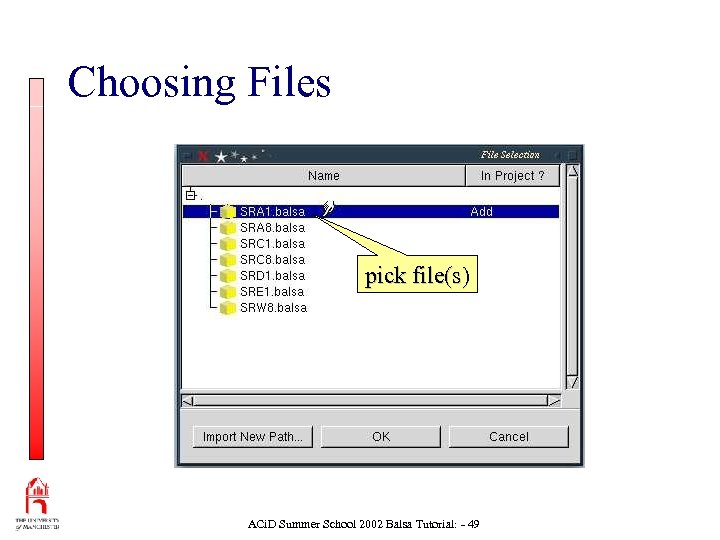

Choosing Files pick file(s) ACi. D Summer School 2002 Balsa Tutorial: - 49

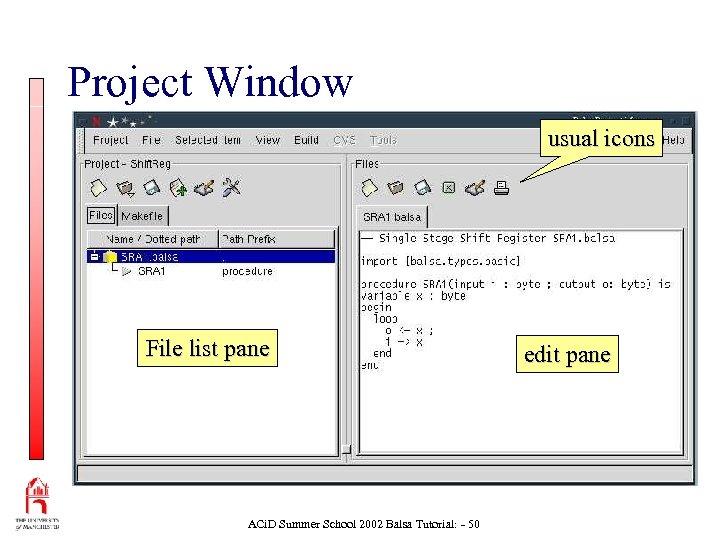

Project Window usual icons File list pane ACi. D Summer School 2002 Balsa Tutorial: - 50 edit pane

Project Manager tool-tip help pop-ups for icons n editor icon opens the editor defined in: Project -> Environment dialogue n • syntax modes for xemacs, elvis, nedit right-mouse clicking on panes brings up context sensitive menus n Browse the various menus (& pop-ups) n ACi. D Summer School 2002 Balsa Tutorial: - 51

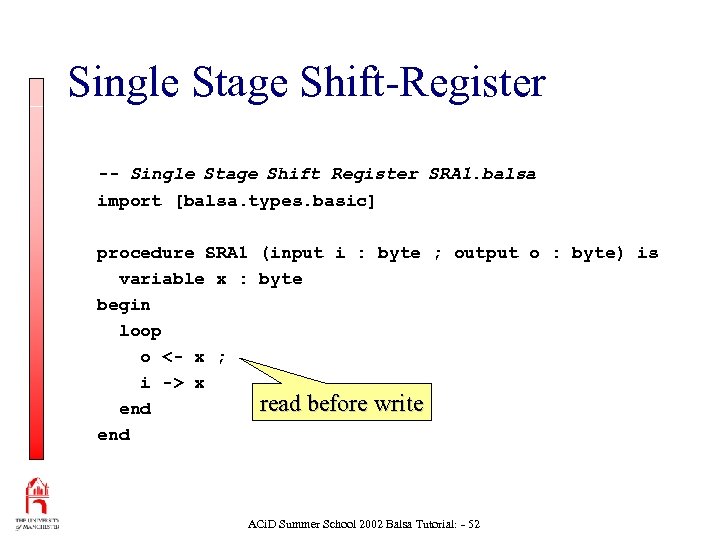

Single Stage Shift-Register -- Single Stage Shift Register SRA 1. balsa import [balsa. types. basic] procedure SRA 1 (input i : byte ; output o : byte) is variable x : byte begin loop o <- x ; i -> x read before write end ACi. D Summer School 2002 Balsa Tutorial: - 52

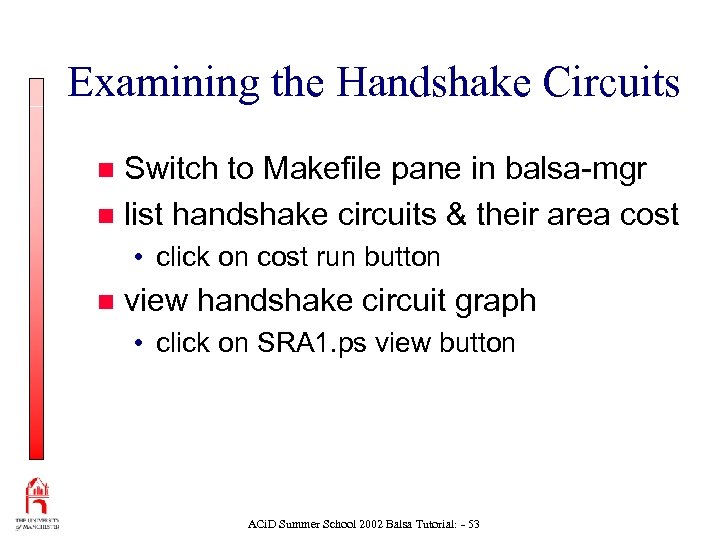

Examining the Handshake Circuits Switch to Makefile pane in balsa-mgr n list handshake circuits & their area cost n • click on cost run button n view handshake circuit graph • click on SRA 1. ps view button ACi. D Summer School 2002 Balsa Tutorial: - 53

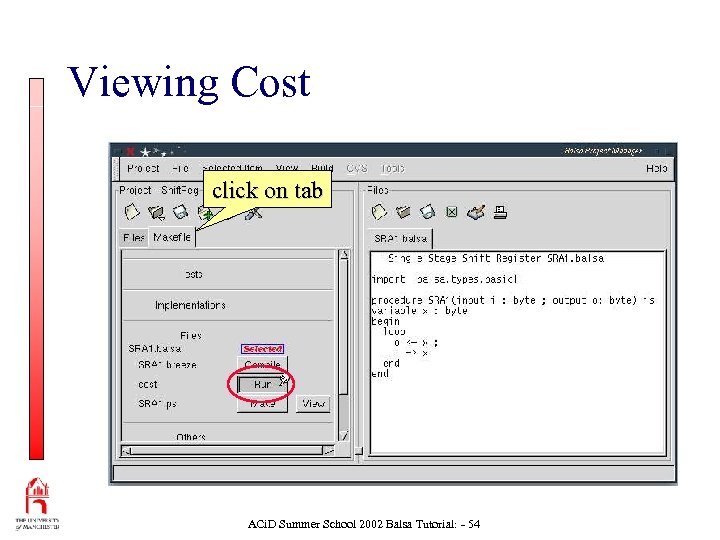

Viewing Cost click on tab ACi. D Summer School 2002 Balsa Tutorial: - 54

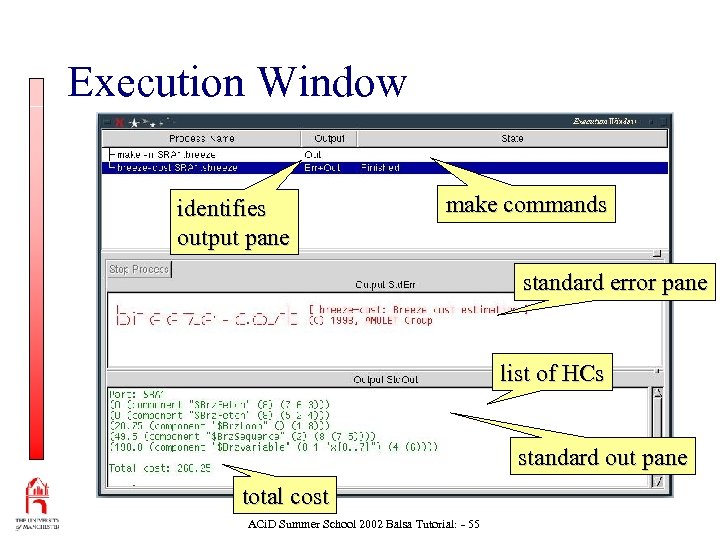

Execution Window identifies output pane make commands standard error pane list of HCs standard out pane total cost ACi. D Summer School 2002 Balsa Tutorial: - 55

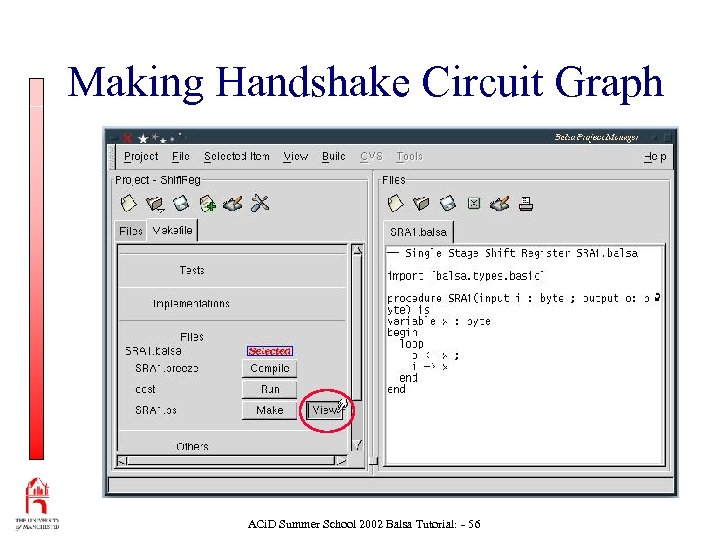

Making Handshake Circuit Graph ACi. D Summer School 2002 Balsa Tutorial: - 56

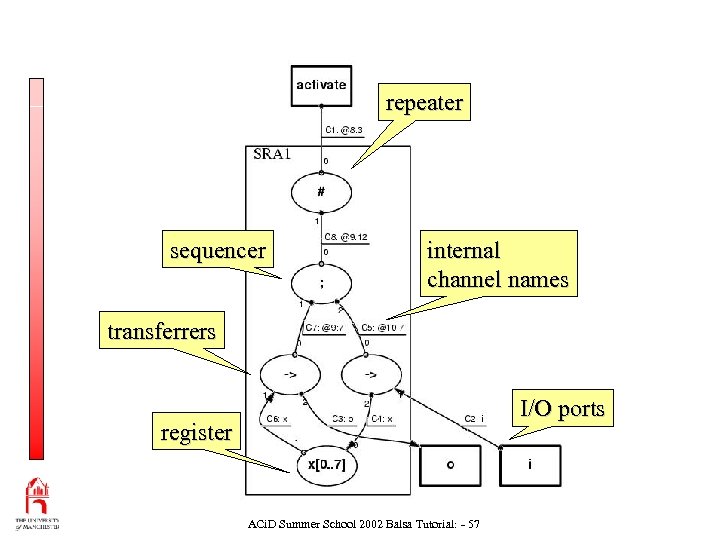

repeater sequencer internal channel names transferrers I/O ports register ACi. D Summer School 2002 Balsa Tutorial: - 57

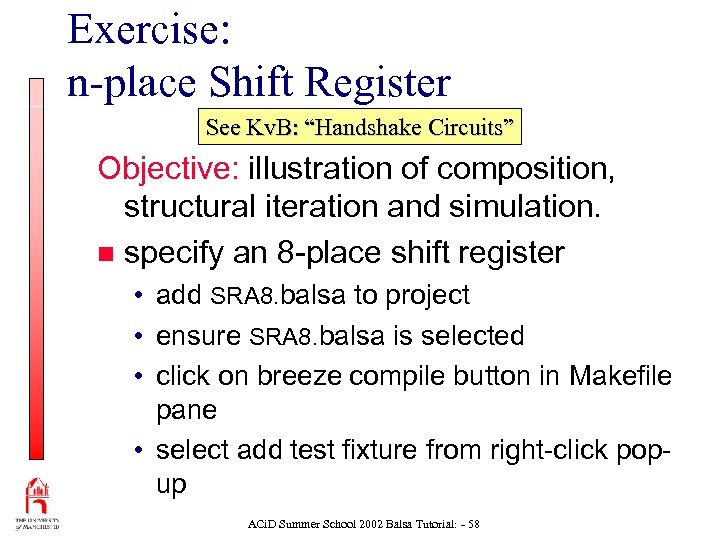

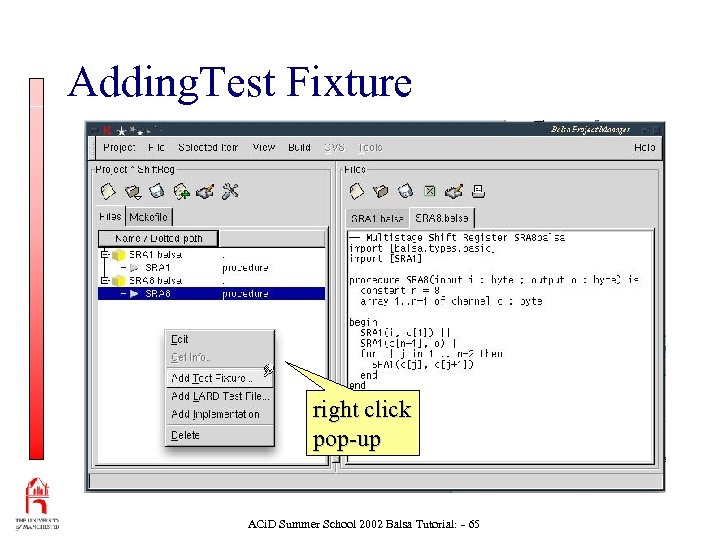

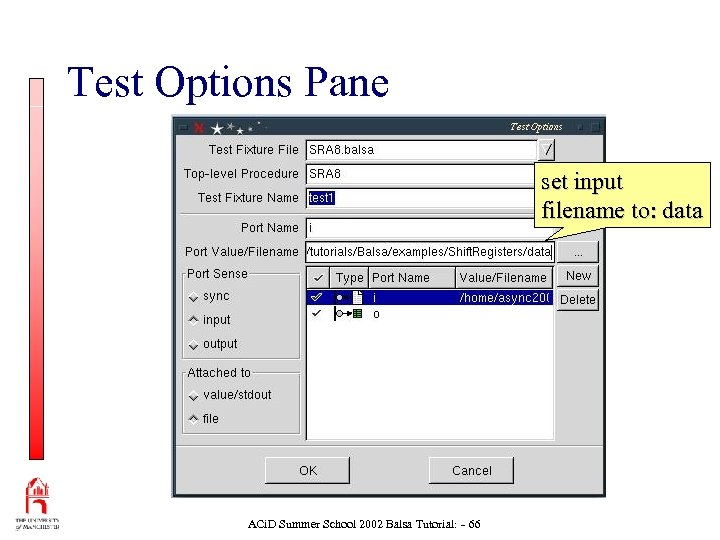

Exercise: n-place Shift Register See Kv. B: “Handshake Circuits” Objective: illustration of composition, structural iteration and simulation. n specify an 8 -place shift register • add SRA 8. balsa to project • ensure SRA 8. balsa is selected • click on breeze compile button in Makefile pane • select add test fixture from right-click popup ACi. D Summer School 2002 Balsa Tutorial: - 58

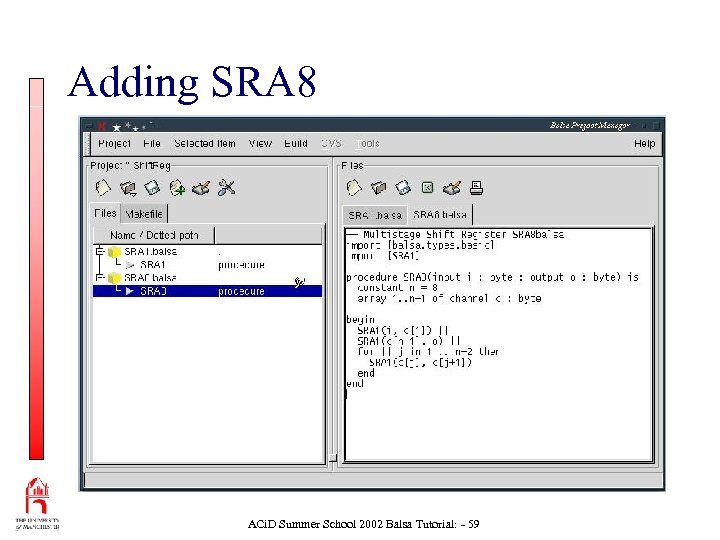

Adding SRA 8 ACi. D Summer School 2002 Balsa Tutorial: - 59

![SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic] SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic]](https://present5.com/presentation/0dcd1d1e885de5b6f44b1403cae2dec9/image-60.jpg)

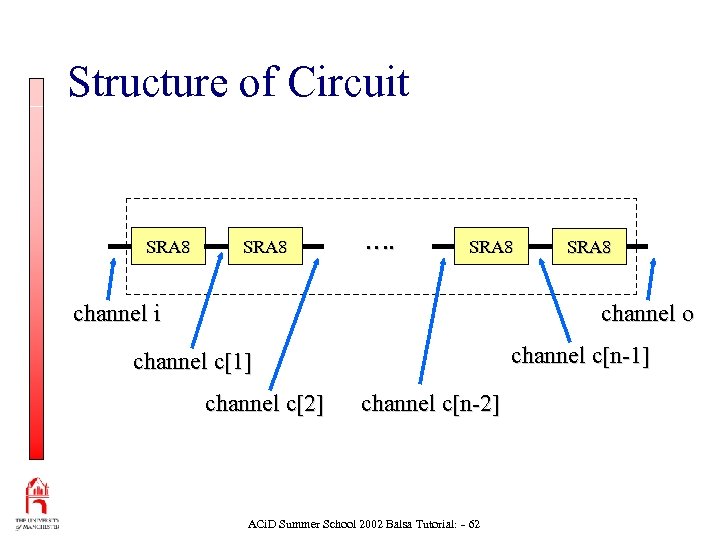

SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic] import [SRA 1] procedure SRA 8 (input i : byte; output o : byte) is constant n = 8 array 1. . n-1 of channel c : byte begin SRA 1 (i, c[1]) || SRA 1 (c[n-1], o) || for || j in 1. . n-2 then SRA 1 (c[j], c[j+1]) end ACi. D Summer School 2002 Balsa Tutorial: - 60

![SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic] SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic]](https://present5.com/presentation/0dcd1d1e885de5b6f44b1403cae2dec9/image-61.jpg)

SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic] import [SRA 1] define a constant procedure SRA 8 (input i : byte; output o : byte) is constant n = 8 array 1. . n-1 of channel c : byte begin internal SRA 1 (i, c[1]) || channel array SRA 1 (c[n-1], o) || for || j in 1. . n-2 then parallel SRA 1 (c[j], c[j+1]) composition end structural end iteration ACi. D Summer School 2002 Balsa Tutorial: - 61

Structure of Circuit SRA 8 …. SRA 8 channel i SRA 8 channel o channel c[n-1] channel c[2] channel c[n-2] ACi. D Summer School 2002 Balsa Tutorial: - 62

![SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic] SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic]](https://present5.com/presentation/0dcd1d1e885de5b6f44b1403cae2dec9/image-63.jpg)

SRA 8 Code -- Multistage Shift Register SRA 8. balsa import [balsa. types. basic] import [SRA 1] procedure SRA 8 (input i : byte; output o : byte) is constant n = 8 array 1. . n-1 of channel c : byte begin SRA 1 (i, c[1]) || SRA 1 (c[n-1], o) || for || j in 1. . n-2 then SRA 1 (c[j], c[j+1]) end ACi. D Summer School 2002 Balsa Tutorial: - 63

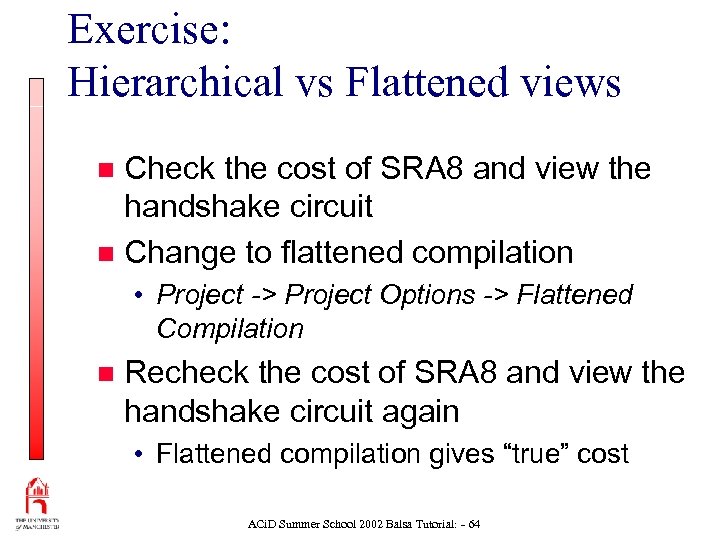

Exercise: Hierarchical vs Flattened views Check the cost of SRA 8 and view the handshake circuit n Change to flattened compilation n • Project -> Project Options -> Flattened Compilation n Recheck the cost of SRA 8 and view the handshake circuit again • Flattened compilation gives “true” cost ACi. D Summer School 2002 Balsa Tutorial: - 64

Adding. Test Fixture right click pop-up ACi. D Summer School 2002 Balsa Tutorial: - 65

Test Options Pane set input filename to: data ACi. D Summer School 2002 Balsa Tutorial: - 66

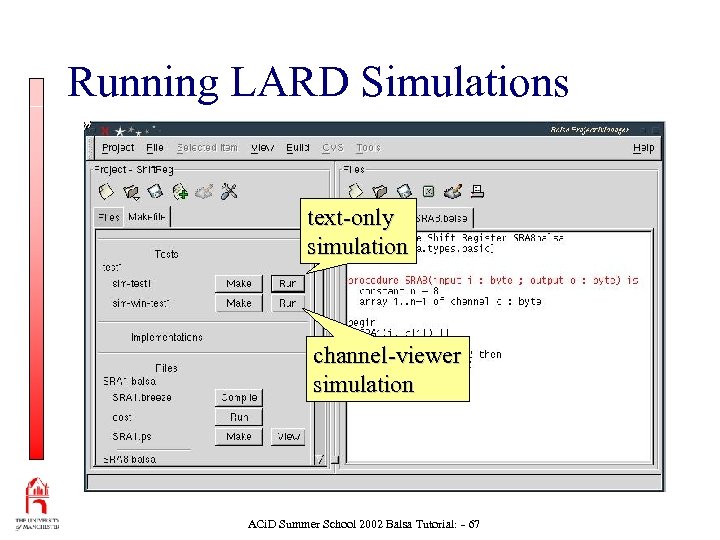

Running LARD Simulations text-only simulation channel-viewer simulation ACi. D Summer School 2002 Balsa Tutorial: - 67

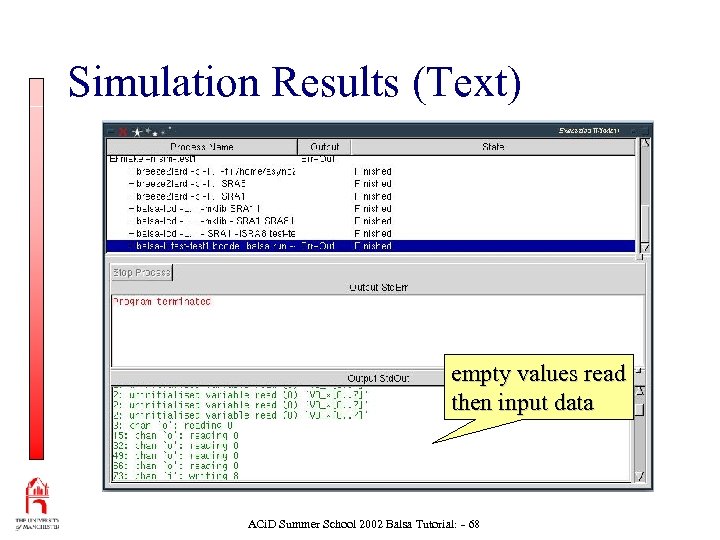

Simulation Results (Text) empty values read then input data ACi. D Summer School 2002 Balsa Tutorial: - 68

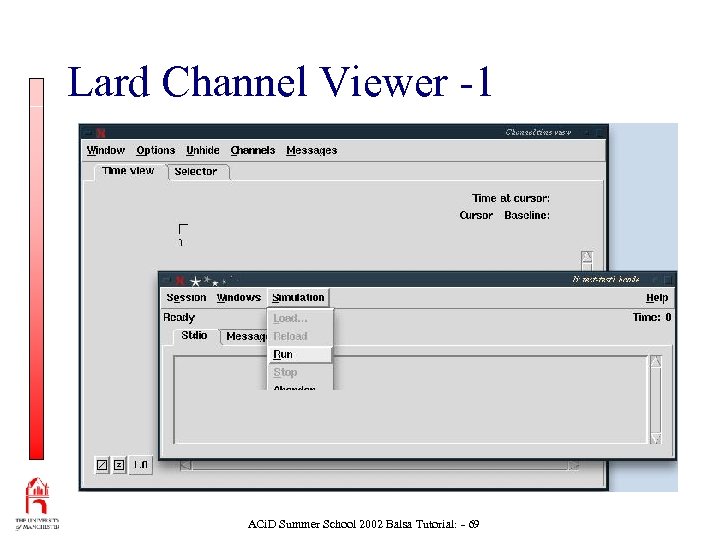

Lard Channel Viewer -1 ACi. D Summer School 2002 Balsa Tutorial: - 69

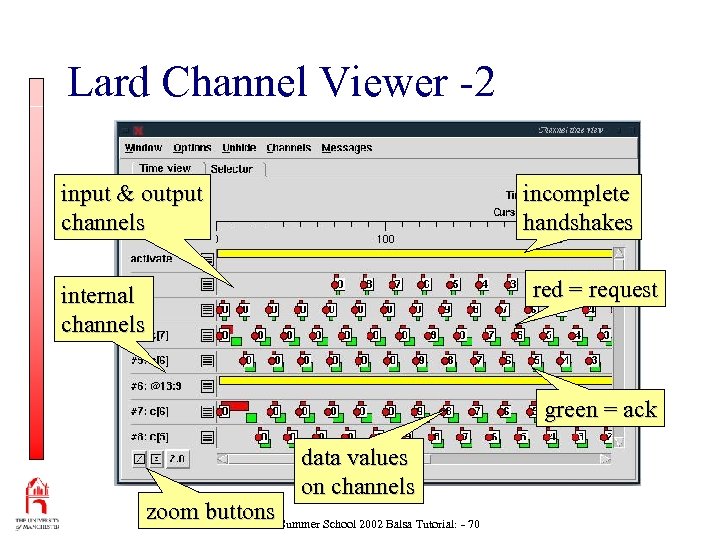

Lard Channel Viewer -2 input & output channels incomplete handshakes red = request internal channels green = ack data values on channels zoom buttons Summer School 2002 Balsa Tutorial: - 70 ACi. D

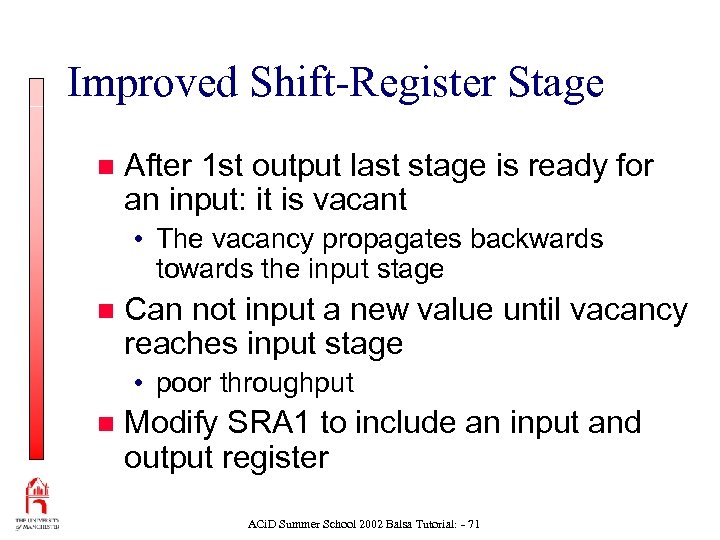

Improved Shift-Register Stage n After 1 st output last stage is ready for an input: it is vacant • The vacancy propagates backwards towards the input stage n Can not input a new value until vacancy reaches input stage • poor throughput n Modify SRA 1 to include an input and output register ACi. D Summer School 2002 Balsa Tutorial: - 71

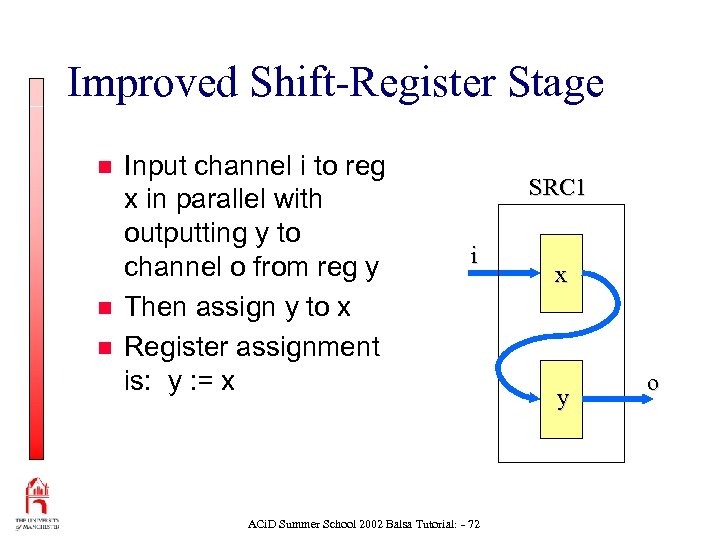

Improved Shift-Register Stage n n n Input channel i to reg x in parallel with outputting y to channel o from reg y Then assign y to x Register assignment is: y : = x SRC 1 i ACi. D Summer School 2002 Balsa Tutorial: - 72 x y o

Exercise: Language Level Trade-offs n Write your own SRC 1 and SRC 8 • copy SRA 1. balsa to SRC 1. balsa and edit n Compare the cost of SRC 8 with SRA 8 (must use flattened compilation) n Compare the behaviours of SRC 8 and SRA 8 ACi. D Summer School 2002 Balsa Tutorial: - 73

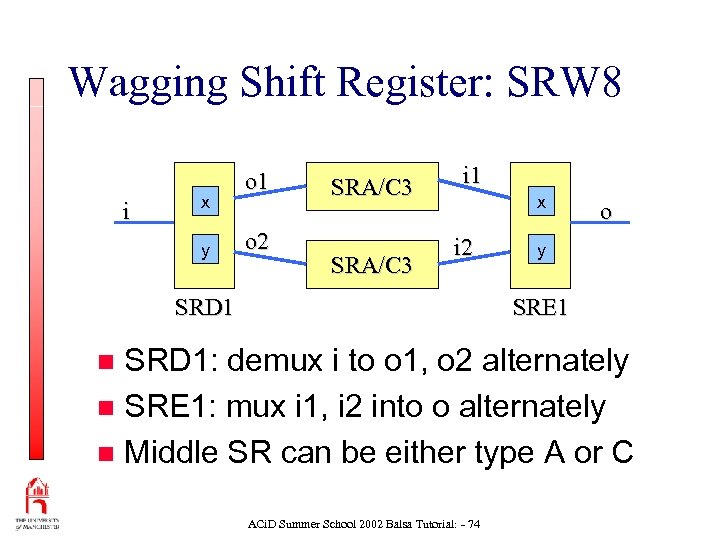

Wagging Shift Register: SRW 8 i x y o 1 o 2 SRA/C 3 i 1 x i 2 SRD 1 o y SRE 1 SRD 1: demux i to o 1, o 2 alternately n SRE 1: mux i 1, i 2 into o alternately n Middle SR can be either type A or C n ACi. D Summer School 2002 Balsa Tutorial: - 74

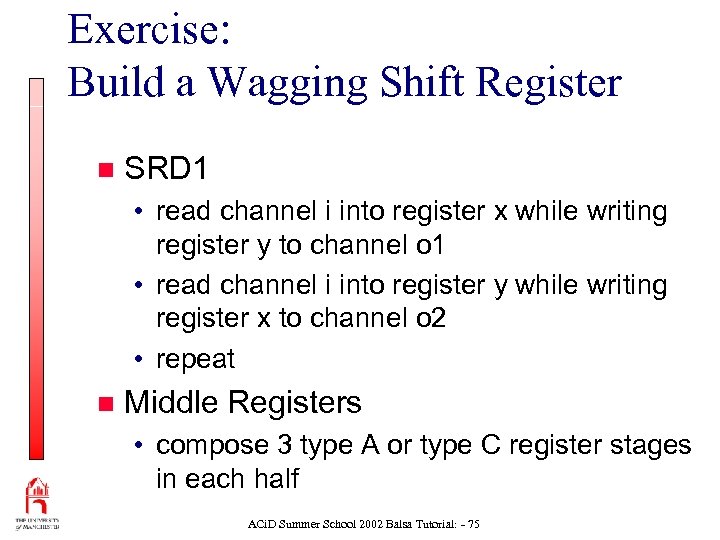

Exercise: Build a Wagging Shift Register n SRD 1 • read channel i into register x while writing register y to channel o 1 • read channel i into register y while writing register x to channel o 2 • repeat n Middle Registers • compose 3 type A or type C register stages in each half ACi. D Summer School 2002 Balsa Tutorial: - 75

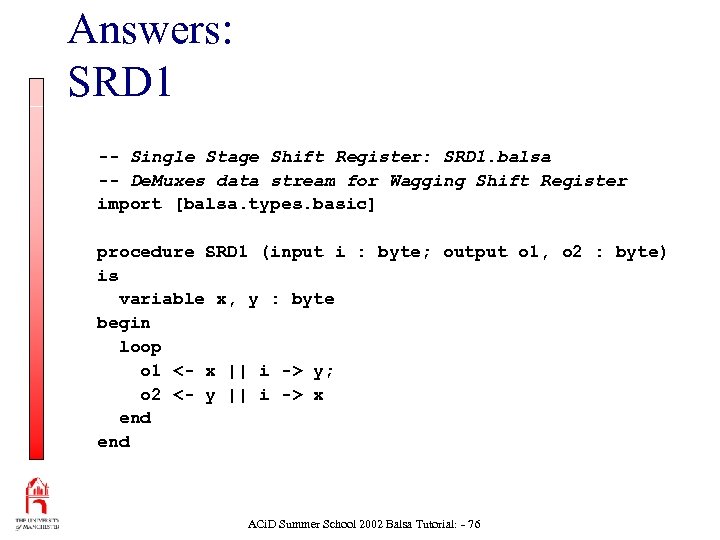

Answers: SRD 1 -- Single Stage Shift Register: SRD 1. balsa -- De. Muxes data stream for Wagging Shift Register import [balsa. types. basic] procedure SRD 1 (input i : byte; output o 1, o 2 : byte) is variable x, y : byte begin loop o 1 <- x || i -> y; o 2 <- y || i -> x end ACi. D Summer School 2002 Balsa Tutorial: - 76

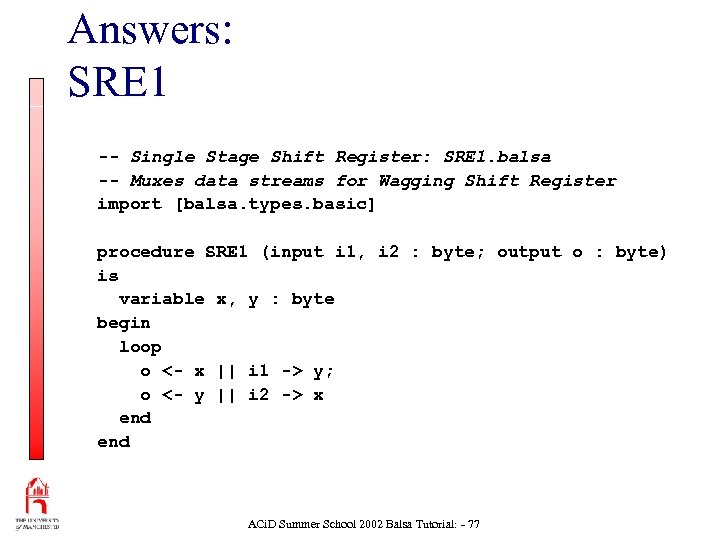

Answers: SRE 1 -- Single Stage Shift Register: SRE 1. balsa -- Muxes data streams for Wagging Shift Register import [balsa. types. basic] procedure SRE 1 (input i 1, i 2 : byte; output o : byte) is variable x, y : byte begin loop o <- x || i 1 -> y; o <- y || i 2 -> x end ACi. D Summer School 2002 Balsa Tutorial: - 77

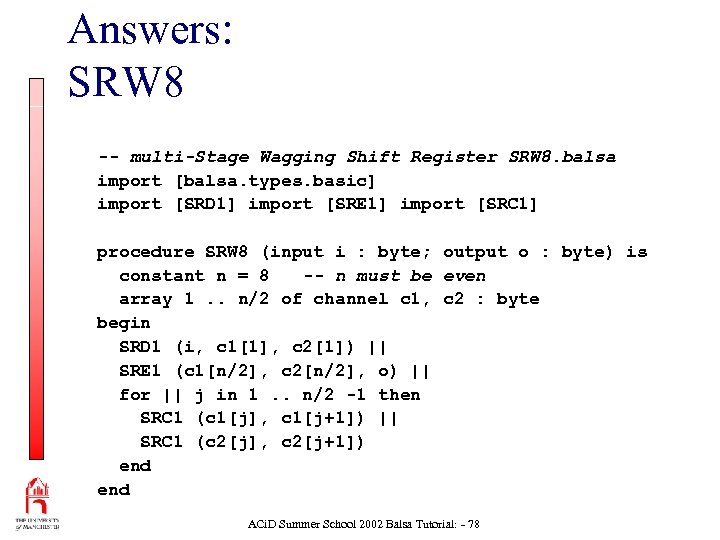

Answers: SRW 8 -- multi-Stage Wagging Shift Register SRW 8. balsa import [balsa. types. basic] import [SRD 1] import [SRE 1] import [SRC 1] procedure SRW 8 (input i : byte; output o : byte) is constant n = 8 -- n must be even array 1. . n/2 of channel c 1, c 2 : byte begin SRD 1 (i, c 1[1], c 2[1]) || SRE 1 (c 1[n/2], c 2[n/2], o) || for || j in 1. . n/2 -1 then SRC 1 (c 1[j], c 1[j+1]) || SRC 1 (c 2[j], c 2[j+1]) end ACi. D Summer School 2002 Balsa Tutorial: - 78

Spamulet 0 - Prototype for SPA 1 Subset of ARM instruction set n ALU ops, LDR/STR, Branch with link (procedure call) implemented n Sequential, register based design, Do. This (); Do. That () n Your task is to add to this description n Spamulet 0 lacks LDM/STM, MUL, SWI, Coprocessor I/F, Pipelining, Exceptions, Operating modes n ACi. D Summer School 2002 Balsa Tutorial: - 79

The Project File cd ~/Balsa/spamulet 0 n 4 Balsa files, LARD test harness n • types. balsa - type and instruction format records • alu. balsa - ALU with CC handling • shift. balsa - parameterised shifter • spamulet. balsa - top-level, fetch-decodeexecute loop • test-spamulet. l - LARD test harness ACi. D Summer School 2002 Balsa Tutorial: - 80

Simulation Framework LARD test harness provides simulated memory loaded from raw memory dump files n Small number of provided examples: hello. s, multiply. s, helloc. c n Memory dumps generated from: n • Assembler: . s spamulet-asm . raw • C: . c spamulet-cc . s ACi. D Summer School 2002 Balsa Tutorial: - 81

LDM/STM - Load/Store Multiple Load and store any of the registers as a block - including the PC! n Commonly used for function arguments, entry register saves and return n ldmdir Rbase!opt, {Ri, Rj, …} n stmdir Rbase!opt, {Ri, Rj …} n Registers always appear in memory in the same order with R 0 at lowest address, R 15 at highest n ACi. D Summer School 2002 Balsa Tutorial: - 82

LDM/STM Directions n dir is one of: • • n ib - increment before db - decrement before ia - increment after da - decrement after Problems include loading PC last and avoiding overwriting the base register ACi. D Summer School 2002 Balsa Tutorial: - 83

LDM/STM Directions 2 n LDM/STM can also be used with “stack addressing” • • n fa - full ascending (ldmda, stmib) fd - full descending (ldmia, stmdb) ea - empty ascending (ldmdb, stmia) ed - empty descending (ldmib, stmda) The C compiler generated LDM/STMs with the stack addressing names ACi. D Summer School 2002 Balsa Tutorial: - 84

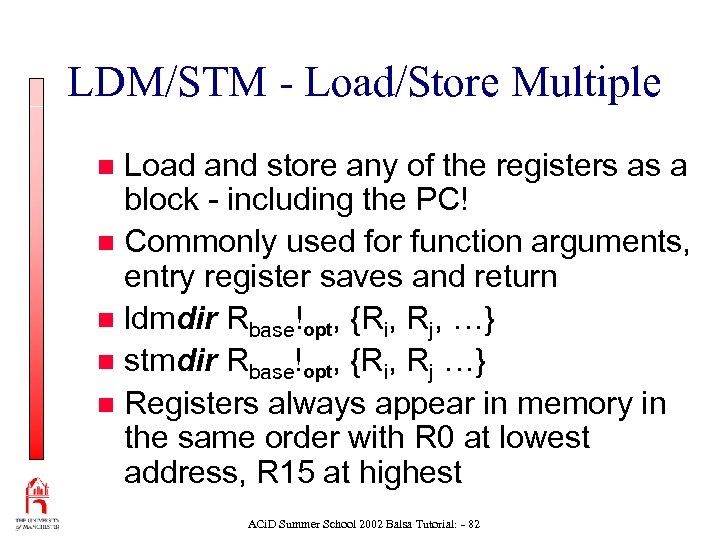

Instruction Encoding ACi. D Summer School 2002 Balsa Tutorial: - 85

Instruction Encoding – 2 Look at inst. Ldm. Stm in types. balsa n Use: (ir as inst. Ldm. Stm) to decode instructions n • e. g. (ir as inst. Ldm. Stm). options. L is the load(1)/store(0) select bit n Option bits very similar to LDR and STR instructions, read spamulet. balsa ACi. D Summer School 2002 Balsa Tutorial: - 86

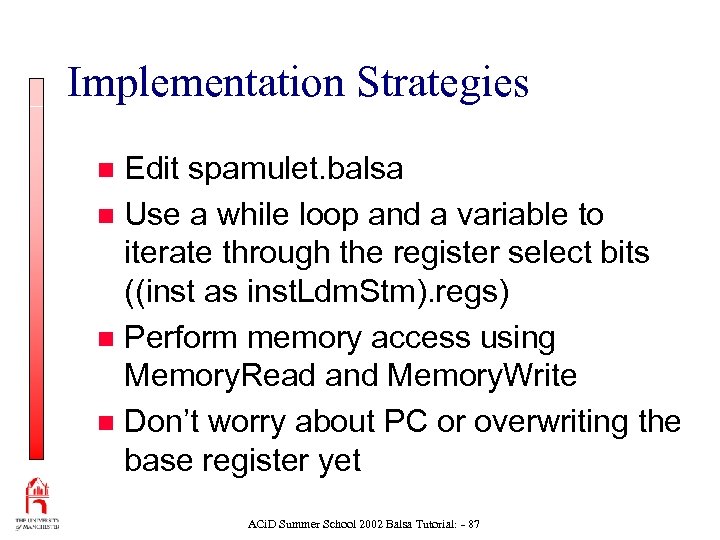

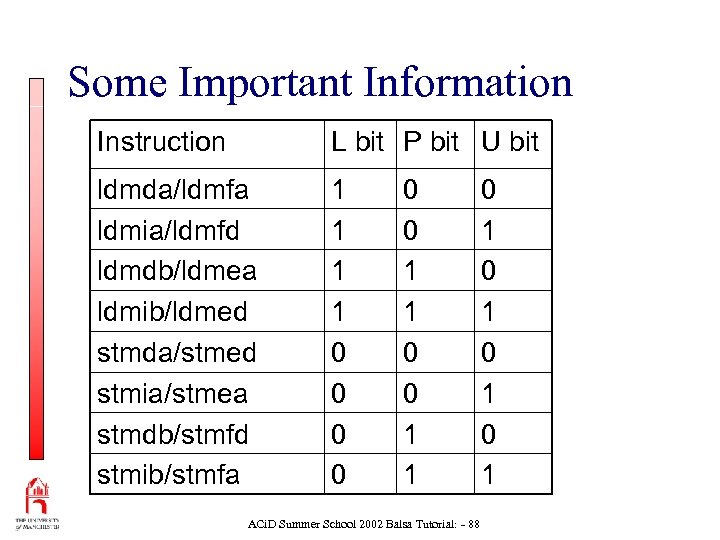

Implementation Strategies Edit spamulet. balsa n Use a while loop and a variable to iterate through the register select bits ((inst as inst. Ldm. Stm). regs) n Perform memory access using Memory. Read and Memory. Write n Don’t worry about PC or overwriting the base register yet n ACi. D Summer School 2002 Balsa Tutorial: - 87

Some Important Information Instruction L bit P bit U bit ldmda/ldmfa ldmia/ldmfd ldmdb/ldmea ldmib/ldmed stmda/stmed stmia/stmea stmdb/stmfd stmib/stmfa 1 1 0 0 0 1 1 ACi. D Summer School 2002 Balsa Tutorial: - 88 0 1 0 1

Some Important Information 2 W bit specifies whether the base register is to be written back (W=1) or keep its pre-LDM/STM value (W=0) n The “!” in the mnemonic selects writeback n Ignore the S bit - it’s used for processor mode changes (e. g. ISR returns) n ACi. D Summer School 2002 Balsa Tutorial: - 89

Some Important Information 3 To help with debugging, Balsa has the print command n Prints simulation values in LARD n Example: n • b <- v 1; print “Hello”; b <- v 2 • print “v 1=“, v 1, “v 2=“, v 2 n Enjoy ACi. D Summer School 2002 Balsa Tutorial: - 90

Additional Exercises n A choice of advanced design exercises: • A general shifter • A bit population counter n Language Summary in handout + code listings ACi. D Summer School 2002 Balsa Tutorial: - 91

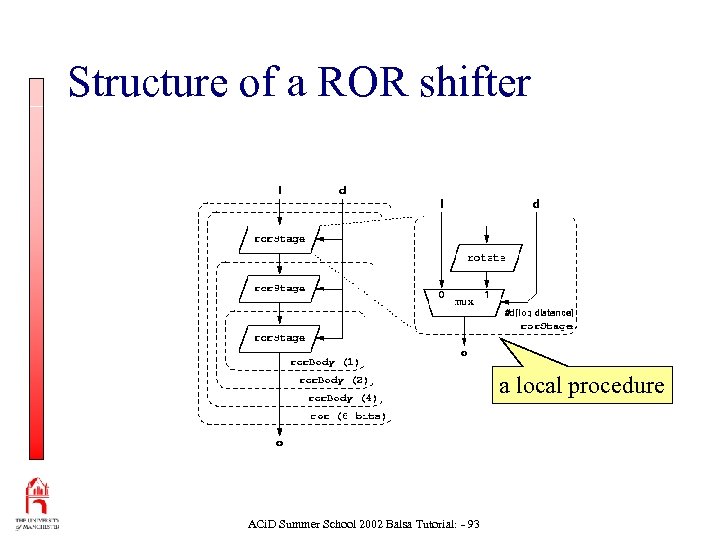

A Balsa Shifter General shifters required for processors n Write a description for a rotate right function n • solution in ror/solution n Alternatively extend the standard solution to other shift functions ACi. D Summer School 2002 Balsa Tutorial: - 92

Structure of a ROR shifter a local procedure ACi. D Summer School 2002 Balsa Tutorial: - 93

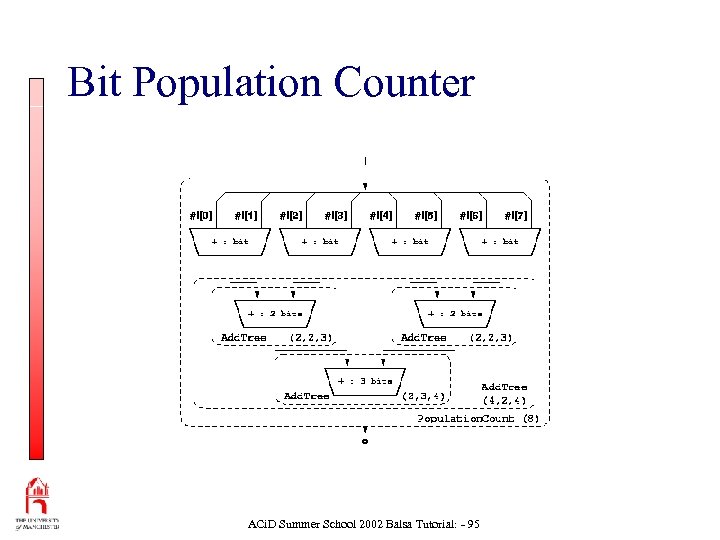

Bit Population Counter Counting the number of bits that are set to ‘ 1’ is necessary for ARM’s LDM/STM instructions n Write description for such a unit n • solution in popcount/solution ACi. D Summer School 2002 Balsa Tutorial: - 94

Bit Population Counter ACi. D Summer School 2002 Balsa Tutorial: - 95

Login and Account Setup Login with tpacid. XX … n Make sure this is your allocated group account name, not just tpacid 02 n > /usr/openwin/bin/openwin n In a shell window > bash n > rmdir balsa n > gtar xzf /softs/balsa/examples. tar. gz n ACi. D Summer School 2002 Balsa Tutorial: - 96

0dcd1d1e885de5b6f44b1403cae2dec9.ppt