b03e1081fe54b74f92891fa0748bcea1.ppt

- Количество слайдов: 19

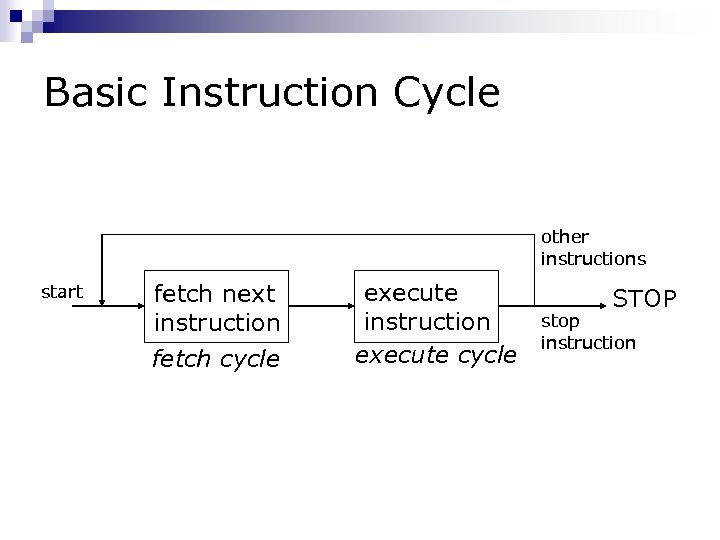

Basic Instruction Cycle other instructions start fetch next instruction fetch cycle execute instruction execute cycle STOP stop instruction

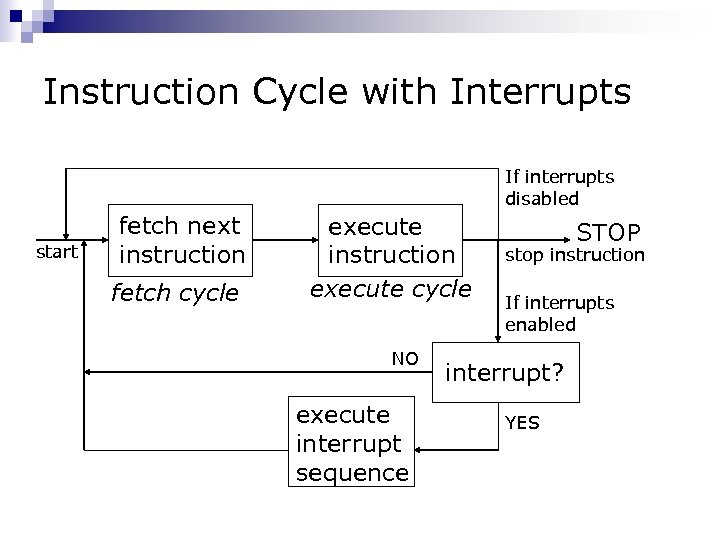

Instruction Cycle with Interrupts If interrupts disabled start fetch next instruction fetch cycle execute instruction execute cycle NO execute interrupt sequence STOP stop instruction If interrupts enabled interrupt? YES

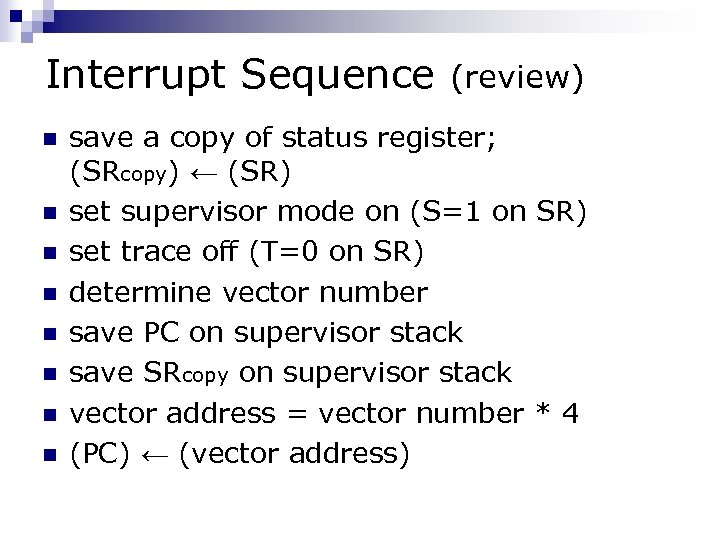

Interrupt Sequence n n n n (review) save a copy of status register; (SRcopy) ← (SR) set supervisor mode on (S=1 on SR) set trace off (T=0 on SR) determine vector number save PC on supervisor stack save SRcopy on supervisor stack vector address = vector number * 4 (PC) ← (vector address)

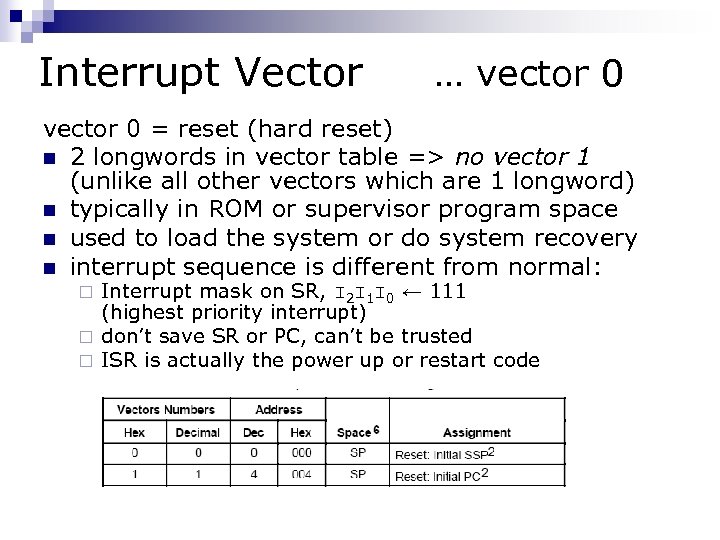

Interrupt Vector … vector 0 = reset (hard reset) n 2 longwords in vector table => no vector 1 (unlike all other vectors which are 1 longword) n typically in ROM or supervisor program space n used to load the system or do system recovery n interrupt sequence is different from normal: Interrupt mask on SR, I 2 I 1 I 0 ← 111 (highest priority interrupt) ¨ don’t save SR or PC, can’t be trusted ¨ ISR is actually the power up or restart code ¨

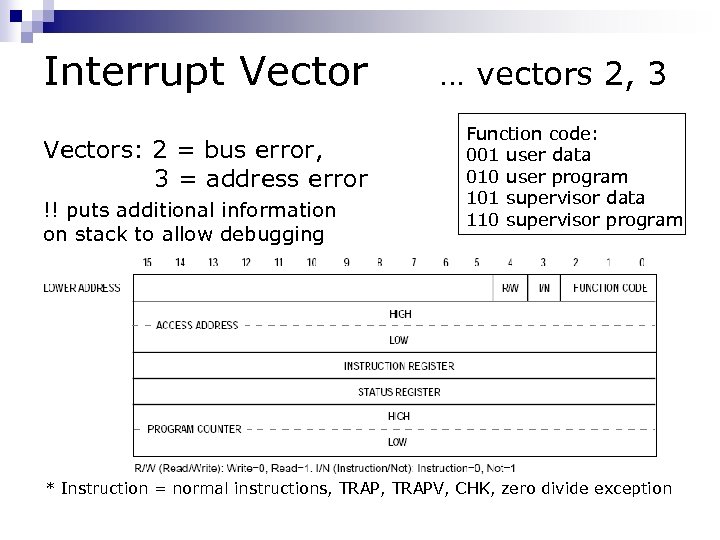

Interrupt Vectors: 2 = bus error, 3 = address error !! puts additional information on stack to allow debugging … vectors 2, 3 Function code: 001 user data 010 user program 101 supervisor data 110 supervisor program * Instruction = normal instructions, TRAPV, CHK, zero divide exception

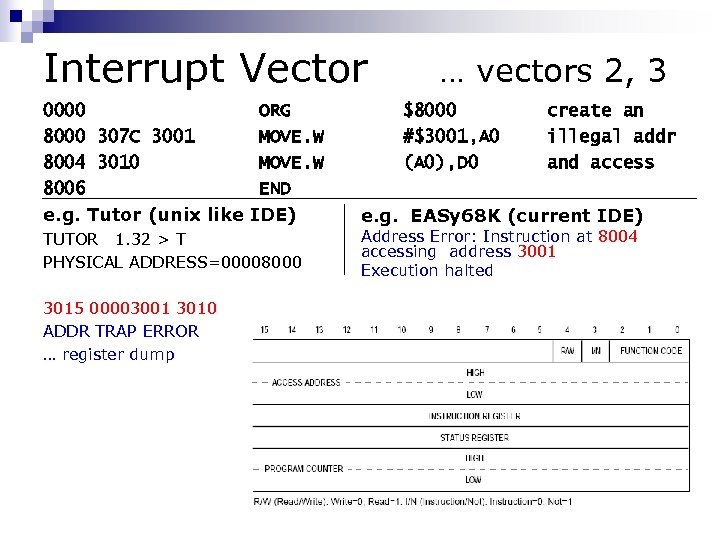

Interrupt Vector 0000 8000 307 C 3001 8004 3010 8006 e. g. Tutor (unix like ORG MOVE. W END IDE) TUTOR 1. 32 > T PHYSICAL ADDRESS=00008000 3015 00003001 3010 ADDR TRAP ERROR … register dump … vectors 2, 3 $8000 #$3001, A 0 (A 0), D 0 create an illegal addr and access e. g. EASy 68 K (current IDE) Address Error: Instruction at 8004 accessing address 3001 Execution halted

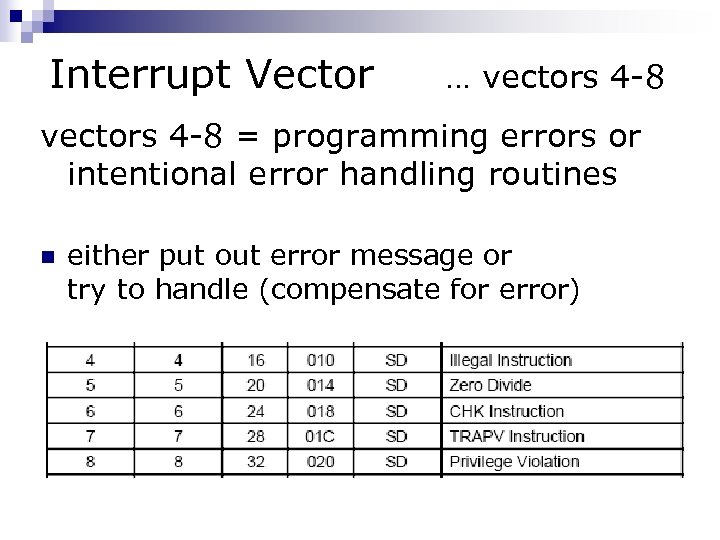

Interrupt Vector … vectors 4 -8 = programming errors or intentional error handling routines n either put out error message or try to handle (compensate for error)

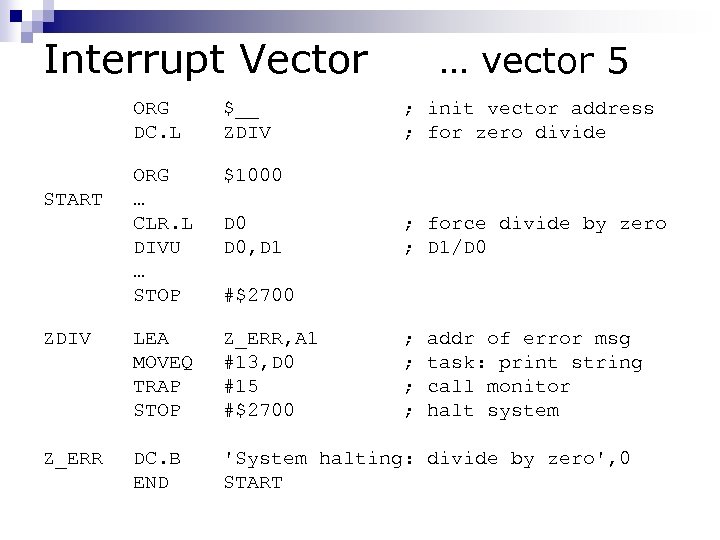

Interrupt Vector … vector 5 ORG DC. L $__ ZDIV ORG … CLR. L DIVU … STOP $1000 ZDIV LEA MOVEQ TRAP STOP Z_ERR, A 1 #13, D 0 #15 #$2700 Z_ERR DC. B END 'System halting: divide by zero', 0 START D 0, D 1 ; init vector address ; for zero divide ; force divide by zero ; D 1/D 0 #$2700 ; ; addr of error msg task: print string call monitor halt system

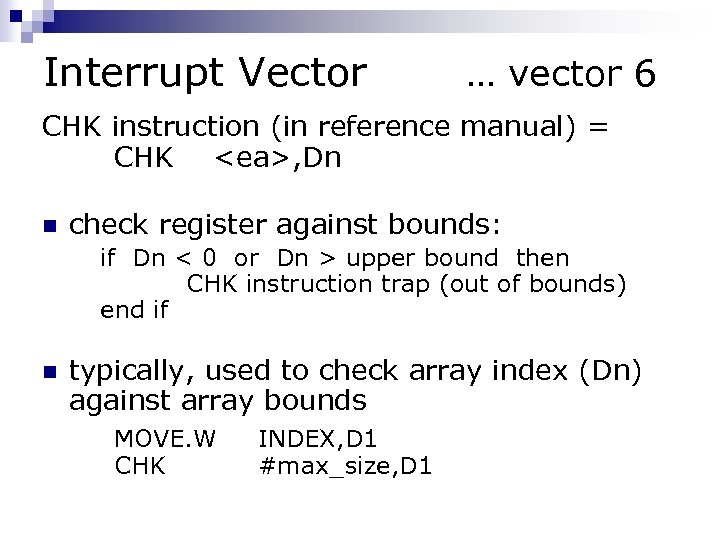

Interrupt Vector … vector 6 CHK instruction (in reference manual) = CHK <ea>, Dn n check register against bounds: if Dn < 0 or Dn > upper bound then CHK instruction trap (out of bounds) end if n typically, used to check array index (Dn) against array bounds MOVE. W CHK INDEX, D 1 #max_size, D 1

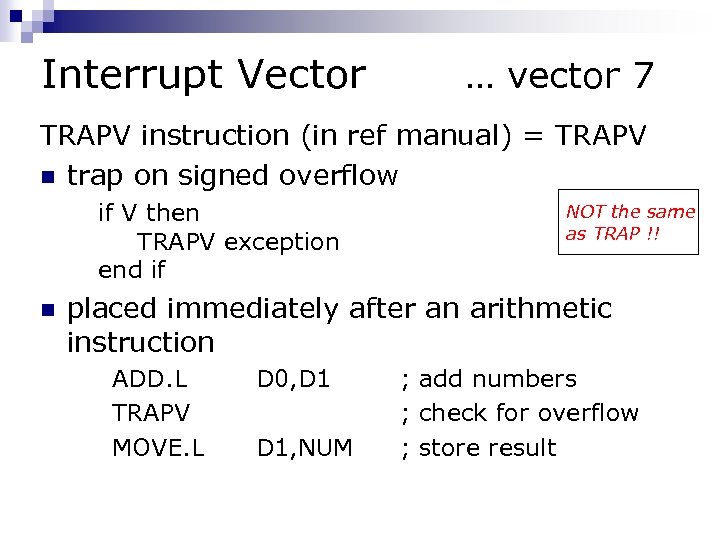

Interrupt Vector … vector 7 TRAPV instruction (in ref manual) = TRAPV n trap on signed overflow if V then TRAPV exception end if n NOT the same as TRAP !! placed immediately after an arithmetic instruction ADD. L TRAPV MOVE. L D 0, D 1, NUM ; add numbers ; check for overflow ; store result

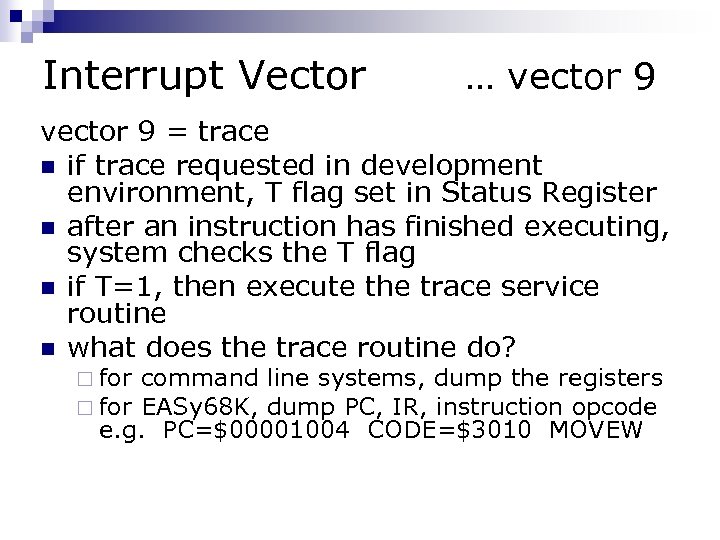

Interrupt Vector … vector 9 = trace n if trace requested in development environment, T flag set in Status Register n after an instruction has finished executing, system checks the T flag n if T=1, then execute the trace service routine n what does the trace routine do? ¨ for command line systems, dump the registers EASy 68 K, dump PC, IR, instruction opcode e. g. PC=$00001004 CODE=$3010 MOVEW

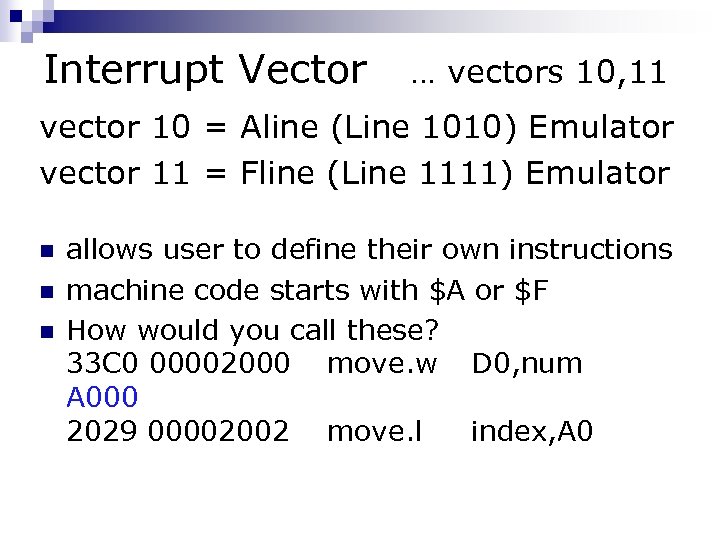

Interrupt Vector … vectors 10, 11 vector 10 = Aline (Line 1010) Emulator vector 11 = Fline (Line 1111) Emulator n n n allows user to define their own instructions machine code starts with $A or $F How would you call these? 33 C 0 00002000 move. w D 0, num A 000 2029 00002002 move. l index, A 0

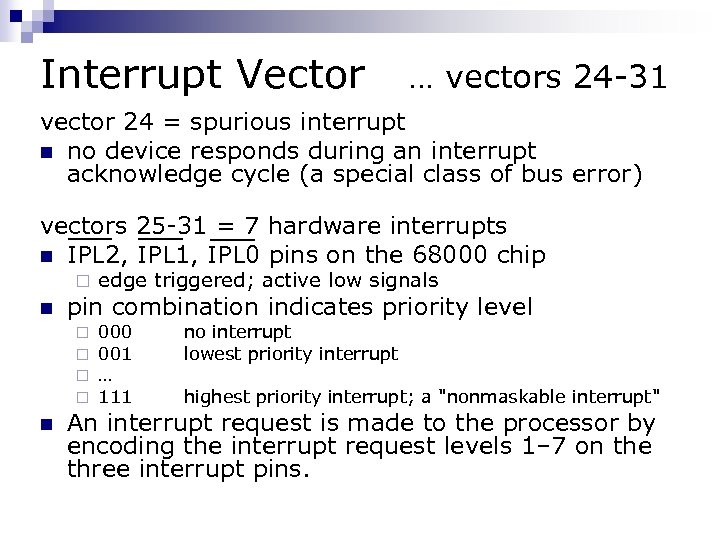

Interrupt Vector … vectors 24 -31 vector 24 = spurious interrupt n no device responds during an interrupt acknowledge cycle (a special class of bus error) vectors 25 -31 = 7 hardware interrupts n IPL 2, IPL 1, IPL 0 pins on the 68000 chip ¨ n pin combination indicates priority level ¨ ¨ n edge triggered; active low signals 000 001 … 111 no interrupt lowest priority interrupt highest priority interrupt; a "nonmaskable interrupt" An interrupt request is made to the processor by encoding the interrupt request levels 1– 7 on the three interrupt pins.

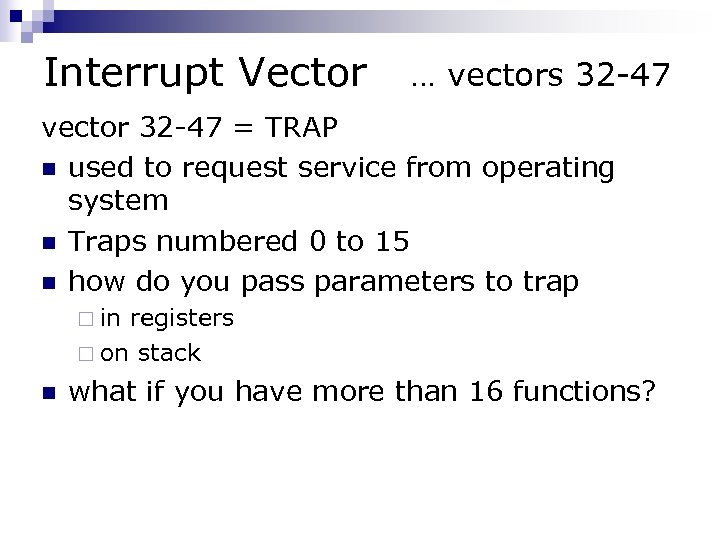

Interrupt Vector … vectors 32 -47 vector 32 -47 = TRAP n used to request service from operating system n Traps numbered 0 to 15 n how do you pass parameters to trap ¨ in registers ¨ on stack n what if you have more than 16 functions?

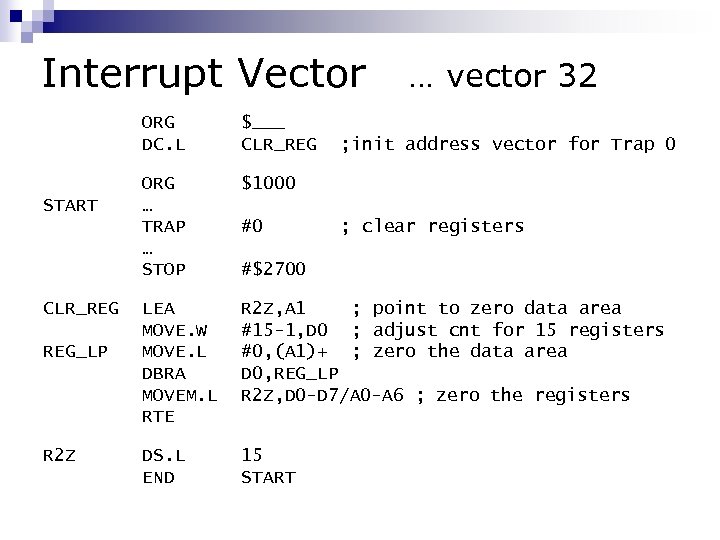

Interrupt Vector … vector 32 ORG DC. L START CLR_REG REG_LP R 2 Z $___ CLR_REG ORG … TRAP … STOP $1000 LEA MOVE. W MOVE. L DBRA MOVEM. L RTE R 2 Z, A 1 ; point to zero data area #15 -1, D 0 ; adjust cnt for 15 registers #0, (A 1)+ ; zero the data area D 0, REG_LP R 2 Z, D 0 -D 7/A 0 -A 6 ; zero the registers DS. L END 15 START #0 ; init address vector for Trap 0 ; clear registers #$2700

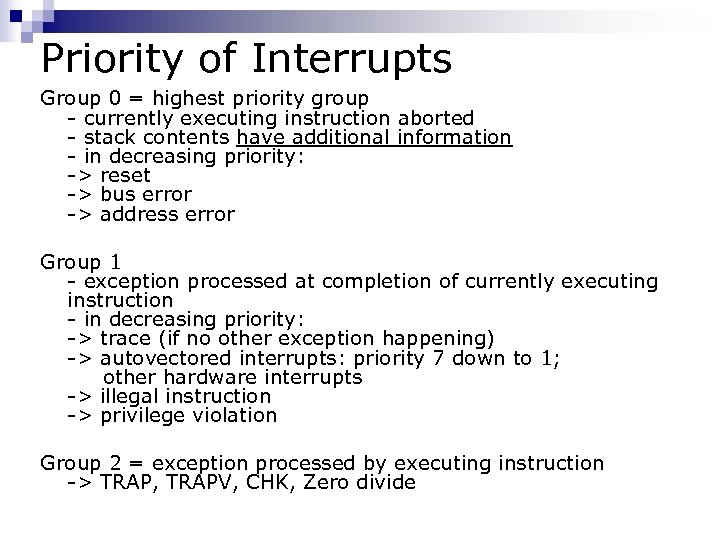

Priority of Interrupts Group 0 = highest priority group - currently executing instruction aborted - stack contents have additional information - in decreasing priority: -> reset -> bus error -> address error Group 1 - exception processed at completion of currently executing instruction - in decreasing priority: -> trace (if no other exception happening) -> autovectored interrupts: priority 7 down to 1; other hardware interrupts -> illegal instruction -> privilege violation Group 2 = exception processed by executing instruction -> TRAP, TRAPV, CHK, Zero divide

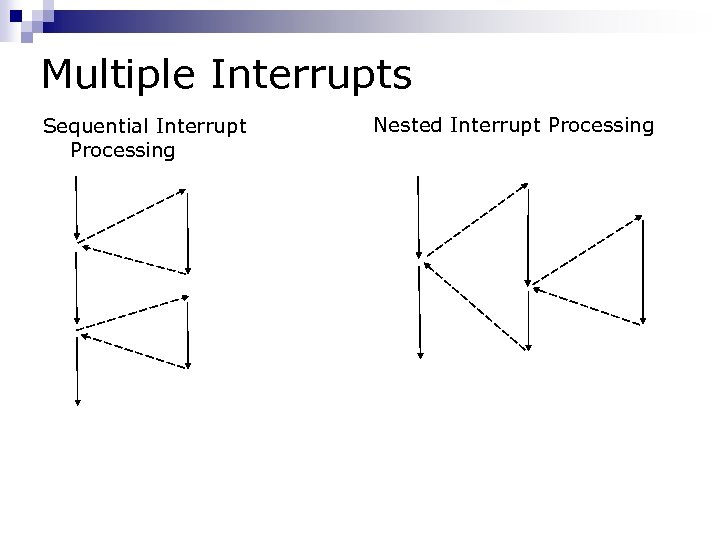

Multiple Interrupts Sequential Interrupt Processing Nested Interrupt Processing

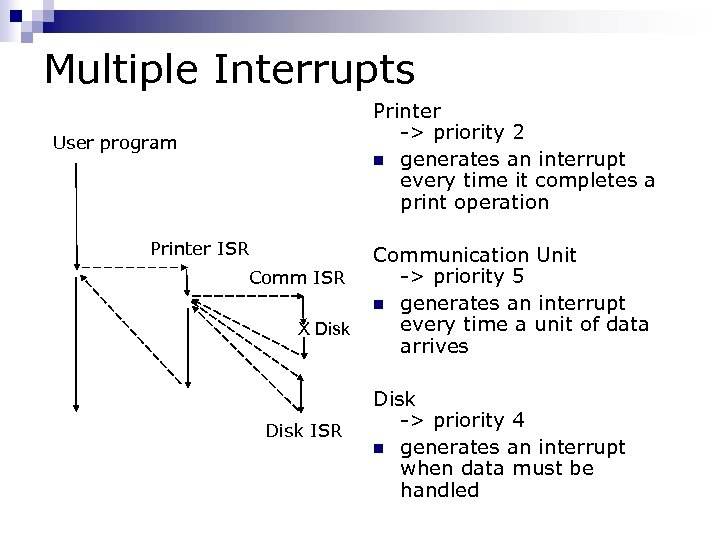

Multiple Interrupts Printer -> priority 2 n generates an interrupt every time it completes a print operation User program Printer ISR Comm ISR X Disk ISR Communication Unit -> priority 5 n generates an interrupt every time a unit of data arrives Disk -> priority 4 n generates an interrupt when data must be handled

Reading/Expectations Reading: n Section 6 - Exception Processing from M 68000 8 -/16 -/32 Bit Microprocessors User’s Manual [pdf, 184 p; Motorola] Expectations: n you are responsible for all material in the above section, excluding references to M 68010 n you should be able to write interrupt service routines for any vector including determining the vector address n you should be able to determine the order of interrupts based on priority and time of arrival for a multiple interrupt system

b03e1081fe54b74f92891fa0748bcea1.ppt