170c928f49b27d46658ff4456ea8c2be.ppt

- Количество слайдов: 13

Automated TFT Noise Characterization Platform Kendell Clark (EE), Stephen Marshall (EE), Carmen Parisi (EE), James Spoth (CE), Ryan Vaughan (ME) Rochester Institute of Technology Analog Devices Integrated Microsystems Laboratory

Automated TFT Noise Characterization Platform Kendell Clark (EE), Stephen Marshall (EE), Carmen Parisi (EE), James Spoth (CE), Ryan Vaughan (ME) Rochester Institute of Technology Analog Devices Integrated Microsystems Laboratory

Project Overview n n Aimed at research groups without the budget to purchase commercially available solutions which can retail at over 1 million dollars. n ADIML Design & build an automated low noise measurement environment for the purpose of characterizing on wafer devices, specifically monocrystalline silicon TFTs on glass. System should provide a streamlined measurement process which reduces measurement time and complexity. RIT

Project Overview n n Aimed at research groups without the budget to purchase commercially available solutions which can retail at over 1 million dollars. n ADIML Design & build an automated low noise measurement environment for the purpose of characterizing on wafer devices, specifically monocrystalline silicon TFTs on glass. System should provide a streamlined measurement process which reduces measurement time and complexity. RIT

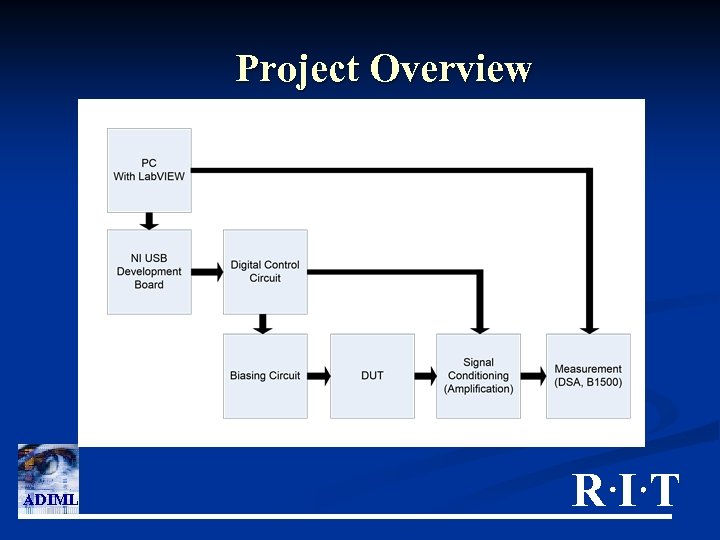

Project Overview ADIML RIT

Project Overview ADIML RIT

Project Specifications n Mechanical n n Electrical – Digital Circuitry & Software n n n ADIML Construct an RF/EMI shielded container which fits over existing probe station (Cascade Microtech M 150) Shielded container must not interfere with the normal operation of the probe station. Must allow probe station microscope to view wafer while in place. Interface custom bias circuitry to lab PC. Control DUT bias settings, signal amplifiers, and lab measurement equipment. NO clocks or oscillators allowed in the shielded container. RIT

Project Specifications n Mechanical n n Electrical – Digital Circuitry & Software n n n ADIML Construct an RF/EMI shielded container which fits over existing probe station (Cascade Microtech M 150) Shielded container must not interfere with the normal operation of the probe station. Must allow probe station microscope to view wafer while in place. Interface custom bias circuitry to lab PC. Control DUT bias settings, signal amplifiers, and lab measurement equipment. NO clocks or oscillators allowed in the shielded container. RIT

Project Specifications n Electrical – Analog Bias Circuitry n n n ADIML Allow user to set DUT bias points based off of the device’s I-V curves. Provide the low level noise signals with adequate amplification so they can be measured by lab equipment. Noise floor must be as low as possible to ensure accurate noise measurements of the DUT. RIT

Project Specifications n Electrical – Analog Bias Circuitry n n n ADIML Allow user to set DUT bias points based off of the device’s I-V curves. Provide the low level noise signals with adequate amplification so they can be measured by lab equipment. Noise floor must be as low as possible to ensure accurate noise measurements of the DUT. RIT

Project Specifications n Electrical – Analog Bias Circuitry n n n ADIML Allow user to set DUT bias points based off of the device’s I-V curves. Provide the low level noise signals with adequate amplification so they can be measured by lab equipment. Noise floor must be as low as possible to ensure accurate noise measurements of the DUT. RIT

Project Specifications n Electrical – Analog Bias Circuitry n n n ADIML Allow user to set DUT bias points based off of the device’s I-V curves. Provide the low level noise signals with adequate amplification so they can be measured by lab equipment. Noise floor must be as low as possible to ensure accurate noise measurements of the DUT. RIT

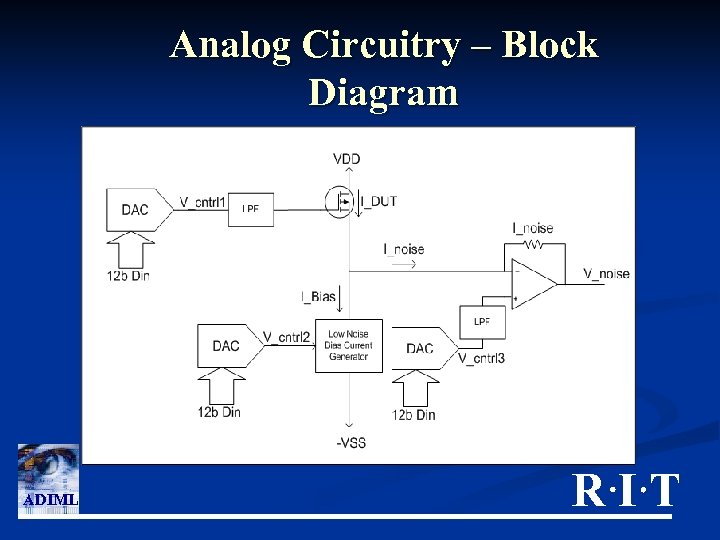

Analog Circuitry – Block Diagram ADIML RIT

Analog Circuitry – Block Diagram ADIML RIT

Analog Circuitry – Voltage Bias Circuitry n n Control Voltage comes from a DAC located on the PCB. RFilter & C form a LPF with corner frequency of 1 m. Hz. n n ADIML RCharge allows for capacitor to reach desired voltage levels quickly. >60 d. B attenuation of noise in the measurement frequency range, 1 Hz to 100 k. Hz RIT

Analog Circuitry – Voltage Bias Circuitry n n Control Voltage comes from a DAC located on the PCB. RFilter & C form a LPF with corner frequency of 1 m. Hz. n n ADIML RCharge allows for capacitor to reach desired voltage levels quickly. >60 d. B attenuation of noise in the measurement frequency range, 1 Hz to 100 k. Hz RIT

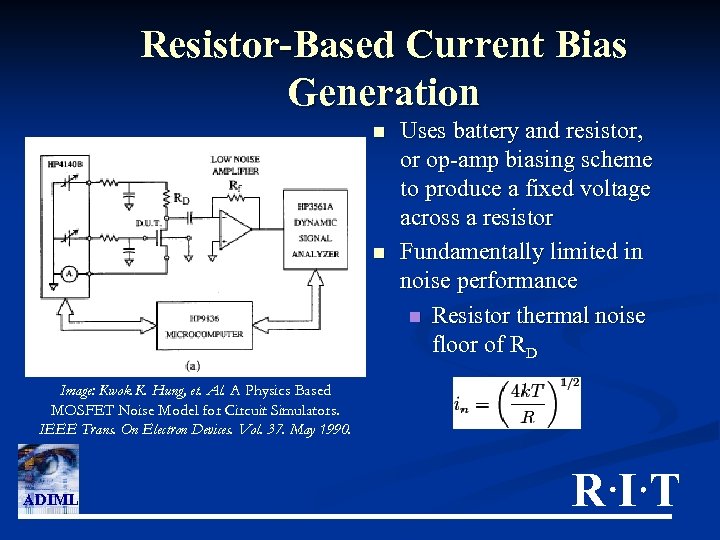

Resistor-Based Current Bias Generation n n Uses battery and resistor, or op-amp biasing scheme to produce a fixed voltage across a resistor Fundamentally limited in noise performance n Resistor thermal noise floor of RD Image: Kwok K. Hung, et. Al. A Physics Based MOSFET Noise Model for Circuit Simulators. IEEE Trans. On Electron Devices. Vol. 37. May 1990. ADIML RIT

Resistor-Based Current Bias Generation n n Uses battery and resistor, or op-amp biasing scheme to produce a fixed voltage across a resistor Fundamentally limited in noise performance n Resistor thermal noise floor of RD Image: Kwok K. Hung, et. Al. A Physics Based MOSFET Noise Model for Circuit Simulators. IEEE Trans. On Electron Devices. Vol. 37. May 1990. ADIML RIT

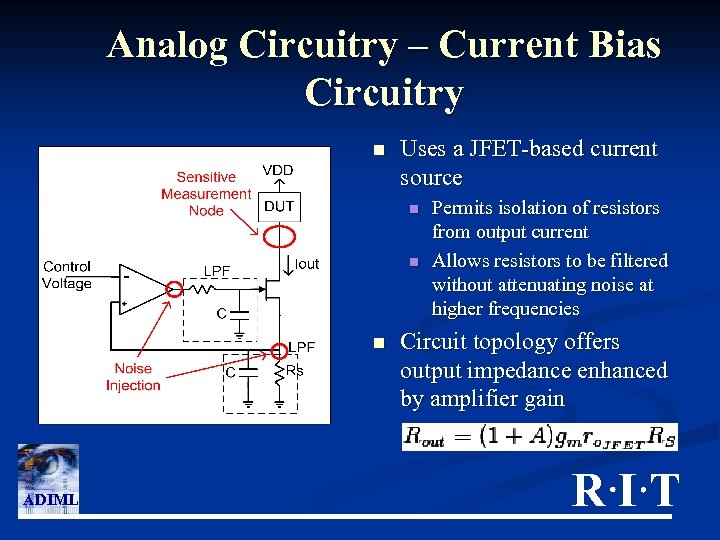

Analog Circuitry – Current Bias Circuitry n Uses a JFET-based current source n n n ADIML Permits isolation of resistors from output current Allows resistors to be filtered without attenuating noise at higher frequencies Circuit topology offers output impedance enhanced by amplifier gain RIT

Analog Circuitry – Current Bias Circuitry n Uses a JFET-based current source n n n ADIML Permits isolation of resistors from output current Allows resistors to be filtered without attenuating noise at higher frequencies Circuit topology offers output impedance enhanced by amplifier gain RIT

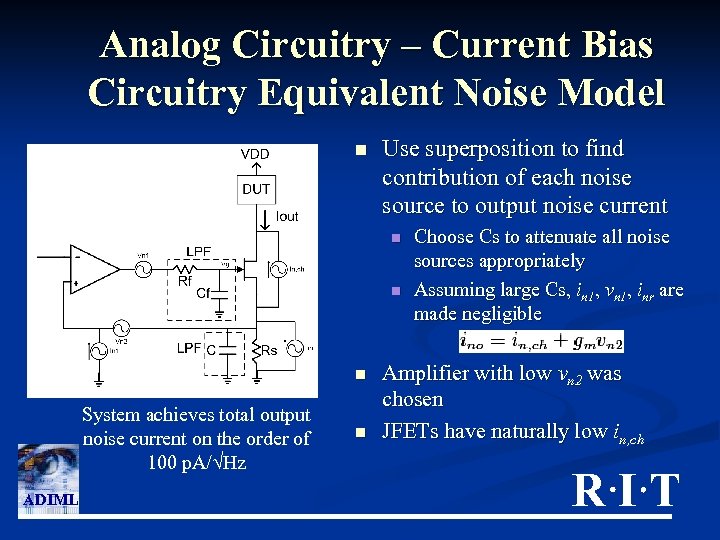

Analog Circuitry – Current Bias Circuitry Equivalent Noise Model n Use superposition to find contribution of each noise source to output noise current n n n System achieves total output noise current on the order of 100 p. A/√Hz ADIML n Choose Cs to attenuate all noise sources appropriately Assuming large Cs, in 1, vn 1, inr are made negligible Amplifier with low vn 2 was chosen JFETs have naturally low in, ch RIT

Analog Circuitry – Current Bias Circuitry Equivalent Noise Model n Use superposition to find contribution of each noise source to output noise current n n n System achieves total output noise current on the order of 100 p. A/√Hz ADIML n Choose Cs to attenuate all noise sources appropriately Assuming large Cs, in 1, vn 1, inr are made negligible Amplifier with low vn 2 was chosen JFETs have naturally low in, ch RIT

![References n n ADIML [1] Johns, David A. and Ken Martin. Analog Integrated Circuit References n n ADIML [1] Johns, David A. and Ken Martin. Analog Integrated Circuit](https://present5.com/presentation/170c928f49b27d46658ff4456ea8c2be/image-12.jpg) References n n ADIML [1] Johns, David A. and Ken Martin. Analog Integrated Circuit Design. John Wiley and Sons. 1997. [2] Stanford Research Systems. Model SR 570 – Low Noise Current Preamplifer. SRS, Inc. 1997. [3] Kwok K. Hung, et. Al. A Physics Based MOSFET Noise Model for Circuit Simulators. IEEE Trans. On Electron Devices. Vol. 37. May 1990. Expanded list available at booth RIT

References n n ADIML [1] Johns, David A. and Ken Martin. Analog Integrated Circuit Design. John Wiley and Sons. 1997. [2] Stanford Research Systems. Model SR 570 – Low Noise Current Preamplifer. SRS, Inc. 1997. [3] Kwok K. Hung, et. Al. A Physics Based MOSFET Noise Model for Circuit Simulators. IEEE Trans. On Electron Devices. Vol. 37. May 1990. Expanded list available at booth RIT

Acknowledgements n n ADIML Dr. Robert J. Bowman, Faculty Advisor and Principal Investigator Professor George Slack, Faculty Mentor and Guide RIT

Acknowledgements n n ADIML Dr. Robert J. Bowman, Faculty Advisor and Principal Investigator Professor George Slack, Faculty Mentor and Guide RIT