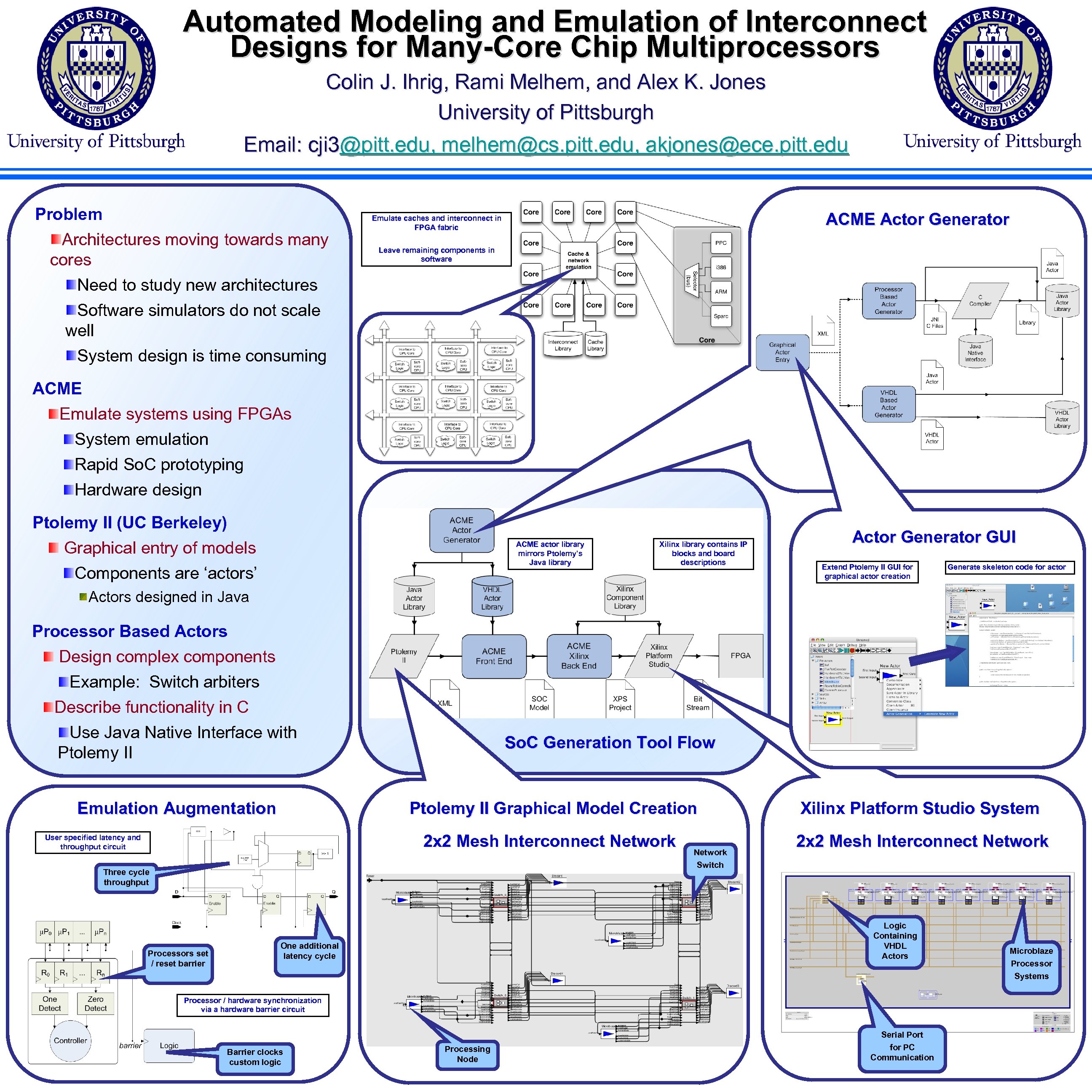

Automated Modeling and Emulation of Interconnect Designs for Many-Core Chip Multiprocessors Colin J. Ihrig, Rami Melhem, and Alex K. Jones University of Pittsburgh ACME Actor Generator Email: cji 3@pitt. edu, melhem@cs. pitt. edu, akjones@ece. pitt. edu Problem Architectures moving towards many cores Need to study new architectures Software simulators do not scale well System design is time consuming ACME Actor Generator Emulate caches and interconnect in FPGA fabric Leave remaining components in software ACME Emulate systems using FPGAs System emulation Rapid So. C prototyping Hardware design Ptolemy II (UC Berkeley) Graphical entry of models ACME actor library mirrors Ptolemy’s Java library Components are ‘actors’ Xilinx library contains IP blocks and board descriptions Actor Generator GUI Extend Ptolemy II GUI for graphical actor creation Generate skeleton code for actor Actors designed in Java Processor Based Actors Design complex components Example: Switch arbiters Describe functionality in C Use Java Native Interface with Ptolemy II So. C Generation Tool Flow Ptolemy II Graphical Model Creation User specified latency and throughput circuit Xilinx Platform Studio System 2 x 2 Mesh Interconnect Network Emulation Augmentation 2 x 2 Mesh Interconnect Network Three cycle throughput Processors set / reset barrier Network Switch Logic Containing VHDL Actors One additional latency cycle Microblaze Processor Systems Processor / hardware synchronization via a hardware barrier circuit Barrier clocks custom logic Processing Node Serial Port for PC Communication

Automated Modeling and Emulation of Interconnect Designs for Many-Core Chip Multiprocessors Colin J. Ihrig, Rami Melhem, and Alex K. Jones University of Pittsburgh ACME Actor Generator Email: cji 3@pitt. edu, melhem@cs. pitt. edu, akjones@ece. pitt. edu Problem Architectures moving towards many cores Need to study new architectures Software simulators do not scale well System design is time consuming ACME Actor Generator Emulate caches and interconnect in FPGA fabric Leave remaining components in software ACME Emulate systems using FPGAs System emulation Rapid So. C prototyping Hardware design Ptolemy II (UC Berkeley) Graphical entry of models ACME actor library mirrors Ptolemy’s Java library Components are ‘actors’ Xilinx library contains IP blocks and board descriptions Actor Generator GUI Extend Ptolemy II GUI for graphical actor creation Generate skeleton code for actor Actors designed in Java Processor Based Actors Design complex components Example: Switch arbiters Describe functionality in C Use Java Native Interface with Ptolemy II So. C Generation Tool Flow Ptolemy II Graphical Model Creation User specified latency and throughput circuit Xilinx Platform Studio System 2 x 2 Mesh Interconnect Network Emulation Augmentation 2 x 2 Mesh Interconnect Network Three cycle throughput Processors set / reset barrier Network Switch Logic Containing VHDL Actors One additional latency cycle Microblaze Processor Systems Processor / hardware synchronization via a hardware barrier circuit Barrier clocks custom logic Processing Node Serial Port for PC Communication

![]()