cccf81f87e8370d0fa6034c0f2877912.ppt

- Количество слайдов: 37

Automated Generation of Layout and Control for Quantum Circuits Mark Whitney, Nemanja Isailovic, Yatish Patel, John Kubiatowicz University of California, Berkeley

Automated Generation of Layout and Control for Quantum Circuits Mark Whitney, Nemanja Isailovic, Yatish Patel, John Kubiatowicz University of California, Berkeley

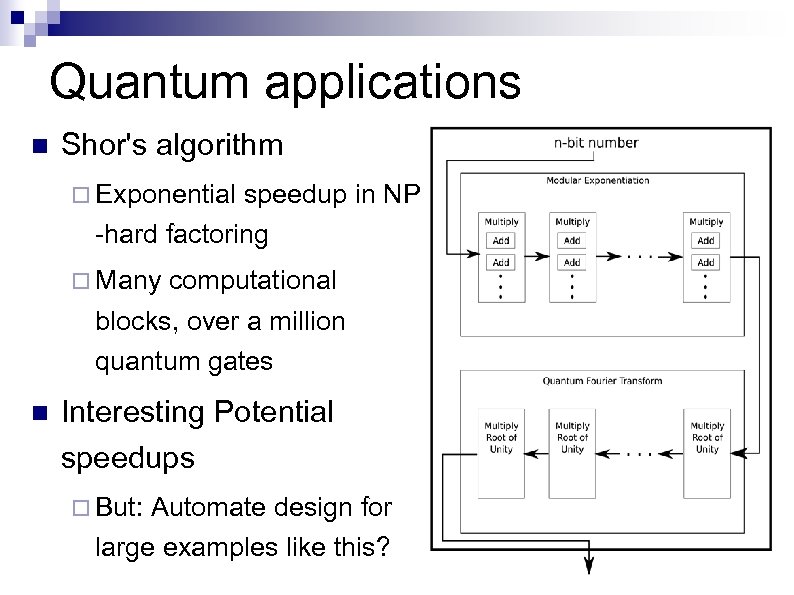

Quantum applications n Shor's algorithm ¨ Exponential speedup in NP -hard factoring ¨ Many computational blocks, over a million quantum gates n Interesting Potential speedups ¨ But: Automate design for large examples like this?

Quantum applications n Shor's algorithm ¨ Exponential speedup in NP -hard factoring ¨ Many computational blocks, over a million quantum gates n Interesting Potential speedups ¨ But: Automate design for large examples like this?

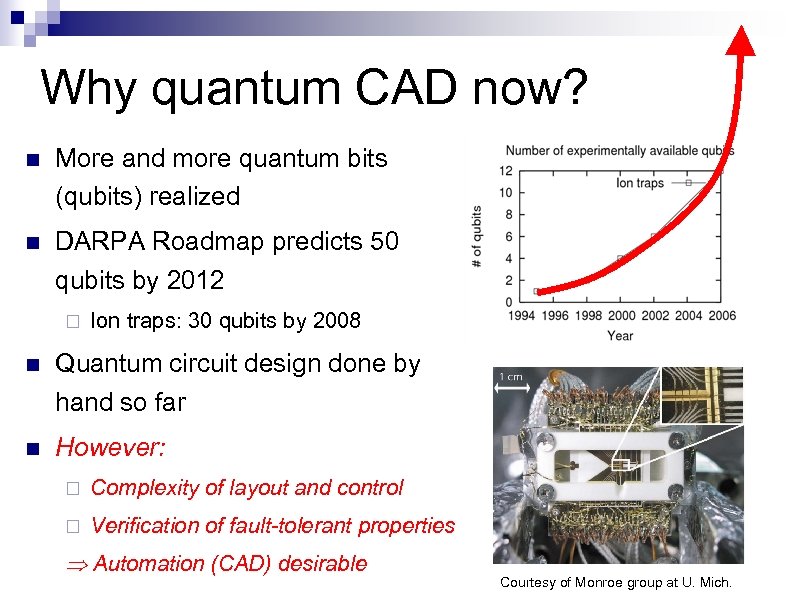

Why quantum CAD now? n More and more quantum bits (qubits) realized n DARPA Roadmap predicts 50 qubits by 2012 ¨ Ion traps: 30 qubits by 2008 n Quantum circuit design done by hand so far n However: ¨ Complexity of layout and control ¨ Verification of fault-tolerant properties Automation (CAD) desirable Courtesy of Monroe group at U. Mich.

Why quantum CAD now? n More and more quantum bits (qubits) realized n DARPA Roadmap predicts 50 qubits by 2012 ¨ Ion traps: 30 qubits by 2008 n Quantum circuit design done by hand so far n However: ¨ Complexity of layout and control ¨ Verification of fault-tolerant properties Automation (CAD) desirable Courtesy of Monroe group at U. Mich.

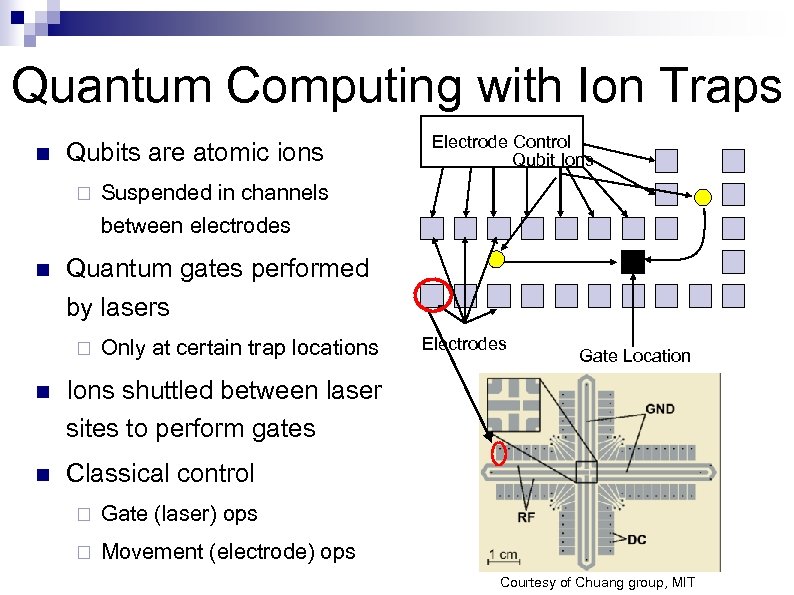

Quantum Computing with Ion Traps n Qubits are atomic ions ¨ n Electrode Control Qubit Ions Suspended in channels between electrodes Quantum gates performed by lasers ¨ Only at certain trap locations n Gate Location Ions shuttled between laser sites to perform gates n Electrodes Classical control ¨ Gate (laser) ops ¨ Movement (electrode) ops Courtesy of Chuang group, MIT

Quantum Computing with Ion Traps n Qubits are atomic ions ¨ n Electrode Control Qubit Ions Suspended in channels between electrodes Quantum gates performed by lasers ¨ Only at certain trap locations n Gate Location Ions shuttled between laser sites to perform gates n Electrodes Classical control ¨ Gate (laser) ops ¨ Movement (electrode) ops Courtesy of Chuang group, MIT

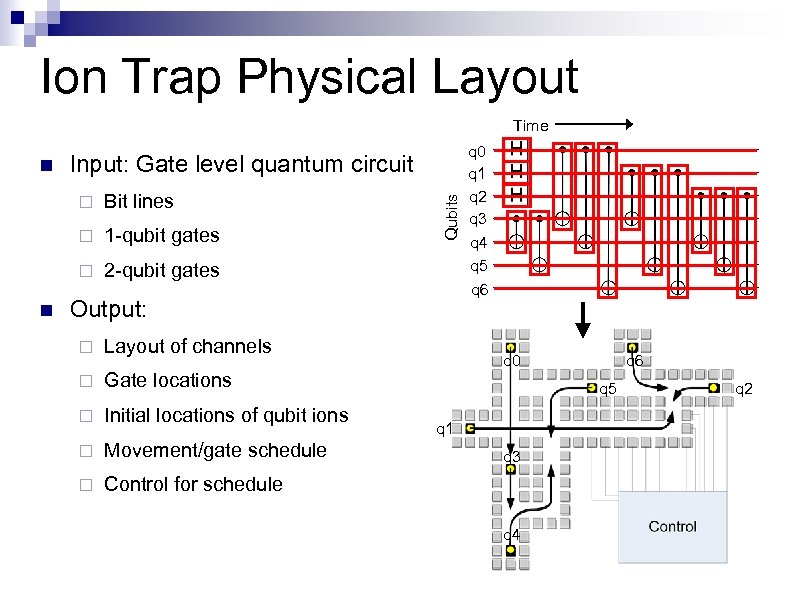

Ion Trap Physical Layout Time Input: Gate level quantum circuit ¨ ¨ 1 -qubit gates ¨ n Bit lines 2 -qubit gates Qubits n Output: ¨ Layout of channels ¨ Gate locations ¨ Initial locations of qubit ions ¨ Movement/gate schedule ¨ q 0 q 1 q 2 q 3 q 4 q 5 q 6 Control for schedule q 0 q 6 q 5 q 1 q 3 q 4 q 2

Ion Trap Physical Layout Time Input: Gate level quantum circuit ¨ ¨ 1 -qubit gates ¨ n Bit lines 2 -qubit gates Qubits n Output: ¨ Layout of channels ¨ Gate locations ¨ Initial locations of qubit ions ¨ Movement/gate schedule ¨ q 0 q 1 q 2 q 3 q 4 q 5 q 6 Control for schedule q 0 q 6 q 5 q 1 q 3 q 4 q 2

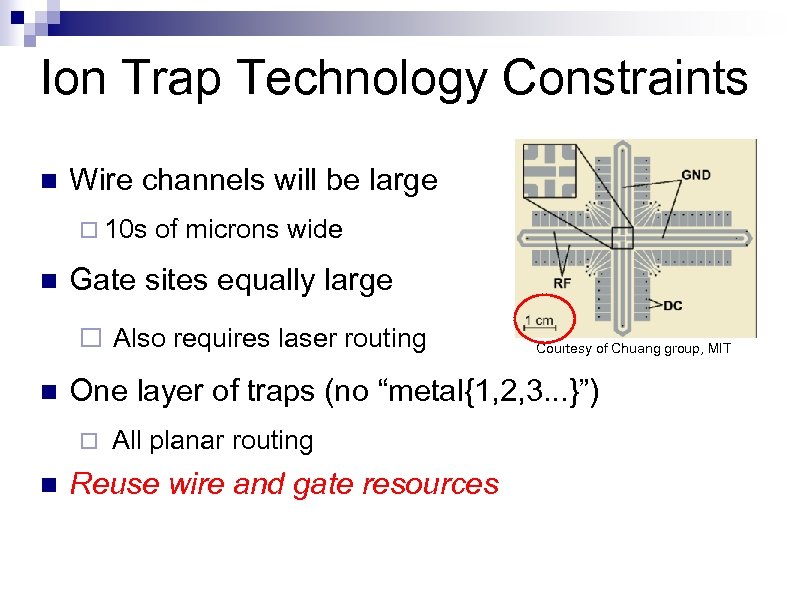

Ion Trap Technology Constraints n Wire channels will be large ¨ 10 s n of microns wide Gate sites equally large ¨ Also requires laser routing n One layer of traps (no “metal{1, 2, 3. . . }”) ¨ n Courtesy of Chuang group, MIT All planar routing Reuse wire and gate resources

Ion Trap Technology Constraints n Wire channels will be large ¨ 10 s n of microns wide Gate sites equally large ¨ Also requires laser routing n One layer of traps (no “metal{1, 2, 3. . . }”) ¨ n Courtesy of Chuang group, MIT All planar routing Reuse wire and gate resources

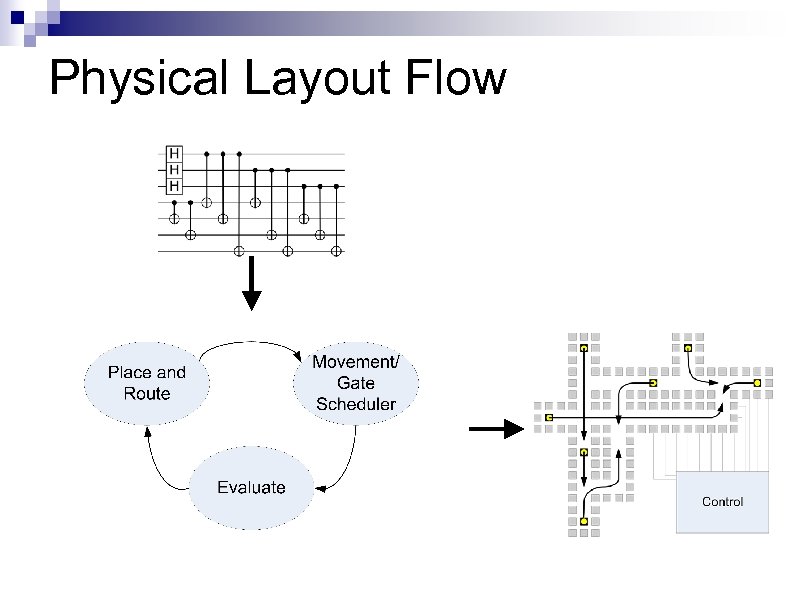

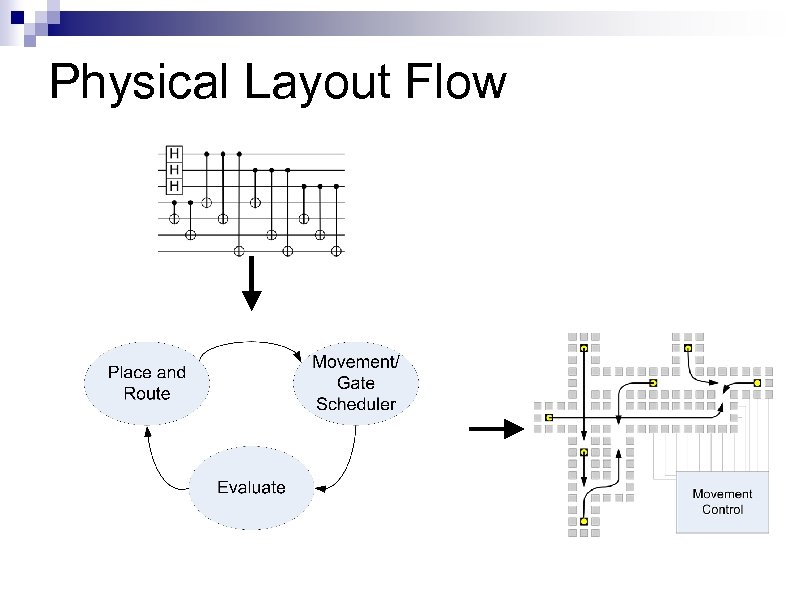

Physical Layout Flow

Physical Layout Flow

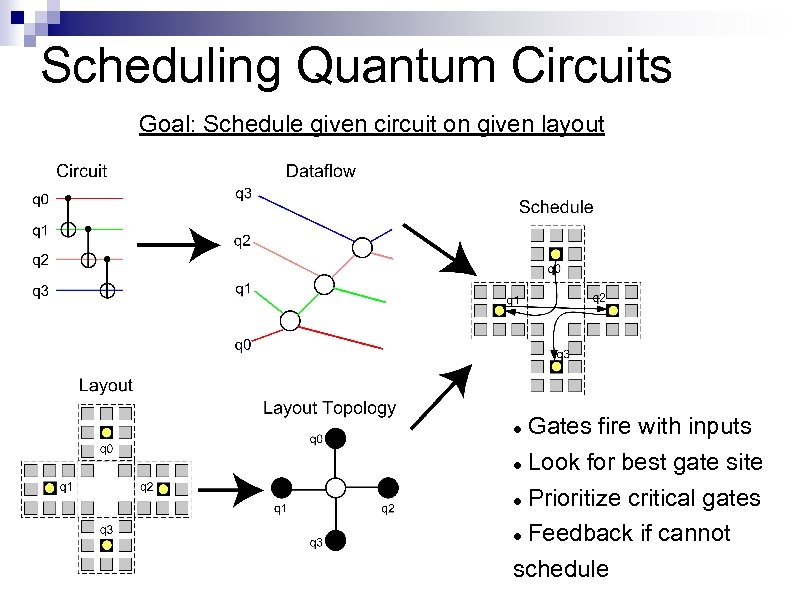

Scheduling Quantum Circuits Goal: Schedule given circuit on given layout Gates fire with inputs Look for best gate site Prioritize critical gates Feedback if cannot schedule

Scheduling Quantum Circuits Goal: Schedule given circuit on given layout Gates fire with inputs Look for best gate site Prioritize critical gates Feedback if cannot schedule

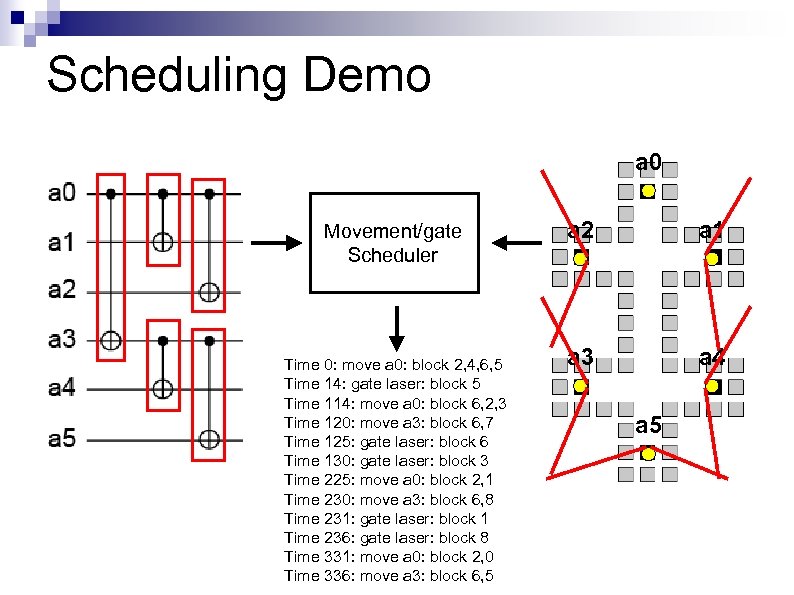

Scheduling Demo a 0 Movement/gate Scheduler Time 0: move a 0: block 2, 4, 6, 5 Time 14: gate laser: block 5 Time 114: move a 0: block 6, 2, 3 Time 120: move a 3: block 6, 7 Time 125: gate laser: block 6 Time 130: gate laser: block 3 Time 225: move a 0: block 2, 1 Time 230: move a 3: block 6, 8 Time 231: gate laser: block 1 Time 236: gate laser: block 8 Time 331: move a 0: block 2, 0 Time 336: move a 3: block 6, 5 a 2 a 1 a 3 a 4 a 5

Scheduling Demo a 0 Movement/gate Scheduler Time 0: move a 0: block 2, 4, 6, 5 Time 14: gate laser: block 5 Time 114: move a 0: block 6, 2, 3 Time 120: move a 3: block 6, 7 Time 125: gate laser: block 6 Time 130: gate laser: block 3 Time 225: move a 0: block 2, 1 Time 230: move a 3: block 6, 8 Time 231: gate laser: block 1 Time 236: gate laser: block 8 Time 331: move a 0: block 2, 0 Time 336: move a 3: block 6, 5 a 2 a 1 a 3 a 4 a 5

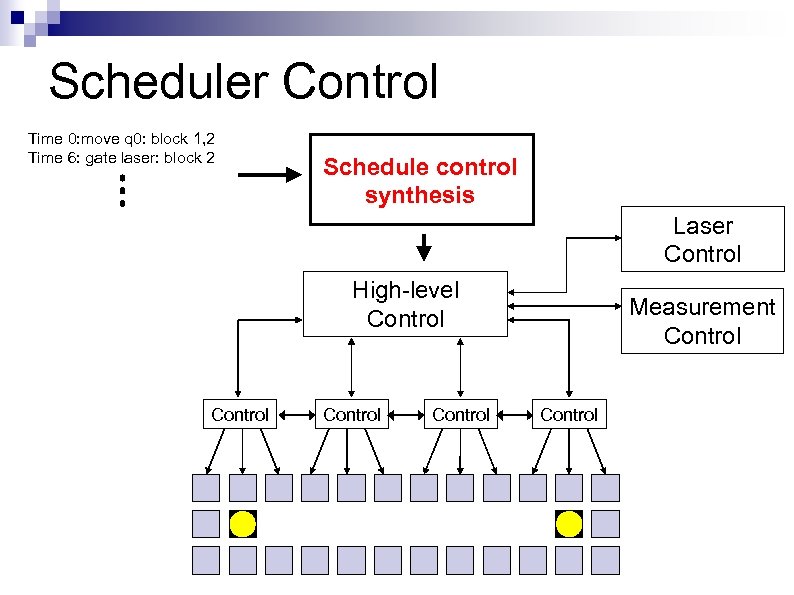

Scheduler Control Time 0: move q 0: block 1, 2 Time 6: gate laser: block 2 Schedule control synthesis Laser Control High-level Control Measurement Control

Scheduler Control Time 0: move q 0: block 1, 2 Time 6: gate laser: block 2 Schedule control synthesis Laser Control High-level Control Measurement Control

Physical Layout Flow

Physical Layout Flow

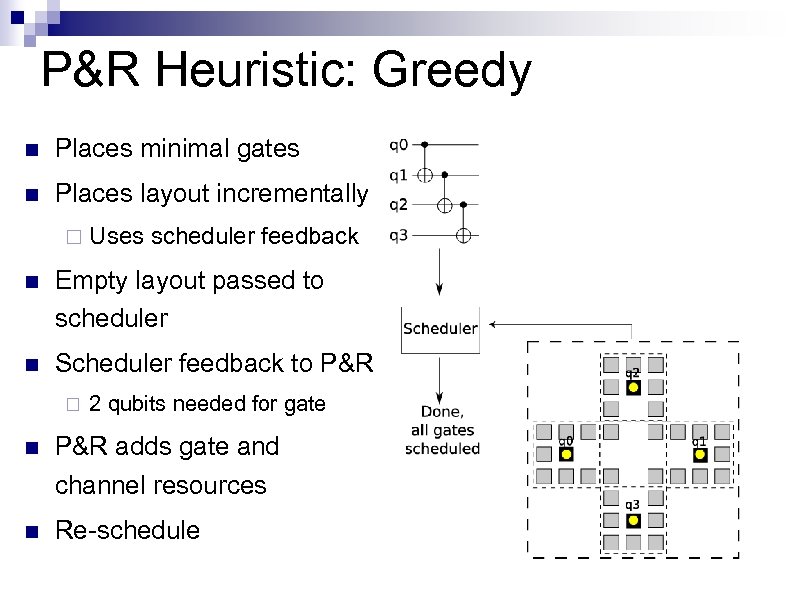

P&R Heuristic: Greedy n Places minimal gates n Places layout incrementally ¨ Uses scheduler feedback n Empty layout passed to scheduler n Scheduler feedback to P&R ¨ 2 qubits needed for gate n P&R adds gate and channel resources n Re-schedule

P&R Heuristic: Greedy n Places minimal gates n Places layout incrementally ¨ Uses scheduler feedback n Empty layout passed to scheduler n Scheduler feedback to P&R ¨ 2 qubits needed for gate n P&R adds gate and channel resources n Re-schedule

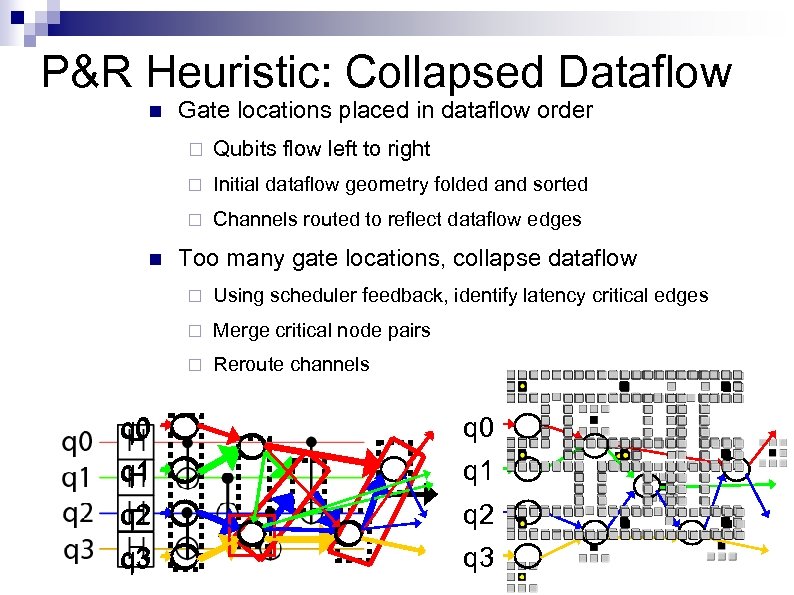

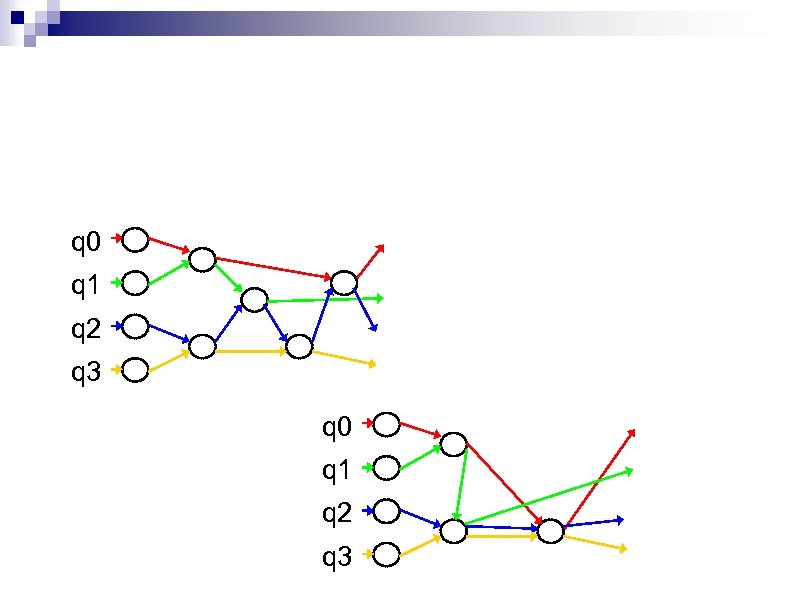

P&R Heuristic: Collapsed Dataflow n Gate locations placed in dataflow order ¨ ¨ Initial dataflow geometry folded and sorted ¨ n Qubits flow left to right Channels routed to reflect dataflow edges Too many gate locations, collapse dataflow ¨ Using scheduler feedback, identify latency critical edges ¨ Merge critical node pairs ¨ Reroute channels q 0 q 1 q 0 q 2 q 3 q 2 q 1 q 3

P&R Heuristic: Collapsed Dataflow n Gate locations placed in dataflow order ¨ ¨ Initial dataflow geometry folded and sorted ¨ n Qubits flow left to right Channels routed to reflect dataflow edges Too many gate locations, collapse dataflow ¨ Using scheduler feedback, identify latency critical edges ¨ Merge critical node pairs ¨ Reroute channels q 0 q 1 q 0 q 2 q 3 q 2 q 1 q 3

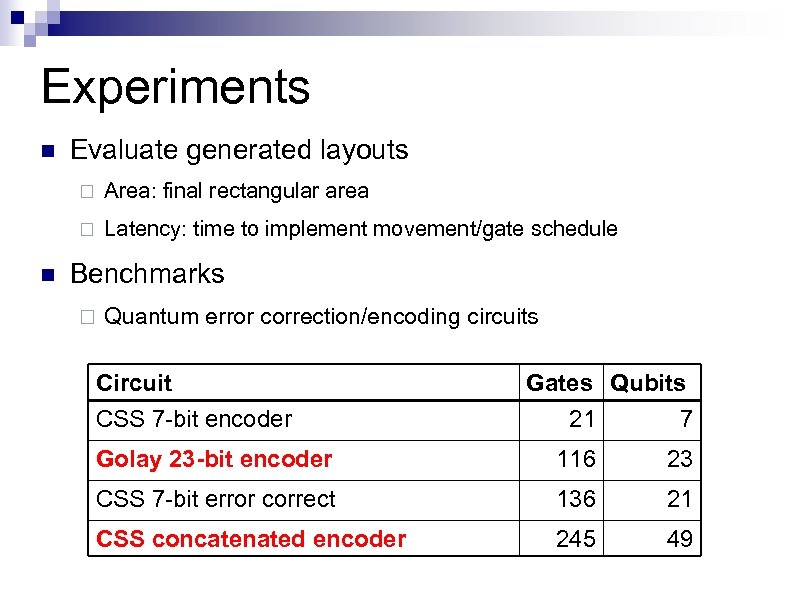

Experiments n Evaluate generated layouts ¨ ¨ n Area: final rectangular area Latency: time to implement movement/gate schedule Benchmarks ¨ Quantum error correction/encoding circuits Circuit CSS 7 -bit encoder Gates Qubits 21 7 Golay 23 -bit encoder 116 23 CSS 7 -bit error correct 136 21 CSS concatenated encoder 245 49

Experiments n Evaluate generated layouts ¨ ¨ n Area: final rectangular area Latency: time to implement movement/gate schedule Benchmarks ¨ Quantum error correction/encoding circuits Circuit CSS 7 -bit encoder Gates Qubits 21 7 Golay 23 -bit encoder 116 23 CSS 7 -bit error correct 136 21 CSS concatenated encoder 245 49

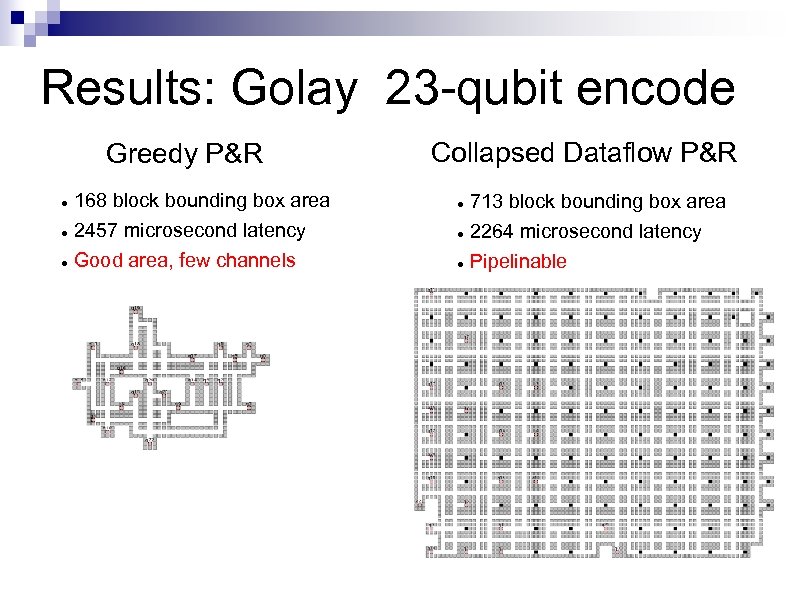

Results: Golay 23 -qubit encode Greedy P&R 168 block bounding box area 2457 microsecond latency Good area, few channels Collapsed Dataflow P&R 713 block bounding box area 2264 microsecond latency Pipelinable

Results: Golay 23 -qubit encode Greedy P&R 168 block bounding box area 2457 microsecond latency Good area, few channels Collapsed Dataflow P&R 713 block bounding box area 2264 microsecond latency Pipelinable

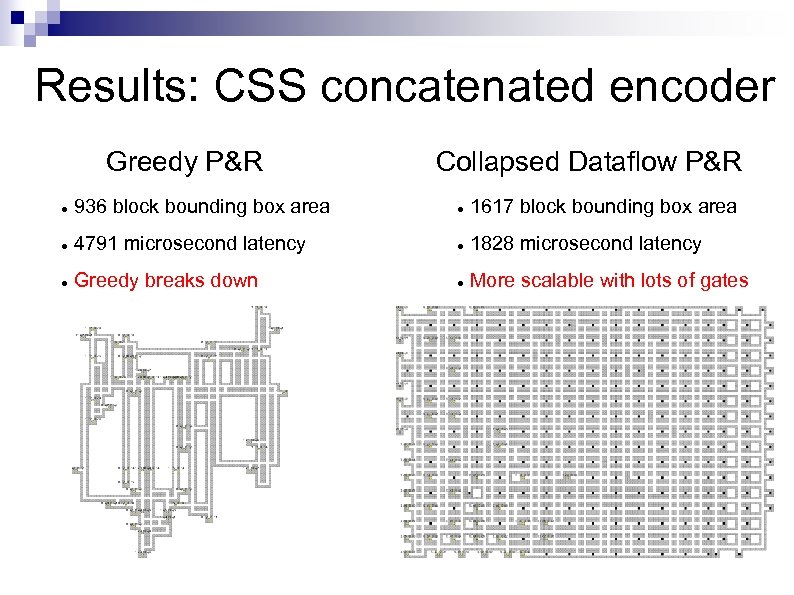

Results: CSS concatenated encoder Greedy P&R Collapsed Dataflow P&R 936 block bounding box area 1617 block bounding box area 4791 microsecond latency 1828 microsecond latency Greedy breaks down More scalable with lots of gates

Results: CSS concatenated encoder Greedy P&R Collapsed Dataflow P&R 936 block bounding box area 1617 block bounding box area 4791 microsecond latency 1828 microsecond latency Greedy breaks down More scalable with lots of gates

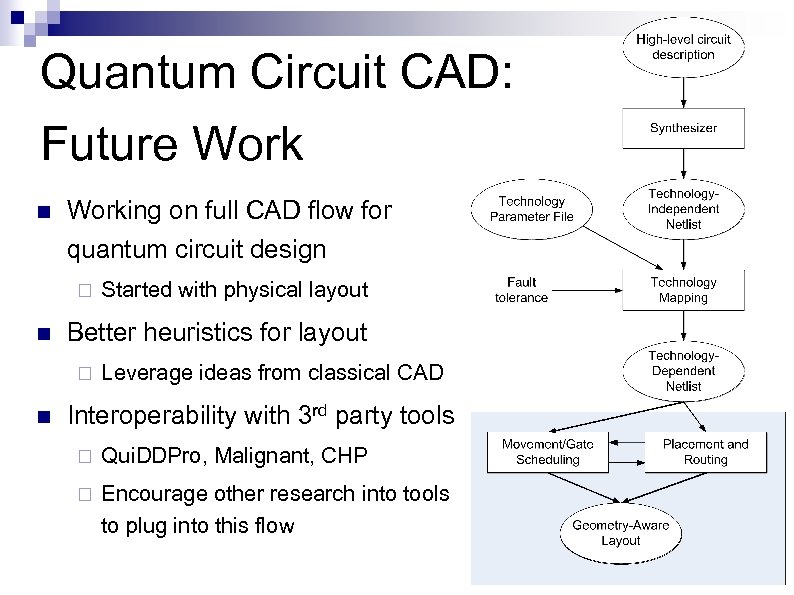

Quantum Circuit CAD: Future Work n Working on full CAD flow for quantum circuit design ¨ n Better heuristics for layout ¨ n Started with physical layout Leverage ideas from classical CAD Interoperability with 3 rd party tools ¨ Qui. DDPro, Malignant, CHP ¨ Encourage other research into tools to plug into this flow

Quantum Circuit CAD: Future Work n Working on full CAD flow for quantum circuit design ¨ n Better heuristics for layout ¨ n Started with physical layout Leverage ideas from classical CAD Interoperability with 3 rd party tools ¨ Qui. DDPro, Malignant, CHP ¨ Encourage other research into tools to plug into this flow

Conclusion n Scheduling heuristic for ion trap quantum circuits ¨ ¨ n Sequences gate and communication ops on arbitrary layout Synthesizes classical control HDL Iterative place and route heuristics ¨ ¨ n Simple greedy minimizes gate sites (lasers) Collapsed dataflow more scalable and potentially good throughput First steps toward larger CAD flow for quantum computing ¨ Provide tools for experimentalists as more qubits implemented ¨ Testbed for new circuit designs for fault tolerance, new algorithms

Conclusion n Scheduling heuristic for ion trap quantum circuits ¨ ¨ n Sequences gate and communication ops on arbitrary layout Synthesizes classical control HDL Iterative place and route heuristics ¨ ¨ n Simple greedy minimizes gate sites (lasers) Collapsed dataflow more scalable and potentially good throughput First steps toward larger CAD flow for quantum computing ¨ Provide tools for experimentalists as more qubits implemented ¨ Testbed for new circuit designs for fault tolerance, new algorithms

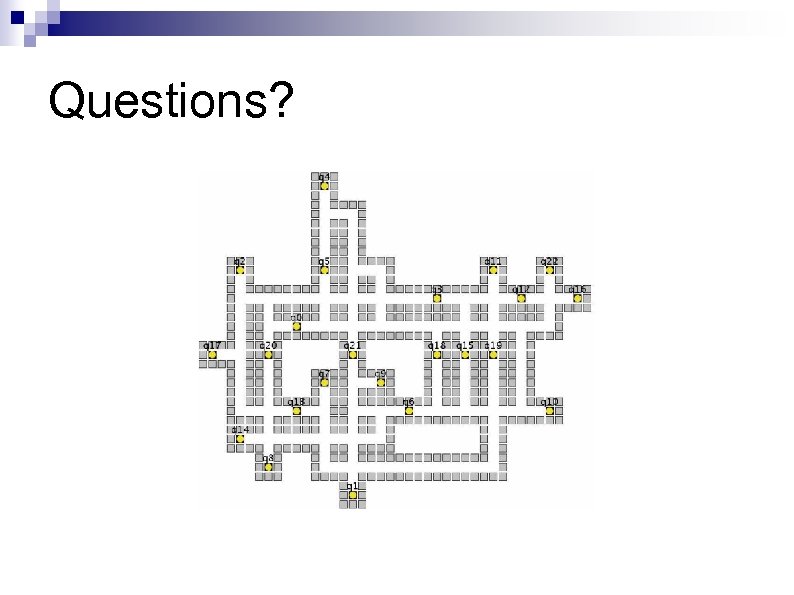

Questions?

Questions?

Future Work n Add hierarchical P&R for larger circuits n Fault tolerance layout evaluation metric n Automatic insertion of error correction circuits n Automatic selection of error correcting codes

Future Work n Add hierarchical P&R for larger circuits n Fault tolerance layout evaluation metric n Automatic insertion of error correction circuits n Automatic selection of error correcting codes

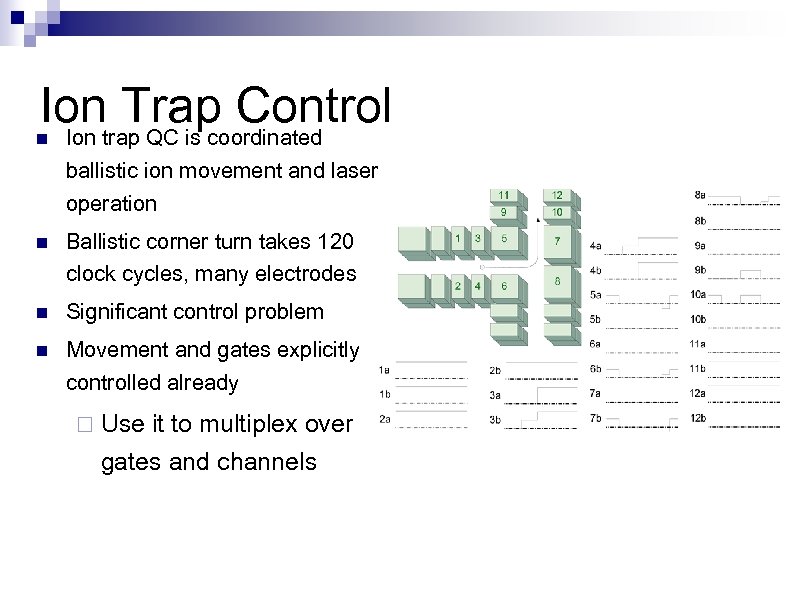

Iontrap QC is coordinated Trap Control Ion n ballistic ion movement and laser operation n Ballistic corner turn takes 120 clock cycles, many electrodes n Significant control problem n Movement and gates explicitly controlled already ¨ Use it to multiplex over gates and channels

Iontrap QC is coordinated Trap Control Ion n ballistic ion movement and laser operation n Ballistic corner turn takes 120 clock cycles, many electrodes n Significant control problem n Movement and gates explicitly controlled already ¨ Use it to multiplex over gates and channels

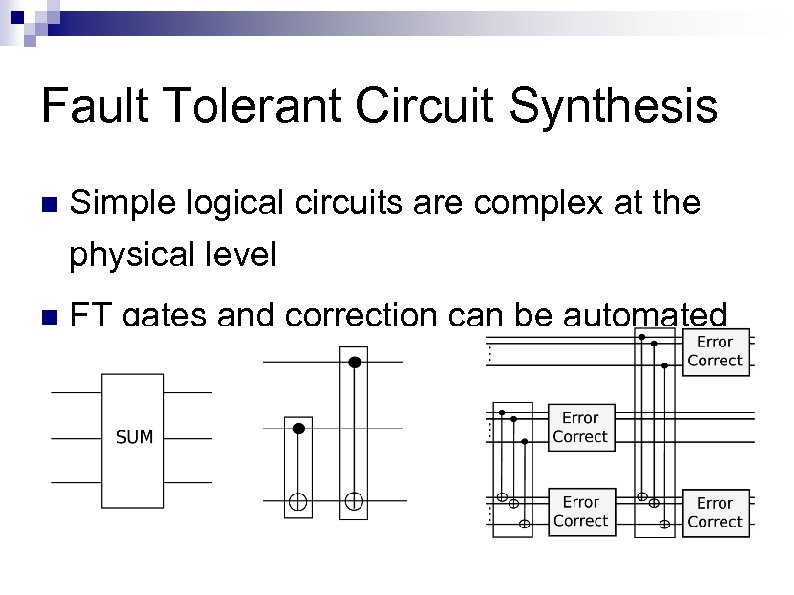

Fault Tolerant Circuit Synthesis n Simple logical circuits are complex at the physical level n FT gates and correction can be automated

Fault Tolerant Circuit Synthesis n Simple logical circuits are complex at the physical level n FT gates and correction can be automated

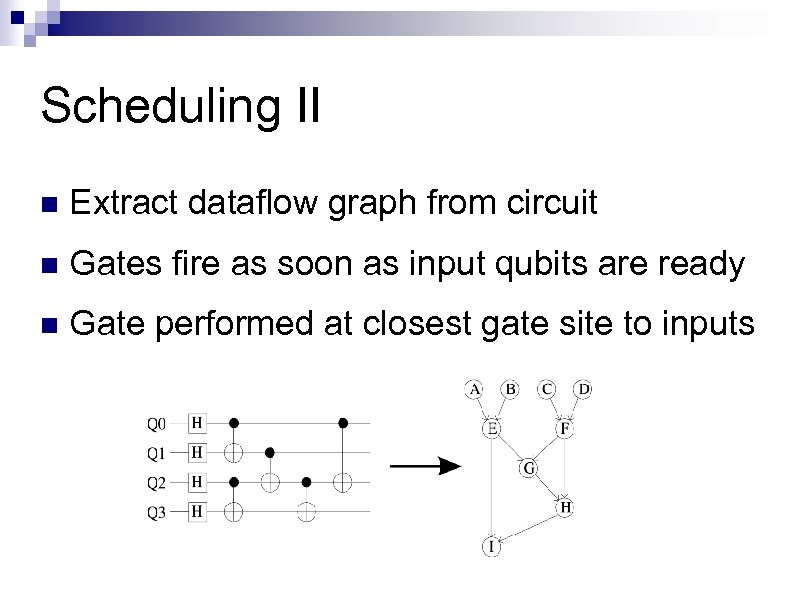

Scheduling II n Extract dataflow graph from circuit n Gates fire as soon as input qubits are ready n Gate performed at closest gate site to inputs

Scheduling II n Extract dataflow graph from circuit n Gates fire as soon as input qubits are ready n Gate performed at closest gate site to inputs

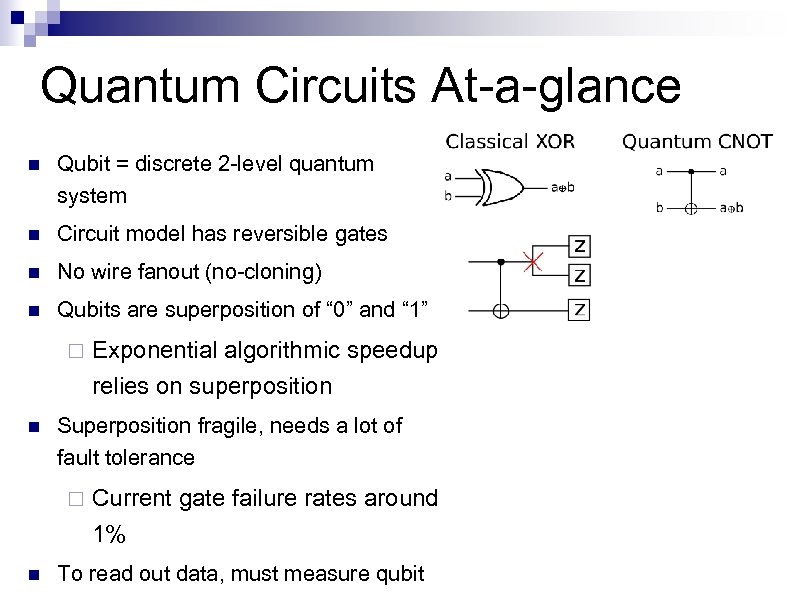

Quantum Circuits At-a-glance n Qubit = discrete 2 -level quantum system n Circuit model has reversible gates n No wire fanout (no-cloning) n Qubits are superposition of “ 0” and “ 1” ¨ n Superposition fragile, needs a lot of fault tolerance ¨ n Exponential algorithmic speedup relies on superposition Current gate failure rates around 1% To read out data, must measure qubit

Quantum Circuits At-a-glance n Qubit = discrete 2 -level quantum system n Circuit model has reversible gates n No wire fanout (no-cloning) n Qubits are superposition of “ 0” and “ 1” ¨ n Superposition fragile, needs a lot of fault tolerance ¨ n Exponential algorithmic speedup relies on superposition Current gate failure rates around 1% To read out data, must measure qubit

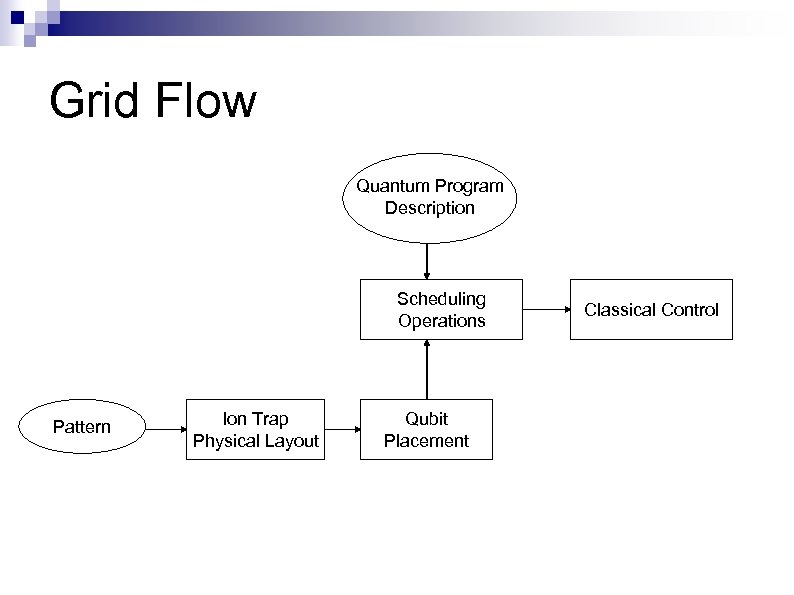

Grid Flow Quantum Program Description Scheduling Operations Pattern Ion Trap Physical Layout Qubit Placement Classical Control

Grid Flow Quantum Program Description Scheduling Operations Pattern Ion Trap Physical Layout Qubit Placement Classical Control

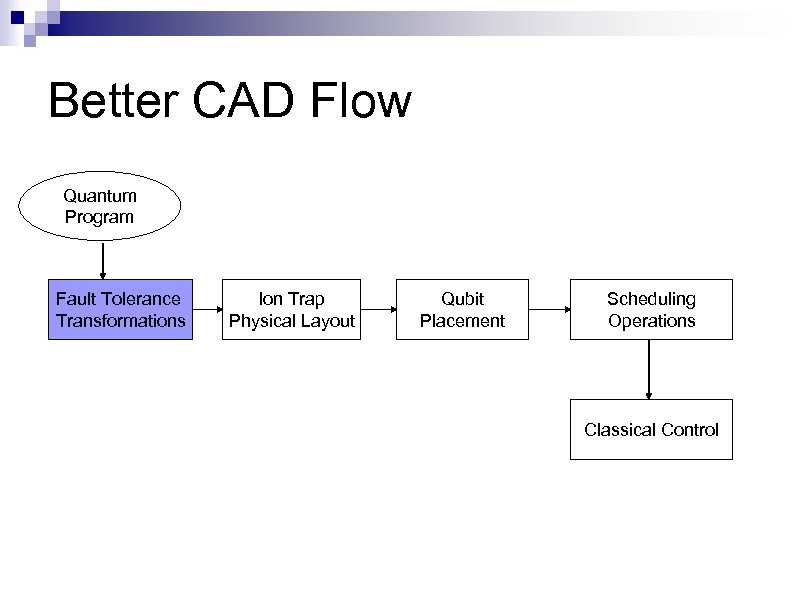

Better CAD Flow Quantum Program Fault Tolerance Transformations Ion Trap Physical Layout Qubit Placement Scheduling Operations Classical Control

Better CAD Flow Quantum Program Fault Tolerance Transformations Ion Trap Physical Layout Qubit Placement Scheduling Operations Classical Control

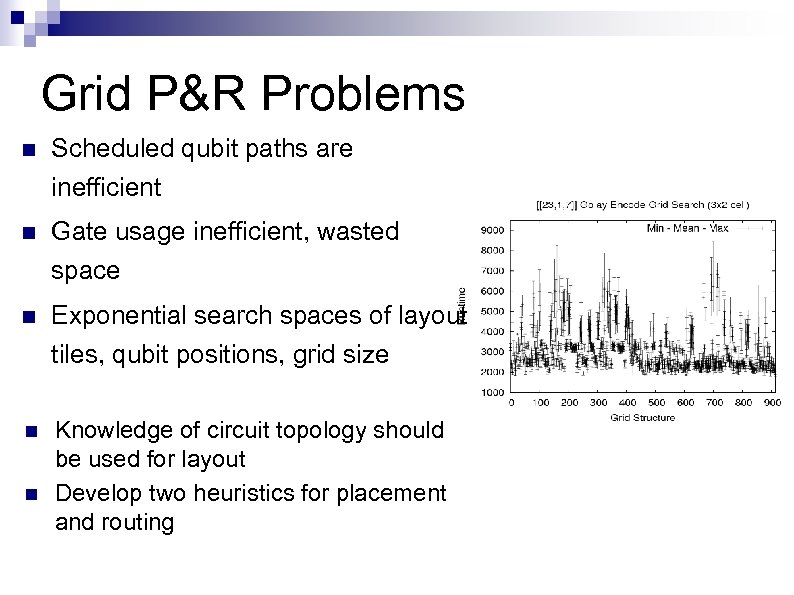

Grid P&R Problems n Scheduled qubit paths are inefficient n Gate usage inefficient, wasted space n Exponential search spaces of layout tiles, qubit positions, grid size n Knowledge of circuit topology should be used for layout Develop two heuristics for placement and routing n

Grid P&R Problems n Scheduled qubit paths are inefficient n Gate usage inefficient, wasted space n Exponential search spaces of layout tiles, qubit positions, grid size n Knowledge of circuit topology should be used for layout Develop two heuristics for placement and routing n

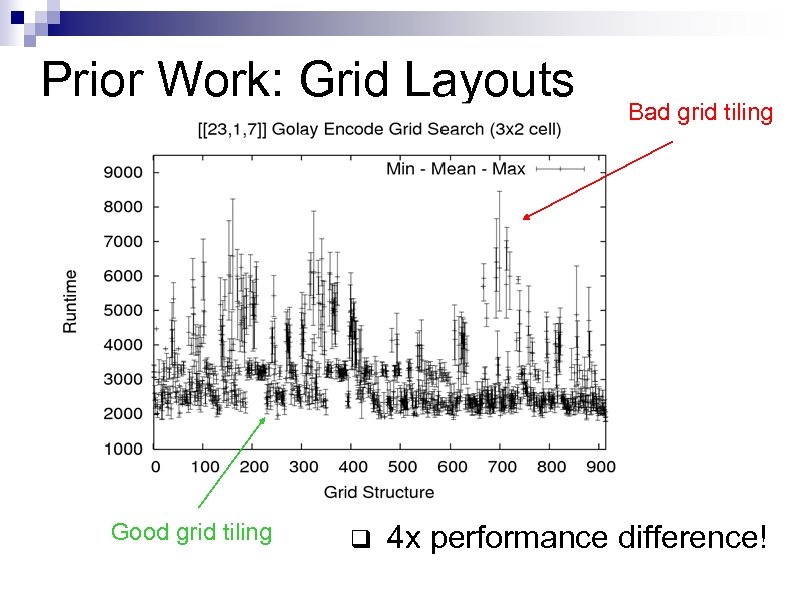

Prior Work: Grid Layouts Good grid tiling q Bad grid tiling 4 x performance difference!

Prior Work: Grid Layouts Good grid tiling q Bad grid tiling 4 x performance difference!

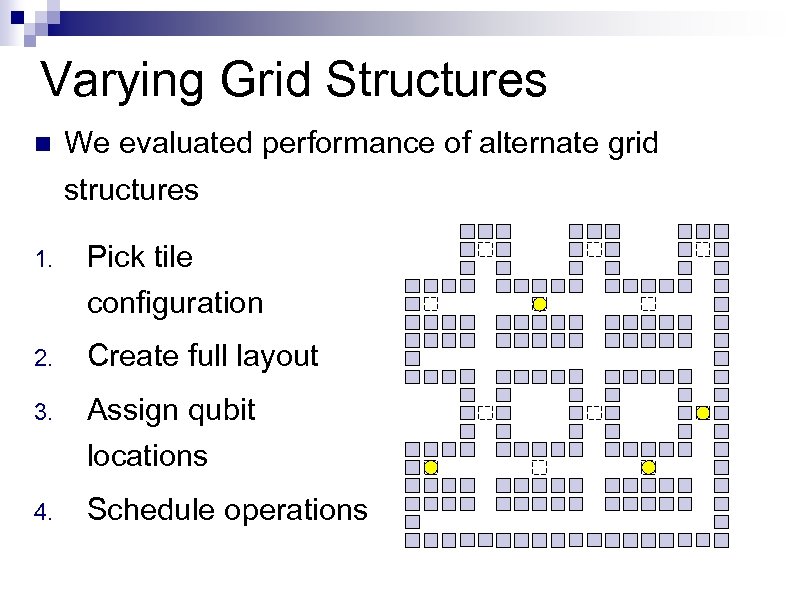

Varying Grid Structures n We evaluated performance of alternate grid structures 1. Pick tile configuration 2. Create full layout 3. Assign qubit locations 4. Schedule operations

Varying Grid Structures n We evaluated performance of alternate grid structures 1. Pick tile configuration 2. Create full layout 3. Assign qubit locations 4. Schedule operations

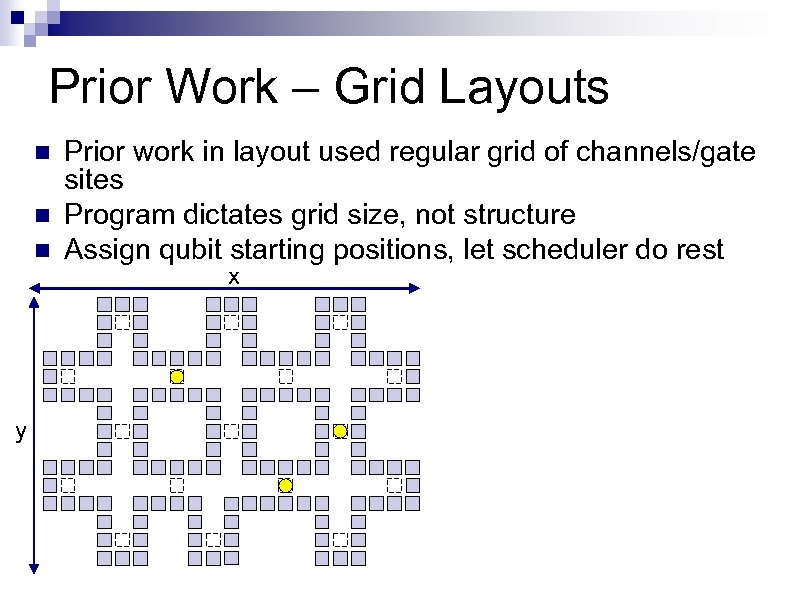

Prior Work – Grid Layouts n n n y Prior work in layout used regular grid of channels/gate sites Program dictates grid size, not structure Assign qubit starting positions, let scheduler do rest x

Prior Work – Grid Layouts n n n y Prior work in layout used regular grid of channels/gate sites Program dictates grid size, not structure Assign qubit starting positions, let scheduler do rest x

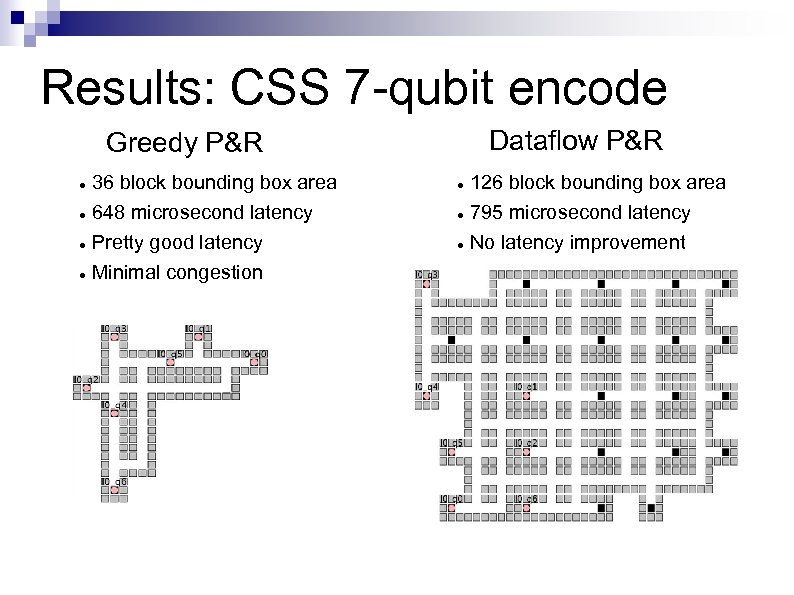

Results: CSS 7 -qubit encode Dataflow P&R Greedy P&R 36 block bounding box area 648 microsecond latency Pretty good latency Minimal congestion 126 block bounding box area 795 microsecond latency No latency improvement

Results: CSS 7 -qubit encode Dataflow P&R Greedy P&R 36 block bounding box area 648 microsecond latency Pretty good latency Minimal congestion 126 block bounding box area 795 microsecond latency No latency improvement

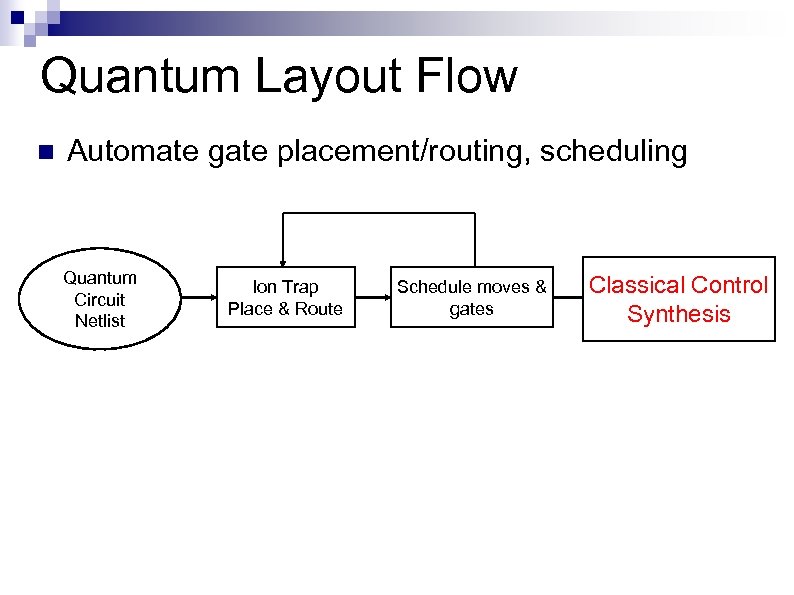

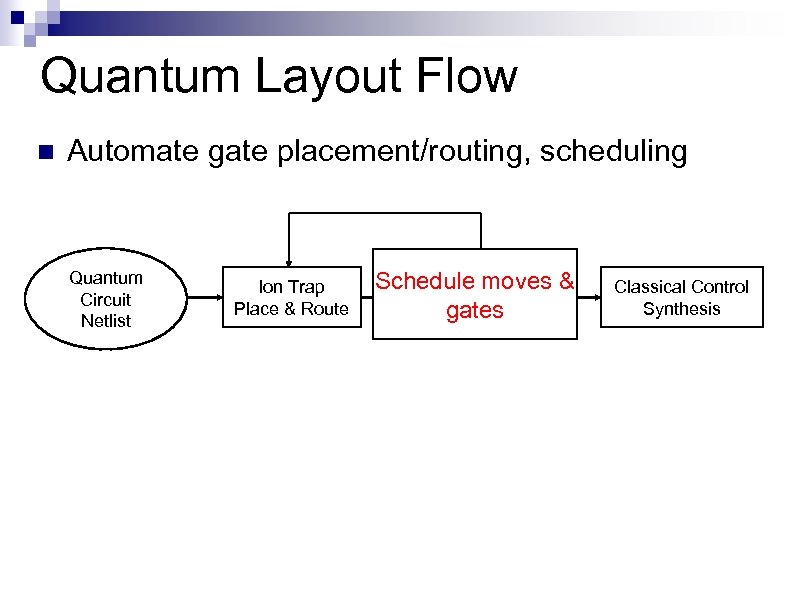

Quantum Layout Flow n Automate gate placement/routing, scheduling Quantum Circuit Netlist Ion Trap Place & Route Schedule moves & gates Classical. Control Classical Control Synthesis

Quantum Layout Flow n Automate gate placement/routing, scheduling Quantum Circuit Netlist Ion Trap Place & Route Schedule moves & gates Classical. Control Classical Control Synthesis

Quantum Layout Flow n Automate gate placement/routing, scheduling Quantum Circuit Netlist Ion Trap Place & Route Schedule moves & gates Classical Control Synthesis

Quantum Layout Flow n Automate gate placement/routing, scheduling Quantum Circuit Netlist Ion Trap Place & Route Schedule moves & gates Classical Control Synthesis

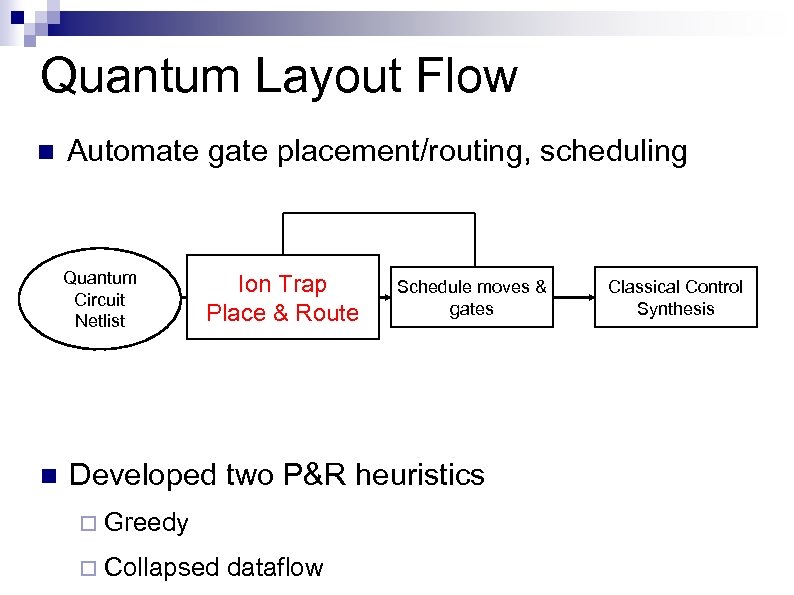

Quantum Layout Flow n Automate gate placement/routing, scheduling Quantum Circuit Netlist n Ion Trap Place & Route Schedule moves & gates Developed two P&R heuristics ¨ Greedy ¨ Collapsed dataflow Classical Control Synthesis

Quantum Layout Flow n Automate gate placement/routing, scheduling Quantum Circuit Netlist n Ion Trap Place & Route Schedule moves & gates Developed two P&R heuristics ¨ Greedy ¨ Collapsed dataflow Classical Control Synthesis

q 0 q 1 q 2 q 3

q 0 q 1 q 2 q 3

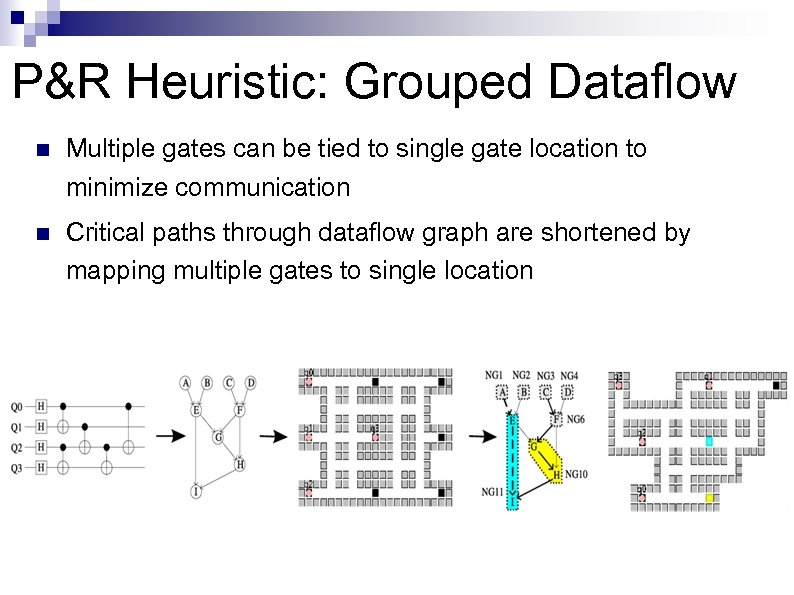

P&R Heuristic: Grouped Dataflow n Multiple gates can be tied to single gate location to minimize communication n Critical paths through dataflow graph are shortened by mapping multiple gates to single location

P&R Heuristic: Grouped Dataflow n Multiple gates can be tied to single gate location to minimize communication n Critical paths through dataflow graph are shortened by mapping multiple gates to single location