e8cf13e0dd5de8165b515bfa71d3f3d3.ppt

- Количество слайдов: 11

Automated Gateware Discovery Using Open Firmware A presentation on my research, and aims to lay foundation for automating gateware detection. Presented By: Shanly Rajan Embedded Systems Engineer (SA SKA) MSc Student (UCT) Supervisors: Prof Mike Inggs; Dr Marc Welz SKA BURSARY CONFERENCE : 04 DECEMBER 2009

Automated Gateware Discovery Using Open Firmware A presentation on my research, and aims to lay foundation for automating gateware detection. Presented By: Shanly Rajan Embedded Systems Engineer (SA SKA) MSc Student (UCT) Supervisors: Prof Mike Inggs; Dr Marc Welz SKA BURSARY CONFERENCE : 04 DECEMBER 2009

Overview Gateware : Introduction Software-FPGA Interaction BORPH : An overview BORPH Trade-offs Open Firmware U-boot Open Firmware Research Status & Future Directions Conclusion

Overview Gateware : Introduction Software-FPGA Interaction BORPH : An overview BORPH Trade-offs Open Firmware U-boot Open Firmware Research Status & Future Directions Conclusion

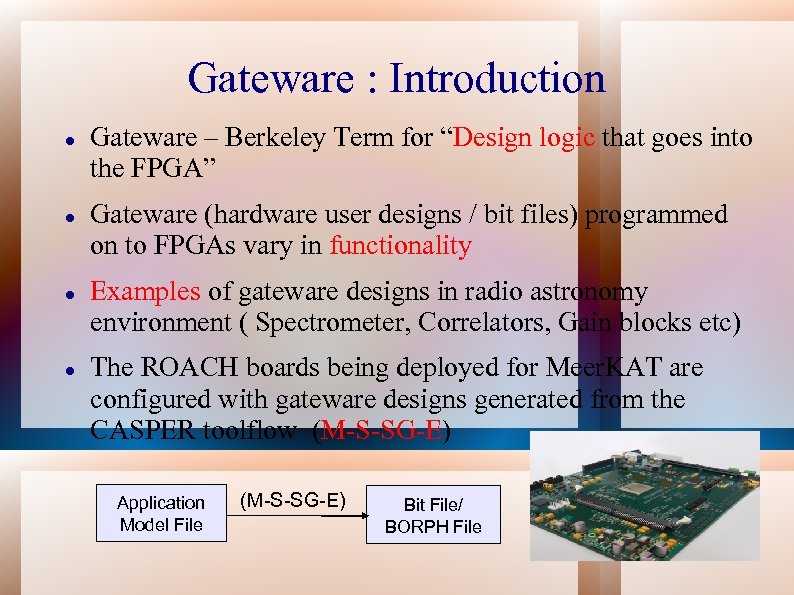

Gateware : Introduction Gateware – Berkeley Term for “Design logic that goes into the FPGA” Gateware (hardware user designs / bit files) programmed on to FPGAs vary in functionality Examples of gateware designs in radio astronomy environment ( Spectrometer, Correlators, Gain blocks etc) The ROACH boards being deployed for Meer. KAT are configured with gateware designs generated from the CASPER toolflow (M-S-SG-E) Application Model File (M-S-SG-E) Bit File/ BORPH File

Gateware : Introduction Gateware – Berkeley Term for “Design logic that goes into the FPGA” Gateware (hardware user designs / bit files) programmed on to FPGAs vary in functionality Examples of gateware designs in radio astronomy environment ( Spectrometer, Correlators, Gain blocks etc) The ROACH boards being deployed for Meer. KAT are configured with gateware designs generated from the CASPER toolflow (M-S-SG-E) Application Model File (M-S-SG-E) Bit File/ BORPH File

Software-FPGA Interaction Generally gateware implementations on the FPGA requires software support to provide the user an interface to communicate with the gateware logic. Writing software each time to interact with a piece of gateware is a time-consuming and difficult task. Conventional method of software - hardware (FPGA) interaction would be writing device drivers to operate on a piece of hardware. Existing software - FPGA approach: BORPH (Berkeley Operating System for Re Programmable Hardware).

Software-FPGA Interaction Generally gateware implementations on the FPGA requires software support to provide the user an interface to communicate with the gateware logic. Writing software each time to interact with a piece of gateware is a time-consuming and difficult task. Conventional method of software - hardware (FPGA) interaction would be writing device drivers to operate on a piece of hardware. Existing software - FPGA approach: BORPH (Berkeley Operating System for Re Programmable Hardware).

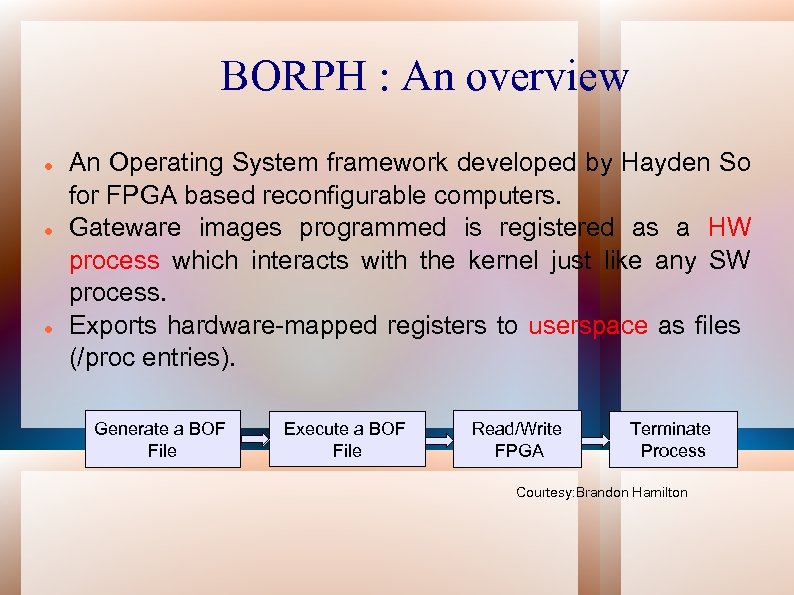

BORPH : An overview An Operating System framework developed by Hayden So for FPGA based reconfigurable computers. Gateware images programmed is registered as a HW process which interacts with the kernel just like any SW process. Exports hardware-mapped registers to userspace as files (/proc entries). Generate a BOF File Execute a BOF File Read/Write FPGA Terminate Process Courtesy: Brandon Hamilton

BORPH : An overview An Operating System framework developed by Hayden So for FPGA based reconfigurable computers. Gateware images programmed is registered as a HW process which interacts with the kernel just like any SW process. Exports hardware-mapped registers to userspace as files (/proc entries). Generate a BOF File Execute a BOF File Read/Write FPGA Terminate Process Courtesy: Brandon Hamilton

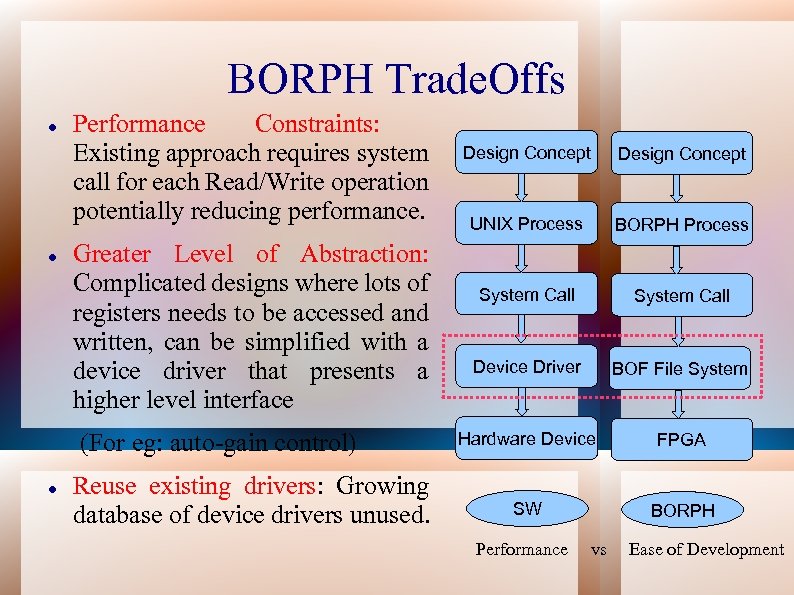

BORPH Trade. Offs Performance Constraints: Existing approach requires system call for each Read/Write operation potentially reducing performance. Greater Level of Abstraction: Complicated designs where lots of registers needs to be accessed and written, can be simplified with a device driver that presents a higher level interface (For eg: auto-gain control) Reuse existing drivers: Growing database of device drivers unused. Design Concept UNIX Process BORPH Process System Call Device Driver BOF File System Hardware Device FPGA SW BORPH Performance vs Ease of Development

BORPH Trade. Offs Performance Constraints: Existing approach requires system call for each Read/Write operation potentially reducing performance. Greater Level of Abstraction: Complicated designs where lots of registers needs to be accessed and written, can be simplified with a device driver that presents a higher level interface (For eg: auto-gain control) Reuse existing drivers: Growing database of device drivers unused. Design Concept UNIX Process BORPH Process System Call Device Driver BOF File System Hardware Device FPGA SW BORPH Performance vs Ease of Development

Open Firmware : Hardware Independent Boot Code Boot Time Drivers for testing machine hardware Building Device Trees which OS later uses Device Tree : The set of devices attached to the system, including permanently installed devices and plug-in devices, is described by an Open Firmware Data Structure known as the device tree.

Open Firmware : Hardware Independent Boot Code Boot Time Drivers for testing machine hardware Building Device Trees which OS later uses Device Tree : The set of devices attached to the system, including permanently installed devices and plug-in devices, is described by an Open Firmware Data Structure known as the device tree.

U-boot Open Firmware U-boot, the bootloader for the powerpc architecture in ROACH has built-in OF support The device-tree layout for u-boot is strongly inherited from the definition of the Open Firmware IEEE 1275 -1994 device-tree The observation that gateware implementations on FPGA can be treated as pluggable peripherals suggests that it can be represented in the device tree just like any other physical peripheral Conventional/Traditional Method : Scheme of loading existing device drivers to operate on physical peripherals can also be extended to gateware images as well. The research facilitates the process of identifying and operating on gateware images by extending the existing infrastructure of probing devices in traditional software by using Open Firmware.

U-boot Open Firmware U-boot, the bootloader for the powerpc architecture in ROACH has built-in OF support The device-tree layout for u-boot is strongly inherited from the definition of the Open Firmware IEEE 1275 -1994 device-tree The observation that gateware implementations on FPGA can be treated as pluggable peripherals suggests that it can be represented in the device tree just like any other physical peripheral Conventional/Traditional Method : Scheme of loading existing device drivers to operate on physical peripherals can also be extended to gateware images as well. The research facilitates the process of identifying and operating on gateware images by extending the existing infrastructure of probing devices in traditional software by using Open Firmware.

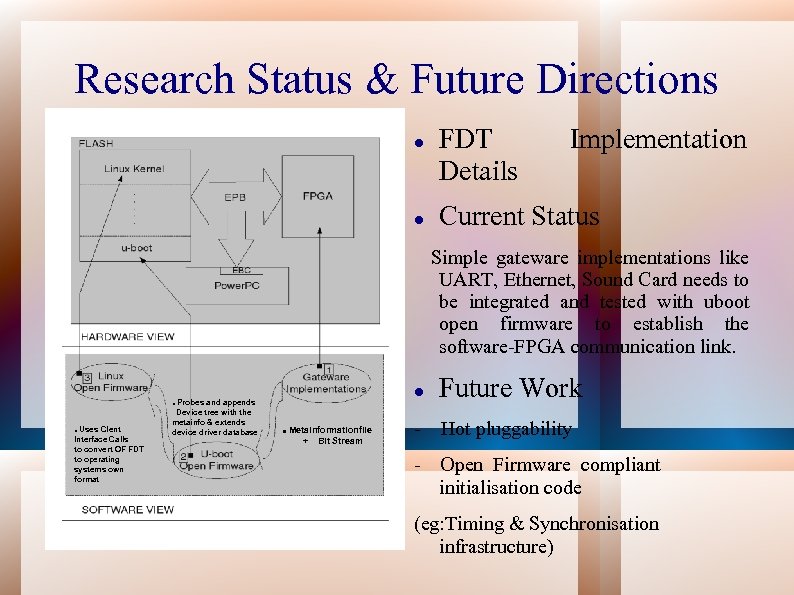

Research Status & Future Directions FDT Details Implementation Current Status Simple gateware implementations like UART, Ethernet, Sound Card needs to be integrated and tested with uboot open firmware to establish the software-FPGA communication link. Probes and appends Device tree with the metainfo & extends device driver database Uses Clent Interface Calls to convert OF FDT to operating systems own format Metainformationfile + Bit Stream Future Work - Hot pluggability - Open Firmware compliant initialisation code (eg: Timing & Synchronisation infrastructure)

Research Status & Future Directions FDT Details Implementation Current Status Simple gateware implementations like UART, Ethernet, Sound Card needs to be integrated and tested with uboot open firmware to establish the software-FPGA communication link. Probes and appends Device tree with the metainfo & extends device driver database Uses Clent Interface Calls to convert OF FDT to operating systems own format Metainformationfile + Bit Stream Future Work - Hot pluggability - Open Firmware compliant initialisation code (eg: Timing & Synchronisation infrastructure)

Conclusion Gateware : Introduction Software-FPGA Interaction BORPH : An overview BORPH Trade-offs Open Firmware U-boot Open Firmware Research Status & Future Directions Existing Software – FPGA Approach (Use BORPH) Alternate Approach Considered (EXTENDING DEVICE TREES)

Conclusion Gateware : Introduction Software-FPGA Interaction BORPH : An overview BORPH Trade-offs Open Firmware U-boot Open Firmware Research Status & Future Directions Existing Software – FPGA Approach (Use BORPH) Alternate Approach Considered (EXTENDING DEVICE TREES)

Questions q

Questions q