cbf12bf8d5af0c2f8a2548d933f0702b.ppt

- Количество слайдов: 12

ASIC R&D at Fermilab R. Yarema October 30, 2003 Long Range Planning Committee

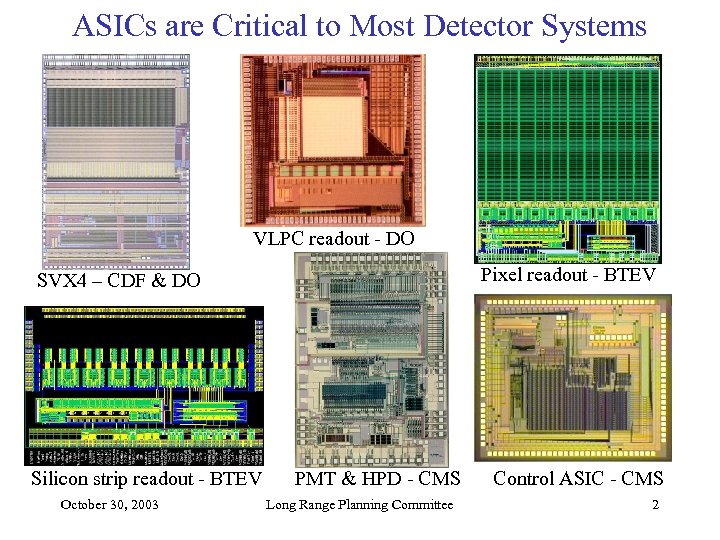

ASICs are Critical to Most Detector Systems VLPC readout - DO Pixel readout - BTEV SVX 4 – CDF & DO Silicon strip readout - BTEV October 30, 2003 PMT & HPD - CMS Long Range Planning Committee Control ASIC - CMS 2

Detector and ASIC Development • Detector R&D often begins first without a clear idea of how to read out the detector. – “What kind of chip do you have that might be used to readout signals from a ……. detector? ? ” • ASIC R&D usually begins later – Virtually every progress review involving a chip says that not enough time is allotted for ASIC development • • Chip demands keep increasing Specifications keep changing Processes keep changing Development starts too late – An ASIC is frequently on the critical path • Detector and ASIC development need to proceed in parallel. October 30, 2003 Long Range Planning Committee 3

New ASIC efforts at Fermilab • Charge Digitizer (QIE) for BTEV PMTs – For PMT readout (negative current input) – Desire 0. 15% resolution, dynamic range of 65, 000: 1 – Auto ranging current splitter with precision integrators and embedded ADC – Device planned to have 8 binary weighted ranges and an 8 bit FADC – 132 ns clock – Pipelined operation with latency of 3 or 4 clock cycles – Controlled impedance input for cable termination (50 ohms) – Design in early stages – Submission targeted for early ’ 04 in AMS 0. 8 u Bi. CMOS October 30, 2003 Long Range Planning Committee 4

• TDC for BTEV – – – Multi-channel TDC, 8 or 16 channels 1 nsec resolution Data scarification (read only hit channels) 132 nsec beam crossing Include various miscellaneous functions Radiation tolerant design (TID, SEU) in 0. 25 µ • Resonant Mode Converter Chip (RMCC) – Useful for LC detector R&D, BTEV, Off-axis neutrinos, etc – Integrated Cockcroft-Walton based voltage control chip with internal reference, DAC, ADC and op amps. – Serial programming interface with 12 bit DAC. – 12 bit ADC for voltage and temperature read back. – Polarity programmable with pin selection. – 10 -20 µa @ 1000 V – Up to 5 KV possible, higher with special drive circuit – Low ripple – Provides relatively inexpensive single channel voltage control and read back for high voltage applications. October 30, 2003 Long Range Planning Committee 5

Future ASIC R&D Projects • Very Deep Submicron CMOS technology (0. 13 to 0. 09 µm) – In the last 12 years, designs have moved from 3. 0 µ to 0. 25 µ feature sizes. (SVX => SVX 2 => SVX 3 => SVX 4) – Move to smaller feature sizes will inevitably occur. • Processes will become obsolete • Need for higher resolution detectors – Move offers challenges • Lower voltage range, less analog voltage range • Different approach to radiation hardness, new libraries • Cost management, masks are extremely expensive ($500 K/set) • International collaborations for qualifying processes – Move requires substantial effort and time- start soon. October 30, 2003 Long Range Planning Committee 6

• APD Readout Chip (readout chip for small signals) – Multiple channel (64? ) readout device for applications like Neutrino Off-Axis Detector and LC Calorimeter R&D. – Must operate with low input signals (2000 e). – Have performed test with in-house designed chip (MASDA) for amorphous silicon detectors, which shows low noise operation is possible. – APDs are cooled to – 40°C to reduce dark current. – New design to be optimized for APDs with minimum S/N=10. October 30, 2003 Long Range Planning Committee 7

• Readout Chip for RPCs and GEMs – Possible application in Linear Collider and Neutrino Off-Axis Detector. – Single chip with different front end amplifiers for different detectors. – Multi-channel device (8 -32 channels, size mostly related to RPC layout). – One bit ADC – Timestamp each hit. – Store hits in local buffers, read out periodically. – Non-triggered system • Read out timestamps and channel ID into trigger processor • Use timestamps to construct hits • Works well for low event rates and low noise rates October 30, 2003 Long Range Planning Committee 8

• Multi-channel Mini-strip Readout ASIC – Designed for silicon strip upgrades requiring higher luminosity such as SLHC and Phenix (work for others). • Design for Cin = 0. 2 – 1 pf (50 x 2000 -10000 um cells) • High channel count, e. g. 512 ch/chip • Relaxed bump bonding pitch – Challenges • Chip power distribution • Back side current connection for lower noise • Cooling – Borrow from experience on SVX 4 and FPIX 2 October 30, 2003 Long Range Planning Committee 9

• CCD and Monolithic Active Pixel Sensors (MAPS) – Alternate technologies for future detectors – ASIC for CCD projects like the Linear Collider • • • 20 x 20 um cells Radiation concerns (~10 Krads) 25 -50 Mhz readout on 8 -30 readout amplifiers/CCD Internal 8 bit FADC Cluster processing – MAPS hold great potential for HEP and space • Combined detector and readout chip with ADCs • Very small pixel cells (3 um x 3 um) • Low mass (thin to 50 um) – MASDA • Amorphous silicon detector with integrated transistors for medical imaging – low noise, high resolution, slow readout. October 30, 2003 Long Range Planning Committee 10

ASIC Design Group • Particle Physics Division – Electrical Engineering Department -70 • Board level and other hardware design • ASIC Design – ASIC designers - 5 » Full custom analog » Full custom mixed signal – Testing – group of 5 » Wafer and robotic testing of packaged parts » Radiation studies October 30, 2003 Long Range Planning Committee 11

Summary • ASICs have been and will continue to be critical to new detector development. • ASIC development is costly in terms of tools and chip fabrication. • ASIC R&D is needed to keep pace with new process features and design challenges. • ASIC R&D needs to be adequately funded and proceed along with detector development October 30, 2003 Long Range Planning Committee 12

cbf12bf8d5af0c2f8a2548d933f0702b.ppt