391589fd6ce96b606b51a0b59e15696e.ppt

- Количество слайдов: 15

ASIC, Customer-Owned Tooling, and Processor Design Style Myths That Lead EDA Astray Nancy Nettleton Manager, VLSI ASIC Device Engineering April 2000

ASIC, Customer-Owned Tooling, and Processor Design Style Myths That Lead EDA Astray Nancy Nettleton Manager, VLSI ASIC Device Engineering April 2000

Design Style Myths COT is a design style that achieves higher performance through greater ownership of physical design. ASICs are slower than processors because of design margin. Design automation tactics tuned on processors are effective on ASICs if they are more heavily automated.

Design Style Myths COT is a design style that achieves higher performance through greater ownership of physical design. ASICs are slower than processors because of design margin. Design automation tactics tuned on processors are effective on ASICs if they are more heavily automated.

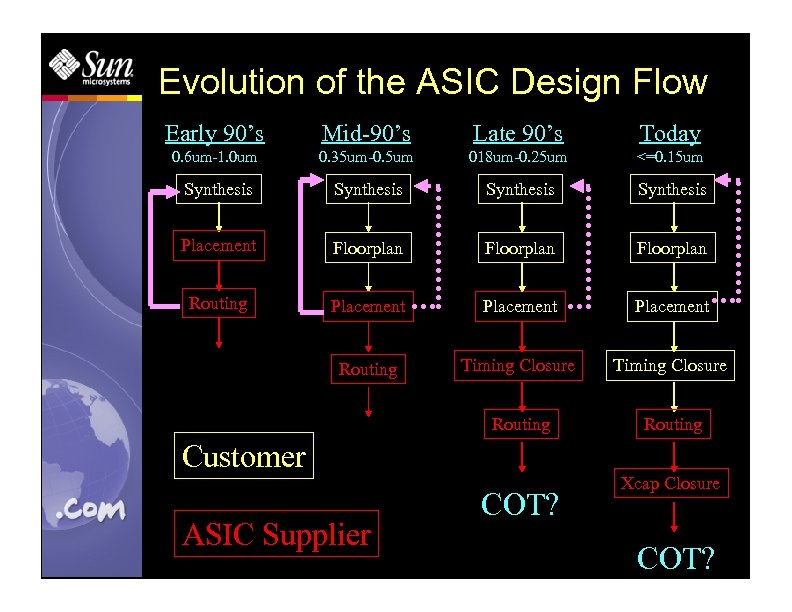

Evolution of the ASIC Design Flow Early 90’s Mid-90’s Late 90’s Today 0. 6 um-1. 0 um 0. 35 um-0. 5 um 018 um-0. 25 um <=0. 15 um Synthesis Placement Floorplan Routing Placement Routing Timing Closure Routing Customer ASIC Supplier COT? Xcap Closure COT?

Evolution of the ASIC Design Flow Early 90’s Mid-90’s Late 90’s Today 0. 6 um-1. 0 um 0. 35 um-0. 5 um 018 um-0. 25 um <=0. 15 um Synthesis Placement Floorplan Routing Placement Routing Timing Closure Routing Customer ASIC Supplier COT? Xcap Closure COT?

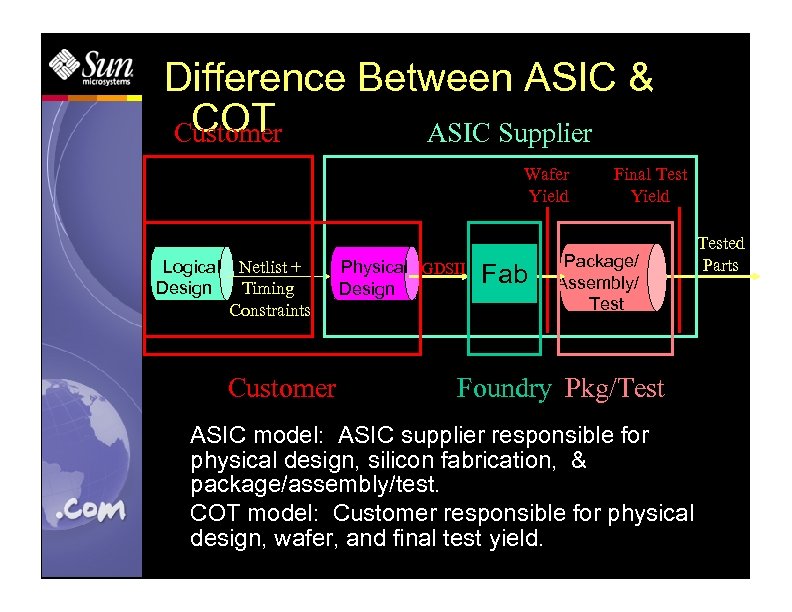

Difference Between ASIC & COT Customer ASIC Supplier Wafer Yield Logical Design Netlist + Timing Constraints Customer Physical GDSII Design Fab Final Test Yield Package/ Assembly/ Test Foundry Pkg/Test ASIC model: ASIC supplier responsible for physical design, silicon fabrication, & package/assembly/test. COT model: Customer responsible for physical design, wafer, and final test yield. Tested Parts

Difference Between ASIC & COT Customer ASIC Supplier Wafer Yield Logical Design Netlist + Timing Constraints Customer Physical GDSII Design Fab Final Test Yield Package/ Assembly/ Test Foundry Pkg/Test ASIC model: ASIC supplier responsible for physical design, silicon fabrication, & package/assembly/test. COT model: Customer responsible for physical design, wafer, and final test yield. Tested Parts

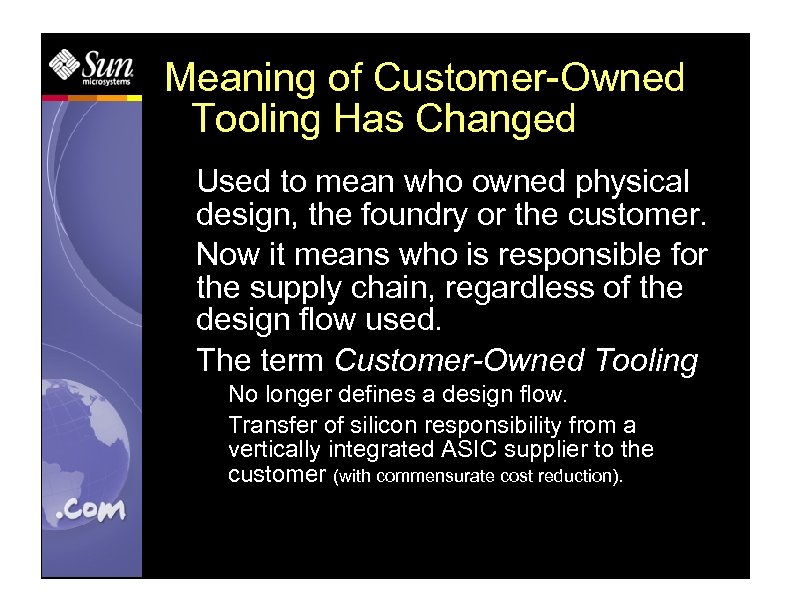

Meaning of Customer-Owned Tooling Has Changed Used to mean who owned physical design, the foundry or the customer. Now it means who is responsible for the supply chain, regardless of the design flow used. The term Customer-Owned Tooling No longer defines a design flow. Transfer of silicon responsibility from a vertically integrated ASIC supplier to the customer (with commensurate cost reduction).

Meaning of Customer-Owned Tooling Has Changed Used to mean who owned physical design, the foundry or the customer. Now it means who is responsible for the supply chain, regardless of the design flow used. The term Customer-Owned Tooling No longer defines a design flow. Transfer of silicon responsibility from a vertically integrated ASIC supplier to the customer (with commensurate cost reduction).

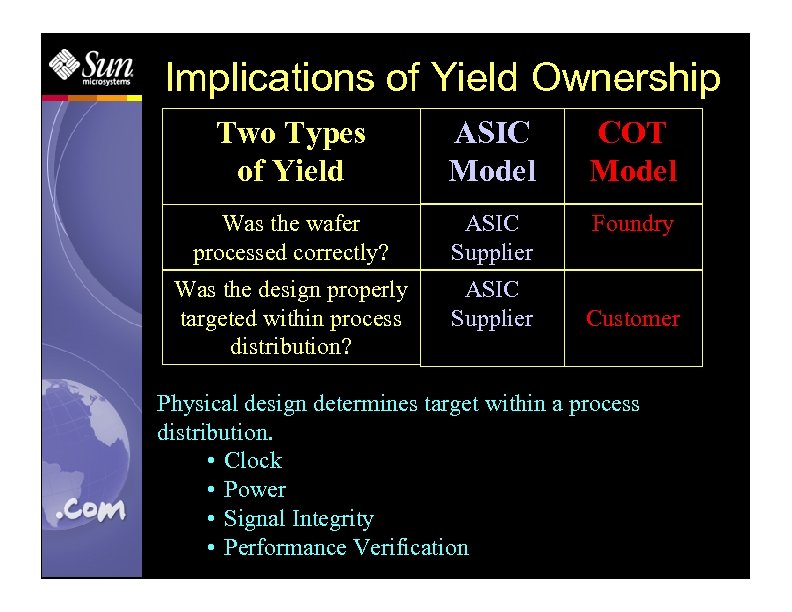

Implications of Yield Ownership Two Types of Yield ASIC Model COT Model Was the wafer processed correctly? ASIC Supplier Foundry Was the design properly targeted within process distribution? ASIC Supplier Customer Physical design determines target within a process distribution. • Clock • Power • Signal Integrity • Performance Verification

Implications of Yield Ownership Two Types of Yield ASIC Model COT Model Was the wafer processed correctly? ASIC Supplier Foundry Was the design properly targeted within process distribution? ASIC Supplier Customer Physical design determines target within a process distribution. • Clock • Power • Signal Integrity • Performance Verification

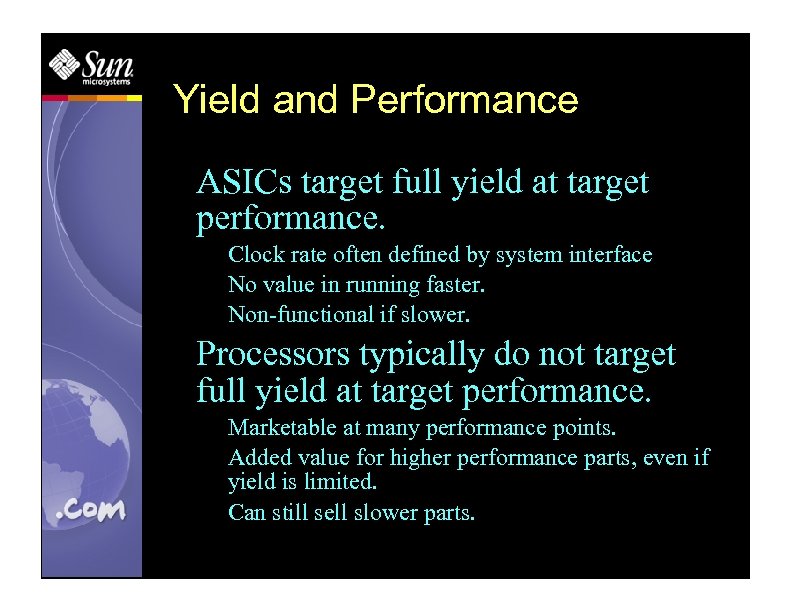

Yield and Performance ASICs target full yield at target performance. Clock rate often defined by system interface No value in running faster. Non-functional if slower. Processors typically do not target full yield at target performance. Marketable at many performance points. Added value for higher performance parts, even if yield is limited. Can still sell slower parts.

Yield and Performance ASICs target full yield at target performance. Clock rate often defined by system interface No value in running faster. Non-functional if slower. Processors typically do not target full yield at target performance. Marketable at many performance points. Added value for higher performance parts, even if yield is limited. Can still sell slower parts.

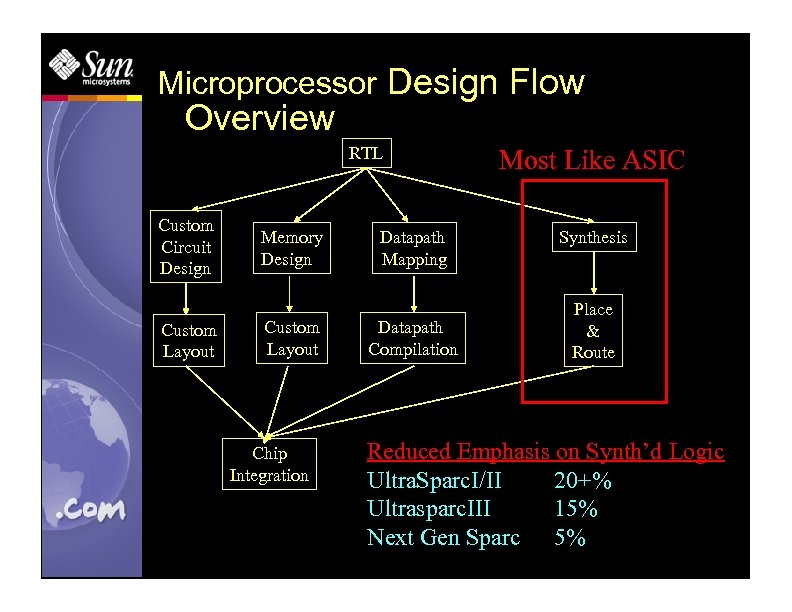

Microprocessor Design Flow Overview RTL Custom Circuit Design Custom Layout Memory Design Custom Layout Chip Integration Datapath Mapping Datapath Compilation Most Like ASIC Synthesis Place & Route Reduced Emphasis on Synth’d Logic Ultra. Sparc. I/II 20+% Ultrasparc. III 15% Next Gen Sparc 5%

Microprocessor Design Flow Overview RTL Custom Circuit Design Custom Layout Memory Design Custom Layout Chip Integration Datapath Mapping Datapath Compilation Most Like ASIC Synthesis Place & Route Reduced Emphasis on Synth’d Logic Ultra. Sparc. I/II 20+% Ultrasparc. III 15% Next Gen Sparc 5%

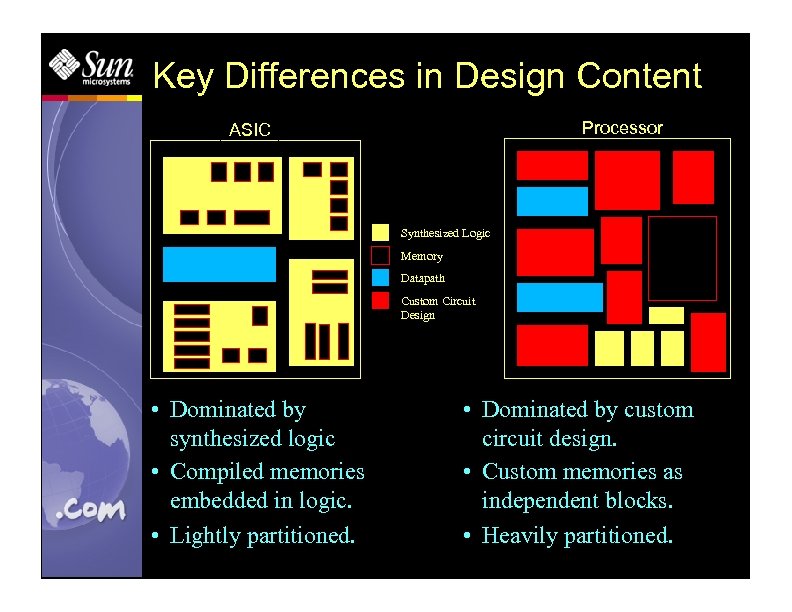

Key Differences in Design Content Processor ASIC Synthesized Logic Memory Datapath Custom Circuit Design • Dominated by synthesized logic • Compiled memories embedded in logic. • Lightly partitioned. • Dominated by custom circuit design. • Custom memories as independent blocks. • Heavily partitioned.

Key Differences in Design Content Processor ASIC Synthesized Logic Memory Datapath Custom Circuit Design • Dominated by synthesized logic • Compiled memories embedded in logic. • Lightly partitioned. • Dominated by custom circuit design. • Custom memories as independent blocks. • Heavily partitioned.

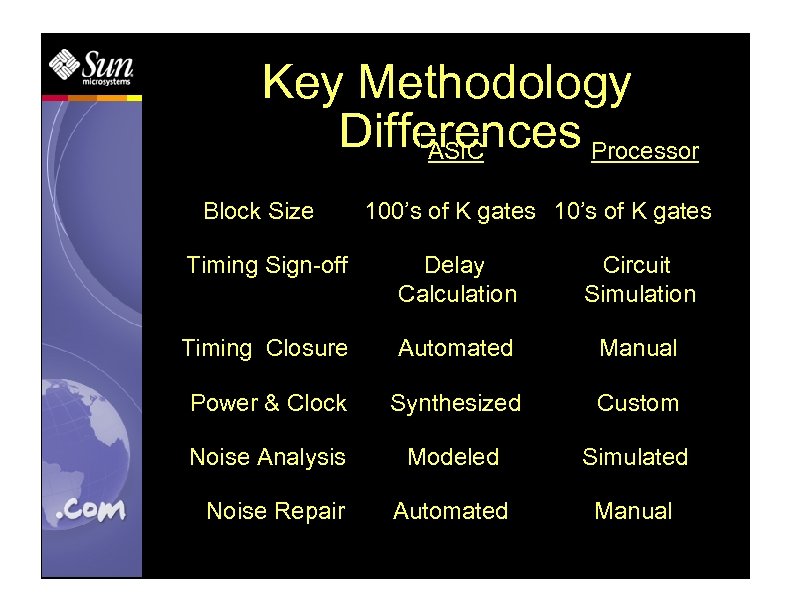

Key Methodology Differences Processor ASIC Block Size 100’s of K gates 10’s of K gates Timing Sign-off Delay Calculation Circuit Simulation Timing Closure Automated Manual Power & Clock Synthesized Custom Noise Analysis Modeled Simulated Automated Manual Noise Repair

Key Methodology Differences Processor ASIC Block Size 100’s of K gates 10’s of K gates Timing Sign-off Delay Calculation Circuit Simulation Timing Closure Automated Manual Power & Clock Synthesized Custom Noise Analysis Modeled Simulated Automated Manual Noise Repair

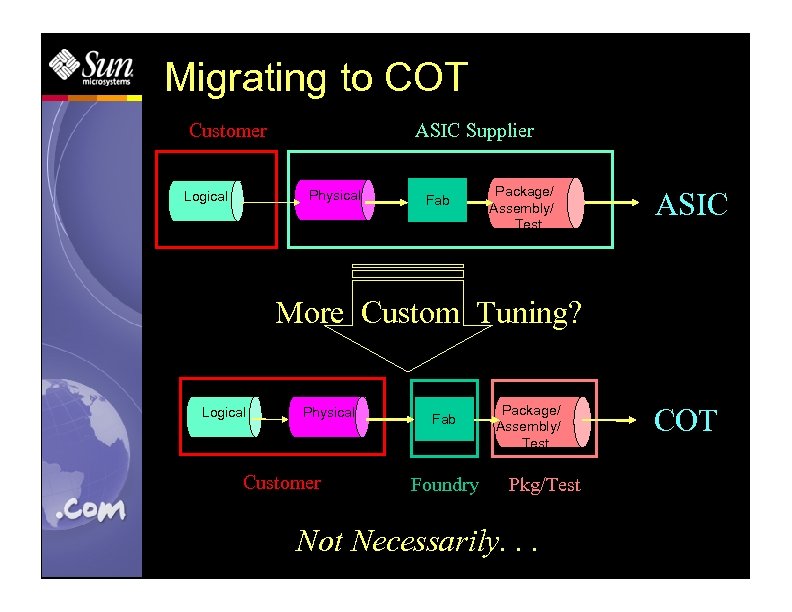

Migrating to COT Customer ASIC Supplier Physical Logical Fab Package/ Assembly/ Test ASIC More Custom Tuning? Logical Physical Customer Fab Foundry Package/ Assembly/ Test Pkg/Test Not Necessarily. . . COT

Migrating to COT Customer ASIC Supplier Physical Logical Fab Package/ Assembly/ Test ASIC More Custom Tuning? Logical Physical Customer Fab Foundry Package/ Assembly/ Test Pkg/Test Not Necessarily. . . COT

If Customer Owns Physical Design, Why Not Tune It? ASIC content is fundamentally different than processor content. Volatile system IP is partitioned onto ASICs Highly tuned system interfaces Definition evolves right up to system power-on. Rapid silicon implementation is often more important than detailed tuning. Even if customer owns physical design, the nature of the system IP may prohibit design tuning. Then why go COT? $ $ $ $ $

If Customer Owns Physical Design, Why Not Tune It? ASIC content is fundamentally different than processor content. Volatile system IP is partitioned onto ASICs Highly tuned system interfaces Definition evolves right up to system power-on. Rapid silicon implementation is often more important than detailed tuning. Even if customer owns physical design, the nature of the system IP may prohibit design tuning. Then why go COT? $ $ $ $ $

Different Design Objectives Processor More stable architecture (through partitioning) Achieve best possible timing limited on numberof well-understood critical paths. System chips Less stable architecture (because of system partitioning) Achieve acceptable timing large on number of unknown critical paths.

Different Design Objectives Processor More stable architecture (through partitioning) Achieve best possible timing limited on numberof well-understood critical paths. System chips Less stable architecture (because of system partitioning) Achieve acceptable timing large on number of unknown critical paths.

Implications Processors becoming increasingly unsuitable as proving grounds for prevalent silicon design techniques. Excellent vehicles for circuit design and performance-related problems. Not representative of system chips Small, homogeneous synthesized logic blocks Heavily partitioned and tuned Less automation.

Implications Processors becoming increasingly unsuitable as proving grounds for prevalent silicon design techniques. Excellent vehicles for circuit design and performance-related problems. Not representative of system chips Small, homogeneous synthesized logic blocks Heavily partitioned and tuned Less automation.

Conclusion Customer-Owned Tooling is a business model, not a design style. Ownership of physical design does not equate to higher performance. Performance of system chips is often defined by IP and schedule, not design techniques. Heavy partitioning and custom circuit design make processor design increasingly less representative of system chip automation.

Conclusion Customer-Owned Tooling is a business model, not a design style. Ownership of physical design does not equate to higher performance. Performance of system chips is often defined by IP and schedule, not design techniques. Heavy partitioning and custom circuit design make processor design increasingly less representative of system chip automation.