Архитектура системы команд CISC и RISC.ppt

- Количество слайдов: 19

Архитектуры с полным (CISC) и сокращенным (RISC) набором команд

uter omp Co CISC et C on S ructi Inst plete m

Примеры процессоров CISC Intel 80386 Cyrix М 6 486 DX-40

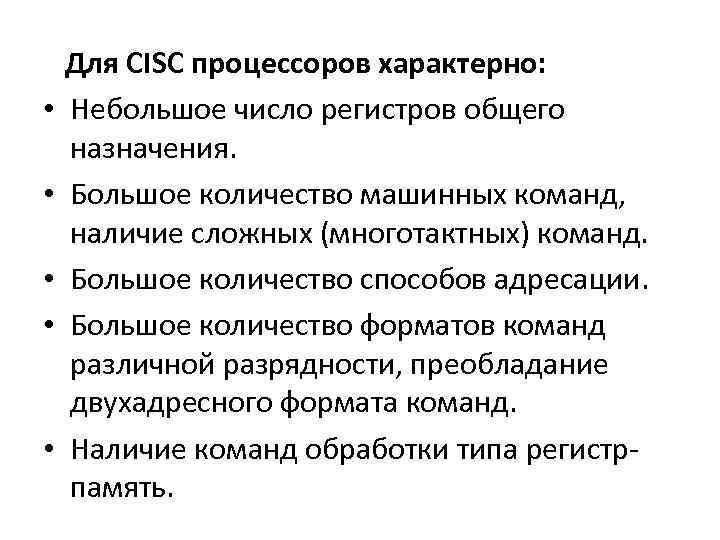

• • • Для CISC процессоров характерно: Небольшое число регистров общего назначения. Большое количество машинных команд, наличие сложных (многотактных) команд. Большое количество способов адресации. Большое количество форматов команд различной разрядности, преобладание двухадресного формата команд. Наличие команд обработки типа регистрпамять.

"HЕ CISC" Cray -1

"НЕ CISC" CDC 6600

Сем азрыв ский р нтиче а

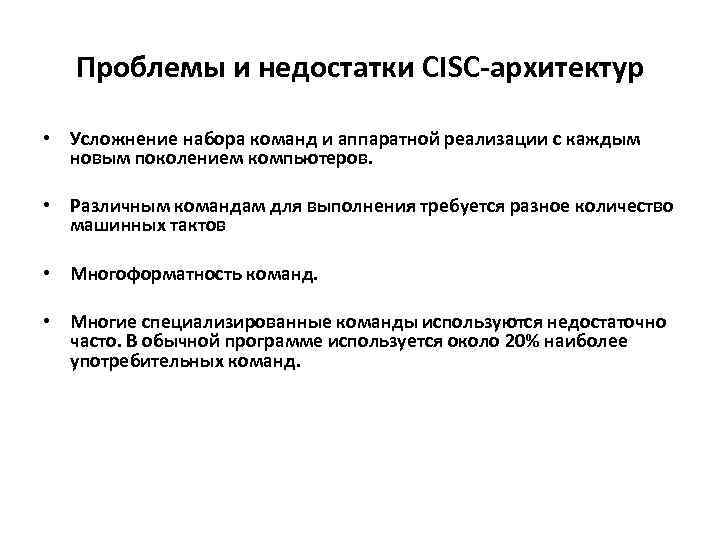

Проблемы и недостатки CISC-архитектур • Усложнение набора команд и аппаратной реализации с каждым новым поколением компьютеров. • Различным командам для выполнения требуется разное количество машинных тактов • Многоформатность команд. • Многие специализированные команды используются недостаточно часто. В обычной программе используется около 20% наиболее употребительных команд.

RISC et Co ion S truct d Ins duce Re ter mpu

John Cook

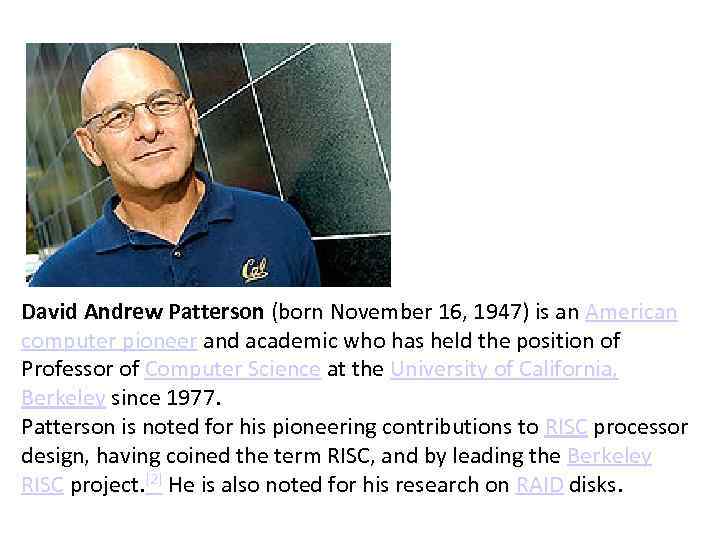

David Andrew Patterson (born November 16, 1947) is an American computer pioneer and academic who has held the position of Professor of Computer Science at the University of California, Berkeley since 1977. Patterson is noted for his pioneering contributions to RISC processor design, having coined the term RISC, and by leading the Berkeley RISC project. [2] He is also noted for his research on RAID disks.

Carlo H. Séquin Professor, CS Division, EECS Dept. , U. C. Berkeley, (Graphics Group) Facilities Development Officer, College of Engineering

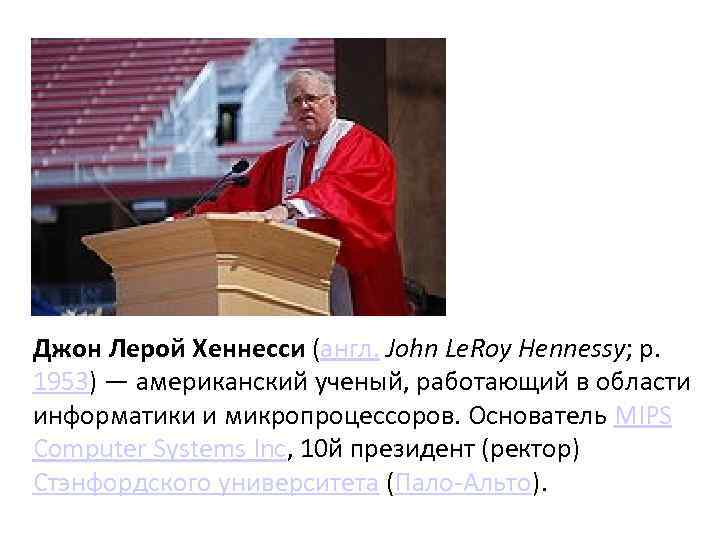

Джон Лерой Хеннесси (англ. John Le. Roy Hennessy; р. 1953) — американский ученый, работающий в области информатики и микропроцессоров. Основатель MIPS Computer Systems Inc, 10 й президент (ректор) Стэнфордского университета (Пало-Альто).

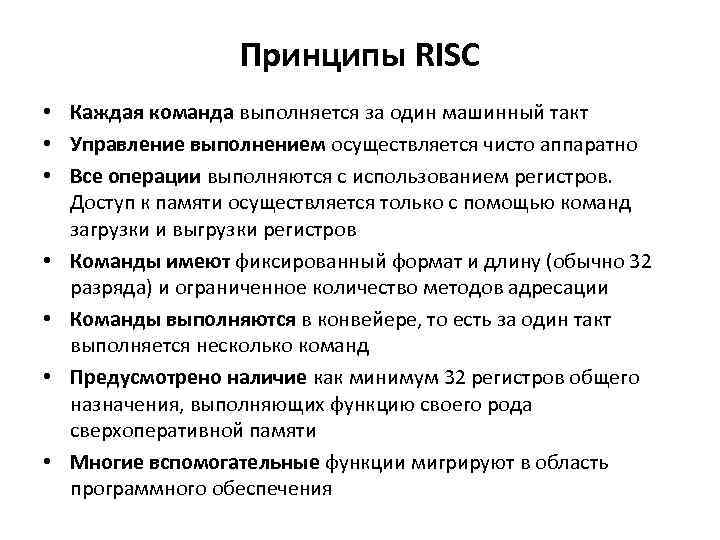

Принципы RISC • Каждая команда выполняется за один машинный такт • Управление выполнением осуществляется чисто аппаратно • Все операции выполняются с использованием регистров. Доступ к памяти осуществляется только с помощью команд загрузки и выгрузки регистров • Команды имеют фиксированный формат и длину (обычно 32 разряда) и ограниченное количество методов адресации • Команды выполняются в конвейере, то есть за один такт выполняется несколько команд • Предусмотрено наличие как минимум 32 регистров общего назначения, выполняющих функцию своего рода сверхоперативной памяти • Многие вспомогательные функции мигрируют в область программного обеспечения

RISC-процессоры • Power. PC • Intel x 86

Архитектура системы команд CISC и RISC.ppt