Архитектура вычислительных систем_лекции_3-4.pptx

- Количество слайдов: 47

Архитектура вычислительных систем Лекции 3 -4. Узлы ЭВМ. Базовая ЭВМ. Павлов А. В. pavlov@phoi. ifmo. ru Кафедра Фотоники и Оптоинформатики

Архитектура вычислительных систем Лекции 3 -4. Узлы ЭВМ. Базовая ЭВМ. Павлов А. В. pavlov@phoi. ifmo. ru Кафедра Фотоники и Оптоинформатики

Основные элементы прикладной архитектуры ЦК. Типы, форматы и способы представления данных в ЦК. Формат данных - внутреннее представление данных: разрядность и назначение битов. Например, для знаковых целых чисел крайний левый бит формата отводится для представления знаков. Для обозначения форматов стандартной длины принято использовать следующие наименования: • Байт (B – Byte) – 8 бит • Слово (W – Word) – 16 бит • Двойное слово (DW – Double Word) – 32 бита • Учетверенное слово (QW – Quadro Word) – 64 бита Ключевое понятие в отношении данных, представляемых в ЦК, - наличие или отсутствие аппаратной поддержки для конкретного типа и формата данных. Под аппаратной поддержкой подразумевается наличие в системе команд ЦК некоторого множества машинных команд, предназначенных для обработки данных определенного типа, представленных в соответствующих форматах. 2014 2

Основные элементы прикладной архитектуры ЦК. Типы, форматы и способы представления данных в ЦК. Формат данных - внутреннее представление данных: разрядность и назначение битов. Например, для знаковых целых чисел крайний левый бит формата отводится для представления знаков. Для обозначения форматов стандартной длины принято использовать следующие наименования: • Байт (B – Byte) – 8 бит • Слово (W – Word) – 16 бит • Двойное слово (DW – Double Word) – 32 бита • Учетверенное слово (QW – Quadro Word) – 64 бита Ключевое понятие в отношении данных, представляемых в ЦК, - наличие или отсутствие аппаратной поддержки для конкретного типа и формата данных. Под аппаратной поддержкой подразумевается наличие в системе команд ЦК некоторого множества машинных команд, предназначенных для обработки данных определенного типа, представленных в соответствующих форматах. 2014 2

Узлы ЭВМ Триггер (trigger – защелка, спусковой крючок)– простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под воздействием входных сигналов. Последовательностными называют такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти. Триггер — один из базовых элементов цифровой техники. Предназначен для запоминания двоичной информации. 2014 3

Узлы ЭВМ Триггер (trigger – защелка, спусковой крючок)– простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под воздействием входных сигналов. Последовательностными называют такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти. Триггер — один из базовых элементов цифровой техники. Предназначен для запоминания двоичной информации. 2014 3

Триггер. Классификация триггерных схем по: • способу приёма логических сигналов; • функциональным возможностям; • принципу построения; • числу устойчивых состояний (обычно устойчивых состояний два, реже - больше); • числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах. 2014 4

Триггер. Классификация триггерных схем по: • способу приёма логических сигналов; • функциональным возможностям; • принципу построения; • числу устойчивых состояний (обычно устойчивых состояний два, реже - больше); • числу уровней — два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах. 2014 4

Триггер. Классификация по способу работы с сигналами: асинхронные, синхронные и смешанные триггерные схемы, статические и динамические. Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб» , «такт» . Синхронные триггеры, в свою очередь, подразделяют на: Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход). Одноступенчатые - одна ступень запоминания информации. Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Двухступенчатые — две ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер 2014 обозначают ТТ. 5

Триггер. Классификация по способу работы с сигналами: асинхронные, синхронные и смешанные триггерные схемы, статические и динамические. Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб» , «такт» . Синхронные триггеры, в свою очередь, подразделяют на: Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход). Одноступенчатые - одна ступень запоминания информации. Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Двухступенчатые — две ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер 2014 обозначают ТТ. 5

Триггер. Классификация: по структурному построению: однотактные (триггеры защёлки) двухтактные триггеры с динамическим управлением По способу реакции на помехи непрозрачные проницаемые непроницаемые По функциональному назначению: RS, D, JK, T, RR, SS, EE, DV. 2014 6

Триггер. Классификация: по структурному построению: однотактные (триггеры защёлки) двухтактные триггеры с динамическим управлением По способу реакции на помехи непрозрачные проницаемые непроницаемые По функциональному назначению: RS, D, JK, T, RR, SS, EE, DV. 2014 6

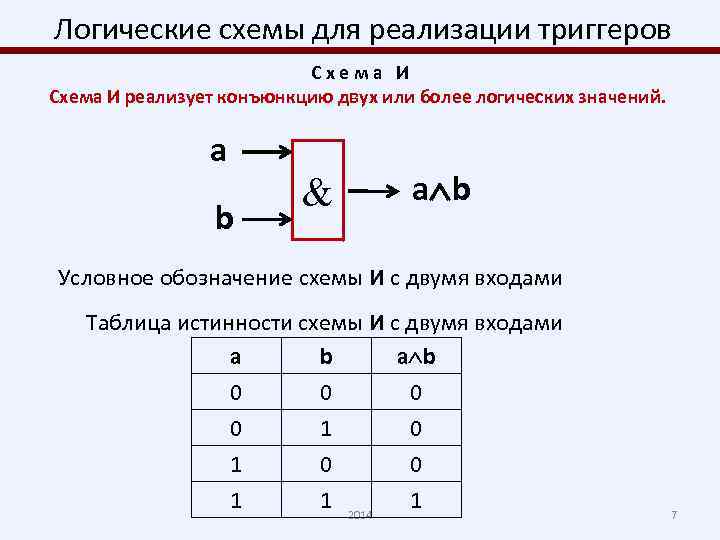

Логические схемы для реализации триггеров С х е м а И Схема И реализует конъюнкцию двух или более логических значений. a b Условное обозначение схемы И с двумя входами Таблица истинности схемы И с двумя входами a b 0 0 1 1 2014 1 7

Логические схемы для реализации триггеров С х е м а И Схема И реализует конъюнкцию двух или более логических значений. a b Условное обозначение схемы И с двумя входами Таблица истинности схемы И с двумя входами a b 0 0 1 1 2014 1 7

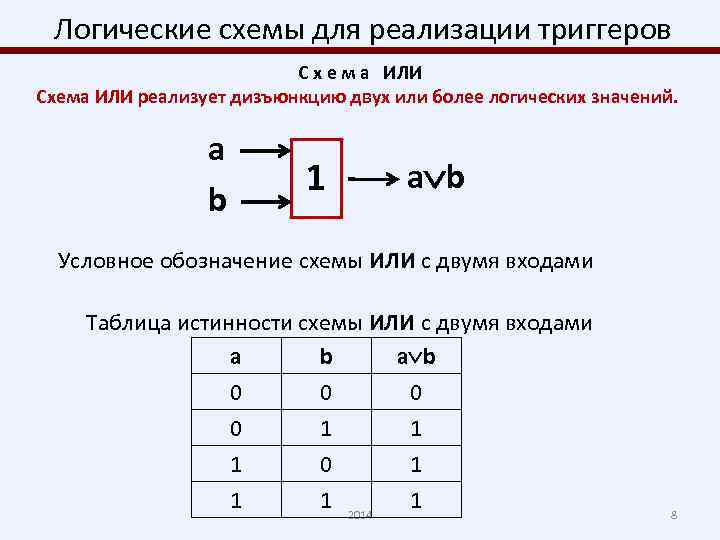

Логические схемы для реализации триггеров С х е м а ИЛИ Схема ИЛИ реализует дизъюнкцию двух или более логических значений. a b 1 a b Условное обозначение схемы ИЛИ с двумя входами Таблица истинности схемы ИЛИ с двумя входами a b 0 0 1 1 1 2014 1 8

Логические схемы для реализации триггеров С х е м а ИЛИ Схема ИЛИ реализует дизъюнкцию двух или более логических значений. a b 1 a b Условное обозначение схемы ИЛИ с двумя входами Таблица истинности схемы ИЛИ с двумя входами a b 0 0 1 1 1 2014 1 8

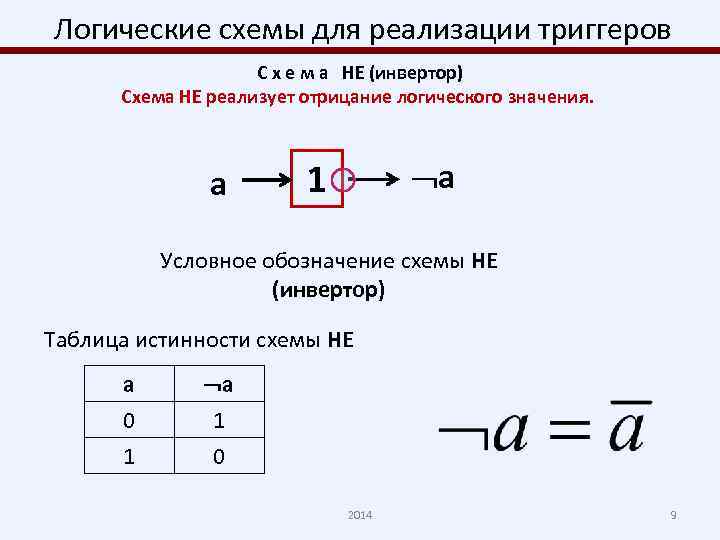

Логические схемы для реализации триггеров С х е м а НЕ (инвертор) Схема НЕ реализует отрицание логического значения. a a 1 Условное обозначение схемы НЕ (инвертор) Таблица истинности схемы НЕ a 0 1 a 1 0 2014 9

Логические схемы для реализации триггеров С х е м а НЕ (инвертор) Схема НЕ реализует отрицание логического значения. a a 1 Условное обозначение схемы НЕ (инвертор) Таблица истинности схемы НЕ a 0 1 a 1 0 2014 9

Логические схемы для реализации триггеров С х е м а И-НЕ Схема И-НЕ реализует отрицание результата работы схемы И. a b ab Таблица истинности схемы И-НЕ a b ab Условное обозначение схемы НЕ 2014 a 0 0 1 b 0 1 0 ab 1 1 1 0 10

Логические схемы для реализации триггеров С х е м а И-НЕ Схема И-НЕ реализует отрицание результата работы схемы И. a b ab Таблица истинности схемы И-НЕ a b ab Условное обозначение схемы НЕ 2014 a 0 0 1 b 0 1 0 ab 1 1 1 0 10

Логические схемы для реализации триггеров С х е м а ИЛИ-НЕ Схема ИЛИ-НЕ реализует отрицание дизъюнкции двух или более логических значений. a b 1 (a b) Таблица истинности схемы ИЛИ-НЕ a b 1 (a b) Условное обозначение схемы ИЛИ-НЕ 2014 a 0 0 1 b 0 1 0 (a b) 1 0 0 1 1 0 11

Логические схемы для реализации триггеров С х е м а ИЛИ-НЕ Схема ИЛИ-НЕ реализует отрицание дизъюнкции двух или более логических значений. a b 1 (a b) Таблица истинности схемы ИЛИ-НЕ a b 1 (a b) Условное обозначение схемы ИЛИ-НЕ 2014 a 0 0 1 b 0 1 0 (a b) 1 0 0 1 1 0 11

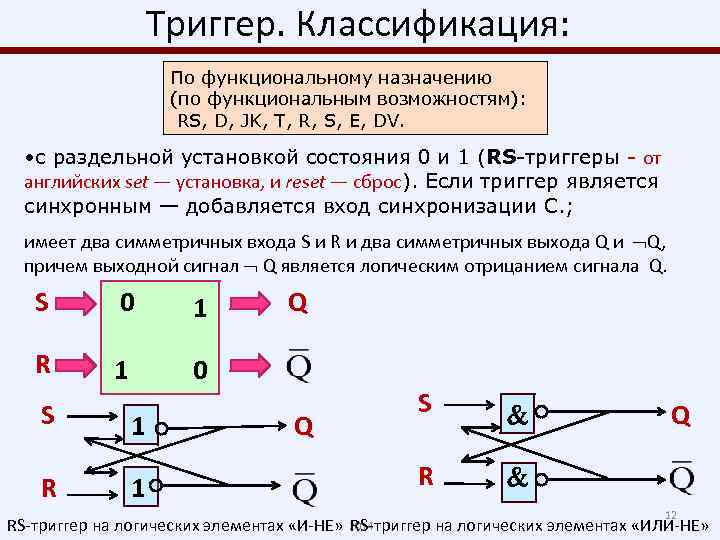

Триггер. Классификация: По функциональному назначению (по функциональным возможностям): RS, D, JK, T, R, S, E, DV. • с раздельной установкой состояния 0 и 1 (RS-триггеры - от английских set — установка, и reset — сброс). Если триггер является синхронным — добавляется вход синхронизации C. ; имеет два симметричных входа S и R и два симметричных выхода Q и Q, причем выходной сигнал Q является логическим отрицанием сигнала Q. S 0 1 R 1 0 S 1 R 1 Q Q S R Q 12 RS-триггер на логических элементах «И-НЕ» 2014 RS-триггер на логических элементах «ИЛИ-НЕ»

Триггер. Классификация: По функциональному назначению (по функциональным возможностям): RS, D, JK, T, R, S, E, DV. • с раздельной установкой состояния 0 и 1 (RS-триггеры - от английских set — установка, и reset — сброс). Если триггер является синхронным — добавляется вход синхронизации C. ; имеет два симметричных входа S и R и два симметричных выхода Q и Q, причем выходной сигнал Q является логическим отрицанием сигнала Q. S 0 1 R 1 0 S 1 R 1 Q Q S R Q 12 RS-триггер на логических элементах «И-НЕ» 2014 RS-триггер на логических элементах «ИЛИ-НЕ»

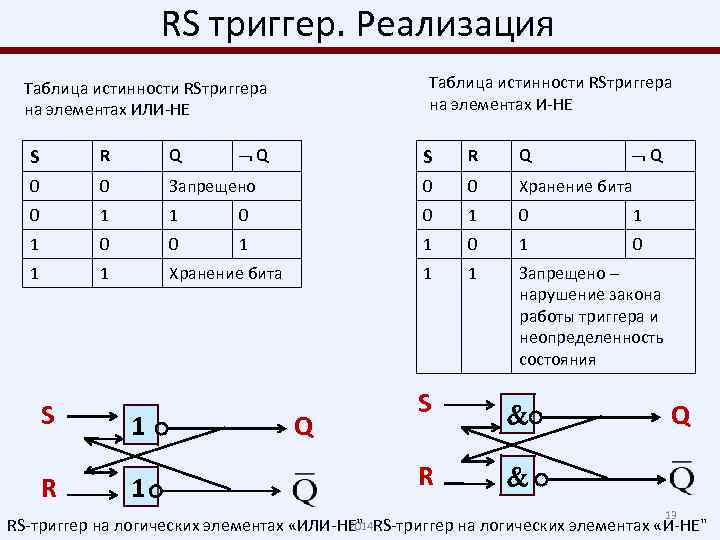

RS триггер. Реализация Таблица истинности RSтриггера на элементах И-НЕ Таблица истинности RSтриггера на элементах ИЛИ-НЕ S R Q 0 0 0 Q Q S R Q Запрещено 0 0 Хранение бита 1 1 0 0 1 1 0 1 1 Хранение бита 1 1 Запрещено – нарушение закона работы триггера и неопределенность состояния S 1 R 1 Q S R Q 13 2014 RS-триггер на логических элементах «ИЛИ-НЕ" RS-триггер на логических элементах «И-НЕ"

RS триггер. Реализация Таблица истинности RSтриггера на элементах И-НЕ Таблица истинности RSтриггера на элементах ИЛИ-НЕ S R Q 0 0 0 Q Q S R Q Запрещено 0 0 Хранение бита 1 1 0 0 1 1 0 1 1 Хранение бита 1 1 Запрещено – нарушение закона работы триггера и неопределенность состояния S 1 R 1 Q S R Q 13 2014 RS-триггер на логических элементах «ИЛИ-НЕ" RS-триггер на логических элементах «И-НЕ"

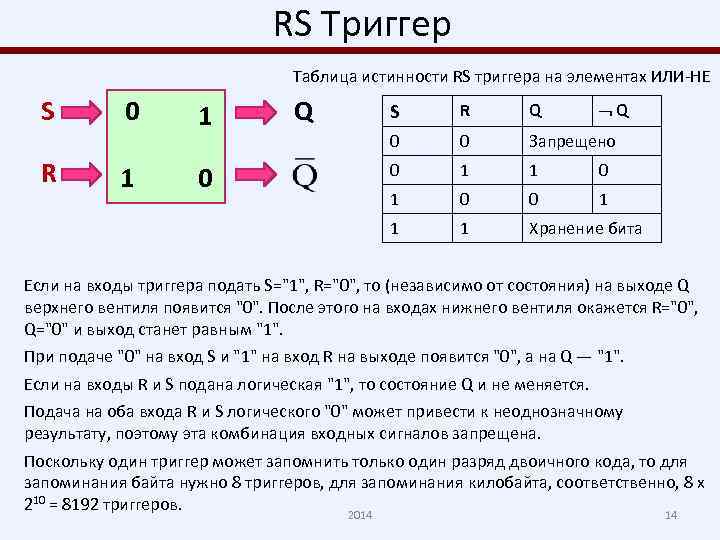

RS Триггер Таблица истинности RS триггера на элементах ИЛИ-НЕ S 0 1 Q Q 1 Q 0 0 Запрещено 0 1 1 0 R 0 0 1 1 R S 1 Хранение бита Если на входы триггера подать S="1", R="0", то (независимо от состояния) на выходе Q верхнего вентиля появится "0". После этого на входах нижнего вентиля окажется R="0", Q="0" и выход станет равным "1". При подаче "0" на вход S и "1" на вход R на выходе появится "0", а на Q — "1". Если на входы R и S подана логическая "1", то состояние Q и не меняется. Подача на оба входа R и S логического "0" может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена. Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. 2014 14

RS Триггер Таблица истинности RS триггера на элементах ИЛИ-НЕ S 0 1 Q Q 1 Q 0 0 Запрещено 0 1 1 0 R 0 0 1 1 R S 1 Хранение бита Если на входы триггера подать S="1", R="0", то (независимо от состояния) на выходе Q верхнего вентиля появится "0". После этого на входах нижнего вентиля окажется R="0", Q="0" и выход станет равным "1". При подаче "0" на вход S и "1" на вход R на выходе появится "0", а на Q — "1". Если на входы R и S подана логическая "1", то состояние Q и не меняется. Подача на оба входа R и S логического "0" может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена. Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. 2014 14

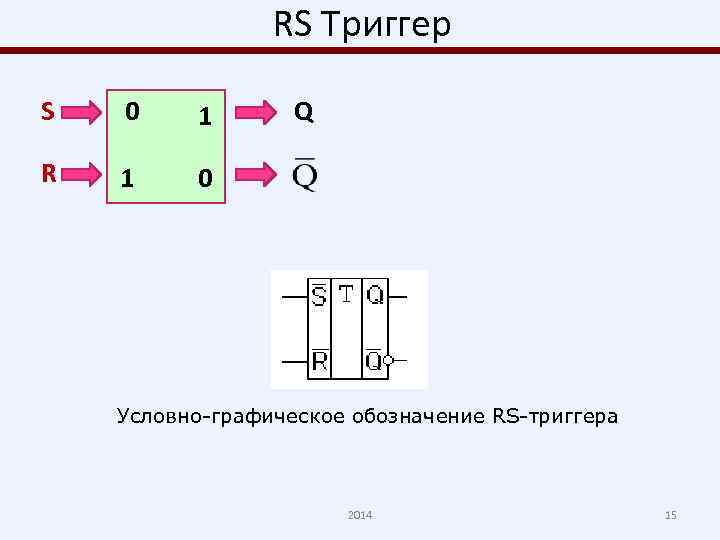

RS Триггер S 0 1 R 1 Q 0 Условно-графическое обозначение RS-триггера 2014 15

RS Триггер S 0 1 R 1 Q 0 Условно-графическое обозначение RS-триггера 2014 15

Триггер. Синхронные RS-триггеры Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы в триггерах нужно только в определённые моменты времени, когда все переходные процессы закончены. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Если триггер синхронный, то существует также дополнительный вход синхронизации C. Для того, чтобы такой триггер учёл информацию на синхронных входах, на входе синхронизации необходимо сформировать активный фронт (обычно положительный фронт). 2014 16

Триггер. Синхронные RS-триггеры Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы в триггерах нужно только в определённые моменты времени, когда все переходные процессы закончены. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Если триггер синхронный, то существует также дополнительный вход синхронизации C. Для того, чтобы такой триггер учёл информацию на синхронных входах, на входе синхронизации необходимо сформировать активный фронт (обычно положительный фронт). 2014 16

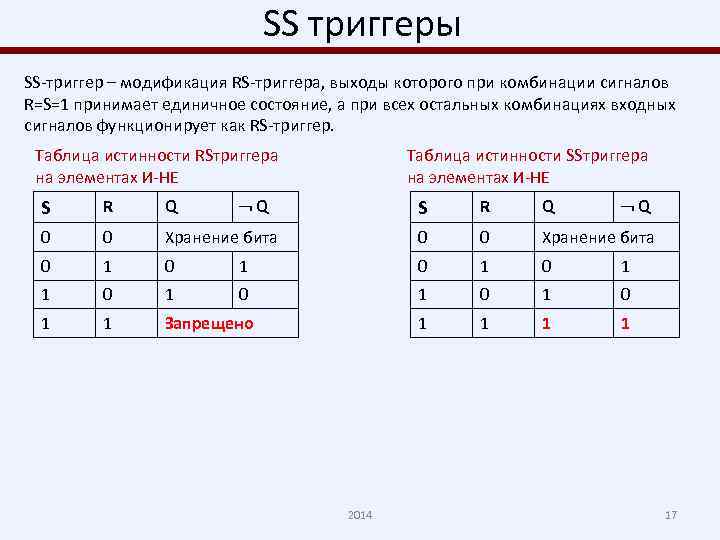

SS триггеры SS-триггер – модификация RS-триггера, выходы которого при комбинации сигналов R=S=1 принимает единичное состояние, а при всех остальных комбинациях входных сигналов функционирует как RS-триггер. Таблица истинности RSтриггера на элементах И-НЕ S R Q 0 0 0 Таблица истинности SSтриггера на элементах И-НЕ Q Q S R Q Хранение бита 0 0 Хранение бита 1 0 1 0 1 1 Запрещено 1 1 2014 17

SS триггеры SS-триггер – модификация RS-триггера, выходы которого при комбинации сигналов R=S=1 принимает единичное состояние, а при всех остальных комбинациях входных сигналов функционирует как RS-триггер. Таблица истинности RSтриггера на элементах И-НЕ S R Q 0 0 0 Таблица истинности SSтриггера на элементах И-НЕ Q Q S R Q Хранение бита 0 0 Хранение бита 1 0 1 0 1 1 Запрещено 1 1 2014 17

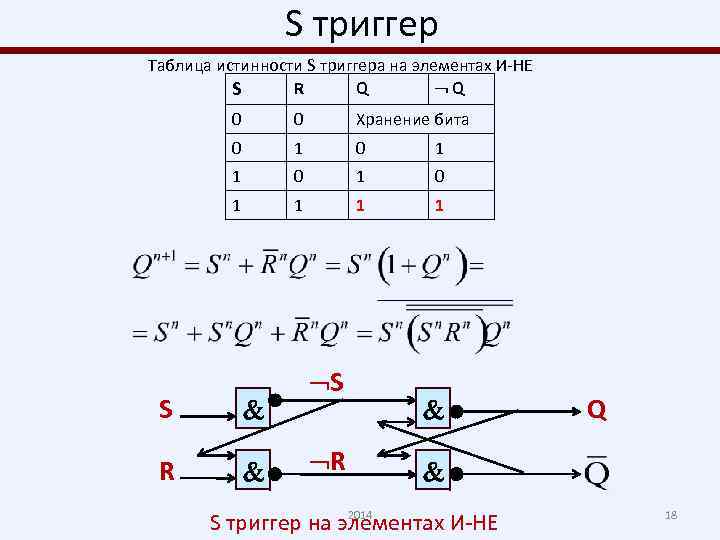

S триггер Таблица истинности S триггера на элементах И-НЕ R Q Q S 0 0 Хранение бита 0 1 0 1 1 1 1 S R Q 2014 S триггер на элементах И-НЕ 18

S триггер Таблица истинности S триггера на элементах И-НЕ R Q Q S 0 0 Хранение бита 0 1 0 1 1 1 1 S R Q 2014 S триггер на элементах И-НЕ 18

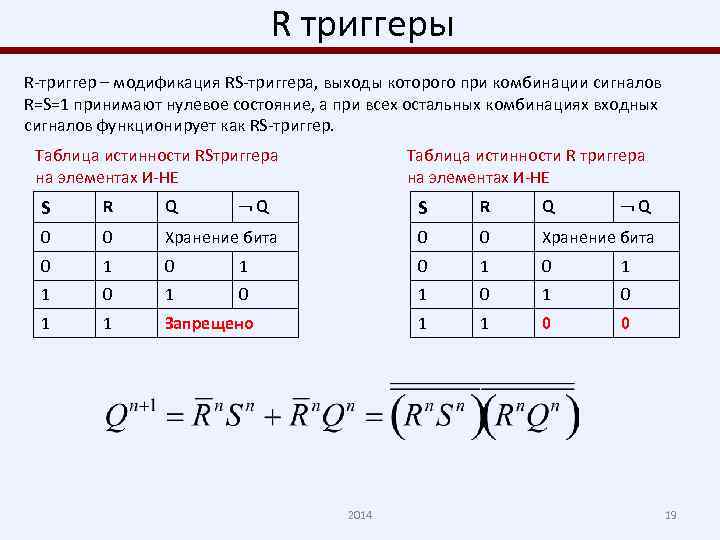

R триггеры R-триггер – модификация RS-триггера, выходы которого при комбинации сигналов R=S=1 принимают нулевое состояние, а при всех остальных комбинациях входных сигналов функционирует как RS-триггер. Таблица истинности RSтриггера на элементах И-НЕ S R Q 0 0 0 Таблица истинности R триггера на элементах И-НЕ Q Q S R Q Хранение бита 0 0 Хранение бита 1 0 1 0 1 1 Запрещено 1 1 0 0 2014 19

R триггеры R-триггер – модификация RS-триггера, выходы которого при комбинации сигналов R=S=1 принимают нулевое состояние, а при всех остальных комбинациях входных сигналов функционирует как RS-триггер. Таблица истинности RSтриггера на элементах И-НЕ S R Q 0 0 0 Таблица истинности R триггера на элементах И-НЕ Q Q S R Q Хранение бита 0 0 Хранение бита 1 0 1 0 1 1 Запрещено 1 1 0 0 2014 19

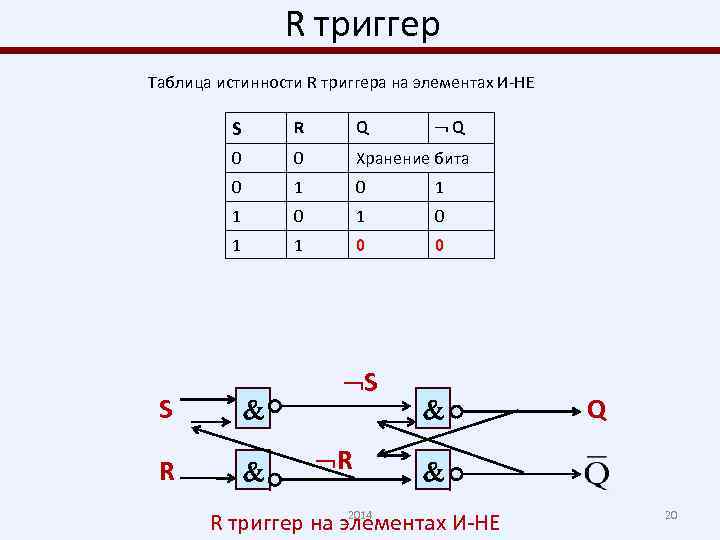

R триггер Таблица истинности R триггера на элементах И-НЕ Q S R Q 0 0 Хранение бита 0 1 0 1 1 0 0 S R Q 2014 R триггер на элементах И-НЕ 20

R триггер Таблица истинности R триггера на элементах И-НЕ Q S R Q 0 0 Хранение бита 0 1 0 1 1 0 0 S R Q 2014 R триггер на элементах И-НЕ 20

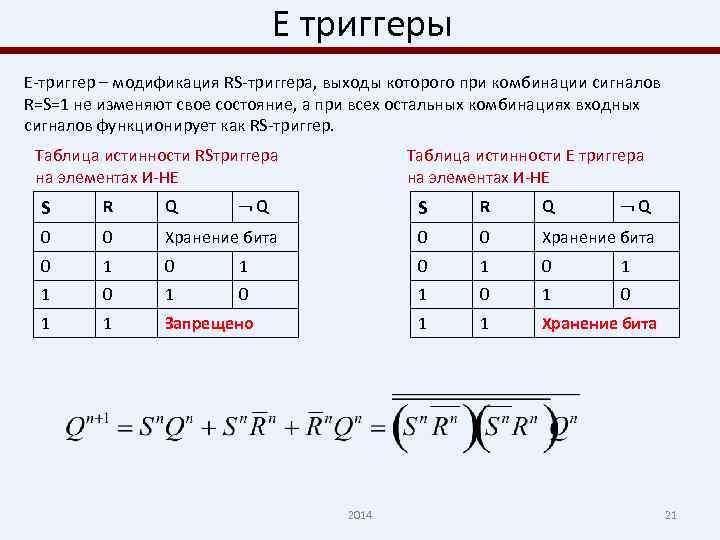

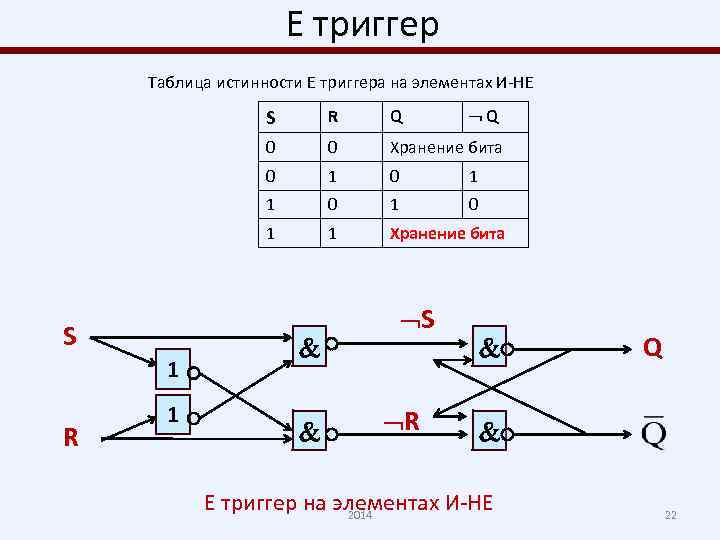

E триггеры Е-триггер – модификация RS-триггера, выходы которого при комбинации сигналов R=S=1 не изменяют свое состояние, а при всех остальных комбинациях входных сигналов функционирует как RS-триггер. Таблица истинности RSтриггера на элементах И-НЕ S R Q 0 0 0 Таблица истинности Е триггера на элементах И-НЕ Q Q S R Q Хранение бита 0 0 Хранение бита 1 0 1 0 1 1 Запрещено 1 1 Хранение бита 2014 21

E триггеры Е-триггер – модификация RS-триггера, выходы которого при комбинации сигналов R=S=1 не изменяют свое состояние, а при всех остальных комбинациях входных сигналов функционирует как RS-триггер. Таблица истинности RSтриггера на элементах И-НЕ S R Q 0 0 0 Таблица истинности Е триггера на элементах И-НЕ Q Q S R Q Хранение бита 0 0 Хранение бита 1 0 1 0 1 1 Запрещено 1 1 Хранение бита 2014 21

Е триггер Таблица истинности E триггера на элементах И-НЕ Q S 1 0 1 0 1 R Хранение бита 1 1 0 0 1 Q 0 S R 1 Хранение бита S R Q Е триггер на элементах И-НЕ 2014 22

Е триггер Таблица истинности E триггера на элементах И-НЕ Q S 1 0 1 0 1 R Хранение бита 1 1 0 0 1 Q 0 S R 1 Хранение бита S R Q Е триггер на элементах И-НЕ 2014 22

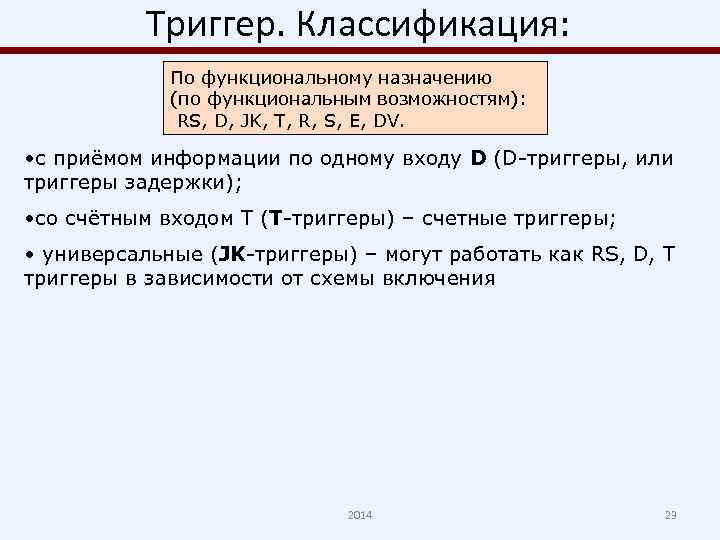

Триггер. Классификация: По функциональному назначению (по функциональным возможностям): RS, D, JK, T, R, S, E, DV. • с приёмом информации по одному входу D (D-триггеры, или триггеры задержки); • со счётным входом Т (Т-триггеры) – счетные триггеры; • универсальные (JK-триггеры) – могут работать как RS, D, T триггеры в зависимости от схемы включения 2014 23

Триггер. Классификация: По функциональному назначению (по функциональным возможностям): RS, D, JK, T, R, S, E, DV. • с приёмом информации по одному входу D (D-триггеры, или триггеры задержки); • со счётным входом Т (Т-триггеры) – счетные триггеры; • универсальные (JK-триггеры) – могут работать как RS, D, T триггеры в зависимости от схемы включения 2014 23

• D-триггеры от англ. delay — задержка В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Поскольку сигналы установки и сброса триггера не могут появляться одновременно, то можно объединить эти входы при помощи инвертора Принципиальная схема D триггера (на элементах ИЛИ-НЕ). Условно-графическое обозначение D триггера Таблица истинности D триггера на С D Q(t) Q(t+1) Пояснения 0 произвольное 0 0 0 произвольное 1 1 Режим хранения информации 1 0 произвольное 0 1 1 произвольное 1 Режим записи информации Д- триггер способен запоминать по синхросигналу и хранить один бит двоичной информации. 2014 24

• D-триггеры от англ. delay — задержка В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Поскольку сигналы установки и сброса триггера не могут появляться одновременно, то можно объединить эти входы при помощи инвертора Принципиальная схема D триггера (на элементах ИЛИ-НЕ). Условно-графическое обозначение D триггера Таблица истинности D триггера на С D Q(t) Q(t+1) Пояснения 0 произвольное 0 0 0 произвольное 1 1 Режим хранения информации 1 0 произвольное 0 1 1 произвольное 1 Режим записи информации Д- триггер способен запоминать по синхросигналу и хранить один бит двоичной информации. 2014 24

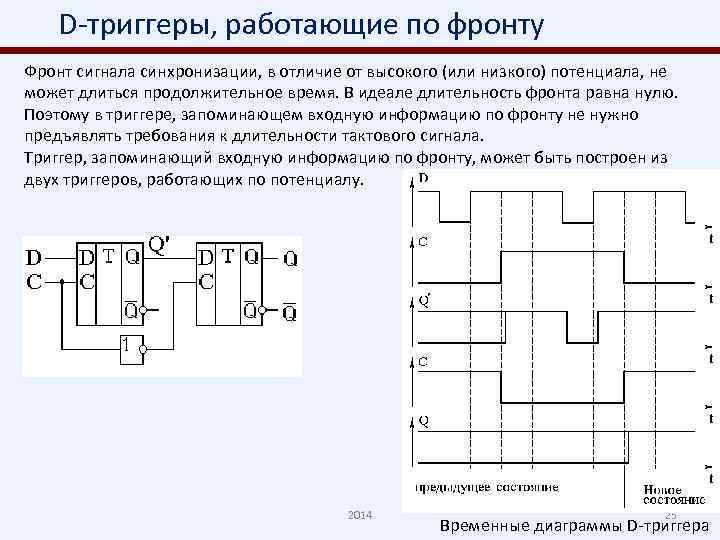

D-триггеры, работающие по фронту Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала. Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу. 2014 25 Временные диаграммы D-триггера

D-триггеры, работающие по фронту Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала. Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу. 2014 25 Временные диаграммы D-триггера

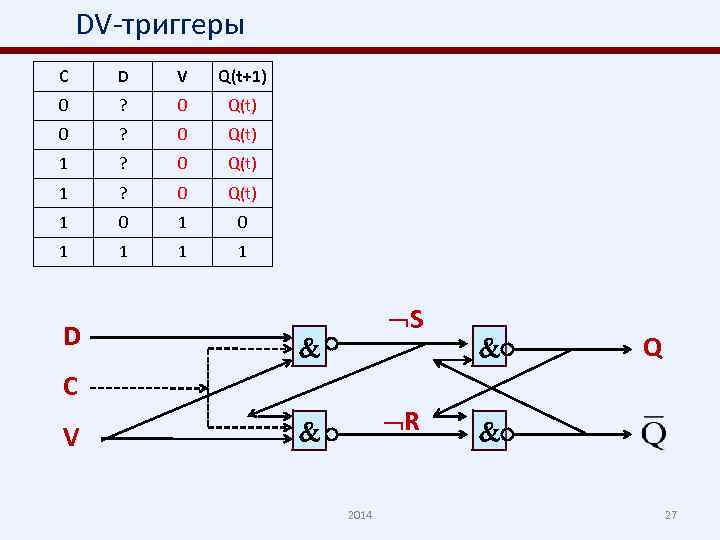

DV-триггеры DV – триггер – это D-триггер, имеющий дополнительный управляющий вход V. При V = 1 DV-триггер работает по правилам D-триггера. При сигнале V = 0 триггер сохраняет свое состояние неизменным – «защелкивается» и хранит информацию независимо от состояния входа D. Наличие дополнительного входа V расширяет функциональные возможности D-триггера – информация на выходах в нужные моменты может быть сохранена в течении необходимого числа тактов. C D V Q(t+1) С D Q(t) ? 0 0 0 ? 1 1 0 ? 0 1 1 ? 1 2014 ? 0 Q(t) 1 РЗИ Q(t) 1 1 0 1 РХИ ? 0 Q(t+1) 0 0 0 1 1 1 1 26

DV-триггеры DV – триггер – это D-триггер, имеющий дополнительный управляющий вход V. При V = 1 DV-триггер работает по правилам D-триггера. При сигнале V = 0 триггер сохраняет свое состояние неизменным – «защелкивается» и хранит информацию независимо от состояния входа D. Наличие дополнительного входа V расширяет функциональные возможности D-триггера – информация на выходах в нужные моменты может быть сохранена в течении необходимого числа тактов. C D V Q(t+1) С D Q(t) ? 0 0 0 ? 1 1 0 ? 0 1 1 ? 1 2014 ? 0 Q(t) 1 РЗИ Q(t) 1 1 0 1 РХИ ? 0 Q(t+1) 0 0 0 1 1 1 1 26

DV-триггеры C D V Q(t+1) 0 ? 0 Q(t) 1 0 1 1 D S C V R 2014 Q 27

DV-триггеры C D V Q(t+1) 0 ? 0 Q(t) 1 0 1 1 D S C V R 2014 Q 27

Т-триггеры - счетные У Т триггера только один вход. (У TV – два, есть еще и управляющий вход, как у DV. ) После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. При поступлении второго импульса T-триггер сбрасывается в исходное состояние. Таким образом, считать Т-триггер умеет только до одного . Используются при построении схем различных счётчиков T-триггеры можно построить только на базе двухступенчатых триггеров, подобных D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации C. Схема T триггера на основе D триггера Временные диаграммы T-триггера (использован Д-триггер, работающий по заднему фронту сигнала) 2014 28

Т-триггеры - счетные У Т триггера только один вход. (У TV – два, есть еще и управляющий вход, как у DV. ) После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. При поступлении второго импульса T-триггер сбрасывается в исходное состояние. Таким образом, считать Т-триггер умеет только до одного . Используются при построении схем различных счётчиков T-триггеры можно построить только на базе двухступенчатых триггеров, подобных D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации C. Схема T триггера на основе D триггера Временные диаграммы T-триггера (использован Д-триггер, работающий по заднему фронту сигнала) 2014 28

JR-триггеры - универсальные В RS триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы R и S запрещены. Таблица истинности JK триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц JK триггер превращается в Е-триггер. Это означает, что при подаче на тактовый вход C импульсов этот триггер изменяет своё состояние на противоположное. Для реализации счетного режима в схеме введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация, а то, что она перекрестная, вводит новый режим работы — счетный. При подаче на входы J и K логической единицы одновременно JK -триггер переходит в счетный режим, подобно T триггеру. Схема JK триггера 2014 29

JR-триггеры - универсальные В RS триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы R и S запрещены. Таблица истинности JK триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц JK триггер превращается в Е-триггер. Это означает, что при подаче на тактовый вход C импульсов этот триггер изменяет своё состояние на противоположное. Для реализации счетного режима в схеме введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация, а то, что она перекрестная, вводит новый режим работы — счетный. При подаче на входы J и K логической единицы одновременно JK -триггер переходит в счетный режим, подобно T триггеру. Схема JK триггера 2014 29

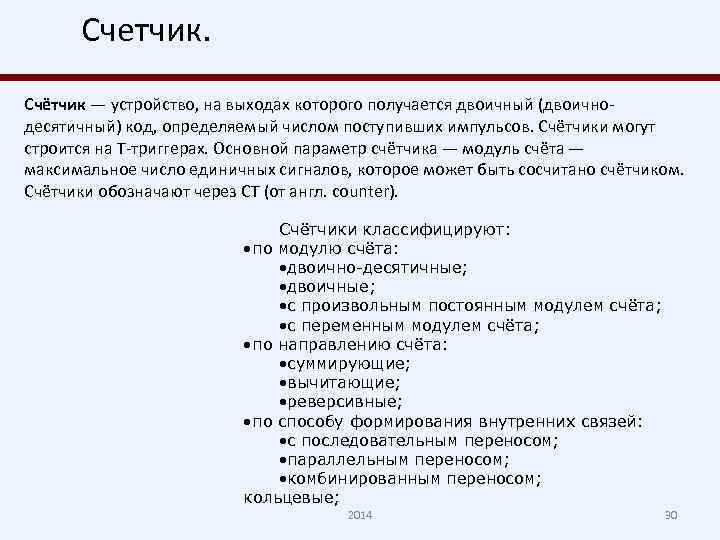

Счетчик. Счётчик — устройство, на выходах которого получается двоичный (двоичнодесятичный) код, определяемый числом поступивших импульсов. Счётчики могут строится на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter). Счётчики классифицируют: • по модулю счёта: двоично-десятичные; двоичные; с произвольным постоянным модулем счёта; с переменным модулем счёта; • по направлению счёта: суммирующие; вычитающие; реверсивные; • по способу формирования внутренних связей: с последовательным переносом; параллельным переносом; комбинированным переносом; кольцевые; 2014 30

Счетчик. Счётчик — устройство, на выходах которого получается двоичный (двоичнодесятичный) код, определяемый числом поступивших импульсов. Счётчики могут строится на T-триггерах. Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter). Счётчики классифицируют: • по модулю счёта: двоично-десятичные; двоичные; с произвольным постоянным модулем счёта; с переменным модулем счёта; • по направлению счёта: суммирующие; вычитающие; реверсивные; • по способу формирования внутренних связей: с последовательным переносом; параллельным переносом; комбинированным переносом; кольцевые; 2014 30

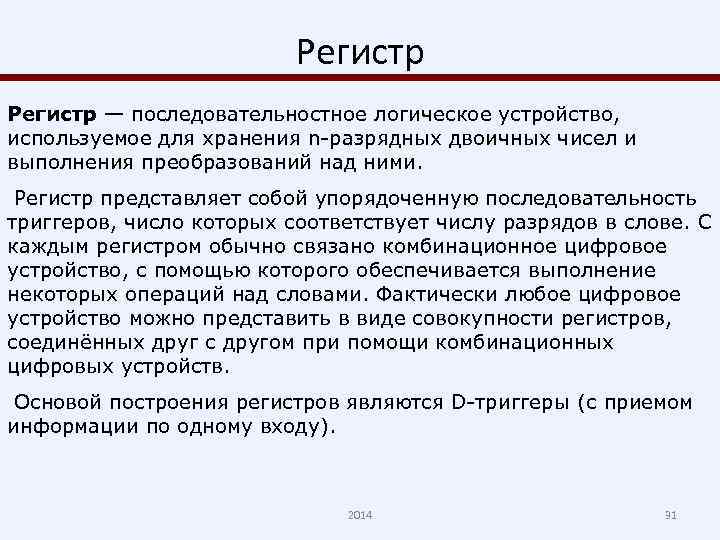

Регистр — последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств. Основой построения регистров являются D-триггеры (с приемом информации по одному входу). 2014 31

Регистр — последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединённых друг с другом при помощи комбинационных цифровых устройств. Основой построения регистров являются D-триггеры (с приемом информации по одному входу). 2014 31

Регистр. Операции • приём слова в регистр; • передача слова из регистра; • поразрядные логические операции; • сдвиг слова влево или вправо на заданное число разрядов; • преобразование последовательного кода слова в параллельный и обратно; • установка регистра в начальное состояние (сброс). 2014 32

Регистр. Операции • приём слова в регистр; • передача слова из регистра; • поразрядные логические операции; • сдвиг слова влево или вправо на заданное число разрядов; • преобразование последовательного кода слова в параллельный и обратно; • установка регистра в начальное состояние (сброс). 2014 32

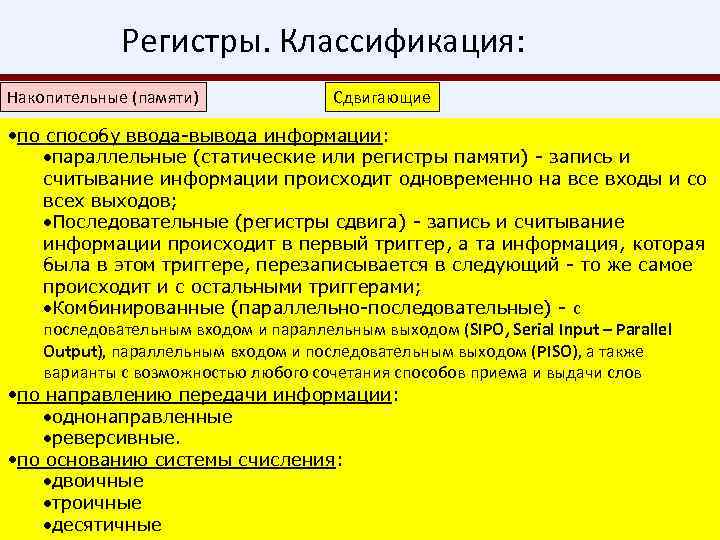

Регистры. Классификация: Накопительные (памяти) Сдвигающие • по способу ввода-вывода информации: параллельные (статические или регистры памяти) - запись и считывание информации происходит одновременно на все входы и со всех выходов; Последовательные (регистры сдвига) - запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий - то же самое происходит и с остальными триггерами; Комбинированные (параллельно-последовательные) - с последовательным входом и параллельным выходом (SIPO, Serial Input – Parallel Output), параллельным входом и последовательным выходом (PISO), а также варианты с возможностью любого сочетания способов приема и выдачи слов • по направлению передачи информации: однонаправленные реверсивные. • по основанию системы счисления: двоичные троичные 2014 33 десятичные

Регистры. Классификация: Накопительные (памяти) Сдвигающие • по способу ввода-вывода информации: параллельные (статические или регистры памяти) - запись и считывание информации происходит одновременно на все входы и со всех выходов; Последовательные (регистры сдвига) - запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий - то же самое происходит и с остальными триггерами; Комбинированные (параллельно-последовательные) - с последовательным входом и параллельным выходом (SIPO, Serial Input – Parallel Output), параллельным входом и последовательным выходом (PISO), а также варианты с возможностью любого сочетания способов приема и выдачи слов • по направлению передачи информации: однонаправленные реверсивные. • по основанию системы счисления: двоичные троичные 2014 33 десятичные

Регистры. Параллельные или статические В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям. Схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, т. е. цепи управления. С D 0 Q 0 D 1 Q 1 D(N-1) Q(N-1) Схема N-разрядного регистра памяти на основе D-триггеров с общим входом управления записью информацией D 0 RG Q 0 D 1 Q 1 D 2 Q 2 … … D(N-1) Q(N-1) С 2014 34

Регистры. Параллельные или статические В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям. Схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, т. е. цепи управления. С D 0 Q 0 D 1 Q 1 D(N-1) Q(N-1) Схема N-разрядного регистра памяти на основе D-триггеров с общим входом управления записью информацией D 0 RG Q 0 D 1 Q 1 D 2 Q 2 … … D(N-1) Q(N-1) С 2014 34

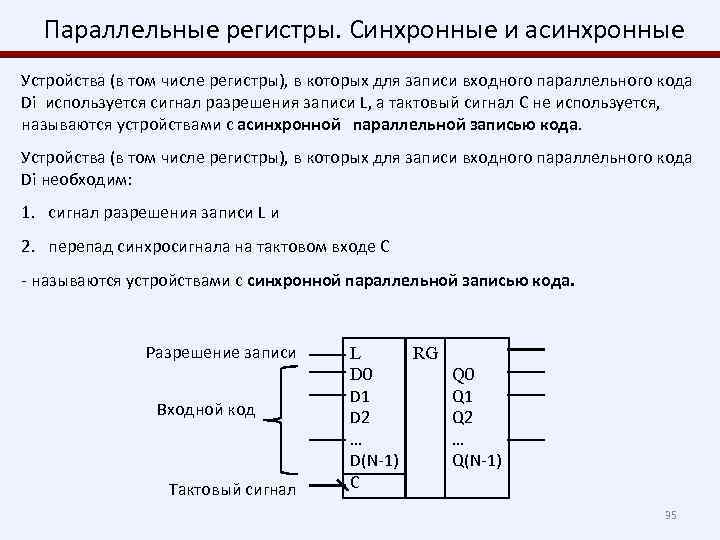

Параллельные регистры. Синхронные и асинхронные Устройства (в том числе регистры), в которых для записи входного параллельного кода Di используется сигнал разрешения записи L, а тактовый сигнал C не используется, называются устройствами с асинхронной параллельной записью кода. Устройства (в том числе регистры), в которых для записи входного параллельного кода Di необходим: 1. сигнал разрешения записи L и 2. перепад синхросигнала на тактовом входе C - называются устройствами с синхронной параллельной записью кода. Разрешение записи Входной код Тактовый сигнал L RG D 0 Q 0 D 1 Q 1 D 2 Q 2 … … D(N-1) Q(N-1) С 35

Параллельные регистры. Синхронные и асинхронные Устройства (в том числе регистры), в которых для записи входного параллельного кода Di используется сигнал разрешения записи L, а тактовый сигнал C не используется, называются устройствами с асинхронной параллельной записью кода. Устройства (в том числе регистры), в которых для записи входного параллельного кода Di необходим: 1. сигнал разрешения записи L и 2. перепад синхросигнала на тактовом входе C - называются устройствами с синхронной параллельной записью кода. Разрешение записи Входной код Тактовый сигнал L RG D 0 Q 0 D 1 Q 1 D 2 Q 2 … … D(N-1) Q(N-1) С 35

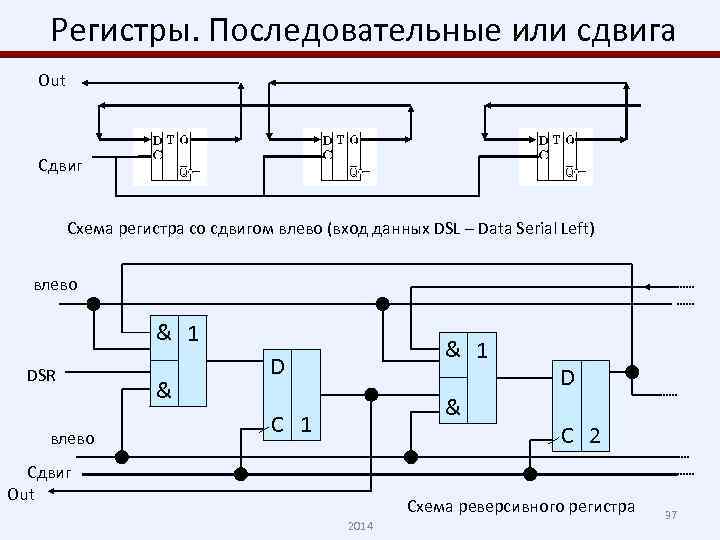

Регистры. Последовательные или сдвига Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса. В однотактных регистрах слово сдвигается при поступлении синхросигнала. Вход и выход – последовательные. DSR – Data Serial Right; DSL – Data Serial Left; Реверсивные регистры (сдвиг вправо или влево). Out Сдвиг DSR регистр 2014 36

Регистры. Последовательные или сдвига Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса. В однотактных регистрах слово сдвигается при поступлении синхросигнала. Вход и выход – последовательные. DSR – Data Serial Right; DSL – Data Serial Left; Реверсивные регистры (сдвиг вправо или влево). Out Сдвиг DSR регистр 2014 36

Регистры. Последовательные или сдвига Out Сдвиг Cхема регистра со сдвигом влево (вход данных DSL – Data Serial Left) влево & 1 DSR влево & & 1 D & C 1 Сдвиг Out D C 2 Cхема реверсивного регистра 2014 37

Регистры. Последовательные или сдвига Out Сдвиг Cхема регистра со сдвигом влево (вход данных DSL – Data Serial Left) влево & 1 DSR влево & & 1 D & C 1 Сдвиг Out D C 2 Cхема реверсивного регистра 2014 37

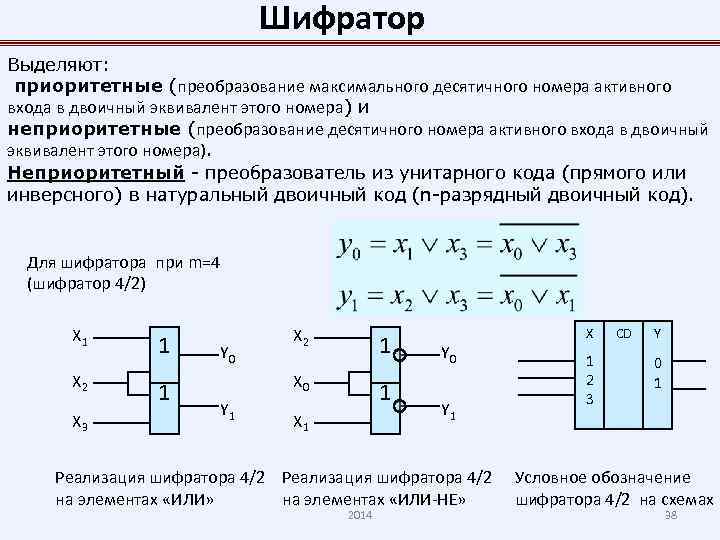

Шифратор Выделяют: приоритетные (преобразование максимального десятичного номера активного входа в двоичный эквивалент этого номера) и неприоритетные (преобразование десятичного номера активного входа в двоичный эквивалент этого номера). Неприоритетный - преобразователь из унитарного кода (прямого или инверсного) в натуральный двоичный код (n-разрядный двоичный код). Для шифратора при m=4 (шифратор 4/2) X 1 X 2 X 3 1 1 Y 0 X 2 1 X 0 Y 1 1 X 1 Y 0 Y 1 Реализация шифратора 4/2 на элементах «ИЛИ» на элементах «ИЛИ-НЕ» 2014 X 1 2 3 CD Y 0 1 Условное обозначение шифратора 4/2 на схемах 38

Шифратор Выделяют: приоритетные (преобразование максимального десятичного номера активного входа в двоичный эквивалент этого номера) и неприоритетные (преобразование десятичного номера активного входа в двоичный эквивалент этого номера). Неприоритетный - преобразователь из унитарного кода (прямого или инверсного) в натуральный двоичный код (n-разрядный двоичный код). Для шифратора при m=4 (шифратор 4/2) X 1 X 2 X 3 1 1 Y 0 X 2 1 X 0 Y 1 1 X 1 Y 0 Y 1 Реализация шифратора 4/2 на элементах «ИЛИ» на элементах «ИЛИ-НЕ» 2014 X 1 2 3 CD Y 0 1 Условное обозначение шифратора 4/2 на схемах 38

Шифратор Применение шифраторов: 1. сжатие информации (число разрядов натурального двоичного кода меньше числа разрядов унитарного кода); 2. ввод данных в ЦК с клавиатуры: 1. ввод числовых данных может выполняться в унитарном коде нажатием одной из десяти клавиш, а ввод данных в процессор производится в двоичном коде; 2. при нажатии клавиши на одном из входов шифратора появляется логическая 1 и на выходах устанавливается двоичный код, соответствующий символу данной клавиши.

Шифратор Применение шифраторов: 1. сжатие информации (число разрядов натурального двоичного кода меньше числа разрядов унитарного кода); 2. ввод данных в ЦК с клавиатуры: 1. ввод числовых данных может выполняться в унитарном коде нажатием одной из десяти клавиш, а ввод данных в процессор производится в двоичном коде; 2. при нажатии клавиши на одном из входов шифратора появляется логическая 1 и на выходах устанавливается двоичный код, соответствующий символу данной клавиши.

Приоритетный шифратор На вход приоритетного шифратора может быть подан произвольный двоичный код. ПДК может содержать произвольное число единиц (или нулей для инверсного), расположенных в произвольном порядке. На выходе приоритетного шифратора формируется натуральный двоичный код, определяющий номер позиции приоритетной единицы, т. е. единицы, стоящей в самом старшем разряде. Приоритетные шифраторы могут использоваться в качестве обычных шифраторов, поскольку унитарный код является частным случаем произвольного. Применяются для преобразователя двоичных чисел из формата с фиксированной запятой в формат с плавающей запятой (порядок определяется по положению старшей единицы), и в аналогоцифровых преобразователях параллельного типа.

Приоритетный шифратор На вход приоритетного шифратора может быть подан произвольный двоичный код. ПДК может содержать произвольное число единиц (или нулей для инверсного), расположенных в произвольном порядке. На выходе приоритетного шифратора формируется натуральный двоичный код, определяющий номер позиции приоритетной единицы, т. е. единицы, стоящей в самом старшем разряде. Приоритетные шифраторы могут использоваться в качестве обычных шифраторов, поскольку унитарный код является частным случаем произвольного. Применяются для преобразователя двоичных чисел из формата с фиксированной запятой в формат с плавающей запятой (порядок определяется по положению старшей единицы), и в аналогоцифровых преобразователях параллельного типа.

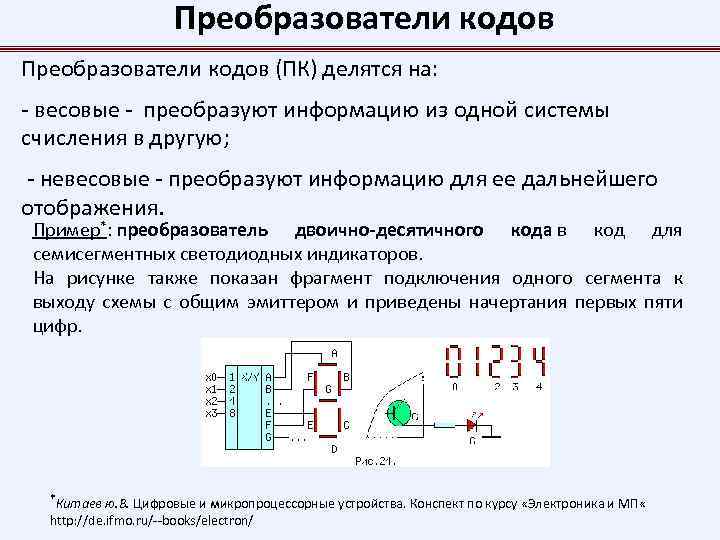

Преобразователи кодов (ПК) делятся на: - весовые - преобразуют информацию из одной системы счисления в другую; - невесовые - преобразуют информацию для ее дальнейшего отображения. Пример*: преобразователь двоично-десятичного кода в код для семисегментных светодиодных индикаторов. На рисунке также показан фрагмент подключения одного сегмента к выходу схемы с общим эмиттером и приведены начертания первых пяти цифр. *Китаев ю. В. Цифровые и микропроцессорные устройства. Конспект по курсу «Электроника и МП « http: //de. ifmo. ru/--books/electron/

Преобразователи кодов (ПК) делятся на: - весовые - преобразуют информацию из одной системы счисления в другую; - невесовые - преобразуют информацию для ее дальнейшего отображения. Пример*: преобразователь двоично-десятичного кода в код для семисегментных светодиодных индикаторов. На рисунке также показан фрагмент подключения одного сегмента к выходу схемы с общим эмиттером и приведены начертания первых пяти цифр. *Китаев ю. В. Цифровые и микропроцессорные устройства. Конспект по курсу «Электроника и МП « http: //de. ifmo. ru/--books/electron/

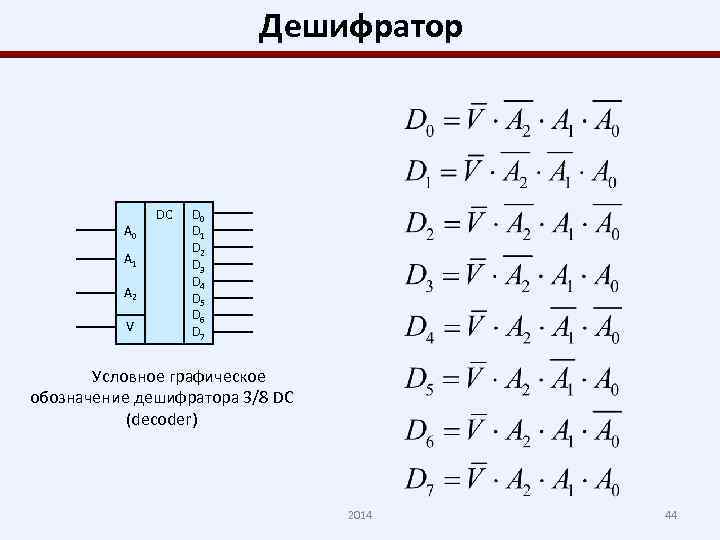

Дешифратор комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду, или преобразователь натурального двоичного кода в унитарный. (Элемент, функционально обратный шифратору). Используются в мультиплексорах, демультиплексорах и иных коммутаторах, в том числе для управления индикаторами, принтерами и выбора ячеек памяти в запоминающих устройствах при записи и считывании информации. Полный дешифратор: количество выходов m = 2 n, где n - число входов. В неполном дешифраторе m < 2 n. 2014 42

Дешифратор комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду, или преобразователь натурального двоичного кода в унитарный. (Элемент, функционально обратный шифратору). Используются в мультиплексорах, демультиплексорах и иных коммутаторах, в том числе для управления индикаторами, принтерами и выбора ячеек памяти в запоминающих устройствах при записи и считывании информации. Полный дешифратор: количество выходов m = 2 n, где n - число входов. В неполном дешифраторе m < 2 n. 2014 42

Дешифратор Полный дешифратор Пусть дешифратор имеет N входов, на них подано двоичное слово x N 1 x. N-2. . . x 0, тогда на выходе будем иметь такой код разрядности меньшей или равной 2 N, что разряд, номер которого равен входному слову, принимает значение единицы, все остальные разряды равны нулю. Очевидно, что максимально возможная разрядность выходного слова равна 2 N. Часто дешифраторы дополняются входом разрешения работы E (enable). Если на этот вход поступает единица, то дешифратор функционирует, в ином случае на выходе дешифратора вырабатывается логический ноль вне зависимости от входных сигналов. Вариант: Вход V (veto – запрет) дешифратора позволяет не только запрещать работу устройства, но и наращивать его разрядность. Когда на этот вход подается логическая единица, независимо от состояния информационных входов на выходе образуются нули. Когда же на вход V дешифратора подается логический нуль, на выходе, номер которого соответствует двоичному коду адреса, обозначенного на входе, образуется логическая единица, на других выходах формируется логический нуль. Существуют дешифраторы с инверсными выходами, у такого дешифратора выбранный разряд показан нулем. 2014 43

Дешифратор Полный дешифратор Пусть дешифратор имеет N входов, на них подано двоичное слово x N 1 x. N-2. . . x 0, тогда на выходе будем иметь такой код разрядности меньшей или равной 2 N, что разряд, номер которого равен входному слову, принимает значение единицы, все остальные разряды равны нулю. Очевидно, что максимально возможная разрядность выходного слова равна 2 N. Часто дешифраторы дополняются входом разрешения работы E (enable). Если на этот вход поступает единица, то дешифратор функционирует, в ином случае на выходе дешифратора вырабатывается логический ноль вне зависимости от входных сигналов. Вариант: Вход V (veto – запрет) дешифратора позволяет не только запрещать работу устройства, но и наращивать его разрядность. Когда на этот вход подается логическая единица, независимо от состояния информационных входов на выходе образуются нули. Когда же на вход V дешифратора подается логический нуль, на выходе, номер которого соответствует двоичному коду адреса, обозначенного на входе, образуется логическая единица, на других выходах формируется логический нуль. Существуют дешифраторы с инверсными выходами, у такого дешифратора выбранный разряд показан нулем. 2014 43

Дешифратор A 0 A 1 A 2 V DC D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Условное графическое обозначение дешифратора 3/8 DC (decoder) 2014 44

Дешифратор A 0 A 1 A 2 V DC D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Условное графическое обозначение дешифратора 3/8 DC (decoder) 2014 44

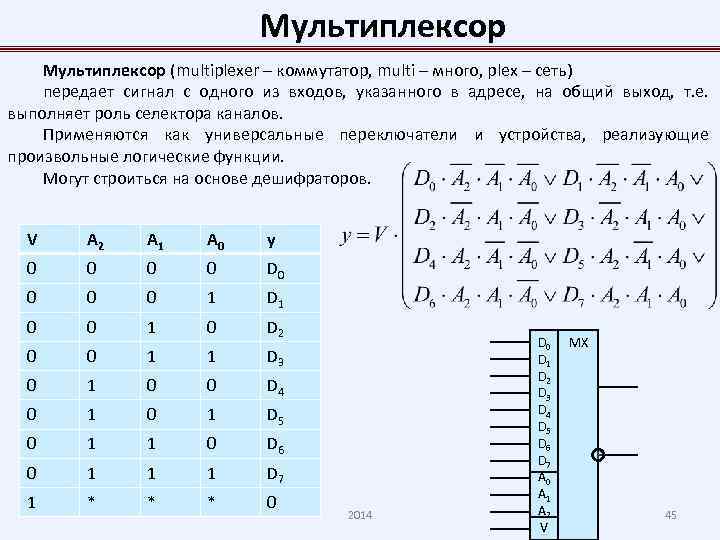

Мультиплексор (multiplexer – коммутатор, multi – много, plex – сеть) передает сигнал с одного из входов, указанного в адресе, на общий выход, т. е. выполняет роль селектора каналов. Применяются как универсальные переключатели и устройства, реализующие произвольные логические функции. Могут строиться на основе дешифраторов. V A 2 A 1 A 0 y 0 0 D 0 0 1 D 1 0 0 1 0 D 2 0 0 1 1 D 3 0 1 0 0 D 4 0 1 D 5 0 1 1 0 D 6 0 1 1 1 D 7 1 * * * 0 2014 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 A 0 A 1 A 2 V MX 45

Мультиплексор (multiplexer – коммутатор, multi – много, plex – сеть) передает сигнал с одного из входов, указанного в адресе, на общий выход, т. е. выполняет роль селектора каналов. Применяются как универсальные переключатели и устройства, реализующие произвольные логические функции. Могут строиться на основе дешифраторов. V A 2 A 1 A 0 y 0 0 D 0 0 1 D 1 0 0 1 0 D 2 0 0 1 1 D 3 0 1 0 0 D 4 0 1 D 5 0 1 1 0 D 6 0 1 1 1 D 7 1 * * * 0 2014 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 A 0 A 1 A 2 V MX 45

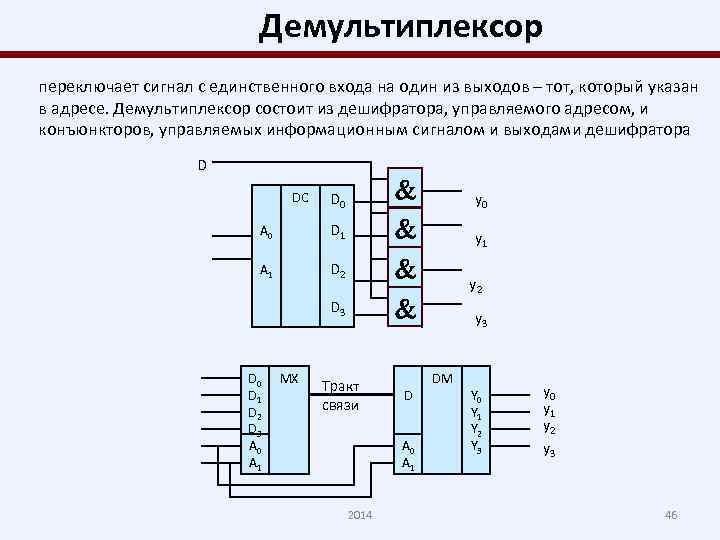

Демультиплексор переключает сигнал с единственного входа на один из выходов – тот, который указан в адресе. Демультиплексор состоит из дешифратора, управляемого адресом, и конъюнкторов, управляемых информационным сигналом и выходами дешифратора D DC D 0 A 0 D 1 A 1 D 2 D 3 D 0 D 1 D 2 D 3 A 0 A 1 MX Тракт связи D A 0 A 1 2014 y 0 y 1 y 2 y 3 DM Y 0 Y 1 Y 2 Y 3 y 0 y 1 y 2 y 3 46

Демультиплексор переключает сигнал с единственного входа на один из выходов – тот, который указан в адресе. Демультиплексор состоит из дешифратора, управляемого адресом, и конъюнкторов, управляемых информационным сигналом и выходами дешифратора D DC D 0 A 0 D 1 A 1 D 2 D 3 D 0 D 1 D 2 D 3 A 0 A 1 MX Тракт связи D A 0 A 1 2014 y 0 y 1 y 2 y 3 DM Y 0 Y 1 Y 2 Y 3 y 0 y 1 y 2 y 3 46

Литература • Шауцкова Л. З. Информатика. http: //book. kbsu. ru • Угрюмов Е. П. Цифровая схемотехника. СПб, БХВ-Петербург, 2004. • Шило В. Л. Популярные цифровые микросхемы. М, Радио и связь, 1987. • Дж. Ф. Уэкерли Проектирование цифровых устройств. М, Постмаркет, 2002. 2014 47

Литература • Шауцкова Л. З. Информатика. http: //book. kbsu. ru • Угрюмов Е. П. Цифровая схемотехника. СПб, БХВ-Петербург, 2004. • Шило В. Л. Популярные цифровые микросхемы. М, Радио и связь, 1987. • Дж. Ф. Уэкерли Проектирование цифровых устройств. М, Постмаркет, 2002. 2014 47