Лекция 3. Цифровой логический уровень. Часть I.ppt

- Количество слайдов: 22

Архитектура вычислительных систем Цифровой логический уровень

Архитектура вычислительных систем Цифровой логический уровень

Часть I Вентили

Часть I Вентили

Транзистор Цифровой логический уровень представляет собой сложную сеть взаимосвязанных электронных компонентов, по которой циркулируют двоичные сигналы, задаваемые напряжениями в цепях. Элементарная схема, вычисляющая некоторую булеву функцию, называется вентилем – в его основе лежит транзистор. Коллектор База Эмиттер

Транзистор Цифровой логический уровень представляет собой сложную сеть взаимосвязанных электронных компонентов, по которой циркулируют двоичные сигналы, задаваемые напряжениями в цепях. Элементарная схема, вычисляющая некоторую булеву функцию, называется вентилем – в его основе лежит транзистор. Коллектор База Эмиттер

Транзисторный инвертор Сам по себе транзистор вентилем не является. Для того чтобы создать простейший вентиль – инвертор – необходимо добавить к транзистору питание, заземляющий выход и резистор. +Vcc питание Поведение вентиля: если Vin = 0, то Vout > 0 если Vin > 0, то Vout = 0 Vout выход Vin вход данный вентиль реализует булеву функцию НЕ на схемах обозначается как заземление

Транзисторный инвертор Сам по себе транзистор вентилем не является. Для того чтобы создать простейший вентиль – инвертор – необходимо добавить к транзистору питание, заземляющий выход и резистор. +Vcc питание Поведение вентиля: если Vin = 0, то Vout > 0 если Vin > 0, то Vout = 0 Vout выход Vin вход данный вентиль реализует булеву функцию НЕ на схемах обозначается как заземление

Простейшие булевы вентили +Vcc Одной функции НЕ недостаточно, чтобы выражать любые булевы функции. Поэтому необходимы еще вентили. Поведение вентиля: Vout если V 1 = 0 И V 2 = 0, то Vout > 0 если V 1 > 0 И V 2 = 0, то Vout > 0 если V 1 = 0 И V 2 > 0, то Vout > 0 V 1 если V 1 > 0 И V 2 > 0, то Vout = 0 данный вентиль реализует булеву функцию НЕ-И V 2 на схемах обозначается как

Простейшие булевы вентили +Vcc Одной функции НЕ недостаточно, чтобы выражать любые булевы функции. Поэтому необходимы еще вентили. Поведение вентиля: Vout если V 1 = 0 И V 2 = 0, то Vout > 0 если V 1 > 0 И V 2 = 0, то Vout > 0 если V 1 = 0 И V 2 > 0, то Vout > 0 V 1 если V 1 > 0 И V 2 > 0, то Vout = 0 данный вентиль реализует булеву функцию НЕ-И V 2 на схемах обозначается как

Простейшие булевы вентили Построим еще один простейший вентиль. Поведение вентиля: если V 1 = 0 И V 2 = 0, то Vout > 0 +Vcc если V 1 > 0 И V 2 = 0, то Vout = 0 если V 1 = 0 И V 2 > 0, то Vout = 0 если V 1 > 0 И V 2 > 0, то Vout = 0 Vout V 1 V 2 данный вентиль реализует булеву функцию НЕ-ИЛИ на схемах обозначается как

Простейшие булевы вентили Построим еще один простейший вентиль. Поведение вентиля: если V 1 = 0 И V 2 = 0, то Vout > 0 +Vcc если V 1 > 0 И V 2 = 0, то Vout = 0 если V 1 = 0 И V 2 > 0, то Vout = 0 если V 1 > 0 И V 2 > 0, то Vout = 0 Vout V 1 V 2 данный вентиль реализует булеву функцию НЕ-ИЛИ на схемах обозначается как

Простейшие булевы вентили НЕ НЕ-И И НЕ-ИЛИ

Простейшие булевы вентили НЕ НЕ-И И НЕ-ИЛИ

Как выразить любую булеву формулу с помощью цифровой логической микросхемы? A B C 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 A B C 0 0 A B C M 1 Пусть мы имеем некоторую булеву функцию от трех аргументов, например функцию большинства. A A ABC B M B ABC C C ABC

Как выразить любую булеву формулу с помощью цифровой логической микросхемы? A B C 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 A B C 0 0 A B C M 1 Пусть мы имеем некоторую булеву функцию от трех аргументов, например функцию большинства. A A ABC B M B ABC C C ABC

Часть II Комбинационные схемы

Часть II Комбинационные схемы

Мультиплексор – схема с 2 n входами, одним выходом и n линиями управления, которые выбирают один из входов и соединяют его с выходом. D 0 D 1 F D 2 D 3 A B

Мультиплексор – схема с 2 n входами, одним выходом и n линиями управления, которые выбирают один из входов и соединяют его с выходом. D 0 D 1 F D 2 D 3 A B

Декодер – схема с n входами и 2 n выходами. Значение, подаваемое на входы данной схеме используется для выбора одной из выходных линий, чтобы послать по ней сигнал. A B C D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 1 A B C D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7

Декодер – схема с n входами и 2 n выходами. Значение, подаваемое на входы данной схеме используется для выбора одной из выходных линий, чтобы послать по ней сигнал. A B C D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 1 A B C D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7

Компаратор сравнивает два слова, которые поступают на вход. A 0 B 0 A 1 B 1 A=B A 2 B 2 A 3 B 3 вентиль исключающее ИЛИ

Компаратор сравнивает два слова, которые поступают на вход. A 0 B 0 A 1 B 1 A=B A 2 B 2 A 3 B 3 вентиль исключающее ИЛИ

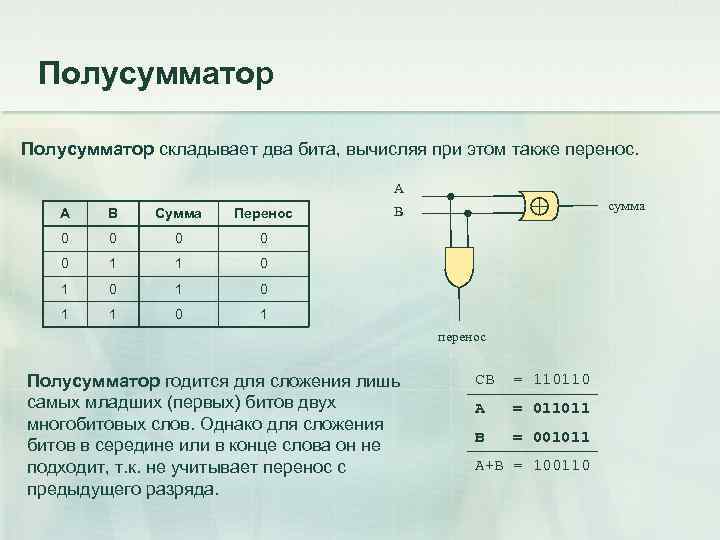

Полусумматор складывает два бита, вычисляя при этом также перенос. A A B Сумма Перенос 0 0 0 1 1 0 1 0 1 1 0 сумма B 1 перенос Полусумматор годится для сложения лишь самых младших (первых) битов двух многобитовых слов. Однако для сложения битов в середине или в конце слова он не подходит, т. к. не учитывает перенос с предыдущего разряда. CB = 110110 A = 011011 B = 001011 A+B = 100110

Полусумматор складывает два бита, вычисляя при этом также перенос. A A B Сумма Перенос 0 0 0 1 1 0 1 0 1 1 0 сумма B 1 перенос Полусумматор годится для сложения лишь самых младших (первых) битов двух многобитовых слов. Однако для сложения битов в середине или в конце слова он не подходит, т. к. не учитывает перенос с предыдущего разряда. CB = 110110 A = 011011 B = 001011 A+B = 100110

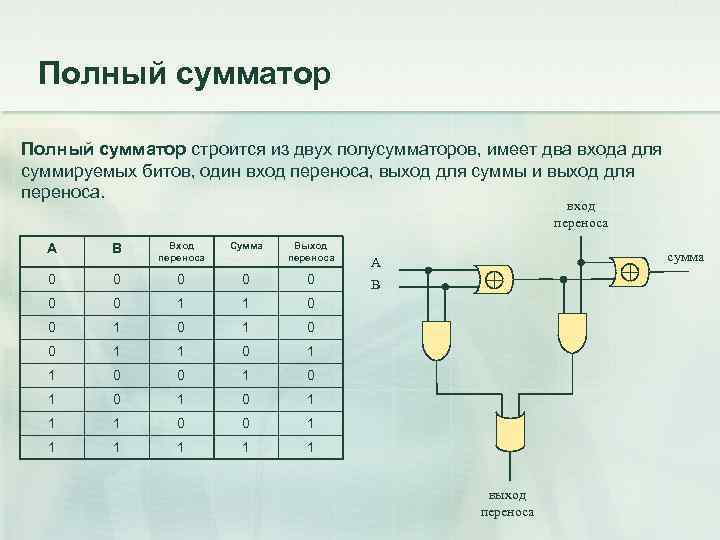

Полный сумматор строится из двух полусумматоров, имеет два входа для суммируемых битов, один вход переноса, выход для суммы и выход для переноса. вход переноса A B Вход переноса Сумма Выход переноса 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1 сумма A B выход переноса

Полный сумматор строится из двух полусумматоров, имеет два входа для суммируемых битов, один вход переноса, выход для суммы и выход для переноса. вход переноса A B Вход переноса Сумма Выход переноса 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1 сумма A B выход переноса

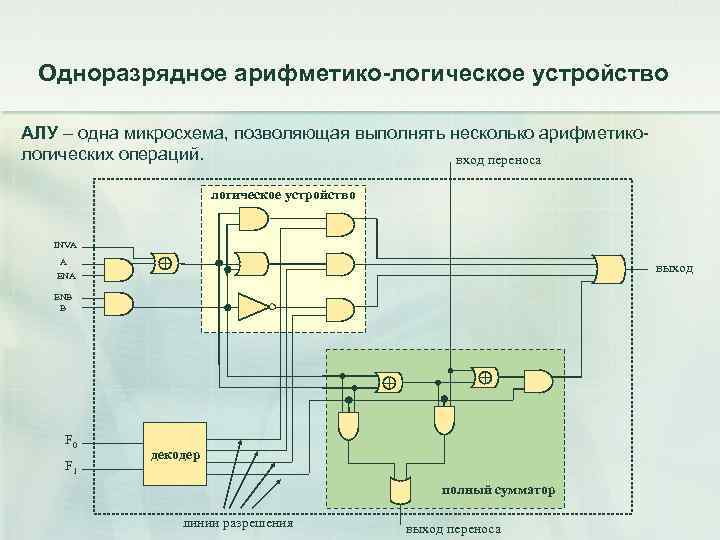

Одноразрядное арифметико-логическое устройство АЛУ – одна микросхема, позволяющая выполнять несколько арифметикологических операций. вход переноса логическое устройство INVA A ENA выход ENB B F 0 F 1 декодер полный сумматор линии разрешения выход переноса

Одноразрядное арифметико-логическое устройство АЛУ – одна микросхема, позволяющая выполнять несколько арифметикологических операций. вход переноса логическое устройство INVA A ENA выход ENB B F 0 F 1 декодер полный сумматор линии разрешения выход переноса

8 -ми битное АЛУ 8 -битное АЛУ можно построить из восьми одноразрядных микропроцессорных секций. F 0 F 1 A 7 B 7 A 6 B 6 A 5 B 5 A 4 B 4 A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 1 -битное АЛУ 1 -битное АЛУ R 7 R 6 R 5 R 4 R 3 R 2 R 1 R 0 вход переноса выход переноса

8 -ми битное АЛУ 8 -битное АЛУ можно построить из восьми одноразрядных микропроцессорных секций. F 0 F 1 A 7 B 7 A 6 B 6 A 5 B 5 A 4 B 4 A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 1 -битное АЛУ 1 -битное АЛУ R 7 R 6 R 5 R 4 R 3 R 2 R 1 R 0 вход переноса выход переноса

Часть III Память

Часть III Память

Защелка Простейшая микросхема, используемая для хранения одного бита памяти, называется защелкой. S =0 R =0 Q =0 =1 Данная схема называется SR-защелкой. Вход S (setting) используется для сохранения бита 1 в данной ячейке памяти, вход R (resetting) – для сброса ячейки памяти в нулевое значение.

Защелка Простейшая микросхема, используемая для хранения одного бита памяти, называется защелкой. S =0 R =0 Q =0 =1 Данная схема называется SR-защелкой. Вход S (setting) используется для сохранения бита 1 в данной ячейке памяти, вход R (resetting) – для сброса ячейки памяти в нулевое значение.

Синхронная SR-защелка меняет свое состояние в зависимости от значений входов S и R только тогда, когда на линию синхронизации подается сигнал. S линия синхронизации Q Q R

Синхронная SR-защелка меняет свое состояние в зависимости от значений входов S и R только тогда, когда на линию синхронизации подается сигнал. S линия синхронизации Q Q R

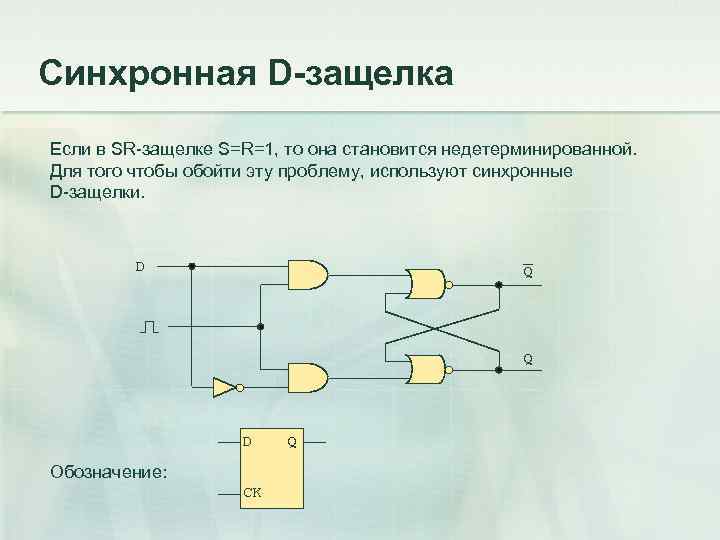

Синхронная D-защелка Если в SR-защелке S=R=1, то она становится недетерминированной. Для того чтобы обойти эту проблему, используют синхронные D-защелки. D Q Q D Обозначение: CK Q

Синхронная D-защелка Если в SR-защелке S=R=1, то она становится недетерминированной. Для того чтобы обойти эту проблему, используют синхронные D-защелки. D Q Q D Обозначение: CK Q

8 -битная схема памяти Vcc 20 19 D 18 Q D CK D 16 15 Q Q D 3 4 12 Q Q D 6 Q 7 Q CK D CK 5 11 D CK CK 2 13 14 D CK CK 1 17 Q CK 8 9 10 GND

8 -битная схема памяти Vcc 20 19 D 18 Q D CK D 16 15 Q Q D 3 4 12 Q Q D 6 Q 7 Q CK D CK 5 11 D CK CK 2 13 14 D CK CK 1 17 Q CK 8 9 10 GND

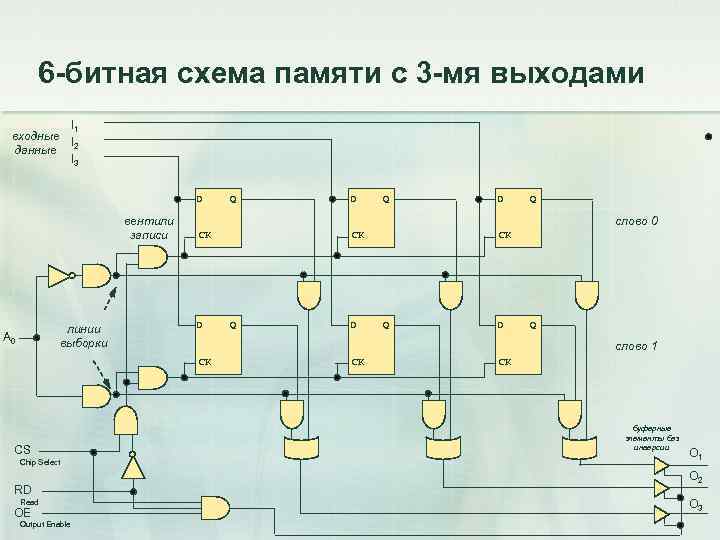

6 -битная схема памяти c 3 -мя выходами I 1 входные I данные 2 I 3 D вентили записи линии выборки A 0 Chip Select RD Read OE Output Enable D Q слово 0 CK D CK Q D Q слово 1 CK CS Q CK CK буферные элементы без инверсии O 1 O 2 O 3

6 -битная схема памяти c 3 -мя выходами I 1 входные I данные 2 I 3 D вентили записи линии выборки A 0 Chip Select RD Read OE Output Enable D Q слово 0 CK D CK Q D Q слово 1 CK CS Q CK CK буферные элементы без инверсии O 1 O 2 O 3