Архитектура вычислительных систем 03. Организация

04 - Организация памяти.ppt

- Количество слайдов: 33

Архитектура вычислительных систем 03. Организация памяти Кафедра ИИТ. Мокрушин А. А.

Архитектура вычислительных систем 03. Организация памяти Кафедра ИИТ. Мокрушин А. А.

Организация памяти Иерархия памяти Оперативная память Виртуальная память Кэш-память Кафедра ИИТ. Мокрушин А. А. 2

Организация памяти Иерархия памяти Оперативная память Виртуальная память Кэш-память Кафедра ИИТ. Мокрушин А. А. 2

01. Иерархия памяти Кафедра ИИТ. Мокрушин А. А. 3

01. Иерархия памяти Кафедра ИИТ. Мокрушин А. А. 3

01. Иерархия памяти ПЗУ ROM PROM EEPROM Энергозависимая память RAM SRAM DRAM SDRAM … Кафедра ИИТ. Мокрушин А. А. 4

01. Иерархия памяти ПЗУ ROM PROM EEPROM Энергозависимая память RAM SRAM DRAM SDRAM … Кафедра ИИТ. Мокрушин А. А. 4

01. ПЗУ Постоянное запоминающее устройство (ПЗУ, англ. ROM — Read- Only Memory) — энергонезависимая память, используется для хранения массива неизменяемых данных. Кафедра ИИТ. Мокрушин А. А. 5

01. ПЗУ Постоянное запоминающее устройство (ПЗУ, англ. ROM — Read- Only Memory) — энергонезависимая память, используется для хранения массива неизменяемых данных. Кафедра ИИТ. Мокрушин А. А. 5

01. ПЗУ По типу исполнения: Массив данных совмещён с устройством выборки (считывающим устройством), в этом случае массив данных называется прошивка: микросхема ПЗУ; Один из внутренних ресурсов однокристальной микро. ЭВМ (микроконтроллера), как правило Flash. ROM. Кафедра ИИТ. Мокрушин А. А. 6

01. ПЗУ По типу исполнения: Массив данных совмещён с устройством выборки (считывающим устройством), в этом случае массив данных называется прошивка: микросхема ПЗУ; Один из внутренних ресурсов однокристальной микро. ЭВМ (микроконтроллера), как правило Flash. ROM. Кафедра ИИТ. Мокрушин А. А. 6

01. Микросхема ПЗУ Микросхема- электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле (или плёнке) и помещённая в неразборный корпус. Кафедра ИИТ. Мокрушин А. А. 7

01. Микросхема ПЗУ Микросхема- электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле (или плёнке) и помещённая в неразборный корпус. Кафедра ИИТ. Мокрушин А. А. 7

01. Микроконтроллер (MCU) — микросхема, предназначенная для управления электронными устройствами. Типичный микроконтроллер сочетает в себе функции процессора и периферийных устройств, может содержать ОЗУ и ПЗУ. По сути, это однокристальный компьютер, способный выполнять простые задачи. Микроконтроллер 1993 года с УФ стиранием памяти 62 E 40 европейской фирмы STMicroelectronics Кафедра ИИТ. Мокрушин А. А. 8

01. Микроконтроллер (MCU) — микросхема, предназначенная для управления электронными устройствами. Типичный микроконтроллер сочетает в себе функции процессора и периферийных устройств, может содержать ОЗУ и ПЗУ. По сути, это однокристальный компьютер, способный выполнять простые задачи. Микроконтроллер 1993 года с УФ стиранием памяти 62 E 40 европейской фирмы STMicroelectronics Кафедра ИИТ. Мокрушин А. А. 8

01. ПЗУ PROM - (Programmable ROM) EPROM - (Erasable Programmable ROM) EEPROM - (Electrically Erasable Programmable ROM) Кафедра ИИТ. Мокрушин А. А. 9

01. ПЗУ PROM - (Programmable ROM) EPROM - (Erasable Programmable ROM) EEPROM - (Electrically Erasable Programmable ROM) Кафедра ИИТ. Мокрушин А. А. 9

02. Оперативная память Кафедра ИИТ. Мокрушин А. А. 10

02. Оперативная память Кафедра ИИТ. Мокрушин А. А. 10

02. Оперативная память Оперативная память представляет собой множество ячеек. Каждая ячейка имеет свой уникальный адрес. Нумерация ячеек начинается с нуля. Каждая ячейка памяти имеет объем 1 байт. Максимальный объем адресуемой памяти равен произведению количества ячеек N на 1 байт. Для процессоров Pentium 4 (разрядность шины адреса = 36 бит) максимальный объем адресуемой памяти равен: N × 1 байт = 2 I × 1 байт = 236 × 1 байт = 68 719 476 736 байт = = 67 108 864 Кбайт = 65 536 Мбайт = 64 Гбайт Кафедра ИИТ. Мокрушин А. А. 11

02. Оперативная память Оперативная память представляет собой множество ячеек. Каждая ячейка имеет свой уникальный адрес. Нумерация ячеек начинается с нуля. Каждая ячейка памяти имеет объем 1 байт. Максимальный объем адресуемой памяти равен произведению количества ячеек N на 1 байт. Для процессоров Pentium 4 (разрядность шины адреса = 36 бит) максимальный объем адресуемой памяти равен: N × 1 байт = 2 I × 1 байт = 236 × 1 байт = 68 719 476 736 байт = = 67 108 864 Кбайт = 65 536 Мбайт = 64 Гбайт Кафедра ИИТ. Мокрушин А. А. 11

02. Оперативная память Объем памяти Ячейки Десятичный Шестнадцатеричный адрес ячейки 64 Гбайт 1010 68 719 476 735 FFFFF … … 4 Гбайт 1010 4 294 967 295 FFFF … 1010 Кафедра ИИТ. Мокрушин А. А. 12

02. Оперативная память Объем памяти Ячейки Десятичный Шестнадцатеричный адрес ячейки 64 Гбайт 1010 68 719 476 735 FFFFF … … 4 Гбайт 1010 4 294 967 295 FFFF … 1010 Кафедра ИИТ. Мокрушин А. А. 12

02. Оперативная память Технологии изготовления: SRAM (Static RAM) DRAM (Dynamic RAM) SDRAM (Synchronous DRAM) DDR SDRAM (Double Data Rate) Rambus Кафедра ИИТ. Мокрушин А. А. 13

02. Оперативная память Технологии изготовления: SRAM (Static RAM) DRAM (Dynamic RAM) SDRAM (Synchronous DRAM) DDR SDRAM (Double Data Rate) Rambus Кафедра ИИТ. Мокрушин А. А. 13

03. Виртуальная память Программа не ограничена объемом физической памяти. Упрощается разработка программ, поскольку можно задействовать большие виртуальные пространства, не заботясь о размере используемой памяти. можно разместить в памяти больше программ, что увеличивает загрузку процессора и пропускную способность системы. Объем ввода-вывода для выгрузки части программы на диск может быть меньше, чем в варианте классического свопинга, в итоге каждая программа будет работать быстрее. Кафедра ИИТ. Мокрушин А. А. 14

03. Виртуальная память Программа не ограничена объемом физической памяти. Упрощается разработка программ, поскольку можно задействовать большие виртуальные пространства, не заботясь о размере используемой памяти. можно разместить в памяти больше программ, что увеличивает загрузку процессора и пропускную способность системы. Объем ввода-вывода для выгрузки части программы на диск может быть меньше, чем в варианте классического свопинга, в итоге каждая программа будет работать быстрее. Кафедра ИИТ. Мокрушин А. А. 14

03. Виртуальная память Страничная виртуальная память. Сегментно-страничная виртуальная память. Кафедра ИИТ. Мокрушин А. А. 15

03. Виртуальная память Страничная виртуальная память. Сегментно-страничная виртуальная память. Кафедра ИИТ. Мокрушин А. А. 15

03. Страничная память Кафедра ИИТ. Мокрушин А. А. 16

03. Страничная память Кафедра ИИТ. Мокрушин А. А. 16

03. Страничная память Кафедра ИИТ. Мокрушин А. А. 17

03. Страничная память Кафедра ИИТ. Мокрушин А. А. 17

03. Сегментная память Сегменты, в отличие от страниц, могут иметь переменный размер. Аппаратная поддержка сегментов распространена мало (главным образом на процессорах Intel). Кафедра ИИТ. Мокрушин А. А. 18

03. Сегментная память Сегменты, в отличие от страниц, могут иметь переменный размер. Аппаратная поддержка сегментов распространена мало (главным образом на процессорах Intel). Кафедра ИИТ. Мокрушин А. А. 18

03. Сегментная память Таблица сегментов: базовый физический адрес сегмента в оперативной памяти; размер сегмента; правила доступа к сегменту; признаки модификации, присутствия и обращения к данному сегменту, а также некоторая другая информация. Кафедра ИИТ. Мокрушин А. А. 19

03. Сегментная память Таблица сегментов: базовый физический адрес сегмента в оперативной памяти; размер сегмента; правила доступа к сегменту; признаки модификации, присутствия и обращения к данному сегменту, а также некоторая другая информация. Кафедра ИИТ. Мокрушин А. А. 19

03. Сегментная память Кафедра ИИТ. Мокрушин А. А. 20

03. Сегментная память Кафедра ИИТ. Мокрушин А. А. 20

03. Сегментная память Кафедра ИИТ. Мокрушин А. А. 21

03. Сегментная память Кафедра ИИТ. Мокрушин А. А. 21

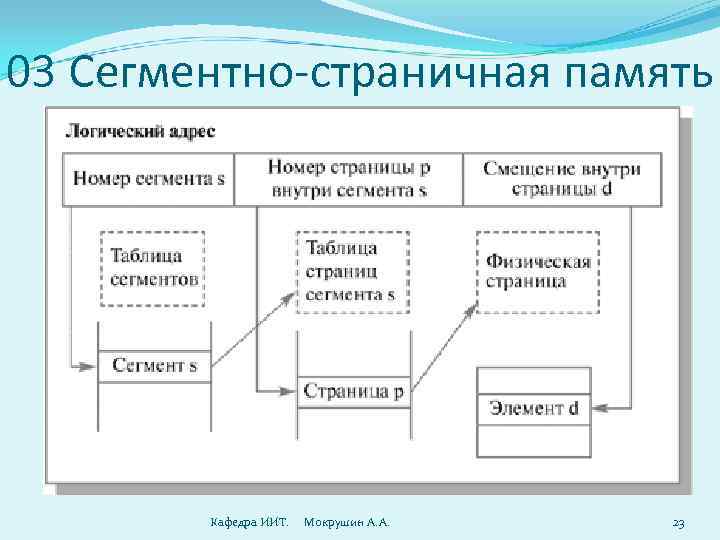

03 Сегментно-страничная память Перемещение данных между памятью и диском осуществляется не сегментами, а страницами. Для каждого процесса операционная система создает отдельную таблицу сегментов, в которой содержатся описатели (дескрипторы) всех сегментов процесса. Логический адрес состоит из трех полей: номера сегмента логической памяти, номера страницы внутри сегмента и смещения внутри страницы. Кафедра ИИТ. Мокрушин А. А. 22

03 Сегментно-страничная память Перемещение данных между памятью и диском осуществляется не сегментами, а страницами. Для каждого процесса операционная система создает отдельную таблицу сегментов, в которой содержатся описатели (дескрипторы) всех сегментов процесса. Логический адрес состоит из трех полей: номера сегмента логической памяти, номера страницы внутри сегмента и смещения внутри страницы. Кафедра ИИТ. Мокрушин А. А. 22

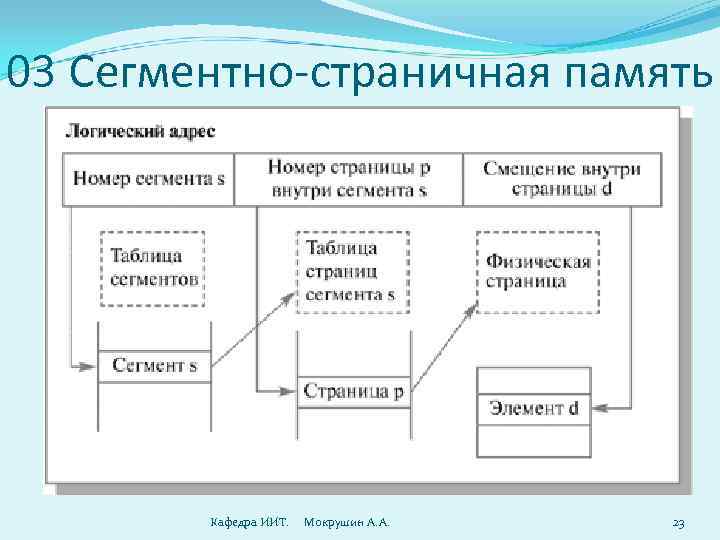

03 Сегментно-страничная память Кафедра ИИТ. Мокрушин А. А. 23

03 Сегментно-страничная память Кафедра ИИТ. Мокрушин А. А. 23

04. Кэш-память способ совместного функционирования двух типов запоминающих устройств, отличающихся временем доступа и стоимостью хранения данных, который за счет динамического копирования в «быстрое» ЗУ наиболее часто используемой информации из «медленного» ЗУ позволяет, с одной стороны, уменьшить среднее время доступа к данным, а с другой стороны, экономить более дорогую быстродействующую память. Кафедра ИИТ. Мокрушин А. А. 24

04. Кэш-память способ совместного функционирования двух типов запоминающих устройств, отличающихся временем доступа и стоимостью хранения данных, который за счет динамического копирования в «быстрое» ЗУ наиболее часто используемой информации из «медленного» ЗУ позволяет, с одной стороны, уменьшить среднее время доступа к данным, а с другой стороны, экономить более дорогую быстродействующую память. Кафедра ИИТ. Мокрушин А. А. 24

04. Алгоритм Кэш-памяти Кафедра ИИТ. Мокрушин А. А. 25

04. Алгоритм Кэш-памяти Кафедра ИИТ. Мокрушин А. А. 25

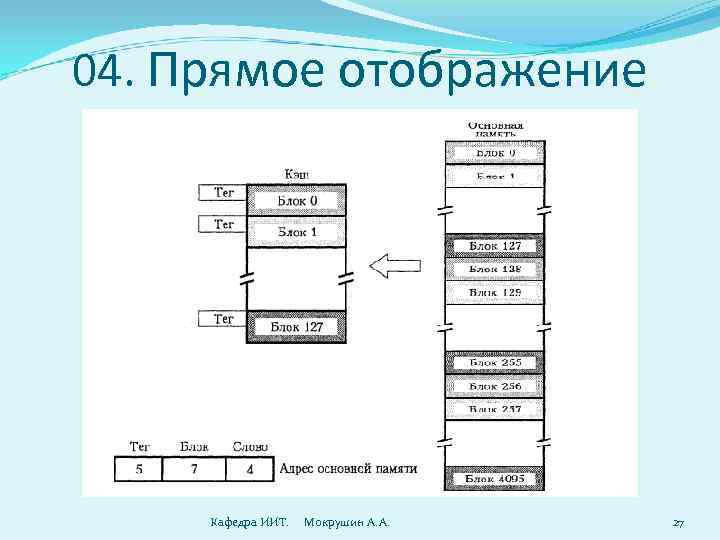

04. Виды Кэш-памяти Прямое отображение Ассоциативный кэш Множественно- ассоциативный кэш Кафедра ИИТ. Мокрушин А. А. 26

04. Виды Кэш-памяти Прямое отображение Ассоциативный кэш Множественно- ассоциативный кэш Кафедра ИИТ. Мокрушин А. А. 26

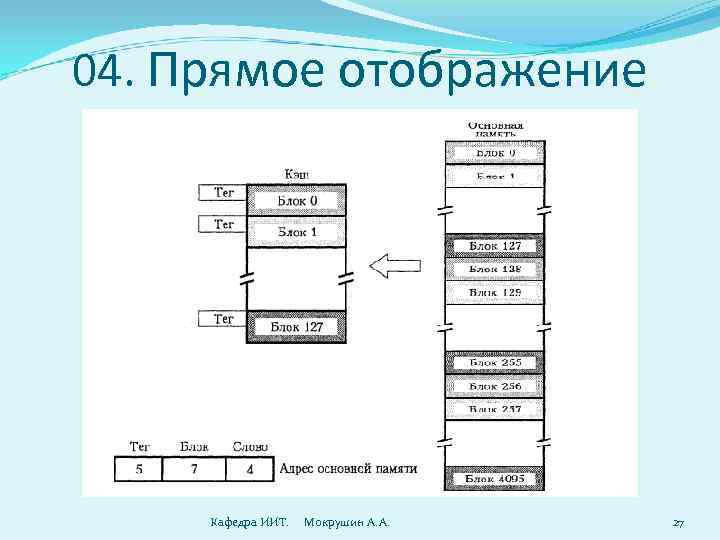

04. Прямое отображение Кафедра ИИТ. Мокрушин А. А. 27

04. Прямое отображение Кафедра ИИТ. Мокрушин А. А. 27

04. Ассоциативный кэш Кафедра ИИТ. Мокрушин А. А. 28

04. Ассоциативный кэш Кафедра ИИТ. Мокрушин А. А. 28

04. Множественно-ассоциативный кэш Кафедра ИИТ. Мокрушин А. А. 29

04. Множественно-ассоциативный кэш Кафедра ИИТ. Мокрушин А. А. 29

04. Принципы работы Временная локальность. Если произошло обращение по некоторому адресу, то следующее обращение по тому же адресу с большой вероятностью произойдет в ближайшее время. Пространственная локальность. Если произошло обращение по некоторому адресу, то с высокой степенью вероятности в ближайшее время произойдет обращение к соседним адресам. Кафедра ИИТ. Мокрушин А. А. 30

04. Принципы работы Временная локальность. Если произошло обращение по некоторому адресу, то следующее обращение по тому же адресу с большой вероятностью произойдет в ближайшее время. Пространственная локальность. Если произошло обращение по некоторому адресу, то с высокой степенью вероятности в ближайшее время произойдет обращение к соседним адресам. Кафедра ИИТ. Мокрушин А. А. 30

04. Согласование данных Сквозная запись (write through). Обратная запись (write back). Кафедра ИИТ. Мокрушин А. А. 31

04. Согласование данных Сквозная запись (write through). Обратная запись (write back). Кафедра ИИТ. Мокрушин А. А. 31

04. Двухуровневый кэш Кафедра ИИТ. Мокрушин А. А. 32

04. Двухуровневый кэш Кафедра ИИТ. Мокрушин А. А. 32

05. Расслоение памяти Кафедра ИИТ. Мокрушин А. А. 33

05. Расслоение памяти Кафедра ИИТ. Мокрушин А. А. 33