2. Архитектура процессоров Intel.ppt

- Количество слайдов: 66

Архитектура процессоров Intel Лекция 2

Архитектура процессоров Intel Лекция 2

План лекции Цикл команды n Методы повышения производительности процессоров n Архитектура и микроархитектура n Микроархитектура Sandy Bridge n Регистры процессоров Intel n

План лекции Цикл команды n Методы повышения производительности процессоров n Архитектура и микроархитектура n Микроархитектура Sandy Bridge n Регистры процессоров Intel n

Цикл команды

Цикл команды

Цикл команды Программа в компьютере реализуется центральным процессором (ЦП) путем последовательного исполнения команд этой программы n Действия, требуемые для выборки (извлечения из оперативной памяти) и выполнения команды, называют циклом команды n

Цикл команды Программа в компьютере реализуется центральным процессором (ЦП) путем последовательного исполнения команд этой программы n Действия, требуемые для выборки (извлечения из оперативной памяти) и выполнения команды, называют циклом команды n

Цикл команды Этапы цикла команды: 1) выборка команды (Instruction Fetch) 2) декодирование (Decode) 3) выполнение (Execute) 4) запись результата (Retire)

Цикл команды Этапы цикла команды: 1) выборка команды (Instruction Fetch) 2) декодирование (Decode) 3) выполнение (Execute) 4) запись результата (Retire)

Цикл команды Этапы цикла команды: 1) выборка команды – процессор считывает команду из оперативной памяти или кэша по адресу, хранящемуся в специальном регистре – счетчике команд (IP – Instruction Pointer)

Цикл команды Этапы цикла команды: 1) выборка команды – процессор считывает команду из оперативной памяти или кэша по адресу, хранящемуся в специальном регистре – счетчике команд (IP – Instruction Pointer)

Цикл команды 2) декодирование – считанная команда преобразуется в последовательность элементарных внутренних команд процессора – микроопераций

Цикл команды 2) декодирование – считанная команда преобразуется в последовательность элементарных внутренних команд процессора – микроопераций

Цикл команды 3) выполнение – происходят арифметические или логические операции над данными; 4) запись результата – полученный ответ записывается в оперативную память или кэш

Цикл команды 3) выполнение – происходят арифметические или логические операции над данными; 4) запись результата – полученный ответ записывается в оперативную память или кэш

Цикл команды

Цикл команды

Методы повышения производительности

Методы повышения производительности

Методы повышения производительности Кэш-память (Memory Cache) n Конвейеризация (Pipelining) n Суперскалярность (Superscalar) n

Методы повышения производительности Кэш-память (Memory Cache) n Конвейеризация (Pipelining) n Суперскалярность (Superscalar) n

Кэш-память n В качестве основной памяти в большинстве компьютеров служат микросхемы динамических ОЗУ, на порядок уступающие по быстродействию процессору

Кэш-память n В качестве основной памяти в большинстве компьютеров служат микросхемы динамических ОЗУ, на порядок уступающие по быстродействию процессору

Кэш-память В результате процессор вынужден простаивать несколько тактов, пока информация из памяти установится на шине данных n Если основную память выполнить на быстрых микросхемах статической памяти, стоимость компьютера существенно возрастет n

Кэш-память В результате процессор вынужден простаивать несколько тактов, пока информация из памяти установится на шине данных n Если основную память выполнить на быстрых микросхемах статической памяти, стоимость компьютера существенно возрастет n

Кэш-память 1965 год, Морис Уилкс – идея кэш-памяти n Между основной памятью и процессором размещается небольшая, но быстродействующая буферная память n В кэш-память копируются те участки основной памяти, к которым происходит обращение процессора n

Кэш-память 1965 год, Морис Уилкс – идея кэш-памяти n Между основной памятью и процессором размещается небольшая, но быстродействующая буферная память n В кэш-память копируются те участки основной памяти, к которым происходит обращение процессора n

Кэш-память Выигрыш достигается за счет принципа локальности n Принцип заключается в том, что при выполнении программы с высокой вероятностью адрес следующей команды либо следует непосредственно за адресом текущей команды, либо находится вблизи него n

Кэш-память Выигрыш достигается за счет принципа локальности n Принцип заключается в том, что при выполнении программы с высокой вероятностью адрес следующей команды либо следует непосредственно за адресом текущей команды, либо находится вблизи него n

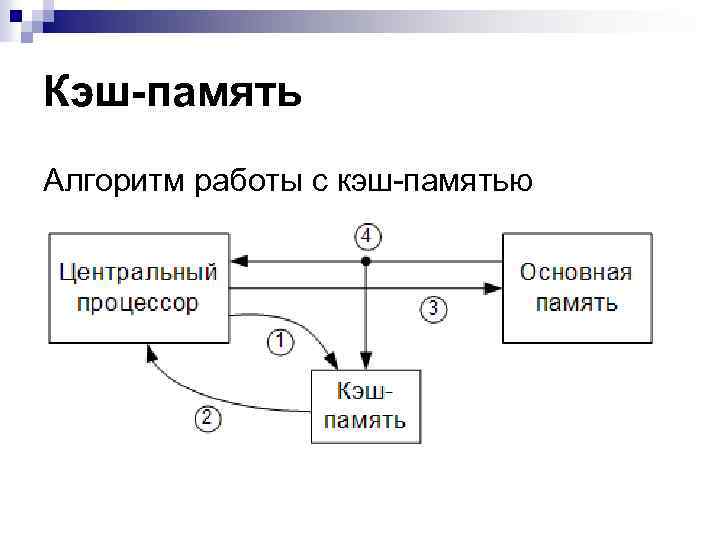

Кэш-память Алгоритм работы с кэш-памятью

Кэш-память Алгоритм работы с кэш-памятью

Кэш-память 1) Поиск копии требуемого слова в кэше 2) Попадание (hit) 3) Промах (miss) 4) Копирование слова в кэш

Кэш-память 1) Поиск копии требуемого слова в кэше 2) Попадание (hit) 3) Промах (miss) 4) Копирование слова в кэш

Кэш-память Виды кэш-памяти: n принстонская архитектура ¨ единая память для команд и данных n гарвардская архитектура ¨ память разделена для команд и данных

Кэш-память Виды кэш-памяти: n принстонская архитектура ¨ единая память для команд и данных n гарвардская архитектура ¨ память разделена для команд и данных

Кэш-память Преимущество единой памяти – автоматическая установка оптимального баланса между командами и данными n Преимущество раздельной памяти – одновременная выборка команд и данных n

Кэш-память Преимущество единой памяти – автоматическая установка оптимального баланса между командами и данными n Преимущество раздельной памяти – одновременная выборка команд и данных n

Кэш-память n Уровни кэш-памяти

Кэш-память n Уровни кэш-памяти

Кэш-память При доступе к памяти процессор сначала обращается к кэш-памяти L 1 n В случае промаха производится обращение к кэш-памяти L 2, затем к L 3 n Если информация отсутствует и там, выполняется обращение к основной памяти и блок данных заносится сначала в L 3, L 2, а затем и в L 1 n

Кэш-память При доступе к памяти процессор сначала обращается к кэш-памяти L 1 n В случае промаха производится обращение к кэш-памяти L 2, затем к L 3 n Если информация отсутствует и там, выполняется обращение к основной памяти и блок данных заносится сначала в L 3, L 2, а затем и в L 1 n

Конвейеризация

Конвейеризация

Конвейеризация Идея конвейера (pipeline) – можно не дожидаться завершения выполнения одной команды, а сразу переходить к следующей n Команда состоит из этапов, и за каждый этап отвечает отдельный блок процессора, образующий ступень конвейера n

Конвейеризация Идея конвейера (pipeline) – можно не дожидаться завершения выполнения одной команды, а сразу переходить к следующей n Команда состоит из этапов, и за каждый этап отвечает отдельный блок процессора, образующий ступень конвейера n

Конвейеризация

Конвейеризация

Конвейеризация Для увеличения эффективности конвейера каждый этап делят на несколько подэтапов (суперконвейеризация) n В процессорах Intel может быть до 31 ступени конвейера (обычно 10 -20) n

Конвейеризация Для увеличения эффективности конвейера каждый этап делят на несколько подэтапов (суперконвейеризация) n В процессорах Intel может быть до 31 ступени конвейера (обычно 10 -20) n

Конвейеризация n При использовании конвейера могут возникать конфликты

Конвейеризация n При использовании конвейера могут возникать конфликты

Конвейеризация 1) Несколько команд одновременно обращаются к одному ресурсу (чаще всего к памяти) Решения: ¨ модульное построение памяти ¨ использование кэш-памяти ¨ разделение кэш-памяти на кэш команд и кэш данных

Конвейеризация 1) Несколько команд одновременно обращаются к одному ресурсу (чаще всего к памяти) Решения: ¨ модульное построение памяти ¨ использование кэш-памяти ¨ разделение кэш-памяти на кэш команд и кэш данных

Конвейеризация 2) Несколько команд обращаются к одной ячейке памяти в неверной последовательности: ¨ чтение после записи (наиболее часто) ¨ запись после чтения ¨ запись после записи

Конвейеризация 2) Несколько команд обращаются к одной ячейке памяти в неверной последовательности: ¨ чтение после записи (наиболее часто) ¨ запись после чтения ¨ запись после записи

Конвейеризация n Чтение после записи (должно быть, но нарушается):

Конвейеризация n Чтение после записи (должно быть, но нарушается):

Конвейеризация Решения: n оптимизирующие компиляторы n задержка команд ( «пузырек» ) n ускоренное продвижение операндов

Конвейеризация Решения: n оптимизирующие компиляторы n задержка команд ( «пузырек» ) n ускоренное продвижение операндов

Конвейеризация 3) неизвестно, какая команда будет выполняться после команды перехода: ¨ команды безусловного перехода ¨ команды условного перехода Решения: ¨ использование буферов адресов перехода (BTB – Branch Target Buffer) ¨ предсказание переходов (branch prediction)

Конвейеризация 3) неизвестно, какая команда будет выполняться после команды перехода: ¨ команды безусловного перехода ¨ команды условного перехода Решения: ¨ использование буферов адресов перехода (BTB – Branch Target Buffer) ¨ предсказание переходов (branch prediction)

Суперскалярность

Суперскалярность

Суперскалярность В суперскалярных процессорах содержится несколько исполнительных блоков, работающих параллельно n Например, блоки целочисленной арифметики, арифметики с плавающей точкой, блоки чтения и записи из памяти n

Суперскалярность В суперскалярных процессорах содержится несколько исполнительных блоков, работающих параллельно n Например, блоки целочисленной арифметики, арифметики с плавающей точкой, блоки чтения и записи из памяти n

Суперскалярность n В таких процессорах обязателен блок диспетчеризации (Scheduler), отвечающий за распределение команд по исполнительным блокам

Суперскалярность n В таких процессорах обязателен блок диспетчеризации (Scheduler), отвечающий за распределение команд по исполнительным блокам

Суперскалярность n Наличие нескольких функциональных блоков приводит к тому, что наибольшая скорость выполнения может достигаться при внеочередном исполнении операций (Out-of-Order Execution)

Суперскалярность n Наличие нескольких функциональных блоков приводит к тому, что наибольшая скорость выполнения может достигаться при внеочередном исполнении операций (Out-of-Order Execution)

Суперскалярность Более поздние операции могут исполняться перед ранними, если не зависят от порождаемых ими результатов n Процессор должен лишь гарантировать, чтобы результаты внеочередного выполнения программы совпадали с результатами последовательного выполнения n

Суперскалярность Более поздние операции могут исполняться перед ранними, если не зависят от порождаемых ими результатов n Процессор должен лишь гарантировать, чтобы результаты внеочередного выполнения программы совпадали с результатами последовательного выполнения n

Суперскалярность n Механизм внеочередного исполнения позволяет в значительной степени сгладить эффект от ожидания считывания данных из кэшей верхних уровней и из оперативной памяти, что может занимать десятки и сотни тактов

Суперскалярность n Механизм внеочередного исполнения позволяет в значительной степени сгладить эффект от ожидания считывания данных из кэшей верхних уровней и из оперативной памяти, что может занимать десятки и сотни тактов

Переименование регистров (Rename) n Программисту предоставляется небольшое число логических регистров ¨ Intel: EAX, EBX, ECX, EDX, EBP, ESI, EDI n При конвейеризации, суперскалярности, внеочередном исполнении команд процессору требуется гораздо больше физических регистров

Переименование регистров (Rename) n Программисту предоставляется небольшое число логических регистров ¨ Intel: EAX, EBX, ECX, EDX, EBP, ESI, EDI n При конвейеризации, суперскалярности, внеочередном исполнении команд процессору требуется гораздо больше физических регистров

Архитектура и микроархитектура

Архитектура и микроархитектура

Архитектура и микроархитектура n При рассмотрении процессоров различают понятия «архитектура» и «микроархитектура»

Архитектура и микроархитектура n При рассмотрении процессоров различают понятия «архитектура» и «микроархитектура»

Архитектура и микроархитектура Архитектура – это логическое построение процессора, т. е. то, какой машина представляется программисту n Это понятие охватывает перечень и формат команд, формы представления данных, способы адресации памяти и т. д. n Все процессоры Intel, начиная с Intel 386, поддерживают архитектуру IA-32 (x 86) n 64 -разрядные архитектуры – x 64, IA-64 n

Архитектура и микроархитектура Архитектура – это логическое построение процессора, т. е. то, какой машина представляется программисту n Это понятие охватывает перечень и формат команд, формы представления данных, способы адресации памяти и т. д. n Все процессоры Intel, начиная с Intel 386, поддерживают архитектуру IA-32 (x 86) n 64 -разрядные архитектуры – x 64, IA-64 n

Архитектура и микроархитектура Микроархитектура – это структура процессора, отраженная в его составных частях и связях между ними n Микроархитектура – это конкретный способ реализации архитектуры n

Архитектура и микроархитектура Микроархитектура – это структура процессора, отраженная в его составных частях и связях между ними n Микроархитектура – это конкретный способ реализации архитектуры n

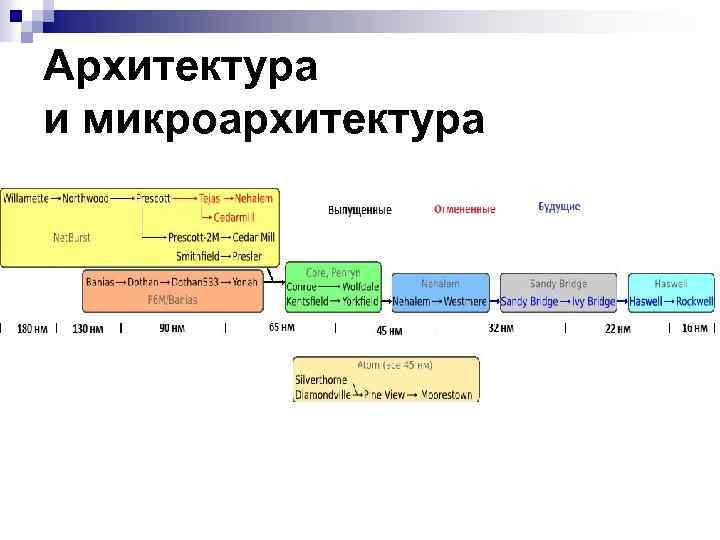

Архитектура и микроархитектура n Виды микроархитектур, применяемых в процессорах Intel: ¨ Р 6 – Pentium Pro, Pentium III ¨ Net. Burst (пакетно-сетевая) – Pentium 4, Pentium D, Pentium Extreme Editions ¨ improved Pentium M – Intel Core Duo, Intel Core Solo

Архитектура и микроархитектура n Виды микроархитектур, применяемых в процессорах Intel: ¨ Р 6 – Pentium Pro, Pentium III ¨ Net. Burst (пакетно-сетевая) – Pentium 4, Pentium D, Pentium Extreme Editions ¨ improved Pentium M – Intel Core Duo, Intel Core Solo

Архитектура и микроархитектура n Виды микроархитектур, применяемых в процессорах Intel: q q q Intel Core – Intel Core 2 Duo, Intel Core 2 Quad, Intel Core 2 Extreme Nehalem – Intel Core i 5, Intel Core i 7 Sandy Bridge – Celeron, Pentium, Core i 3, Core i 5, Core i 7

Архитектура и микроархитектура n Виды микроархитектур, применяемых в процессорах Intel: q q q Intel Core – Intel Core 2 Duo, Intel Core 2 Quad, Intel Core 2 Extreme Nehalem – Intel Core i 5, Intel Core i 7 Sandy Bridge – Celeron, Pentium, Core i 3, Core i 5, Core i 7

Архитектура и микроархитектура

Архитектура и микроархитектура

Sandy Bridge

Sandy Bridge

Sandy Bridge

Sandy Bridge

Sandy Bridge Количество ядер – от 2 до 8 n Частота ядра – от 1, 1 до 4, 0 ГГц n Количество транзисторов – от 504 млн до 2, 27 млрд n

Sandy Bridge Количество ядер – от 2 до 8 n Частота ядра – от 1, 1 до 4, 0 ГГц n Количество транзисторов – от 504 млн до 2, 27 млрд n

Sandy Bridge n Кэш‑память трех уровней: ¨ L 1 – 32 Кбайт кэш команд и 32 Кбайт кэш данных (гарвардская архитектура) ¨ L 2 – 256 Кбайт ¨ L 3 – от 1 до 20 Мбайт

Sandy Bridge n Кэш‑память трех уровней: ¨ L 1 – 32 Кбайт кэш команд и 32 Кбайт кэш данных (гарвардская архитектура) ¨ L 2 – 256 Кбайт ¨ L 3 – от 1 до 20 Мбайт

Sandy Bridge

Sandy Bridge

Sandy Bridge n LLC – Last Level Cache, кэш последнего уровня (L 3) ¨ доступен всем ядрам IMC – Integrated Memory Controller (DDR 3) n DMI – Direct Media Interface (подключение к чипсету) n

Sandy Bridge n LLC – Last Level Cache, кэш последнего уровня (L 3) ¨ доступен всем ядрам IMC – Integrated Memory Controller (DDR 3) n DMI – Direct Media Interface (подключение к чипсету) n

Sandy Bridge

Sandy Bridge

Sandy Bridge 160 целочисленных регистров 64‑разрядных n 144 вещественных регистров 256‑разрядных n

Sandy Bridge 160 целочисленных регистров 64‑разрядных n 144 вещественных регистров 256‑разрядных n

Регистры процессоров Intel

Регистры процессоров Intel

Регистры процессоров Intel Регистр – многоразрядная ячейка памяти, предназначенная для временного хранения текущей информации n Регистровая память – самая быстродействующая в компьютере n Совокупность регистров называется регистровым файлом n

Регистры процессоров Intel Регистр – многоразрядная ячейка памяти, предназначенная для временного хранения текущей информации n Регистровая память – самая быстродействующая в компьютере n Совокупность регистров называется регистровым файлом n

Регистры процессоров Intel Регистры процессора делятся на: n доступные программисту (user-visible registers) n внутренние регистры процессора (internal registers)

Регистры процессоров Intel Регистры процессора делятся на: n доступные программисту (user-visible registers) n внутренние регистры процессора (internal registers)

Регистры процессоров Intel Основные регистры процессоров Intel: n регистры общего назначения n сегментные регистры n регистр указателя команд n регистр флагов n системные регистры n регистры FPU, MMX- и SSE-расширений

Регистры процессоров Intel Основные регистры процессоров Intel: n регистры общего назначения n сегментные регистры n регистр указателя команд n регистр флагов n системные регистры n регистры FPU, MMX- и SSE-расширений

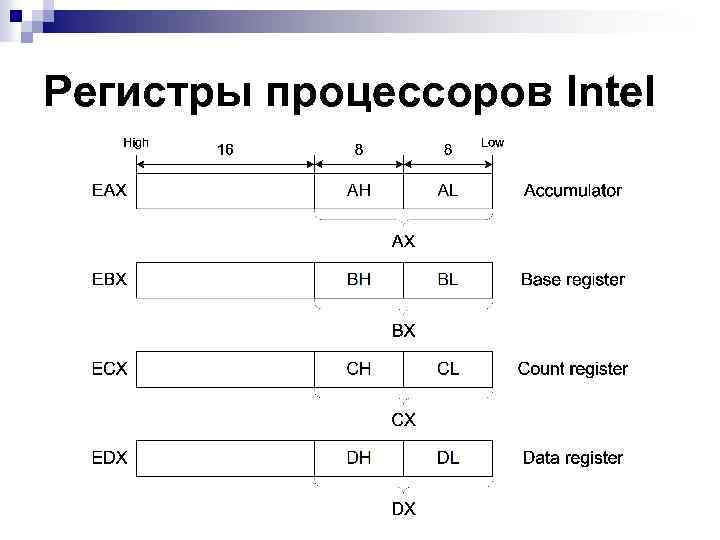

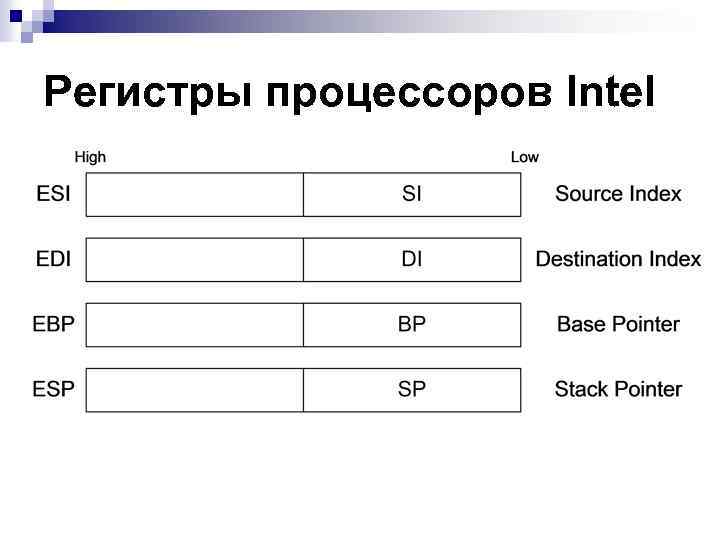

Регистры процессоров Intel Регистры общего назначения (РОН) – регистры, предназначенные для выполнения текущих вычислений n Регистров общего назначения 8, все они – 32 -разрядные: EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP n

Регистры процессоров Intel Регистры общего назначения (РОН) – регистры, предназначенные для выполнения текущих вычислений n Регистров общего назначения 8, все они – 32 -разрядные: EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP n

Регистры процессоров Intel

Регистры процессоров Intel

Регистры процессоров Intel

Регистры процессоров Intel

Регистры процессоров Intel n Сегментные регистры (16 -разрядные) ¨ CS – сегмент кода ¨ DS – сегмент данных ¨ SS – сегмент стека ¨ ES, GS, FS – дополнительные регистры n В сегментных регистрах хранится адрес соответствующего сегмента (указатель на строку в таблице GDT или LDT)

Регистры процессоров Intel n Сегментные регистры (16 -разрядные) ¨ CS – сегмент кода ¨ DS – сегмент данных ¨ SS – сегмент стека ¨ ES, GS, FS – дополнительные регистры n В сегментных регистрах хранится адрес соответствующего сегмента (указатель на строку в таблице GDT или LDT)

Регистры процессоров Intel Регистр указателя команд – EIP (Expanded Instruction Pointer), 32 разряда n Содержит адрес следующей команды относительно начала сегмента n Прямого доступа к нему нет, но команды перехода косвенно его изменяют n

Регистры процессоров Intel Регистр указателя команд – EIP (Expanded Instruction Pointer), 32 разряда n Содержит адрес следующей команды относительно начала сегмента n Прямого доступа к нему нет, но команды перехода косвенно его изменяют n

Регистры процессоров Intel Регистр флагов – EFLAGS, 32 разряда n Хранит информацию о состоянии процессора и о результатах выполнения команд n Флаг – это бит, принимающий значение 1, если он установлен, и 0, если сброшен n

Регистры процессоров Intel Регистр флагов – EFLAGS, 32 разряда n Хранит информацию о состоянии процессора и о результатах выполнения команд n Флаг – это бит, принимающий значение 1, если он установлен, и 0, если сброшен n

Регистры процессоров Intel CF (Carry Flag) – флаг переноса n PF (Parity Flag) – флаг четности n ZF (Zero Flag) – флаг нуля n SF (Signum Flag) – флаг знака n OF (Overflow Flag) – флаг переполнения n

Регистры процессоров Intel CF (Carry Flag) – флаг переноса n PF (Parity Flag) – флаг четности n ZF (Zero Flag) – флаг нуля n SF (Signum Flag) – флаг знака n OF (Overflow Flag) – флаг переполнения n

Регистры процессоров Intel Системные адресные регистры: GDTR, LDTR. IDTR, TR n Управляющие регистры: СR 0 -CR 4 (Control Registers) n Регистры отладки: DR 0 -DR 7 (Debug Registers) n

Регистры процессоров Intel Системные адресные регистры: GDTR, LDTR. IDTR, TR n Управляющие регистры: СR 0 -CR 4 (Control Registers) n Регистры отладки: DR 0 -DR 7 (Debug Registers) n

Регистры процессоров Intel Регистры математического сопроцессора (80 -разрядные): ST(0)-ST(7) n Целочисленные 64 -разрядные регистры MMX-расширения: MMX 0 -MMX 7 n Регистры с плавающей точкой 128 -разрядные SSE-расширения: XMM 0 -XMM 7 n

Регистры процессоров Intel Регистры математического сопроцессора (80 -разрядные): ST(0)-ST(7) n Целочисленные 64 -разрядные регистры MMX-расширения: MMX 0 -MMX 7 n Регистры с плавающей точкой 128 -разрядные SSE-расширения: XMM 0 -XMM 7 n