Архитектура ЭВМ11.ppt

- Количество слайдов: 22

Архитектура процессора • • Краткий обзор архитектур: CISC (complex instruction set computer) RISC (restricted (reduced) instruction set computer) URISC (Ultimate RISC) MISC (minimal instruction set computer)

Архитектура процессора CISC До начала 80 -х совершенствование процессоров было направлено на то, чтобы сконструировать по возможности более функциональный компьютер, который позволил бы выполнять как можно больше разных инструкций. Причины: • Удобно для программистов, так компиляторы языков высокого уровня еще только начинали развиваться, программы писались на ассемблере. • Такой подход позволяет уменьшить количество инструкции. Это уменьшает размеры программы и время ее выполнения.

Архитектура процессора CISC Процессоры, построенные на архитектуре CISC, поддерживали инструкции «на все случаи жизни» : синус, косинус, квадратный корень, добавить элемент в очередь, удалить элемент из очереди, провести интерполяцию полиномом. Также поддерживалось множество способов адресации памяти, например «взять в качестве аргумента инструкции данные, записанные по адресу, записанному вон в том регистре, со смещением, записанным вот в этом регистре»

Архитектура процессора Общие признаки CISC: • Нефиксированное значение длины команды; • Арифметические действия кодируются в одной команде; • Небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Архитектура процессора Недостатки CISC: • Инструкции сложно не только выполнять, но и декодировать (выделять из машинного кода). • Оказалось, что даже в программах на ассемблере эти "сверхвозможности" почти никогда не использовали, а компиляторы языков высокого уровня - и не пытались использовать. • Частые обращения к «медленной» оперативной памяти. • Сложности с реализацией конвейера и суперскалярности (все инструкции разные по длине и по содержанию)

Архитектура процессора RISC проектировался в расчете на типовой код, генерируемый компиляторами. Сведен к минимуму набор инструкций и к абсолютному минимуму - количество режимов адресации памяти. В некоторых реализациях отсутствуют даже операции умножения и деления.

Архитектура процессора Общие признаки RISC • Фиксированная длина машинных инструкций и простой формат команды. • Специализированные команды для операций с памятью — чтения или записи. Операции вида «прочитать-изменить-записать» отсутствуют. Любые операции «изменить» выполняются только над содержимым регистров. • Большое количество регистров общего назначения (32 и более).

Архитектура процессора Преимущества RISC • Простота реализации • Меньше обращений к «медленной» памяти (промежуточные данные можно хранить в регистрах) • Просто реализуемый конвейер. • Более эффективное предсказание переходов.

Архитектура процессора Архитектура x 86 Процессоры архитектуры x 86 ранее являлись CISCпроцессорами, однако, начиная с Intel 486, являются CISC-процессорами с RISC-ядром. Перед исполнением CISC-инструкции x 86 преобразуются в более простой набор внутренних инструкций RISC.

Архитектура процессора Проблемы 32 разрядной архитектуры x 86 • 32 разрядная адресация позволяет использовать не более 4 Гб оперативной памяти (на практике не более 2). • Всего 4 регистра для хранения данных, частые обращения к оперативной памяти. Как следствие, много тактов процессор простаивает, ожидая данные. • Сложности с параллельным выполнением команд.

64 разрядные архитектуры • • • IA-64 Разработана Intel и Hewlett Packard. Процессоры: Itanium и Itanium 2. x 86 -64 Разработана AMD. Другие названия: x 64, AA-64, Hammer Architecture, AMD 64, EM 64 T, IA-32 e, Intel 64. Процессоры: Athlon 64, Athlon II, Phenom, Turion 64, Opteron, Sempron, Pentium Dual-Core, Core 2 Duo, Core 2 Quad, Core i 3, Core i 5, Core i 7, Atom, Xeon.

IA-64 Основана на технологии EPIC (Explicity Parallel Instruction Computing – вычисления с явной параллельностью инструкций). Регистры: • 128 регистров общего назначения GR 0 -127 • 128 регистров с плавающей запятой FR 0 -127 • 64 регистра предикатов PR. Одноразрядные, в них помещаются результаты команд сравнения. • 8 регистров перехода BR. 64 -разрядные, применяются для указания адреса перехода • 128 прикладных регистров AR. Специализированные (в основном 64 -разрядные) регистры. • Счетчик команд IP.

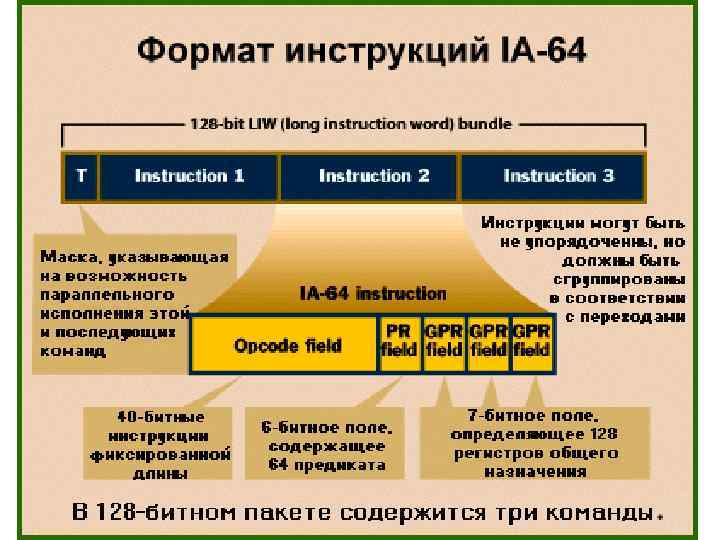

IA-64 Система команд • Команды IA-64 упакованы по три в 128 -битный пакет. • Команды имеют фиксированную длину. Каждая команда содержит три 7 -битных поля регистра общего назначения. • Каждый 128 -битный пакет содержит шаблон длиной в 5 бит, помещаемый в него компилятором, который указывает процессору, какие из команд могут выполняться параллельно.

IA-64 Технология "отмеченных команд" (predication) • Когда компилятор находит оператор ветвления в исходном коде, он может отметить все команды, относящиеся к одному пути ветвления, уникальным идентификатором(предикатом). Например, путь, соответствующий значению условия ветвления TRUE, помечается предикатом Р 1, а каждая команда пути, соответствующего значению условия ветвления FALSE - предикатом Р 2. • Система команд IA-64 определяет для каждой команды 6 битное поле для хранения этого предиката. Таким образом, одновременно могут быть использованы 64 различных предиката.

IA-64 Технология "отмеченных команд" (predication) • Когда процессор обнаруживает "отмеченное" ветвление, он начинает параллельно выполнять блоки, соответствующие всем возможным путям ветвления. Таким образом, на машинном уровне ветвления нет. • В какой-то момент процессор вычислит значение условия ветвления в операторе условного перехода. Предположим, оно равно TRUE, следовательно, правильный путь отмечен предикатом Р 1. Результат работы всех остальных команд будет отброшен.

IA-64 Предварительная загрузка (speculative loading) Компиляторы для IA-64 могут просматривать исходный код с целью поиска команд, использующих данные из памяти. Найдя такую команду, они могут добавить пару команд - команду предварительной загрузки (speculative loading) и проверки загрузки (speculative check). Во время выполнения программы первая из команд загружает данные в память до того, как они понадобятся программе. Вторая команда проверяет, успешно ли произошла загрузка. Предварительная загрузка позволяет уменьшить потери производительности из-за задержек при доступе к памяти, а также повысить параллелизм.

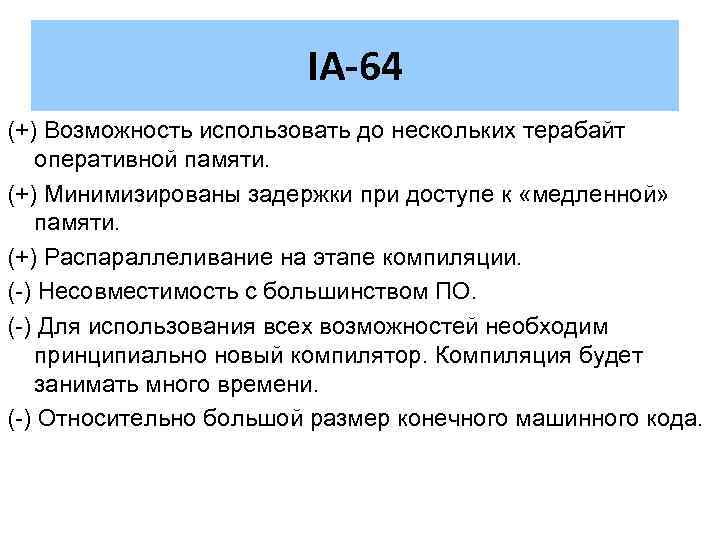

IA-64 (+) Возможность использовать до нескольких терабайт оперативной памяти. (+) Минимизированы задержки при доступе к «медленной» памяти. (+) Распараллеливание на этапе компиляции. (-) Несовместимость с большинством ПО. (-) Для использования всех возможностей необходим принципиально новый компилятор. Компиляция будет занимать много времени. (-) Относительно большой размер конечного машинного кода.

x 86 -64 Это расширение архитектуры x 86 с полной обратной совместимостью. Режимы работы: • Long Mode( «Длинный» режим) дает возможность воспользоваться всеми дополнительными преимуществами, предоставляемыми архитектурой x 86 -64. Для использования этого режима необходима 64 -битная операционная система, например, Windows XP Professional x 64 Edition. • Legacy Mode позволяет процессору выполнять инструкции, рассчитанные для процессоров x 86, и предоставляет полную совместимость с 32 -битным кодом и операционными системами. В этом режиме процессор ведёт себя точно так же, как x 86 -процессор, например Pentium 4.

x 86 -64 Регистры: • 16 целочисленных 64 -битных регистров общего назначения (RAX, RBX, RCX, RDX, RBP, RSI, RDI, RSP, R 8 — R 15). Для обращения к младшим 8 -, 16 - и 32 -битам новых регистров можно использовать суффиксы b, w и d соответственно. Например, R 9 - это 64 -разряный регистр, R 9 b - его младший байт (по аналогии с AL), а R 9 w - младшее слово (то же самое, что AX в EAX). • 64 -битный указатель RIP и 64 -битный регистр флагов RFLAGS.

x 86 -64 Преимущества • 64 -битное адресное пространство. • Расширенный набор регистров. • Привычный для разработчиков набор команд. • Возможность запуска старых 32 -битных приложений в 64 битной операционной системе. • Возможность использования 32 -битных операционных систем. Недостатки • Увеличение требований программ к памяти из-за того, что увеличился размер адресов и операндов. • Нет принципиального повышения производительности.

Архитектура ЭВМ11.ppt