Архитектура_МПСУ_2013.ppt

- Количество слайдов: 64

АРХИТЕКТУРА микропроцессорных систем управления (МПСУ)

АРХИТЕКТУРА микропроцессорных систем управления (МПСУ)

Вопросы лекции 1. Виртуальный микропроцессор 2. Структура и классификация микропроцессорных систем управления 3. Пример реализации виртуальной МПСУ

Вопросы лекции 1. Виртуальный микропроцессор 2. Структура и классификация микропроцессорных систем управления 3. Пример реализации виртуальной МПСУ

1 Вопрос Виртуальный микропроцессор

1 Вопрос Виртуальный микропроцессор

Варианты реализации цифровых устройств: 1. Программный способ управления «Микропроцессорные средства» ; 2. Аппаратный а) Неизменяемый – «Жесткая логика» б)Перестраиваемый – «Программируемые логические интегральные схемы (ПЛИС)» .

Варианты реализации цифровых устройств: 1. Программный способ управления «Микропроцессорные средства» ; 2. Аппаратный а) Неизменяемый – «Жесткая логика» б)Перестраиваемый – «Программируемые логические интегральные схемы (ПЛИС)» .

Два варианта разработки и изготовления БИС и СБИС 1. Разработка и выпуск БИС и СБИС для очень крупных заказчиков за их средства. 2. Разработка и выпуск БИС и СБИС за счет завода изготовителя и продажа мелким потребителям в очень больших количествах.

Два варианта разработки и изготовления БИС и СБИС 1. Разработка и выпуск БИС и СБИС для очень крупных заказчиков за их средства. 2. Разработка и выпуск БИС и СБИС за счет завода изготовителя и продажа мелким потребителям в очень больших количествах.

Достоинства микропроцессоров: Выпускаются в виде больших (БИС) и сверх больших (СБИС) интегральных схем. При массовом выпуске БИС и СБИС цена одной микросхемы очень мала. Но: требуется вложить очень большие средства в подготовку производства (миллионы долларов)

Достоинства микропроцессоров: Выпускаются в виде больших (БИС) и сверх больших (СБИС) интегральных схем. При массовом выпуске БИС и СБИС цена одной микросхемы очень мала. Но: требуется вложить очень большие средства в подготовку производства (миллионы долларов)

Определение микропроцессора Цифровое программно управляемое устройство реализованное в виде нескольких микросхем.

Определение микропроцессора Цифровое программно управляемое устройство реализованное в виде нескольких микросхем.

Микропроцессор состоит из центрального процессора и набора периферийных узлов.

Микропроцессор состоит из центрального процессора и набора периферийных узлов.

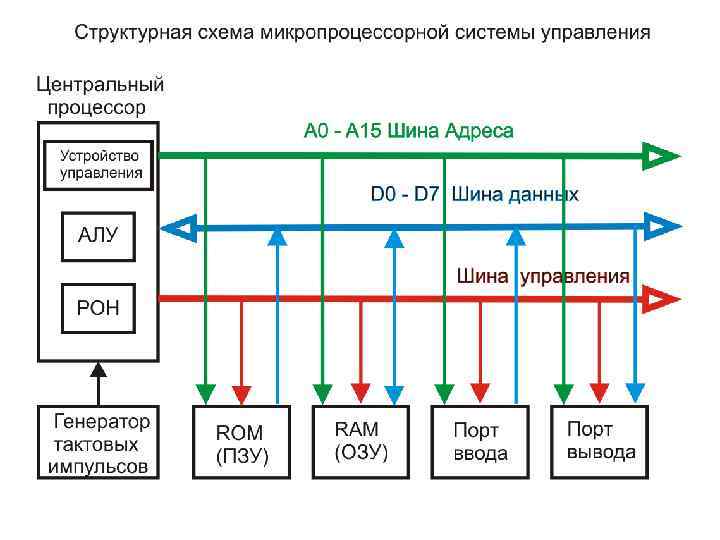

Основные узлы центрального процессора: • устройство управления; • арифметико-логическое устройство; • регистры общего назначения;

Основные узлы центрального процессора: • устройство управления; • арифметико-логическое устройство; • регистры общего назначения;

Вспомогательные микропроцессора (системы): • • генератор тактовых импульсов; память программ; память данных; устройства ввода-вывода;

Вспомогательные микропроцессора (системы): • • генератор тактовых импульсов; память программ; память данных; устройства ввода-вывода;

Рассмотрим основные элементы микропроцессора

Рассмотрим основные элементы микропроцессора

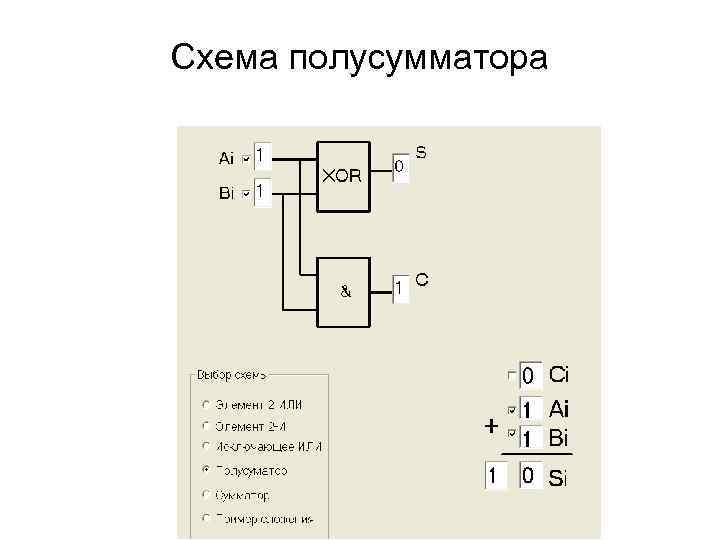

Арифметико-логическое устройство (АЛУ) Предназначено для выполнения арифметических и логических операций над двоичными кодами Основными элементами являются сумматор и полусумматор

Арифметико-логическое устройство (АЛУ) Предназначено для выполнения арифметических и логических операций над двоичными кодами Основными элементами являются сумматор и полусумматор

Схема полусумматора

Схема полусумматора

Схема сумматора

Схема сумматора

Арифметико-логическое устройство (АЛУ)

Арифметико-логическое устройство (АЛУ)

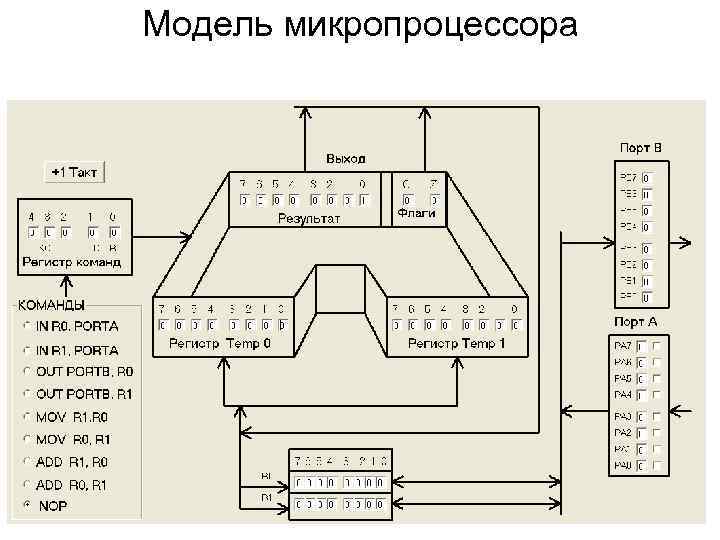

Модель микропроцессора

Модель микропроцессора

Смотри приложение к лекции в папке «Программные_модели_МПСУ»

Смотри приложение к лекции в папке «Программные_модели_МПСУ»

2. Структура и классификация микропроцессорных систем управления

2. Структура и классификация микропроцессорных систем управления

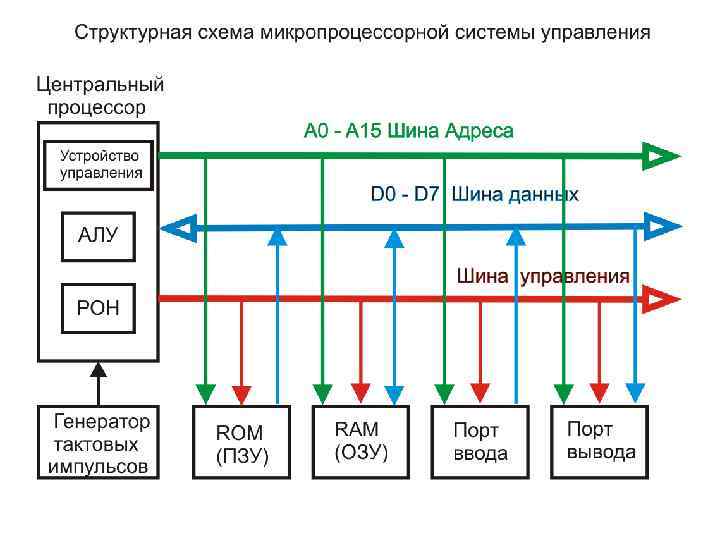

Структура МПСУ МСУ имеют открытую структуру на основе трех шин: 1. Шина адреса 2. Шина данных 3. Шина управления Все элементы МПСУ должны подключатся к этим шинам

Структура МПСУ МСУ имеют открытую структуру на основе трех шин: 1. Шина адреса 2. Шина данных 3. Шина управления Все элементы МПСУ должны подключатся к этим шинам

Ядром системы является микропроцессор. Все остальные элементы являются или устройствами ввода или устройствами вывода. Может быть также комбинированное устройство ввода-вывода.

Ядром системы является микропроцессор. Все остальные элементы являются или устройствами ввода или устройствами вывода. Может быть также комбинированное устройство ввода-вывода.

Каждому устройству выделяется индивидуальный адрес (или группа адресов) с помощью которого центральный процессор выбирает это устройство.

Каждому устройству выделяется индивидуальный адрес (или группа адресов) с помощью которого центральный процессор выбирает это устройство.

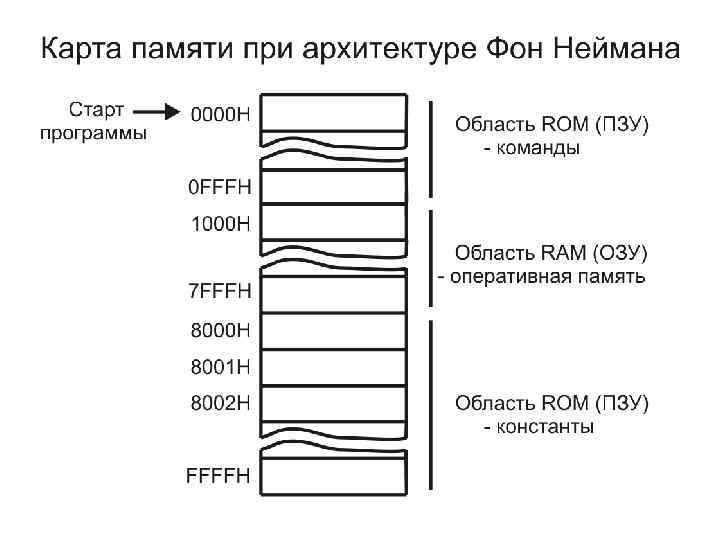

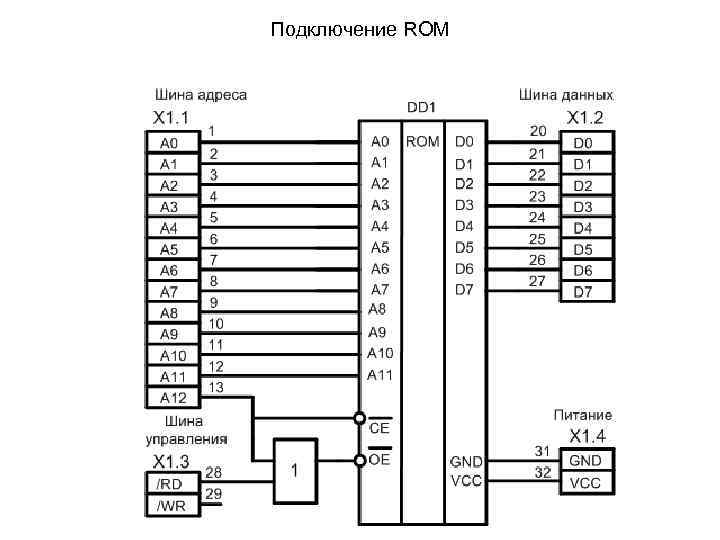

Обозначения запоминающих устройств • ROM – Read Only Memory • (ПЗУ – Постоянное Запоминающее • Устройство) • RAM – Random Access Memory • (ОЗУ – Оперативное Запоминающее • Устройство)

Обозначения запоминающих устройств • ROM – Read Only Memory • (ПЗУ – Постоянное Запоминающее • Устройство) • RAM – Random Access Memory • (ОЗУ – Оперативное Запоминающее • Устройство)

Подключение устройств ввода Все устройства ввода, подключенные к шине данных, должны находится в Zсостоянии (состояние высокого сопротивления линии). В момент чтения содержимого некоторого устройства только оно должно быть активно.

Подключение устройств ввода Все устройства ввода, подключенные к шине данных, должны находится в Zсостоянии (состояние высокого сопротивления линии). В момент чтения содержимого некоторого устройства только оно должно быть активно.

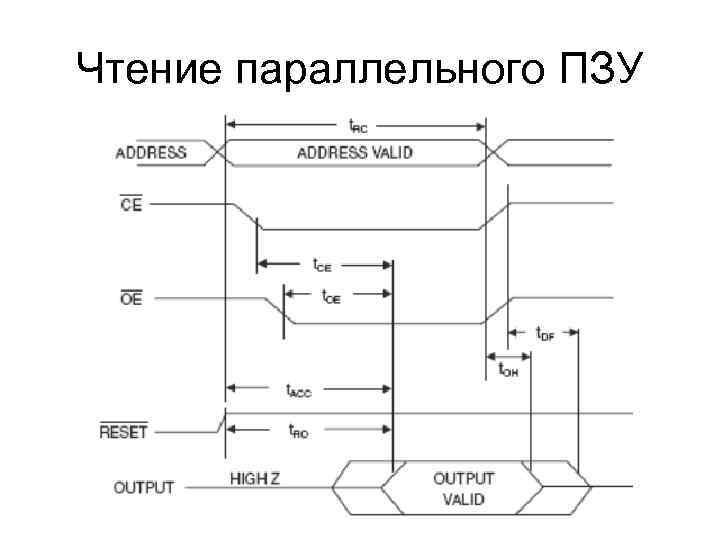

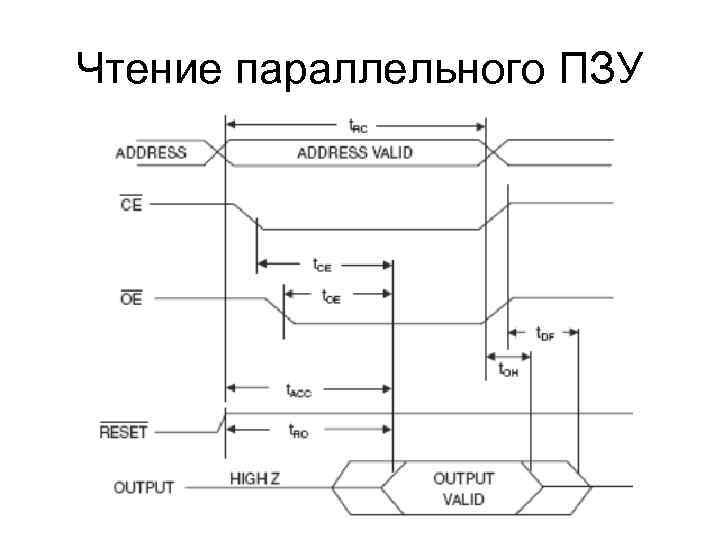

Чтение параллельного ПЗУ

Чтение параллельного ПЗУ

Классификация микропроцессорных средств • Микропроцессорные наборы • Однокристальные микроконтроллеры

Классификация микропроцессорных средств • Микропроцессорные наборы • Однокристальные микроконтроллеры

Микропроцессорные наборы • Содержат комплект микросхем для реализации законченной системы. • Состоят из микропроцессора и вспомогательных микросхем • Требуется сложное оборудование для создание готового изделия

Микропроцессорные наборы • Содержат комплект микросхем для реализации законченной системы. • Состоят из микропроцессора и вспомогательных микросхем • Требуется сложное оборудование для создание готового изделия

ОДНОКРИСТАЛЬНЫЕ МИКРОКОНТРОЛЛЕРЫ • Это цифровые управляющие устройства, реализованные в виде одной интегральной микросхемы. Название происходит от английского глагола «Control» - управлять. • Содержат на кристалле все необходимые для работы узлы и средства ввода-вывода.

ОДНОКРИСТАЛЬНЫЕ МИКРОКОНТРОЛЛЕРЫ • Это цифровые управляющие устройства, реализованные в виде одной интегральной микросхемы. Название происходит от английского глагола «Control» - управлять. • Содержат на кристалле все необходимые для работы узлы и средства ввода-вывода.

Структурная схема микроконтроллера

Структурная схема микроконтроллера

Основные узлы микроконтроллера: • • устройство управления; арифметико-логическое устройство; регистры общего назначения; генератор тактовых импульсов; память программ; память данных; устройства ввода-вывода;

Основные узлы микроконтроллера: • • устройство управления; арифметико-логическое устройство; регистры общего назначения; генератор тактовых импульсов; память программ; память данных; устройства ввода-вывода;

Дополнительные узлы: • таймер; • широтно-импульсный модулятор (ШИМ); • аналого-цифровой преобразователь (АЦП); • сторожевой таймер и др.

Дополнительные узлы: • таймер; • широтно-импульсный модулятор (ШИМ); • аналого-цифровой преобразователь (АЦП); • сторожевой таймер и др.

Классификация по типу архитектуры • Фон Неймана (Пристонская или классическая) • Гарвардская

Классификация по типу архитектуры • Фон Неймана (Пристонская или классическая) • Гарвардская

Архитектура Фон Неймана • Имеется единое адресное пространство • Команды и данные могут быть перемешаны • Имеется принципиальная возможность того, что микропроцессор может сам переписать свою программу

Архитектура Фон Неймана • Имеется единое адресное пространство • Команды и данные могут быть перемешаны • Имеется принципиальная возможность того, что микропроцессор может сам переписать свою программу

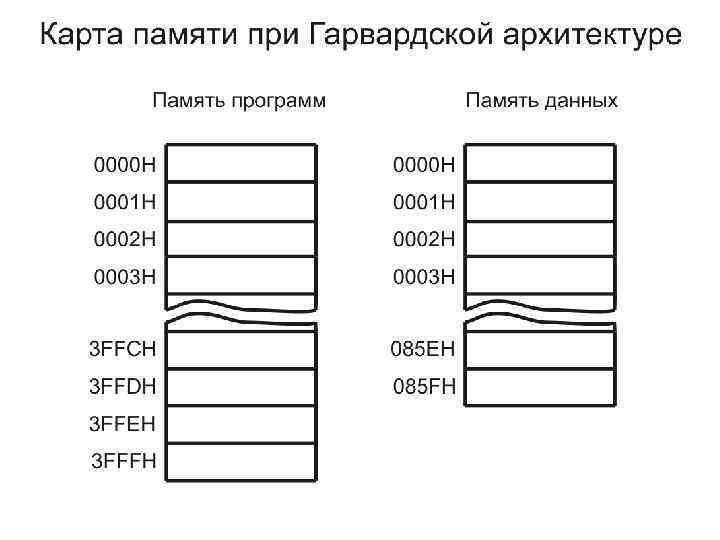

Гарвардская архитектура • Память программ и память данных физически и логически разделены • К памяти данных имеет доступ программист на этапе программирования, посредством специального программатора • К памяти данных обращается центральный процессор в процесс выполнения программы

Гарвардская архитектура • Память программ и память данных физически и логически разделены • К памяти данных имеет доступ программист на этапе программирования, посредством специального программатора • К памяти данных обращается центральный процессор в процесс выполнения программы

Классификация по количеству команд • CISC - Complex Instruction Set Computers • полная система команд • RISC - Reduced Instruction Set Computers • сокращенная система команд

Классификация по количеству команд • CISC - Complex Instruction Set Computers • полная система команд • RISC - Reduced Instruction Set Computers • сокращенная система команд

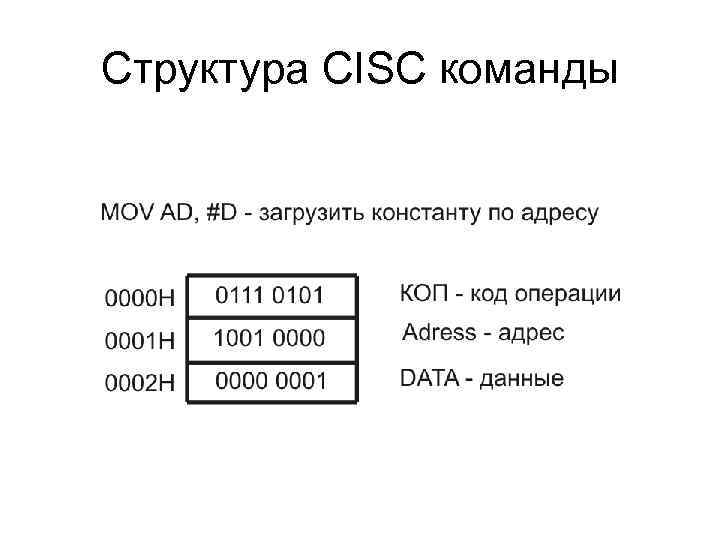

Структура CISC команды

Структура CISC команды

Структура RISC команды

Структура RISC команды

Разрядность микроконтроллеров • Используется следующая разрядность: • • • 4 бита – тетрада; 8 бит – байт; 16 бит – слово; 32 бита – двойное слово; 64 бита – четыре слова.

Разрядность микроконтроллеров • Используется следующая разрядность: • • • 4 бита – тетрада; 8 бит – байт; 16 бит – слово; 32 бита – двойное слово; 64 бита – четыре слова.

• Разрядность шины данных и разрядность команд могут не совпадать • Разрядность микроконтроллера определяется разрядностью шины данных

• Разрядность шины данных и разрядность команд могут не совпадать • Разрядность микроконтроллера определяется разрядностью шины данных

Быстродействие микроконтроллеров • Быстродействие микроконтроллеров – это время выполнения одной операции. • Быстродействие связано с тактовой частотой но определяется не только этим. • Время выполнения одной команды называется машинным циклом. Машинный цикл состоит из тактов генератора.

Быстродействие микроконтроллеров • Быстродействие микроконтроллеров – это время выполнения одной операции. • Быстродействие связано с тактовой частотой но определяется не только этим. • Время выполнения одной команды называется машинным циклом. Машинный цикл состоит из тактов генератора.

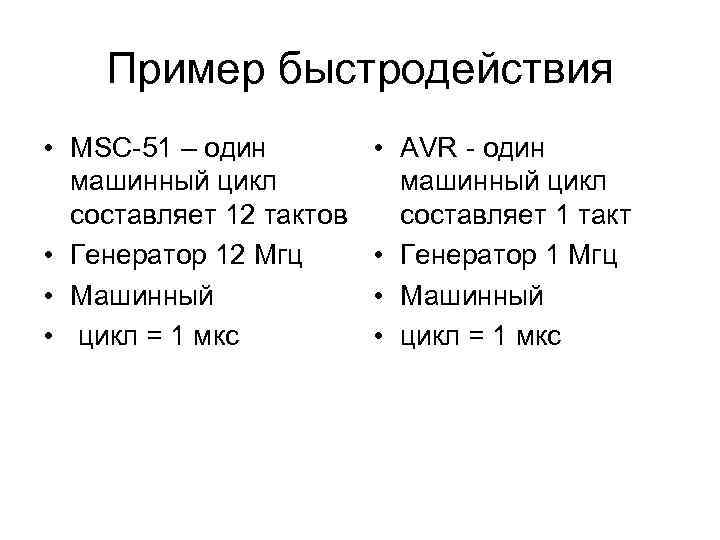

Пример быстродействия • MSC-51 – один машинный цикл составляет 12 тактов • Генератор 12 Мгц • Машинный • цикл = 1 мкс • AVR - один машинный цикл составляет 1 такт • Генератор 1 Мгц • Машинный • цикл = 1 мкс

Пример быстродействия • MSC-51 – один машинный цикл составляет 12 тактов • Генератор 12 Мгц • Машинный • цикл = 1 мкс • AVR - один машинный цикл составляет 1 такт • Генератор 1 Мгц • Машинный • цикл = 1 мкс

3. Вопрос Пример реализации виртуальной МПСУ

3. Вопрос Пример реализации виртуальной МПСУ

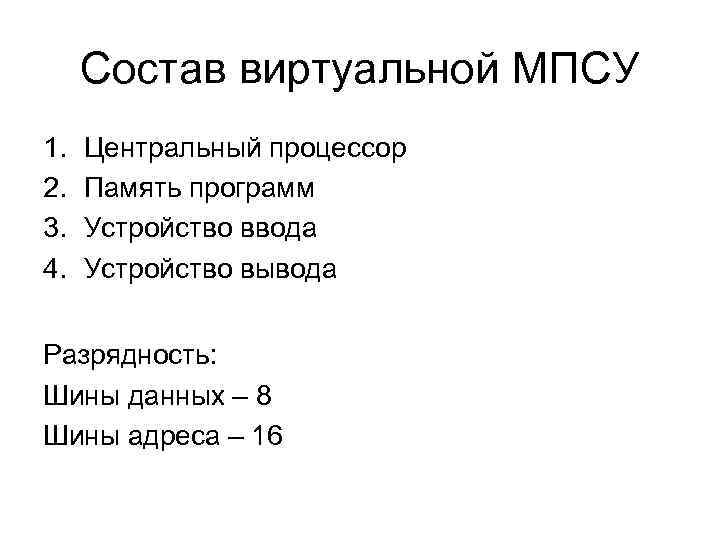

Состав виртуальной МПСУ 1. 2. 3. 4. Центральный процессор Память программ Устройство ввода Устройство вывода Разрядность: Шины данных – 8 Шины адреса – 16

Состав виртуальной МПСУ 1. 2. 3. 4. Центральный процессор Память программ Устройство ввода Устройство вывода Разрядность: Шины данных – 8 Шины адреса – 16

Подключение устройств ввода • Все устройства ввода данных подключенные к шине данных должны находится в Z-состоянии (состояние высокого ипенданса).

Подключение устройств ввода • Все устройства ввода данных подключенные к шине данных должны находится в Z-состоянии (состояние высокого ипенданса).

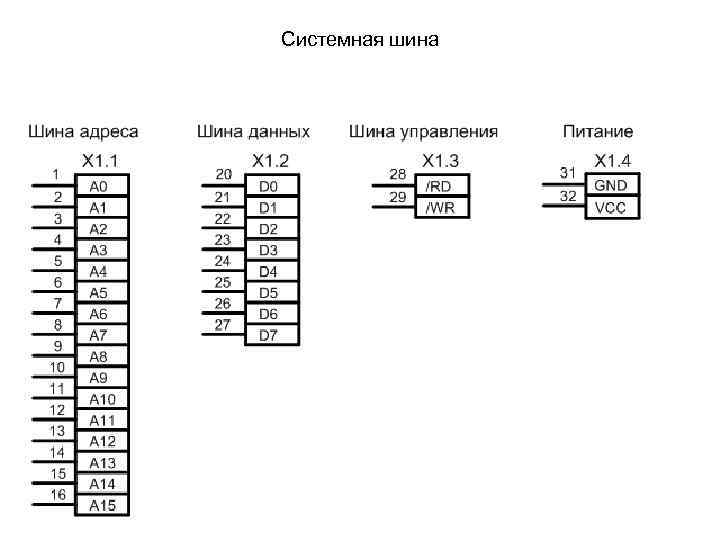

Системная шина

Системная шина

Буферизация шин В нашей МПСУ будет несколько разъемов (сокетов) к которым будут подключатся внешние устройства ввода-вывода. Количество устройств определяется разрядностью шины адреса. Но требуется обеспечить нагрузочную способность шин. Для этого между центральным процессором и внешними устройствами включаются шинные формирователи.

Буферизация шин В нашей МПСУ будет несколько разъемов (сокетов) к которым будут подключатся внешние устройства ввода-вывода. Количество устройств определяется разрядностью шины адреса. Но требуется обеспечить нагрузочную способность шин. Для этого между центральным процессором и внешними устройствами включаются шинные формирователи.

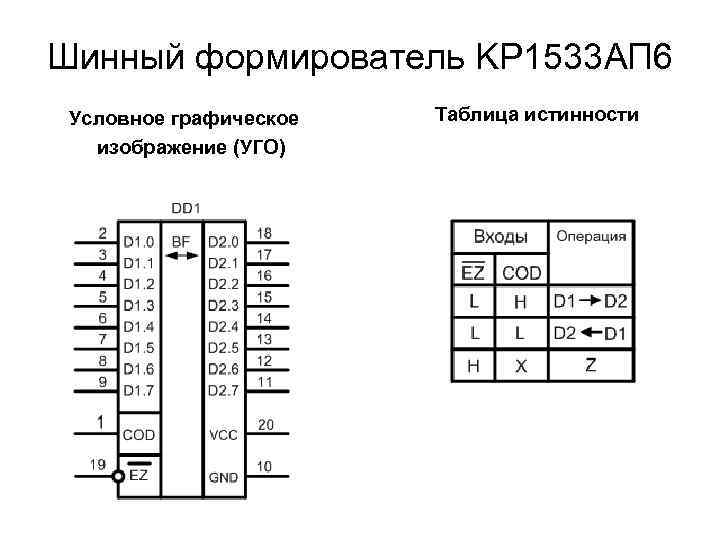

Шинный формирователь KP 1533 АП 6 Условное графическое изображение (УГО) Таблица истинности

Шинный формирователь KP 1533 АП 6 Условное графическое изображение (УГО) Таблица истинности

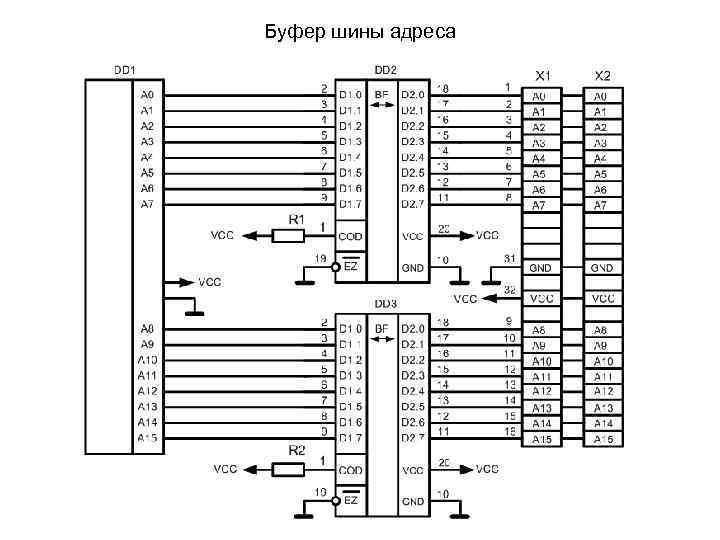

Буфер шины адреса

Буфер шины адреса

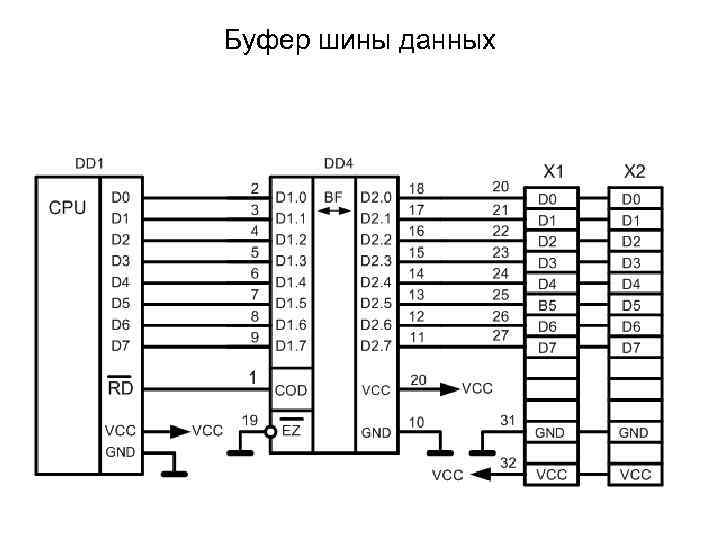

Буфер шины данных

Буфер шины данных

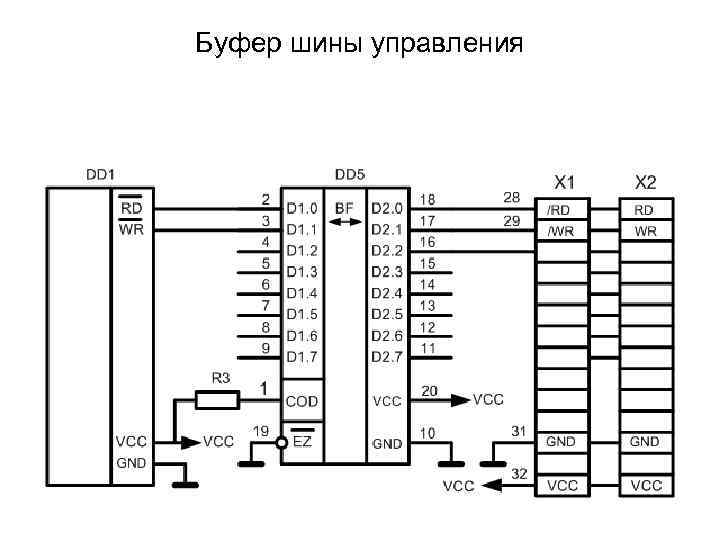

Буфер шины управления

Буфер шины управления

Сигнал выбора устройства Для выбора конкретного внешнего устройства, на основе адреса этого устройства, вырабатывается сигнал разрешающий его работу: /CE – Chip Enable (разрешение кристалла) Или /CS – Chip Select (выбор кристалла) Но при этом выходы устройств ввода по прежнему находятся в Z-состоянии

Сигнал выбора устройства Для выбора конкретного внешнего устройства, на основе адреса этого устройства, вырабатывается сигнал разрешающий его работу: /CE – Chip Enable (разрешение кристалла) Или /CS – Chip Select (выбор кристалла) Но при этом выходы устройств ввода по прежнему находятся в Z-состоянии

Сигнал активации линий ввода-вывода устройства Для активации линий ввода-вывода устройства на основе адреса этого устройств и сигналов /RD и /WR вырабатывается сигнал: /OE – Output Enable (разрешение выхода)

Сигнал активации линий ввода-вывода устройства Для активации линий ввода-вывода устройства на основе адреса этого устройств и сигналов /RD и /WR вырабатывается сигнал: /OE – Output Enable (разрешение выхода)

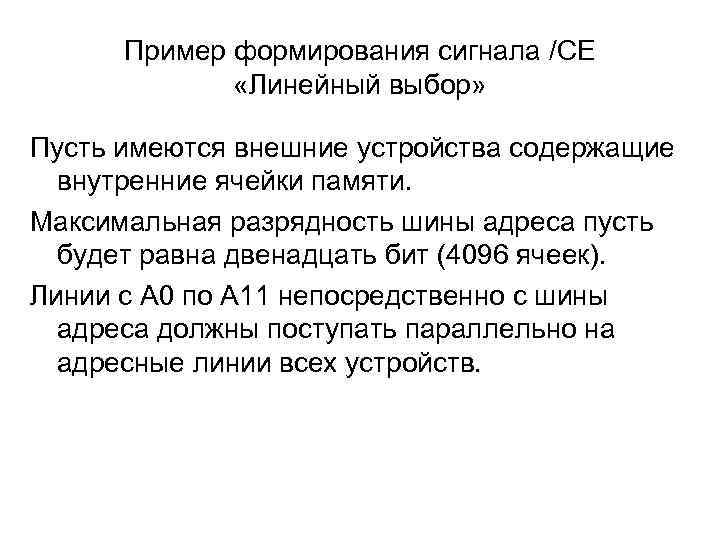

Пример формирования сигнала /CE «Линейный выбор» Пусть имеются внешние устройства содержащие внутренние ячейки памяти. Максимальная разрядность шины адреса пусть будет равна двенадцать бит (4096 ячеек). Линии с А 0 по А 11 непосредственно с шины адреса должны поступать параллельно на адресные линии всех устройств.

Пример формирования сигнала /CE «Линейный выбор» Пусть имеются внешние устройства содержащие внутренние ячейки памяти. Максимальная разрядность шины адреса пусть будет равна двенадцать бит (4096 ячеек). Линии с А 0 по А 11 непосредственно с шины адреса должны поступать параллельно на адресные линии всех устройств.

Следовательно старшие линии шины адреса остались свободными и они могут использоваться для выбора устройств ввода-вывода. Пусть каждый разряд выбирает только одно устройство. Этот разряд должен быть равен нулю (/CE – активен при низком уровне)

Следовательно старшие линии шины адреса остались свободными и они могут использоваться для выбора устройств ввода-вывода. Пусть каждый разряд выбирает только одно устройство. Этот разряд должен быть равен нулю (/CE – активен при низком уровне)

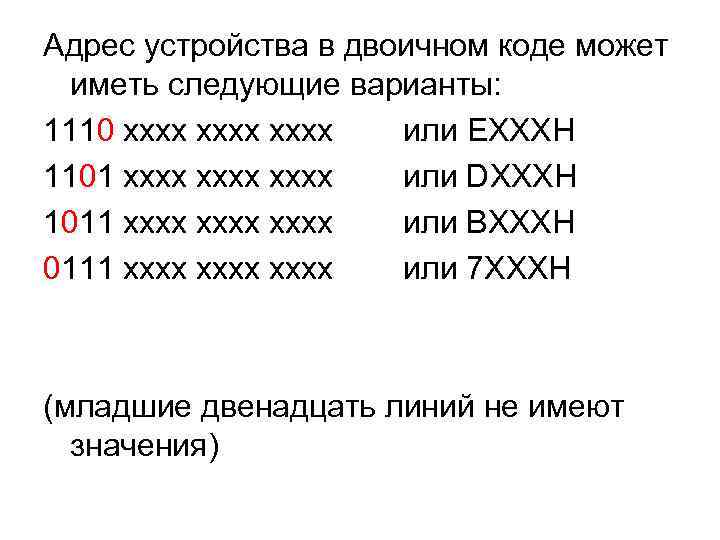

Адрес устройства в двоичном коде может иметь следующие варианты: 1110 xxxx хххх или EXXXH 1101 xxxx хххх или DXXXH 1011 xxxx хххх или BXXXH 0111 xxxx хххх или 7 XXXH (младшие двенадцать линий не имеют значения)

Адрес устройства в двоичном коде может иметь следующие варианты: 1110 xxxx хххх или EXXXH 1101 xxxx хххх или DXXXH 1011 xxxx хххх или BXXXH 0111 xxxx хххх или 7 XXXH (младшие двенадцать линий не имеют значения)

Формирование сигнала /CE (линейный выбор)

Формирование сигнала /CE (линейный выбор)

Формирование сигнала /OE

Формирование сигнала /OE

Чтение параллельного ПЗУ

Чтение параллельного ПЗУ

Подключение ROM

Подключение ROM

Задание на самоподготовку Разработать схему подключения устройства вывода на базе регистра КР 1533 ИР 37. Условное графическое обозначение и таблица истинности КР 1533 ИР 37 приведены ниже.

Задание на самоподготовку Разработать схему подключения устройства вывода на базе регистра КР 1533 ИР 37. Условное графическое обозначение и таблица истинности КР 1533 ИР 37 приведены ниже.

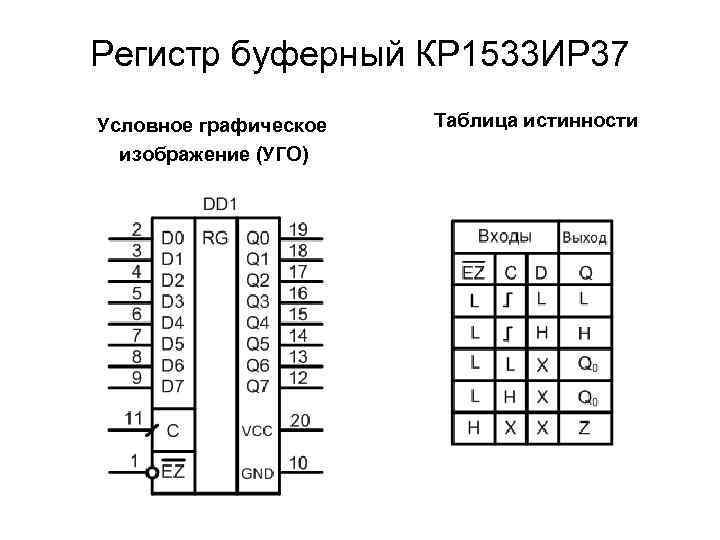

Регистр буферный КР 1533 ИР 37 Условное графическое изображение (УГО) Таблица истинности

Регистр буферный КР 1533 ИР 37 Условное графическое изображение (УГО) Таблица истинности