Архитектура микропроцессора Эльбрус-3М Основные цели проекта Высокая производительность

Архитектура микропроцессора Эльбрус-3М

Основные цели проекта Высокая производительность Вычислительная мощность (параллельные вычисления) Средства поддержки параллельных вычислений Тактовая частота Исполнение двоичных кодов x86 посредством динамической компиляции Совместимость Эффективность Аппаратная поддержка защищенных вычислений (модульного программирования) Диагностика Защита

Вычислительная мощность

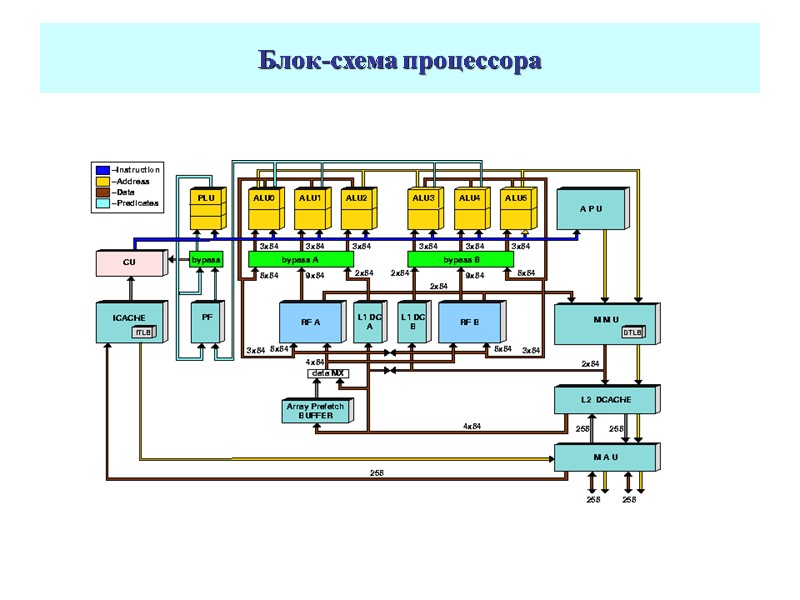

Блок-схема процессора

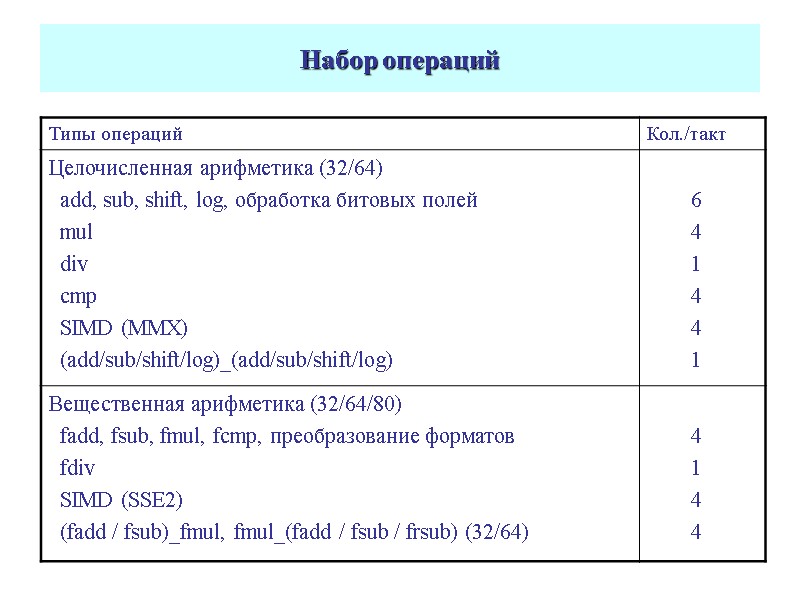

Набор операций

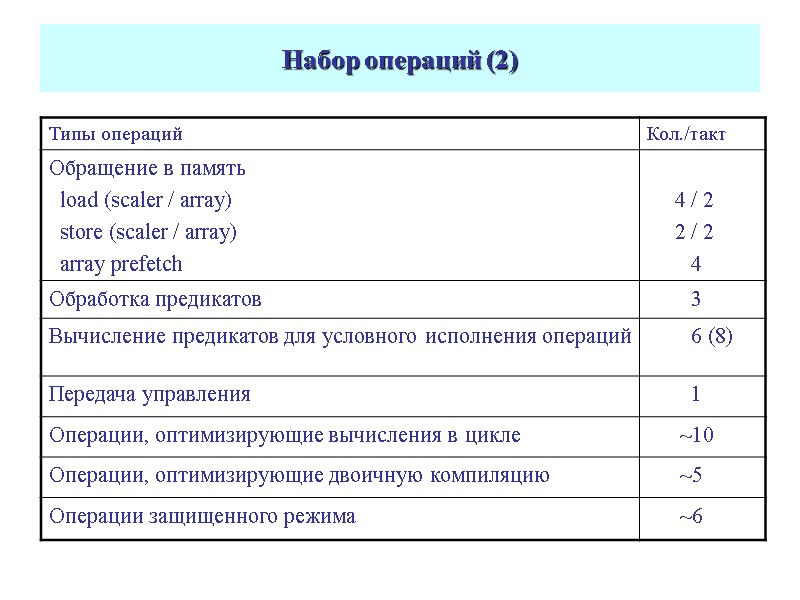

Набор операций (2)

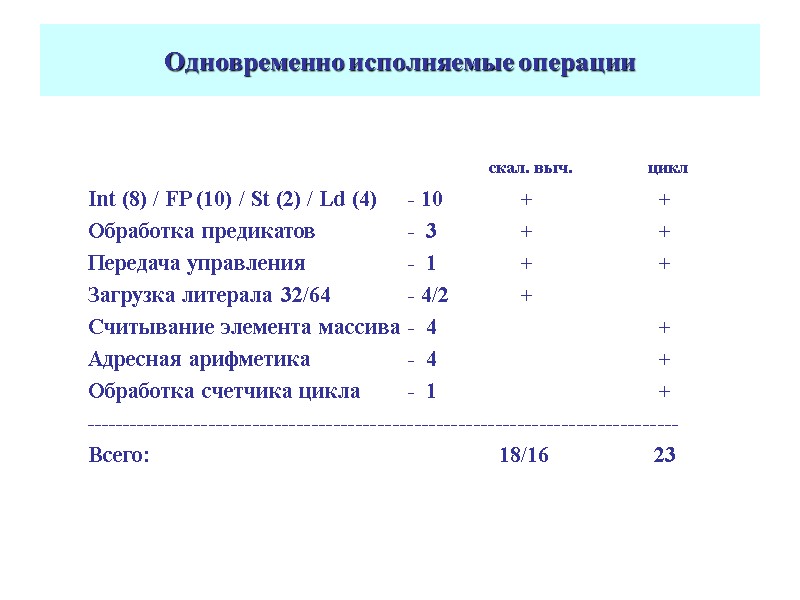

Одновременно исполняемые операции скал. выч. цикл Int (8) / FP (10) / St (2) / Ld (4) - 10 + + Обработка предикатов - 3 + + Передача управления - 1 + + Загрузка литерала 32/64 - 4/2 + Считывание элемента массива - 4 + Адресная арифметика - 4 + Обработка счетчика цикла - 1 + --------------------------------------------------------------------------------- Всего: 18/16 23

Конвейер процессора Целочисленные операции и обращения в L1D$

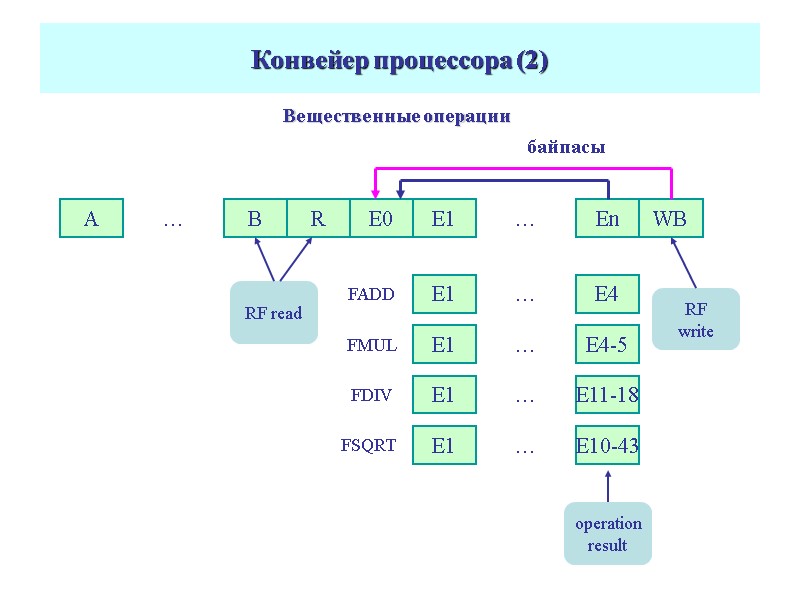

Конвейер процессора (2) Вещественные операции

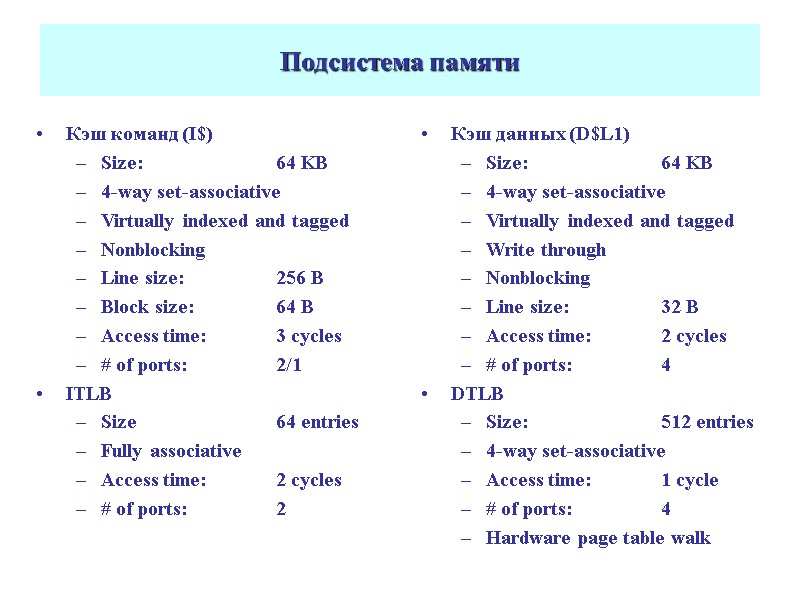

Подсистема памяти Кэш команд (I$) Size: 64 KB 4-way set-associative Virtually indexed and tagged Nonblocking Line size: 256 B Block size: 64 B Access time: 3 cycles # of ports: 2/1 ITLB Size 64 entries Fully associative Access time: 2 cycles # of ports: 2 Кэш данных (D$L1) Size: 64 KB 4-way set-associative Virtually indexed and tagged Write through Nonblocking Line size: 32 B Access time: 2 cycles # of ports: 4 DTLB Size: 512 entries 4-way set-associative Access time: 1 cycle # of ports: 4 Hardware page table walk

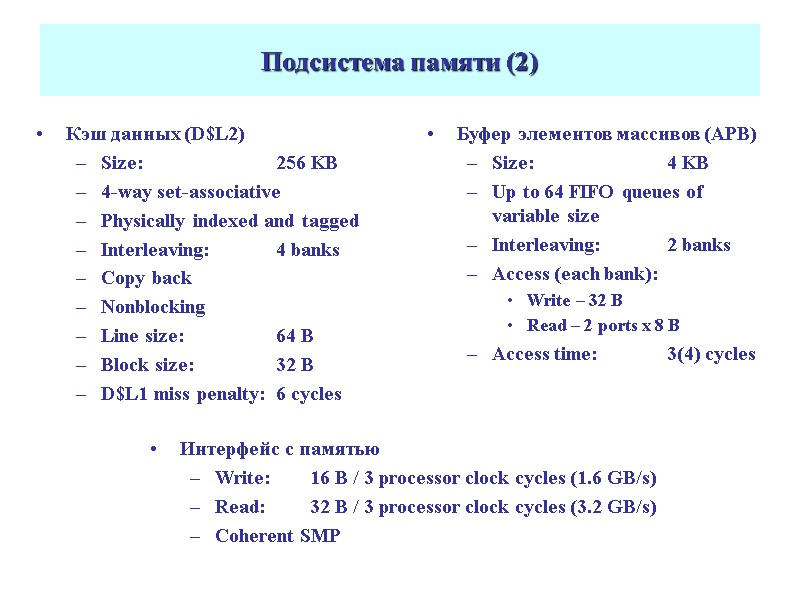

Подсистема памяти (2) Кэш данных (D$L2) Size: 256 KB 4-way set-associative Physically indexed and tagged Interleaving: 4 banks Copy back Nonblocking Line size: 64 B Block size: 32 B D$L1 miss penalty: 6 cycles Буфер элементов массивов (APB) Size: 4 KB Up to 64 FIFO queues of variable size Interleaving: 2 banks Access (each bank): Write – 32 B Read – 2 ports x 8 B Access time: 3(4) cycles Интерфейс с памятью Write: 16 B / 3 processor clock cycles (1.6 GB/s) Read: 32 B / 3 processor clock cycles (3.2 GB/s) Coherent SMP

Средства поддержки параллельных вычислений

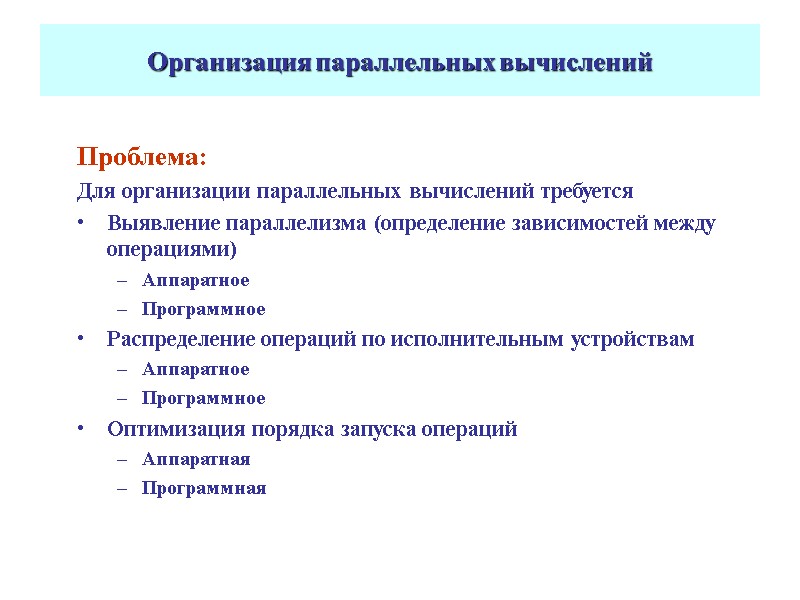

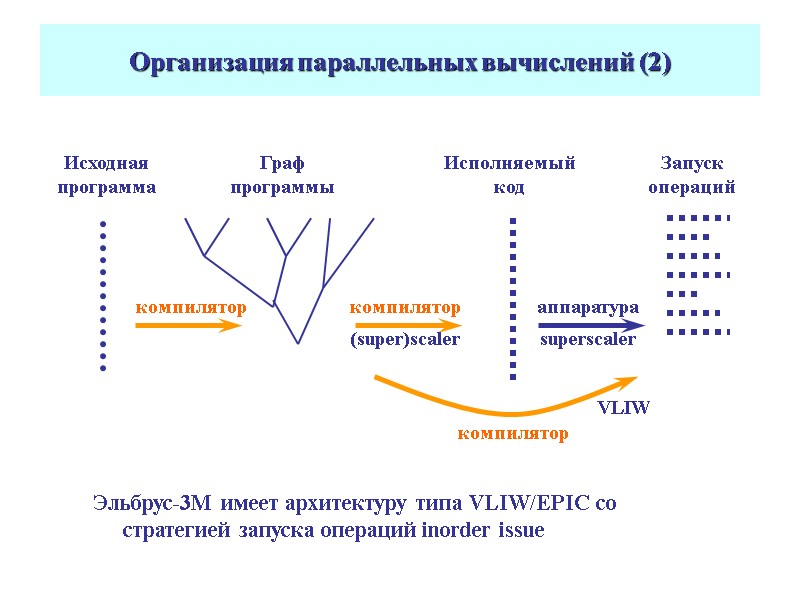

Организация параллельных вычислений Проблема: Для организации параллельных вычислений требуется Выявление параллелизма (определение зависимостей между операциями) Аппаратное Программное Распределение операций по исполнительным устройствам Аппаратное Программное Оптимизация порядка запуска операций Аппаратная Программная

Организация параллельных вычислений (2) Эльбрус-3М имеет архитектуру типа VLIW/EPIC со стратегией запуска операций inorder issue

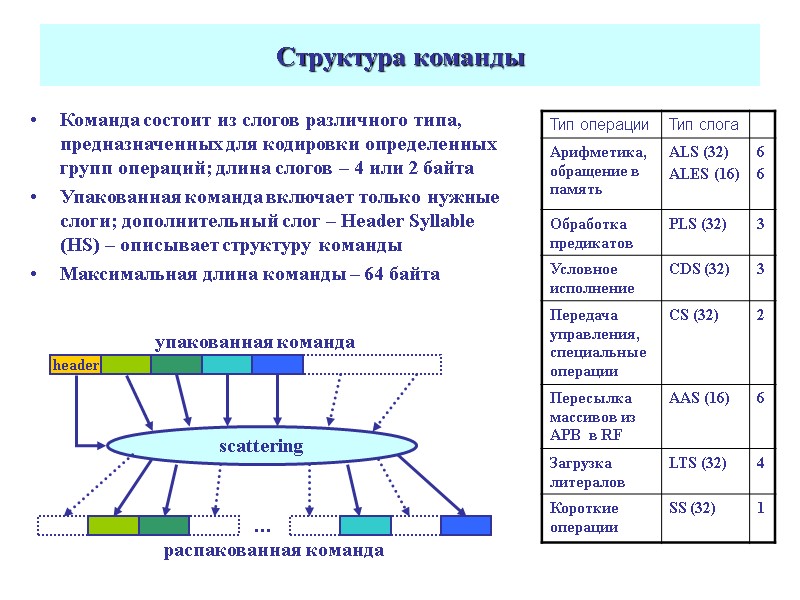

Структура команды Команда состоит из слогов различного типа, предназначенных для кодировки определенных групп операций; длина слогов – 4 или 2 байта Упакованная команда включает только нужные слоги; дополнительный слог – Header Syllable (HS) – описывает структуру команды Максимальная длина команды – 64 байта

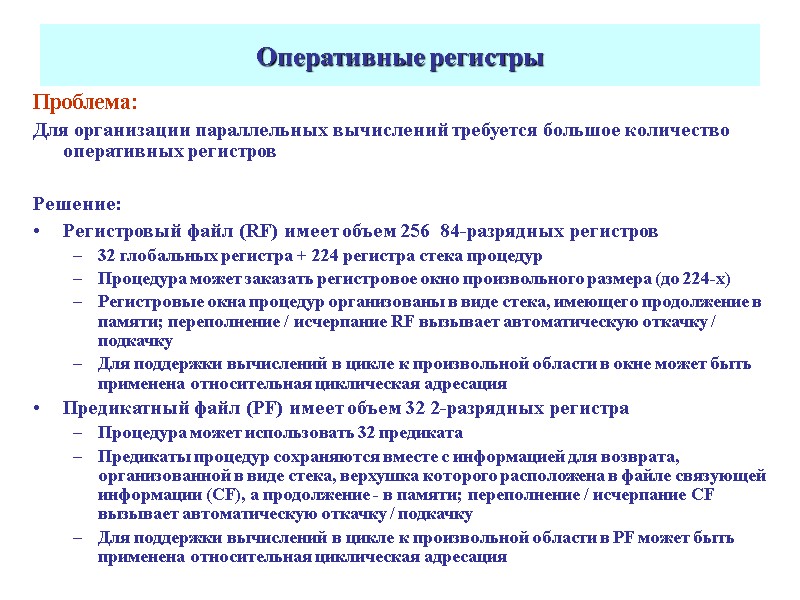

Оперативные регистры Проблема: Для организации параллельных вычислений требуется большое количество оперативных регистров Решение: Регистровый файл (RF) имеет объем 256 84-разрядных регистров 32 глобальных регистра + 224 регистра стека процедур Процедура может заказать регистровое окно произвольного размера (до 224-х) Регистровые окна процедур организованы в виде стека, имеющего продолжение в памяти; переполнение / исчерпание RF вызывает автоматическую откачку / подкачку Для поддержки вычислений в цикле к произвольной области в окне может быть применена относительная циклическая адресация Предикатный файл (PF) имеет объем 32 2-разрядных регистра Процедура может использовать 32 предиката Предикаты процедур сохраняются вместе с информацией для возврата, организованной в виде стека, верхушка которого расположена в файле связующей информации (CF), а продолжение - в памяти; переполнение / исчерпание CF вызывает автоматическую откачку / подкачку Для поддержки вычислений в цикле к произвольной области в PF может быть применена относительная циклическая адресация

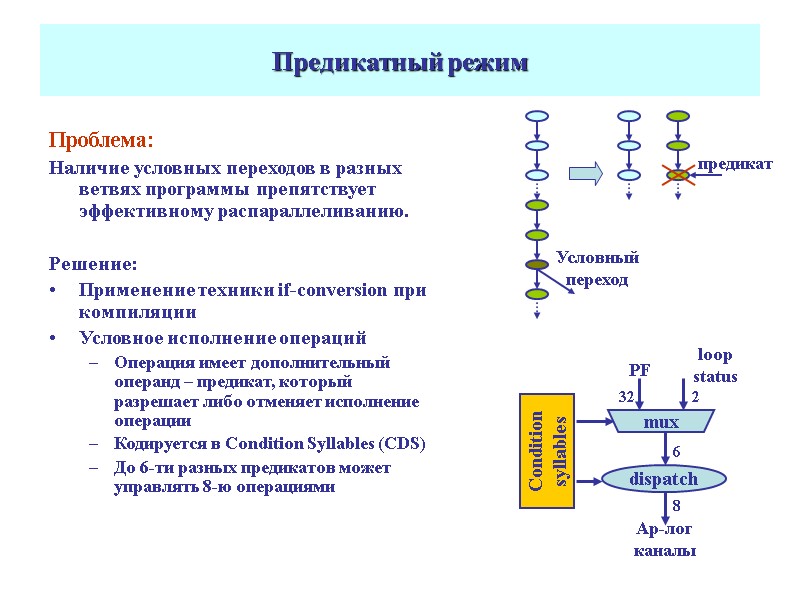

Предикатный режим Проблема: Наличие условных переходов в разных ветвях программы препятствует эффективному распараллеливанию. Решение: Применение техники if-conversion при компиляции Условное исполнение операций Операция имеет дополнительный операнд – предикат, который разрешает либо отменяет исполнение операции Кодируется в Condition Syllables (CDS) До 6-ти разных предикатов может управлять 8-ю операциями

Спекулятивный режим Проблема: Параллелизм вычислений предполагает изменение порядка исполнения операций по сравнению с исходной программой. Требуется механизм восстановления последовательности обработки прерываний. Решение: Техника отложенного прерывания Специальный механизм накапливания замаскированных особых ситуаций вещественной арифметики

Спекулятивный режим (2) Большинство операций имеет спекулятивный режим исполнения Любой операнд в RF, PF и памяти может быть помечен (дополнительными битами) как диагностический тип (DT) Спекулятивная операция, встретившая особую ситуацию, вместо прерывания в качестве результата вырабатывает DT Спекулятивная операция, получившая DT в качестве операнда, также возвращает DT, тем самым транслируя прерывание по спекулятивной ветви По окончании спекулятивной ветви проверяется тип ее результата: Неспекулятивная операция, получившая операнд типа DT, выдает прерывание; через обработчик управление передается на компенсирующий код Условный переход на компенсирующий код Trap handler Recovery code exception DT DT DT 2) 1) спекулятивные операции

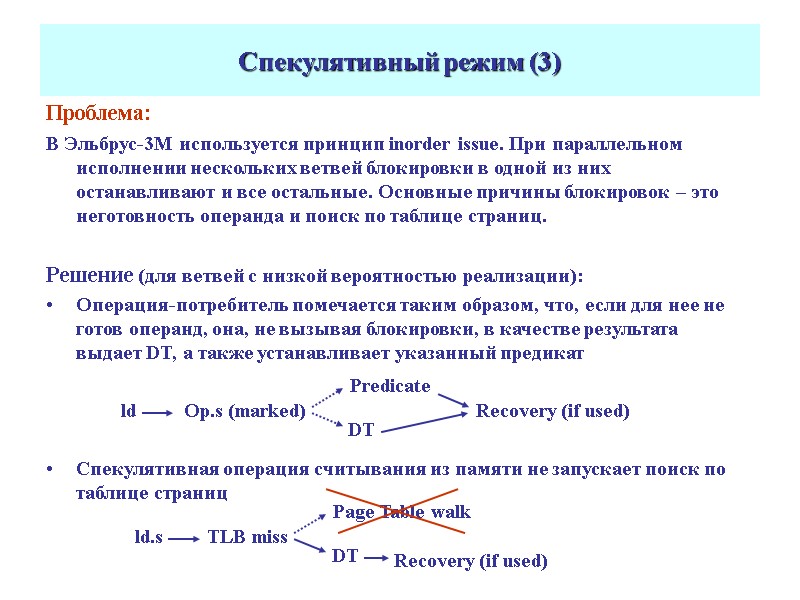

Проблема: В Эльбрус-3М используется принцип inorder issue. При параллельном исполнении нескольких ветвей блокировки в одной из них останавливают и все остальные. Основные причины блокировок – это неготовность операнда и поиск по таблице страниц. Решение (для ветвей с низкой вероятностью реализации): Операция-потребитель помечается таким образом, что, если для нее не готов операнд, она, не вызывая блокировки, в качестве результата выдает DT, а также устанавливает указанный предикат Спекулятивная операция считывания из памяти не запускает поиск по таблице страниц Спекулятивный режим (3)

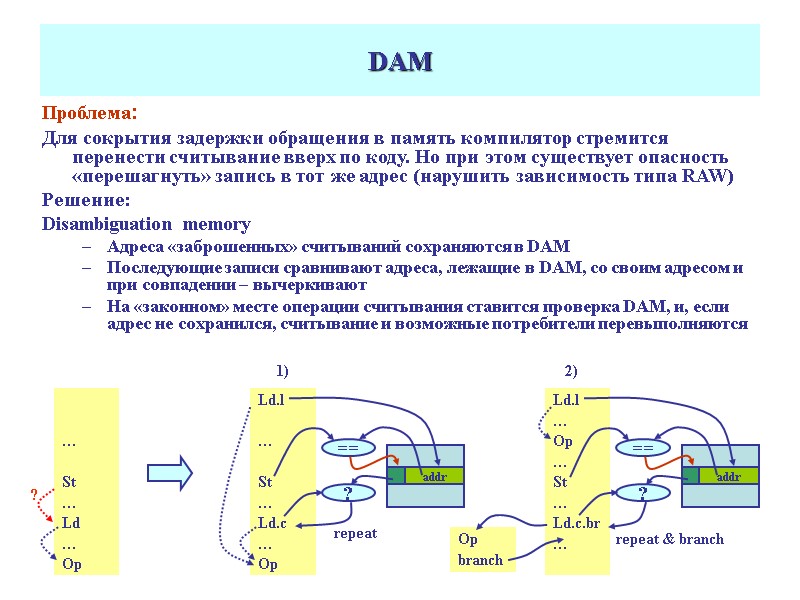

DAM Проблема: Для сокрытия задержки обращения в память компилятор стремится перенести считывание вверх по коду. Но при этом существует опасность «перешагнуть» запись в тот же адрес (нарушить зависимость типа RAW) Решение: Disambiguation memory Адреса «заброшенных» считываний сохраняются в DAM Последующие записи сравнивают адреса, лежащие в DAM, со своим адресом и при совпадении – вычеркивают На «законном» месте операции считывания ставится проверка DAM, и, если адрес не сохранился, считывание и возможные потребители перевыполняются

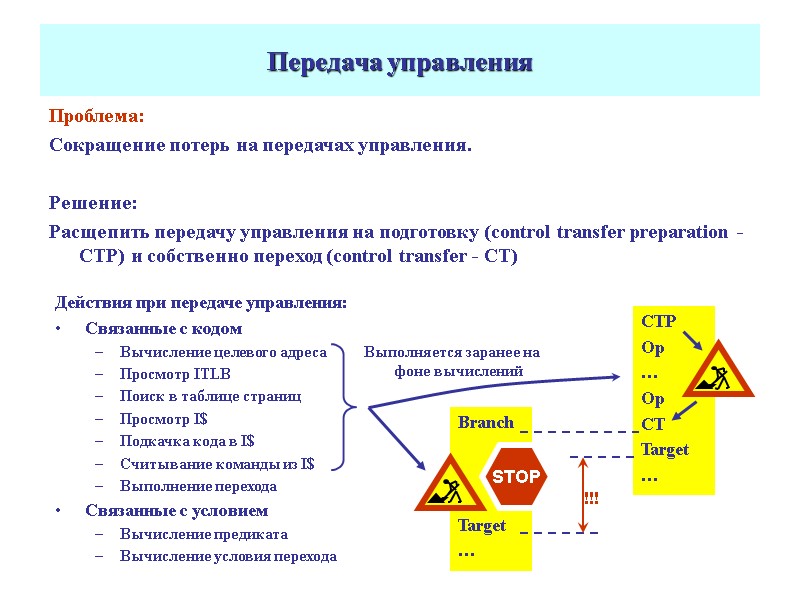

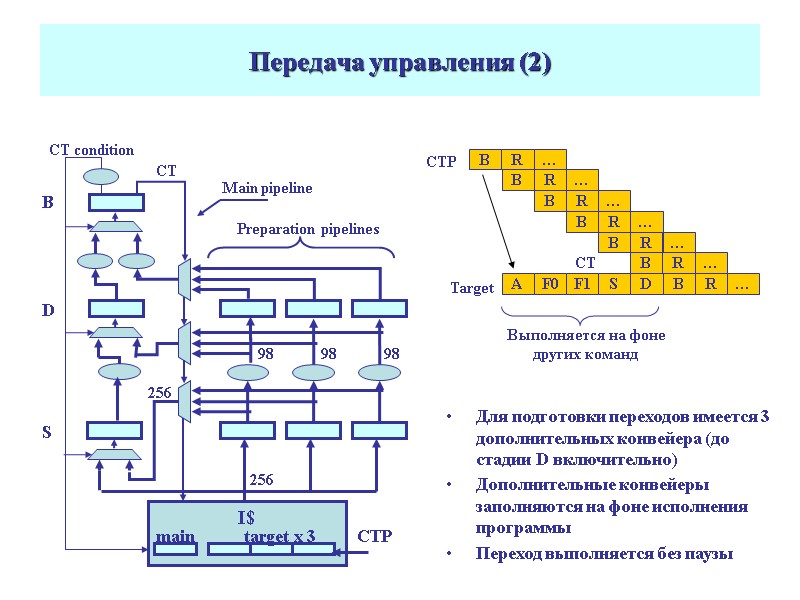

Передача управления Проблема: Сокращение потерь на передачах управления. Решение: Расщепить передачу управления на подготовку (control transfer preparation - CTP) и собственно переход (control transfer - CT) Действия при передаче управления: Связанные с кодом Вычисление целевого адреса Просмотр ITLB Поиск в таблице страниц Просмотр I$ Подкачка кода в I$ Считывание команды из I$ Выполнение перехода Связанные с условием Вычисление предиката Вычисление условия перехода Выполняется заранее на фоне вычислений !!!

Передача управления (2) Для подготовки переходов имеется 3 дополнительных конвейера (до стадии D включительно) Дополнительные конвейеры заполняются на фоне исполнения программы Переход выполняется без паузы S D CT condition CT Preparation pipelines Main pipeline B CTP target x 3 main 256 98 98 98 256

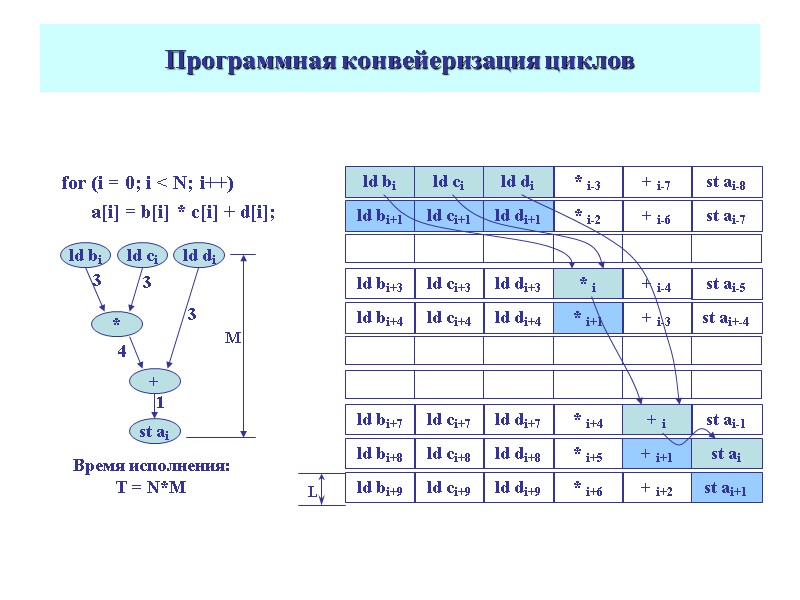

Программная конвейеризация циклов L

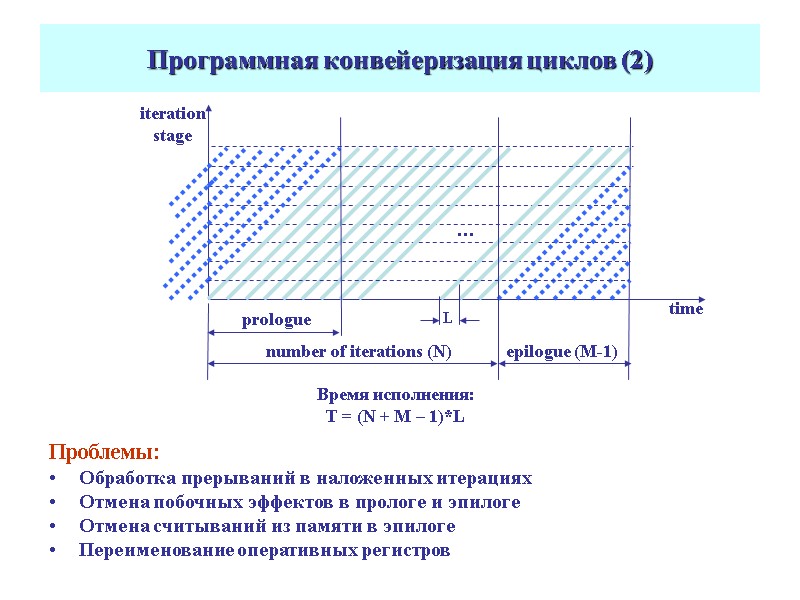

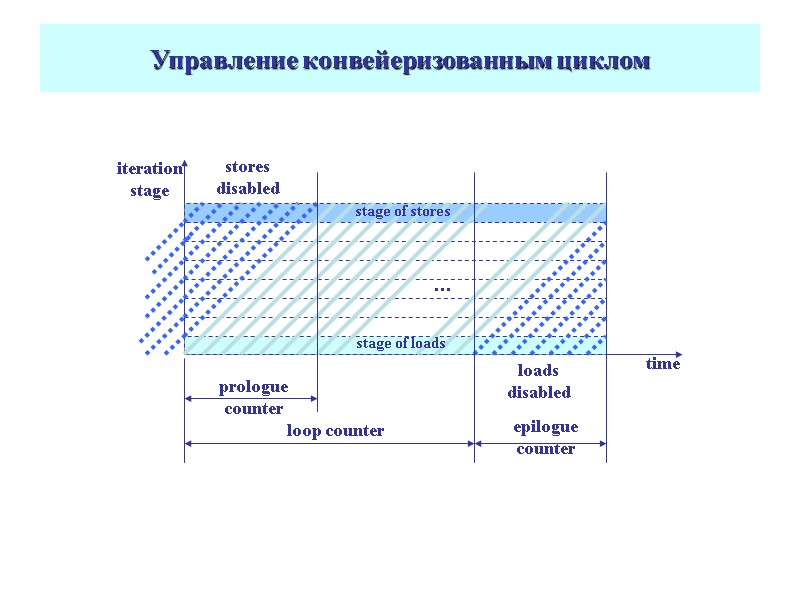

Программная конвейеризация циклов (2) Проблемы: Обработка прерываний в наложенных итерациях Отмена побочных эффектов в прологе и эпилоге Отмена считываний из памяти в эпилоге Переименование оперативных регистров … prologue epilogue (M-1) number of iterations (N) iteration stage time Время исполнения: T = (N + M – 1)*L L

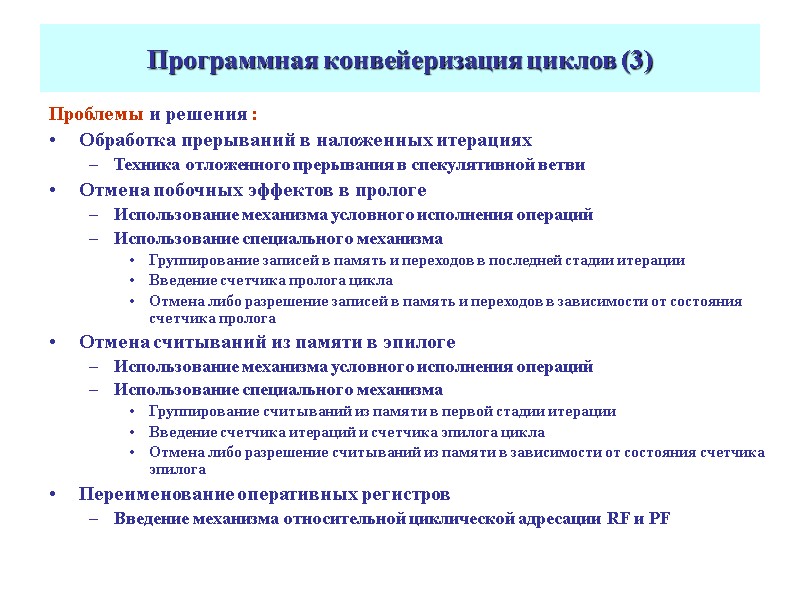

Программная конвейеризация циклов (3) Проблемы и решения : Обработка прерываний в наложенных итерациях Техника отложенного прерывания в спекулятивной ветви Отмена побочных эффектов в прологе Использование механизма условного исполнения операций Использование специального механизма Группирование записей в память и переходов в последней стадии итерации Введение счетчика пролога цикла Отмена либо разрешение записей в память и переходов в зависимости от состояния счетчика пролога Отмена считываний из памяти в эпилоге Использование механизма условного исполнения операций Использование специального механизма Группирование считываний из памяти в первой стадии итерации Введение счетчика итераций и счетчика эпилога цикла Отмена либо разрешение считываний из памяти в зависимости от состояния счетчика эпилога Переименование оперативных регистров Введение механизма относительной циклической адресации RF и PF

Управление конвейеризованным циклом

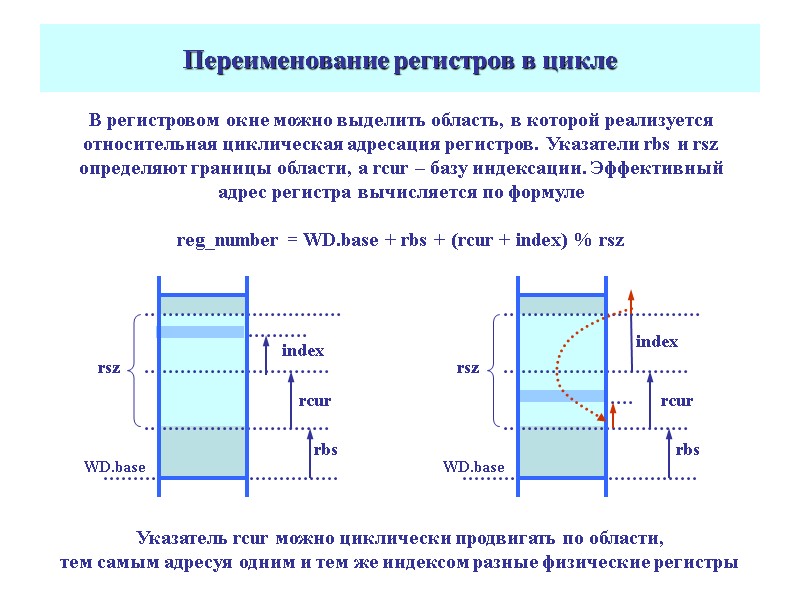

Переименование регистров в цикле В регистровом окне можно выделить область, в которой реализуется относительная циклическая адресация регистров. Указатели rbs и rsz определяют границы области, а rcur – базу индексации. Эффективный адрес регистра вычисляется по формуле reg_number = WD.base + rbs + (rcur + index) % rsz Указатель rcur можно циклически продвигать по области, тем самым адресуя одним и тем же индексом разные физические регистры

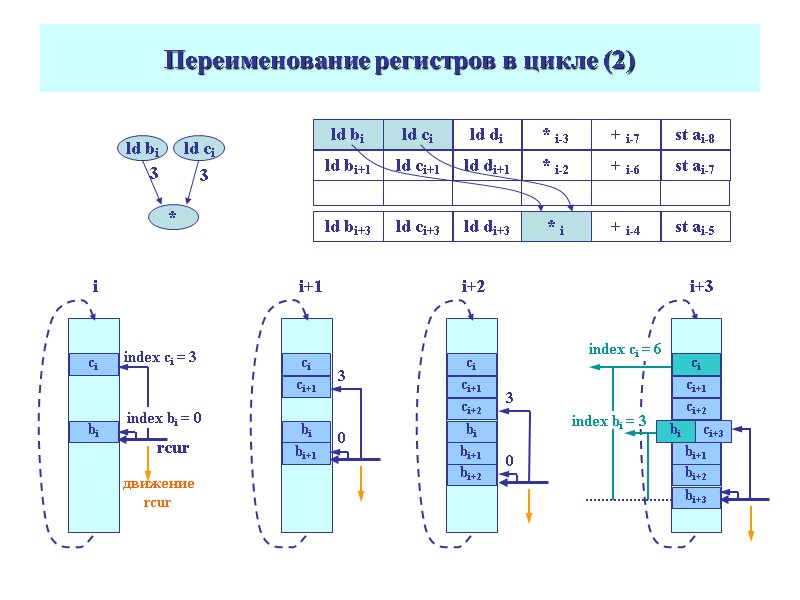

Переименование регистров в цикле (2) i i+3 i+2 i+1

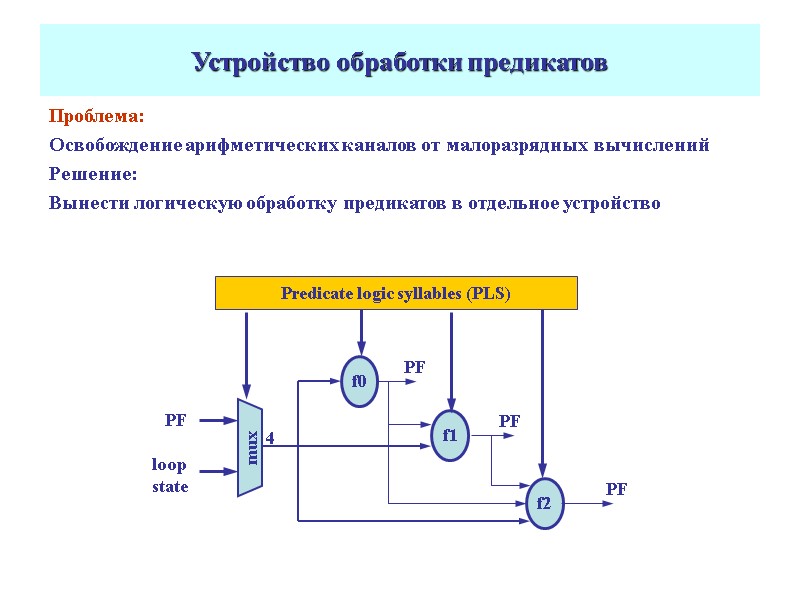

Устройство обработки предикатов Проблема: Освобождение арифметических каналов от малоразрядных вычислений Решение: Вынести логическую обработку предикатов в отдельное устройство

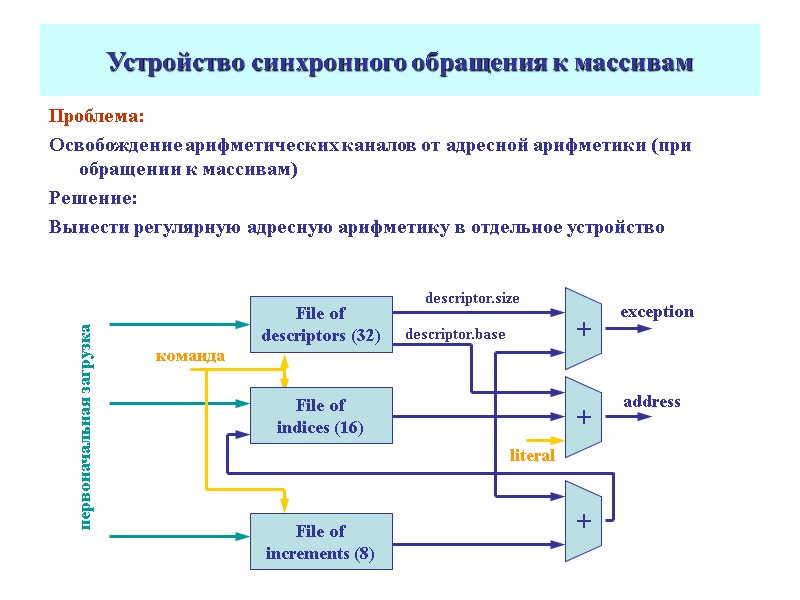

Устройство синхронного обращения к массивам Проблема: Освобождение арифметических каналов от адресной арифметики (при обращении к массивам) Решение: Вынести регулярную адресную арифметику в отдельное устройство

Предварительная подкачка массивов Проблемы: Массивы расположены в оперативной памяти, имеющей большое время доступа Длительность обращения в память статически не известна Техника «забрасывания» считываний вверх по коду требует большого количества оперативных регистров Предварительная подкачка элементов массивов в кэш вытесняет потенциально полезное содержимое Решение: Введение специализированного устройства предварительной подкачки массивов (AAU), имеющего следующие свойства: Перед началом цикла устройство программируется (адреса массивов, шаги, etc) Устройство работает асинхронно по отношению к основной программе Устройство обращается в память группрвыми запросами Устройство имеет «простой» специализированный буфер (APB) для временного хранения элементов массивов По требованию основной программы нужные элементы массивов переписываются из буфера в регистровый файл

Предварительная подкачка массивов (2)

Предварительная подкачка массивов (3) Memory subsystem literal + size base address exception current indices (32) + + Buffer for asynchronous program (32) RF x2 4x8B 2x8B Считывание из основной программы 2x8B Логическое деление буфера: FIFO на каждый массив (32) x2

Резюме Эльбрус-3М имеет архитектуру VLIW со статическим планированием вычислений Аппаратура освобождена от функций выявления межоперационных зависимостей и распараллеливания вычислений – их выполняет компилятор В архитектуре предусмотрены специальные операции, режимы и механизмы, позволяющие сочетать эффективное статическое планирование с обработкой динамических ситуаций Условное выполнение операций Спекулятивное выполнение операций Отложенное прерывание Пропуск операций с неготовыми операндами Пропуск операций обращения в память, потребовавших поиска в Таблице Страниц Поддержка «забрасывания» считываний из памяти выше потенциально конфликтующих записей

Резюме (2) В архитектуре большое внимание уделено эффективности типовых вычислительных конструкций, влияющих на производительность системы Стековая организация регистровых окон процедур с автоматической пересылкой в память и из памяти Техника подготовки передач управления Техника программной предварительной подкачки данных в кэш-память Специализированное устройство для булевских вычислений (освобождение ALU от малоразрядных вычислений) Поддержка вычислений в цикле Предварительная подкачка массивов в специализированный буфер Специализированное устройство регулярной адресной арифметики (освобождение ALU от «сервисных» функций) Поддержка программной конвейеризации циклов (освобождение механизма условного выполнения от «сервисных» функций) Техника циклического переименования регистров

?

36138-arch_e3m.ppt

- Количество слайдов: 37