fafe4944892ff6ae56fbb7110bf3c6ed.ppt

- Количество слайдов: 43

Архитектура и програмирање микропроцесора Intel 8086 p p p Историјат развоја Модел процесора 8086 Програмски модел Организација меморије Адресни начини рада

Архитектура и програмирање микропроцесора Intel 8086 p p p Историјат развоја Модел процесора 8086 Програмски модел Организација меморије Адресни начини рада

Историјат развоја 1971. први микропроцесор уопште: четворобитни Intel 4004. p Нешто касније и осмобитни процесор 8008, а затим и осмобитни следбеници 8080 (1973) и 8085 (1977). p Први 16 -битни микропроцесор уопште је Intel 8086 (1978). p Током наредних 20 -так година следила је серија све моћнијих микропроцесора, како Intel-ових тако и других произвођача. p

Историјат развоја 1971. први микропроцесор уопште: четворобитни Intel 4004. p Нешто касније и осмобитни процесор 8008, а затим и осмобитни следбеници 8080 (1973) и 8085 (1977). p Први 16 -битни микропроцесор уопште је Intel 8086 (1978). p Током наредних 20 -так година следила је серија све моћнијих микропроцесора, како Intel-ових тако и других произвођача. p

Историјат развоја Intel је код свих процесора задржао компатибилност! p Из тих разлога, проучавање процесора 8086 је важно као родоначелника касније серије 80 x 86. p Скуп инструкција овог процесора може се посматрати као подскупа инструкција наредних генерација. p

Историјат развоја Intel је код свих процесора задржао компатибилност! p Из тих разлога, проучавање процесора 8086 је важно као родоначелника касније серије 80 x 86. p Скуп инструкција овог процесора може се посматрати као подскупа инструкција наредних генерација. p

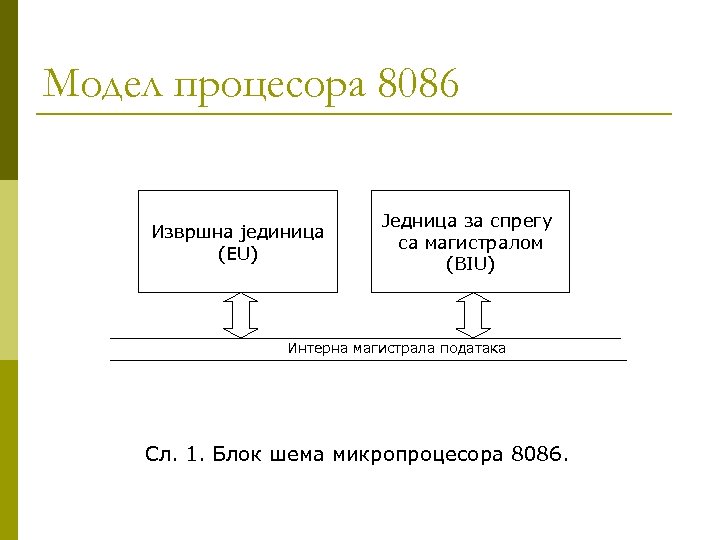

Модел процесора 8086 Извршна јединица (EU) Једница за спрегу са магистралом (BIU) Интерна магистрала података Сл. 1. Блок шема микропроцесора 8086.

Модел процесора 8086 Извршна јединица (EU) Једница за спрегу са магистралом (BIU) Интерна магистрала података Сл. 1. Блок шема микропроцесора 8086.

Модел процесора 8086 p Микропроцесор 8086 организован је у две јединице (сл. 1): n n Извршна јединица (EU – Execution Unit). Једница за спрегу са магистралом (BIU – Bus Interface Unit).

Модел процесора 8086 p Микропроцесор 8086 организован је у две јединице (сл. 1): n n Извршна јединица (EU – Execution Unit). Једница за спрегу са магистралом (BIU – Bus Interface Unit).

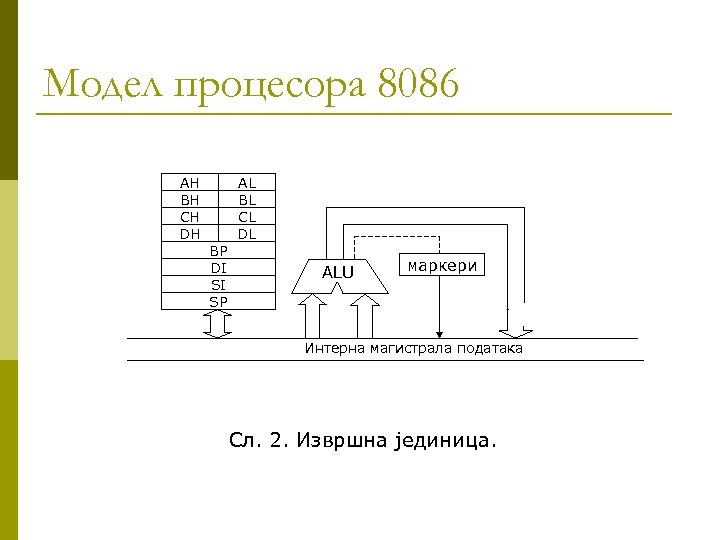

Модел процесора 8086 AH BH CH DH AL BL CL DL BP DI SI SP ALU маркери Интерна магистрала података Сл. 2. Извршна јединица.

Модел процесора 8086 AH BH CH DH AL BL CL DL BP DI SI SP ALU маркери Интерна магистрала података Сл. 2. Извршна јединица.

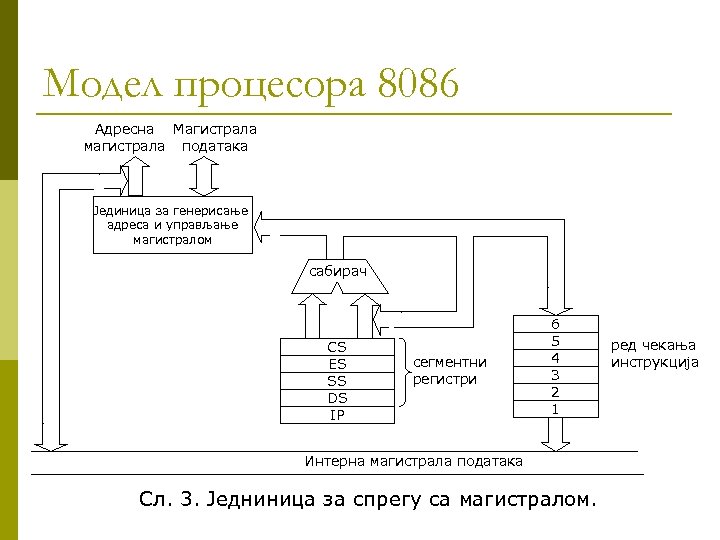

Модел процесора 8086 Адресна Магистрала магистрала података Јединица за генерисање адреса и управљање магистралом сабирач CS ES SS DS IP сегментни регистри 6 5 4 3 2 1 Интерна магистрала података Сл. 3. Једниница за спрегу са магистралом. ред чекања инструкција

Модел процесора 8086 Адресна Магистрала магистрала података Јединица за генерисање адреса и управљање магистралом сабирач CS ES SS DS IP сегментни регистри 6 5 4 3 2 1 Интерна магистрала података Сл. 3. Једниница за спрегу са магистралом. ред чекања инструкција

Модел процесора 8086 BIU преко адресне магистрале и магистрале података обезбеђује спрегу процесора са меморијским и У/И подсистемом а преко интерне магистрале са функционалним јединицама процесора. p EU прихвата кодове инструкција од BIU, извршава инструкције и смешта резултате у интерне регистре. Преко BIU ови резултати могу се сместити у меморију или послати на излаз. p

Модел процесора 8086 BIU преко адресне магистрале и магистрале података обезбеђује спрегу процесора са меморијским и У/И подсистемом а преко интерне магистрале са функционалним јединицама процесора. p EU прихвата кодове инструкција од BIU, извршава инструкције и смешта резултате у интерне регистре. Преко BIU ови резултати могу се сместити у меморију или послати на излаз. p

Модел процесора 8086 p p У току рада између BIU и EU постоји преклапање у обављању њихових задатака. Активности ове две јединице могу се описати на следећи начин: 1. 2. BIU поставља IP на адресну магистралу и прибавља реч/бајт из меморије. IP се инкрементира (колико – то зависи од обима инструкције),

Модел процесора 8086 p p У току рада између BIU и EU постоји преклапање у обављању њихових задатака. Активности ове две јединице могу се описати на следећи начин: 1. 2. BIU поставља IP на адресну магистралу и прибавља реч/бајт из меморије. IP се инкрементира (колико – то зависи од обима инструкције),

Модел процесора 8086 3. 4. 5. Инструкција прихваћена од стране BIU смешта се у ред чекања. Ако је ред чекања био празан EU одмах добавља ту инструкцију и почиње да је извршава. Док EU извршава инструкцију BIU прибавља наредну инструкцију. У зависности од времена извршења прве инструкције, BIU може да попуни ред чекања са неколико нових инструкција пре него EU буде спремна на изврши наредну.

Модел процесора 8086 3. 4. 5. Инструкција прихваћена од стране BIU смешта се у ред чекања. Ако је ред чекања био празан EU одмах добавља ту инструкцију и почиње да је извршава. Док EU извршава инструкцију BIU прибавља наредну инструкцију. У зависности од времена извршења прве инструкције, BIU може да попуни ред чекања са неколико нових инструкција пре него EU буде спремна на изврши наредну.

Модел процесора 8086 p Постоје 3 разлога која могу да уведу EU у стање чекања (wait mode): 1. 2. 3. Инструкција захтева приступ меморијској локацији која није у реу чекања. Код инструкција типа jump ред чекања се празни и потом поново пуни инструкцијама почев од циљне адресе гранања. EU извршава “спору” инструкцију.

Модел процесора 8086 p Постоје 3 разлога која могу да уведу EU у стање чекања (wait mode): 1. 2. 3. Инструкција захтева приступ меморијској локацији која није у реу чекања. Код инструкција типа jump ред чекања се празни и потом поново пуни инструкцијама почев од циљне адресе гранања. EU извршава “спору” инструкцију.

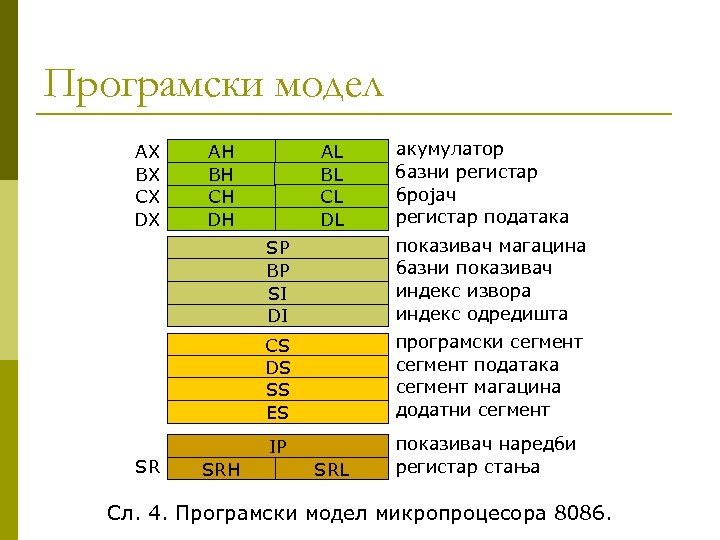

Програмски модел микропроцесора приказује типове интерних регистара доступних програмеру. p При томе, показивач инструкција IP није доступан програмеру директно и у суштини је део BIU. p

Програмски модел микропроцесора приказује типове интерних регистара доступних програмеру. p При томе, показивач инструкција IP није доступан програмеру директно и у суштини је део BIU. p

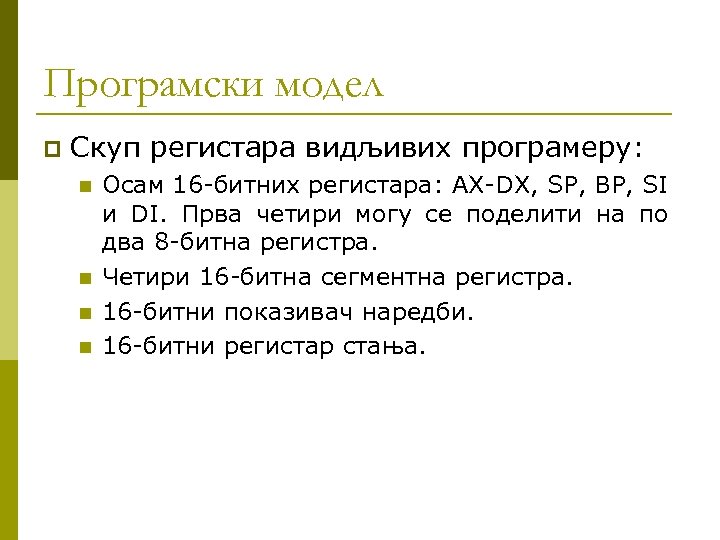

Програмски модел p Скуп регистара видљивих програмеру: n n Осам 16 -битних регистара: AX-DX, SP, BP, SI и DI. Прва четири могу се поделити на по два 8 -битна регистра. Четири 16 -битна сегментна регистра. 16 -битни показивач наредби. 16 -битни регистар стања.

Програмски модел p Скуп регистара видљивих програмеру: n n Осам 16 -битних регистара: AX-DX, SP, BP, SI и DI. Прва четири могу се поделити на по два 8 -битна регистра. Четири 16 -битна сегментна регистра. 16 -битни показивач наредби. 16 -битни регистар стања.

Програмски модел AX BX CX DX AL BL CL DL AH BH CH DH акумулатор базни регистар бројач регистар података SP BP SI DI CS DS SS ES SR програмски сегмент података сегмент магацина додатни сегмент IP SRH показивач магацина базни показивач индекс извора индекс одредишта показивач наредби регистар стања SRL Сл. 4. Програмски модел микропроцесора 8086.

Програмски модел AX BX CX DX AL BL CL DL AH BH CH DH акумулатор базни регистар бројач регистар података SP BP SI DI CS DS SS ES SR програмски сегмент података сегмент магацина додатни сегмент IP SRH показивач магацина базни показивач индекс извора индекс одредишта показивач наредби регистар стања SRL Сл. 4. Програмски модел микропроцесора 8086.

Програмски модел бит позиција Регистар стања 15 14 13 X X X 12 11 10 9 8 7 6 5 4 3 2 1 0 X OF DF IF TF SF ZF X AF X PF X CF SRH SRL Сл. 5. Распоред маркера у регистру стања.

Програмски модел бит позиција Регистар стања 15 14 13 X X X 12 11 10 9 8 7 6 5 4 3 2 1 0 X OF DF IF TF SF ZF X AF X PF X CF SRH SRL Сл. 5. Распоред маркера у регистру стања.

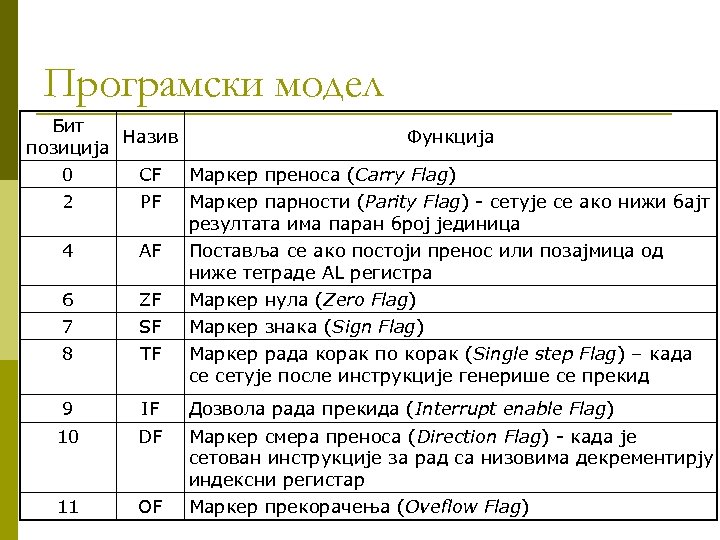

Програмски модел Бит Назив позиција Функција 0 CF Маркер преноса (Carry Flag) 2 PF Маркер парности (Parity Flag) - сетује се ако нижи бајт резултата има паран број јединица 4 AF Поставља се ако постоји пренос или позајмица од ниже тетраде AL регистра 6 ZF Маркер нула (Zero Flag) 7 SF Маркер знака (Sign Flag) 8 TF Маркер рада корак по корак (Single step Flag) – када се сетује после инструкције генерише се прекид 9 IF Дозвола рада прекида (Interrupt enable Flag) 10 DF Маркер смера преноса (Direction Flag) - када је сетован инструкције за рад са низовима декрементирју индексни регистар 11 OF Маркер прекорачења (Oveflow Flag)

Програмски модел Бит Назив позиција Функција 0 CF Маркер преноса (Carry Flag) 2 PF Маркер парности (Parity Flag) - сетује се ако нижи бајт резултата има паран број јединица 4 AF Поставља се ако постоји пренос или позајмица од ниже тетраде AL регистра 6 ZF Маркер нула (Zero Flag) 7 SF Маркер знака (Sign Flag) 8 TF Маркер рада корак по корак (Single step Flag) – када се сетује после инструкције генерише се прекид 9 IF Дозвола рада прекида (Interrupt enable Flag) 10 DF Маркер смера преноса (Direction Flag) - када је сетован инструкције за рад са низовима декрементирју индексни регистар 11 OF Маркер прекорачења (Oveflow Flag)

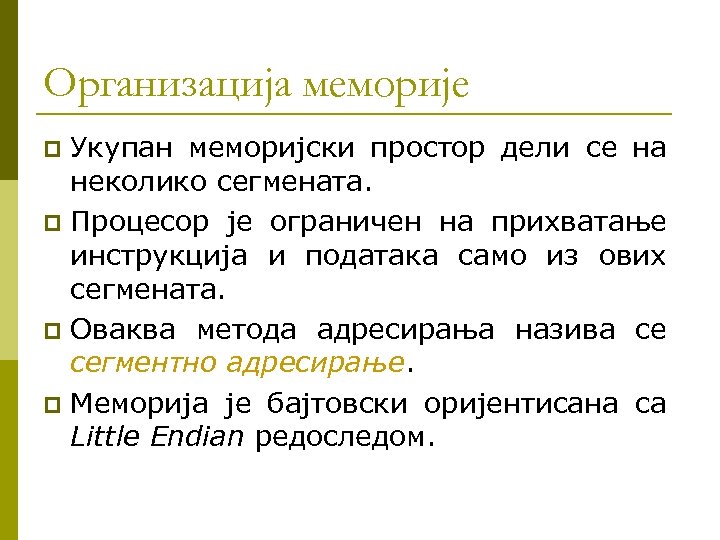

Организација меморије Укупан меморијски простор дели се на неколико сегмената. p Процесор је ограничен на прихватање инструкција и података само из ових сегмената. p Оваква метода адресирања назива се сегментно адресирање. p Меморија је бајтовски оријентисана са Little Endian редоследом. p

Организација меморије Укупан меморијски простор дели се на неколико сегмената. p Процесор је ограничен на прихватање инструкција и података само из ових сегмената. p Оваква метода адресирања назива се сегментно адресирање. p Меморија је бајтовски оријентисана са Little Endian редоследом. p

Организација меморије 8086 има 20 адресних линија што омогућава генерисање 220 различитих адреса (1 МB), тј. адресирање 219 16 битних речи. p Симултани приступ 16 -битним речима из бајтовски оријентисане меморије омогућен је постојањем парне и непарне меморијске банке. p

Организација меморије 8086 има 20 адресних линија што омогућава генерисање 220 различитих адреса (1 МB), тј. адресирање 219 16 битних речи. p Симултани приступ 16 -битним речима из бајтовски оријентисане меморије омогућен је постојањем парне и непарне меморијске банке. p

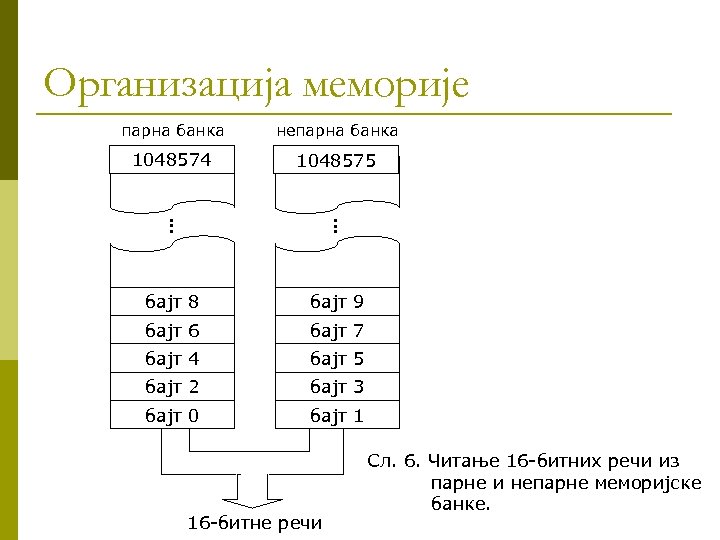

Организација меморије парна банка непарна банка 1048574 1048575 . . . бајт 8 бајт 9 бајт 6 бајт 7 бајт 4 бајт 5 бајт 2 бајт 3 бајт 0 бајт 1 16 -битне речи Сл. 6. Читање 16 -битних речи из парне и непарне меморијске банке.

Организација меморије парна банка непарна банка 1048574 1048575 . . . бајт 8 бајт 9 бајт 6 бајт 7 бајт 4 бајт 5 бајт 2 бајт 3 бајт 0 бајт 1 16 -битне речи Сл. 6. Читање 16 -битних речи из парне и непарне меморијске банке.

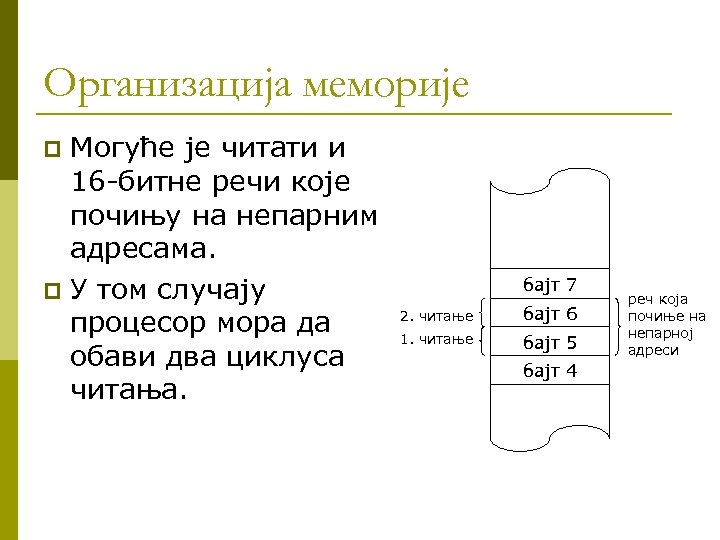

Организација меморије Могуће је читати и 16 -битне речи које почињу на непарним адресама. p У том случају процесор мора да обави два циклуса читања. p бајт 7 2. читање бајт 6 1. читање бајт 5 бајт 4 реч која почиње на непарној адреси

Организација меморије Могуће је читати и 16 -битне речи које почињу на непарним адресама. p У том случају процесор мора да обави два циклуса читања. p бајт 7 2. читање бајт 6 1. читање бајт 5 бајт 4 реч која почиње на непарној адреси

Организација меморије p У оквиру укупног адресног простора од 1 MB микропроцесор 8086 дефинише четири сегмента величине 64 k. B: n n сегмент кода, сегмент магацина, сегмент података и додатни сегмент.

Организација меморије p У оквиру укупног адресног простора од 1 MB микропроцесор 8086 дефинише четири сегмента величине 64 k. B: n n сегмент кода, сегмент магацина, сегмент података и додатни сегмент.

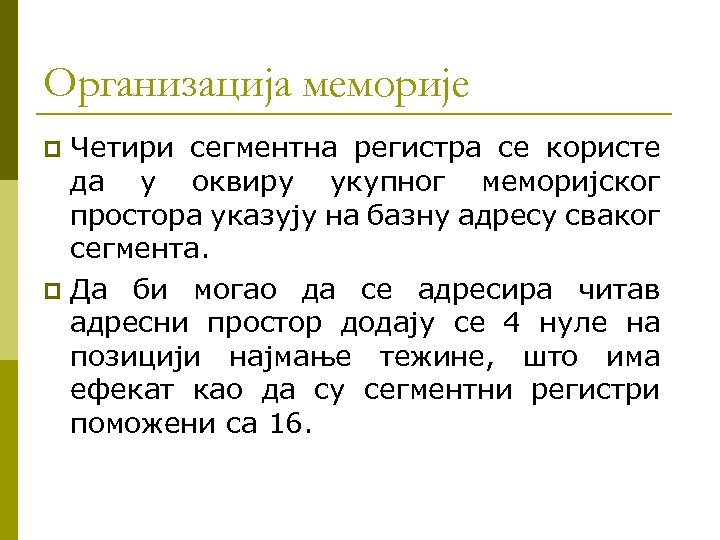

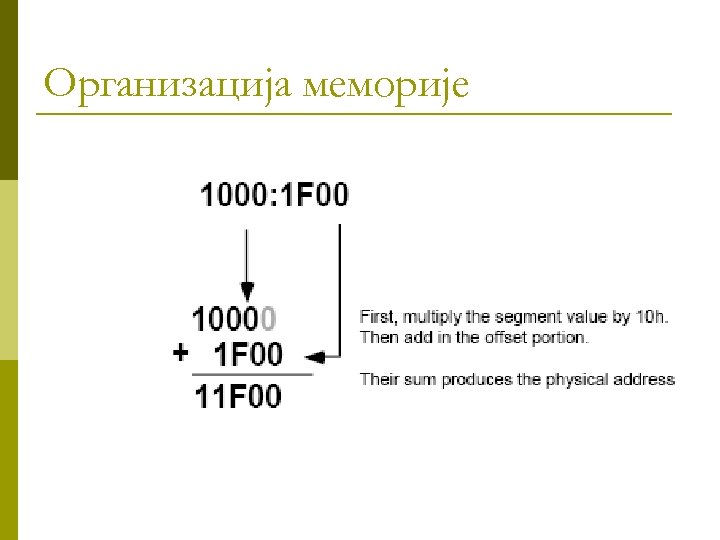

Организација меморије Четири сегментна регистра се користе да у оквиру укупног меморијског простора указују на базну адресу сваког сегмента. p Да би могао да се адресира читав адресни простор додају се 4 нуле на позицији најмање тежине, што има ефекат као да су сегментни регистри поможени са 16. p

Организација меморије Четири сегментна регистра се користе да у оквиру укупног меморијског простора указују на базну адресу сваког сегмента. p Да би могао да се адресира читав адресни простор додају се 4 нуле на позицији најмање тежине, што има ефекат као да су сегментни регистри поможени са 16. p

Организација меморије

Организација меморије

Организација меморије Сегменти се могу делимично или чак потпуно преклапати (CS=DS=ES=SS). p Меморијске локације које не припадају текућем сегменту нису доступне пре редефинисања садржаја сегментних регистара. p

Организација меморије Сегменти се могу делимично или чак потпуно преклапати (CS=DS=ES=SS). p Меморијске локације које не припадају текућем сегменту нису доступне пре редефинисања садржаја сегментних регистара. p

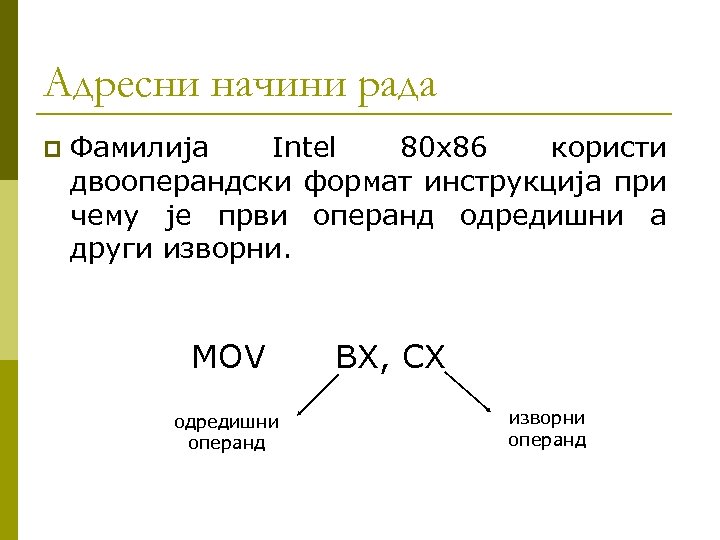

Адресни начини рада p Фамилија Intel 80 x 86 користи двооперандски формат инструкција при чему је први операнд одредишни а други изворни. MOV одредишни операнд BX, CX изворни операнд

Адресни начини рада p Фамилија Intel 80 x 86 користи двооперандски формат инструкција при чему је први операнд одредишни а други изворни. MOV одредишни операнд BX, CX изворни операнд

Адресни начини рада Постоји велики број адресних начина рада (CISC процесор!). p Неки од адресних начина рада присутни су код свих чланова фамилије, а неки тек од процесора 80386 надаље. p Ми ћемо, срећом, да се бавимо само оним начинима адресирања који постоје код 8086. p

Адресни начини рада Постоји велики број адресних начина рада (CISC процесор!). p Неки од адресних начина рада присутни су код свих чланова фамилије, а неки тек од процесора 80386 надаље. p Ми ћемо, срећом, да се бавимо само оним начинима адресирања који постоје код 8086. p

Адресни начини рада p Код 8086 можемо препознати пет врста операнада: n n n регистарски операнди, константе и три начина адресирања меморијских операнада.

Адресни начини рада p Код 8086 можемо препознати пет врста операнада: n n n регистарски операнди, константе и три начина адресирања меморијских операнада.

Адресни начини рада p Сходно томе, имамо пет адресних начина рада (мада, са више детаља посматрано, можемо посматрати чак 17 различитих начина адресирања): n n n Регистарско адресирање; Непосредно адресирање; Директно адресирање; Индексно адресирање.

Адресни начини рада p Сходно томе, имамо пет адресних начина рада (мада, са више детаља посматрано, можемо посматрати чак 17 различитих начина адресирања): n n n Регистарско адресирање; Непосредно адресирање; Директно адресирање; Индексно адресирање.

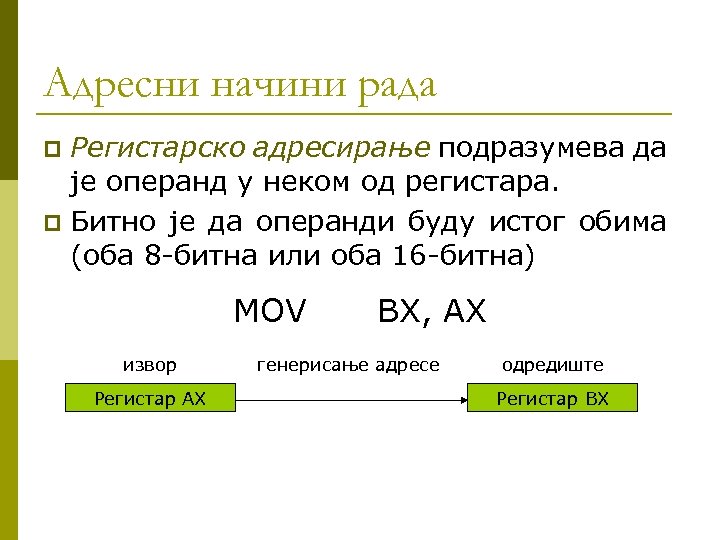

Адресни начини рада Регистарско адресирање подразумева да је операнд у неком од регистара. p Битно је да операнди буду истог обима (оба 8 -битна или оба 16 -битна) p MOV извор Регистар AX BX, AX генерисање адресе одредиште Регистар BX

Адресни начини рада Регистарско адресирање подразумева да је операнд у неком од регистара. p Битно је да операнди буду истог обима (оба 8 -битна или оба 16 -битна) p MOV извор Регистар AX BX, AX генерисање адресе одредиште Регистар BX

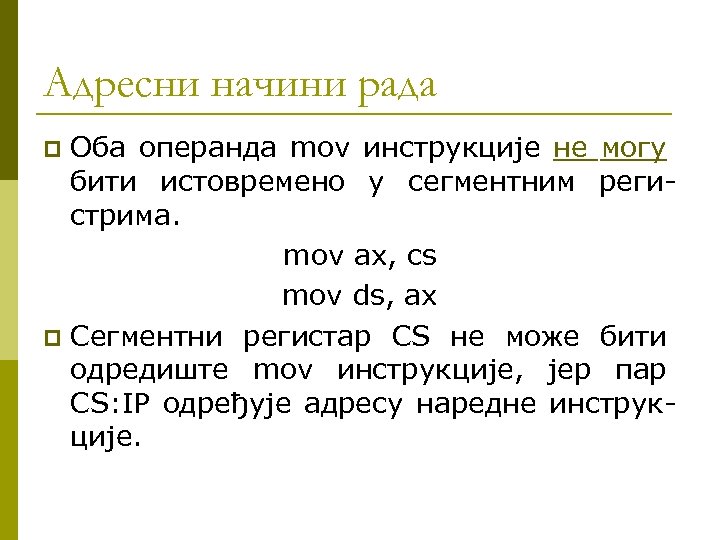

Адресни начини рада Оба операнда mov инструкције не могу бити истовремено у сегментним регистрима. mov ax, cs mov ds, ax p Сегментни регистар CS не може бити одредиште mov инструкције, јер пар CS: IP одређује адресу наредне инструкције. p

Адресни начини рада Оба операнда mov инструкције не могу бити истовремено у сегментним регистрима. mov ax, cs mov ds, ax p Сегментни регистар CS не може бити одредиште mov инструкције, јер пар CS: IP одређује адресу наредне инструкције. p

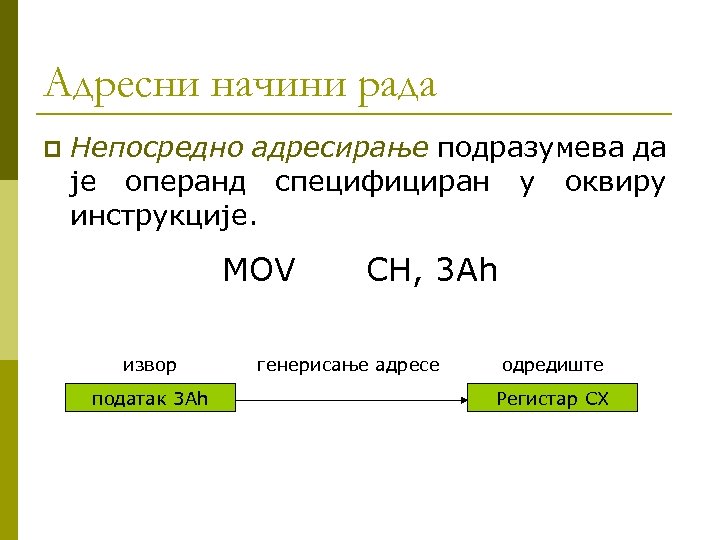

Адресни начини рада p Непосредно адресирање подразумева да је операнд специфициран у оквиру инструкције. MOV извор податак 3 Ah CH, 3 Ah генерисање адресе одредиште Регистар CX

Адресни начини рада p Непосредно адресирање подразумева да је операнд специфициран у оквиру инструкције. MOV извор податак 3 Ah CH, 3 Ah генерисање адресе одредиште Регистар CX

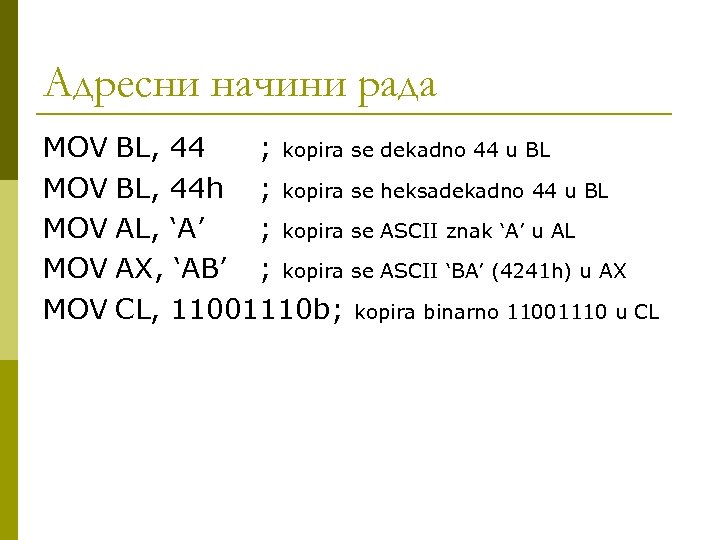

Адресни начини рада MOV BL, 44 ; kopira se dekadno 44 u BL MOV BL, 44 h ; kopira se heksadekadno 44 u BL MOV AL, ‘A’ ; kopira se ASCII znak ‘A’ u AL MOV AX, ‘AB’ ; kopira se ASCII ‘BA’ (4241 h) u AX MOV CL, 11001110 b; kopira binarno 11001110 u CL

Адресни начини рада MOV BL, 44 ; kopira se dekadno 44 u BL MOV BL, 44 h ; kopira se heksadekadno 44 u BL MOV AL, ‘A’ ; kopira se ASCII znak ‘A’ u AL MOV AX, ‘AB’ ; kopira se ASCII ‘BA’ (4241 h) u AX MOV CL, 11001110 b; kopira binarno 11001110 u CL

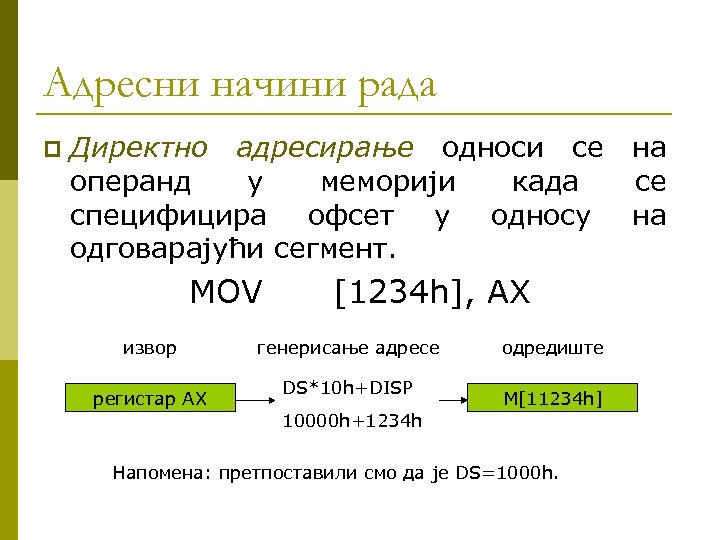

Адресни начини рада p Директно адресирање односи се операнд у меморији када специфицира офсет у односу одговарајући сегмент. MOV извор регистар AX [1234 h], AX генерисање адресе DS*10 h+DISP одредиште M[11234 h] 10000 h+1234 h Напомена: претпоставили смо да је DS=1000 h. на се на

Адресни начини рада p Директно адресирање односи се операнд у меморији када специфицира офсет у односу одговарајући сегмент. MOV извор регистар AX [1234 h], AX генерисање адресе DS*10 h+DISP одредиште M[11234 h] 10000 h+1234 h Напомена: претпоставили смо да је DS=1000 h. на се на

Адресни начини рада Уместо офсета могуће је навести лабелу која одговара некој променљивој дефинисаној у сегменту података. data 1 DB 12 H data 2 DW 3456 H … MOV AL, data 1 MOV AX, data 2 p Лабела је дужине 6 знакова (код новијих процесора до 35) и почиње словом или знацима @, $, _, ? . p

Адресни начини рада Уместо офсета могуће је навести лабелу која одговара некој променљивој дефинисаној у сегменту података. data 1 DB 12 H data 2 DW 3456 H … MOV AL, data 1 MOV AX, data 2 p Лабела је дужине 6 знакова (код новијих процесора до 35) и почиње словом или знацима @, $, _, ? . p

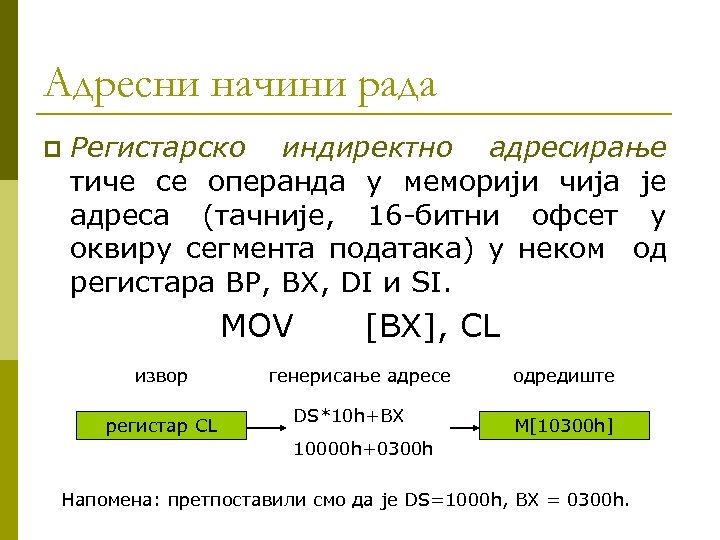

Адресни начини рада p Регистарско индиректно адресирање тиче се операнда у меморији чија је адреса (тачније, 16 -битни офсет у оквиру сегмента података) у неком од регистара BP, BX, DI и SI. MOV извор регистар CL [BX], CL генерисање адресе DS*10 h+BX одредиште M[10300 h] 10000 h+0300 h Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h.

Адресни начини рада p Регистарско индиректно адресирање тиче се операнда у меморији чија је адреса (тачније, 16 -битни офсет у оквиру сегмента података) у неком од регистара BP, BX, DI и SI. MOV извор регистар CL [BX], CL генерисање адресе DS*10 h+BX одредиште M[10300 h] 10000 h+0300 h Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h.

Адресни начини рада У одређеним случајевима потребно је користити директиву BYTE PTR или WORD PTR да се специфицира обим операнда. p Такође, директивом OFFSET се адреса неког податка (тј. офсет у односу на почетак сегмента података) може преузети у неки од регистара. p

Адресни начини рада У одређеним случајевима потребно је користити директиву BYTE PTR или WORD PTR да се специфицира обим операнда. p Такође, директивом OFFSET се адреса неког податка (тј. офсет у односу на почетак сегмента података) може преузети у неки од регистара. p

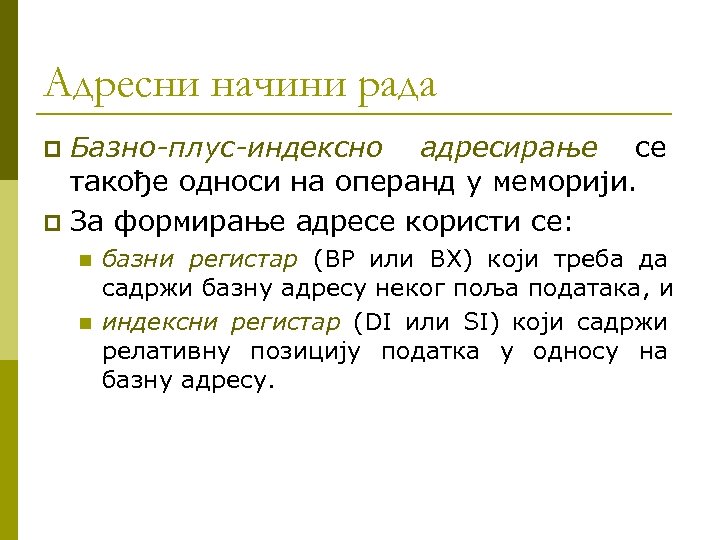

Адресни начини рада Базно-плус-индексно адресирање се такође односи на операнд у меморији. p За формирање адресе користи се: p n n базни регистар (BP или BX) који треба да садржи базну адресу неког поља података, и индексни регистар (DI или SI) који садржи релативну позицију податка у односу на базну адресу.

Адресни начини рада Базно-плус-индексно адресирање се такође односи на операнд у меморији. p За формирање адресе користи се: p n n базни регистар (BP или BX) који треба да садржи базну адресу неког поља података, и индексни регистар (DI или SI) који садржи релативну позицију податка у односу на базну адресу.

![Адресни начини рада MOV извор регистар BP [BX+SI], BP генерисање адресе DS*10 h+BX+SI одредиште Адресни начини рада MOV извор регистар BP [BX+SI], BP генерисање адресе DS*10 h+BX+SI одредиште](https://present5.com/presentation/fafe4944892ff6ae56fbb7110bf3c6ed/image-38.jpg) Адресни начини рада MOV извор регистар BP [BX+SI], BP генерисање адресе DS*10 h+BX+SI одредиште M[10500 h] 10000 h+0300 h+0200 h Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h, SI=0200 h.

Адресни начини рада MOV извор регистар BP [BX+SI], BP генерисање адресе DS*10 h+BX+SI одредиште M[10500 h] 10000 h+0300 h+0200 h Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h, SI=0200 h.

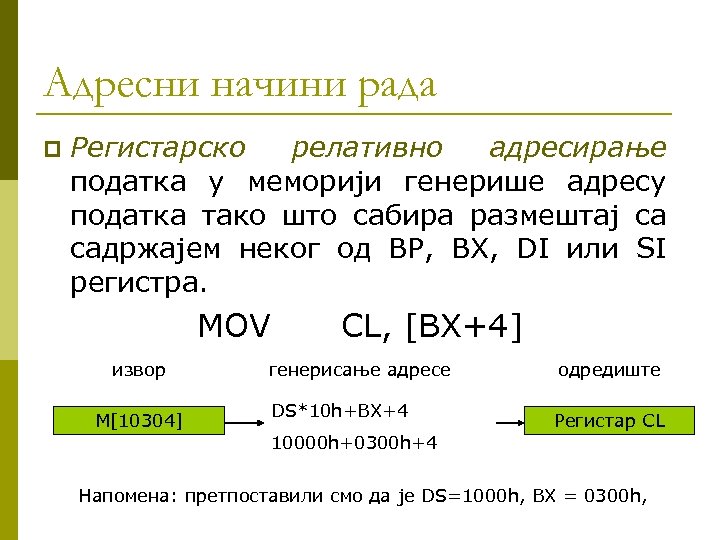

Адресни начини рада p Регистарско релативно адресирање податка у меморији генерише адресу податка тако што сабира размештај са садржајем неког од BP, BX, DI или SI регистра. MOV извор M[10304] CL, [BX+4] генерисање адресе DS*10 h+BX+4 одредиште Регистар CL 10000 h+0300 h+4 Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h,

Адресни начини рада p Регистарско релативно адресирање податка у меморији генерише адресу податка тако што сабира размештај са садржајем неког од BP, BX, DI или SI регистра. MOV извор M[10304] CL, [BX+4] генерисање адресе DS*10 h+BX+4 одредиште Регистар CL 10000 h+0300 h+4 Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h,

Адресни начини рада p Размештај се наводи у оквиру заграде, као у претходном примеру, или изван заграде. MOV p VEKTOR[DI], AL Размештај је означени 16 -битни број (код 8086/. . . /80286).

Адресни начини рада p Размештај се наводи у оквиру заграде, као у претходном примеру, или изван заграде. MOV p VEKTOR[DI], AL Размештај је означени 16 -битни број (код 8086/. . . /80286).

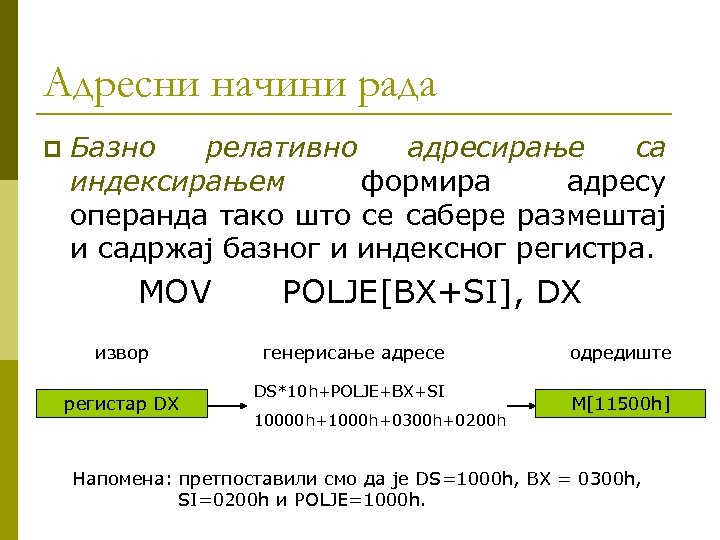

Адресни начини рада p Базно релативно адресирање са индексирањем формира адресу операнда тако што се сабере размештај и садржај базног и индексног регистра. MOV извор регистар DX POLJE[BX+SI], DX генерисање адресе DS*10 h+POLJE+BX+SI 10000 h+1000 h+0300 h+0200 h одредиште M[11500 h] Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h, SI=0200 h и POLJE=1000 h.

Адресни начини рада p Базно релативно адресирање са индексирањем формира адресу операнда тако што се сабере размештај и садржај базног и индексног регистра. MOV извор регистар DX POLJE[BX+SI], DX генерисање адресе DS*10 h+POLJE+BX+SI 10000 h+1000 h+0300 h+0200 h одредиште M[11500 h] Напомена: претпоставили смо да је DS=1000 h, BX = 0300 h, SI=0200 h и POLJE=1000 h.

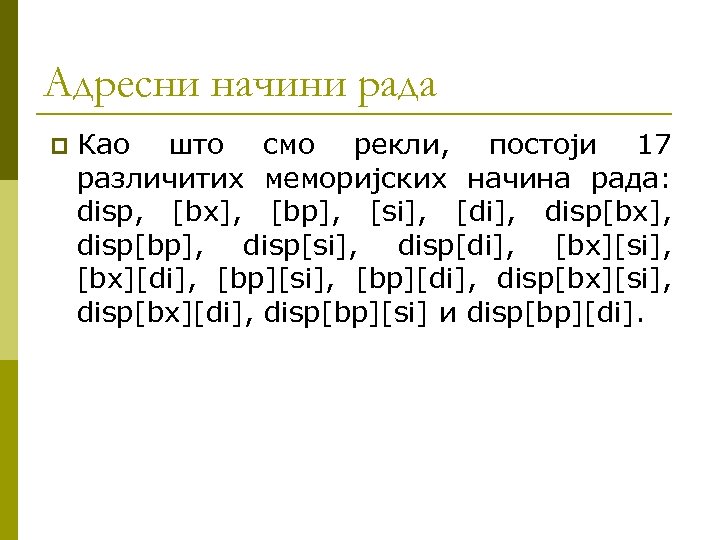

Адресни начини рада p Као што смо рекли, постоји 17 различитих меморијских начина рада: disp, [bx], [bp], [si], [di], disp[bx], disp[bp], disp[si], disp[di], [bx][si], [bx][di], [bp][si], [bp][di], disp[bx][si], disp[bx][di], disp[bp][si] и disp[bp][di].

Адресни начини рада p Као што смо рекли, постоји 17 различитих меморијских начина рада: disp, [bx], [bp], [si], [di], disp[bx], disp[bp], disp[si], disp[di], [bx][si], [bx][di], [bp][si], [bp][di], disp[bx][si], disp[bx][di], disp[bp][si] и disp[bp][di].

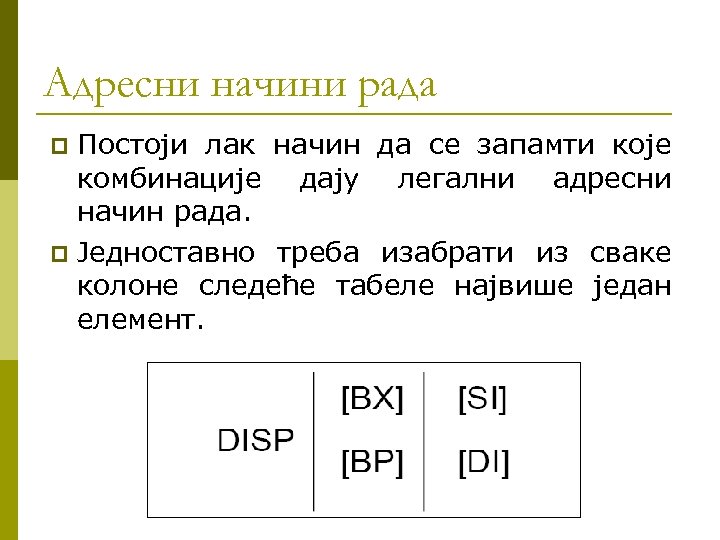

Адресни начини рада Постоји лак начин да се запамти које комбинације дају легални адресни начин рада. p Једноставно треба изабрати из сваке колоне следеће табеле највише један елемент. p

Адресни начини рада Постоји лак начин да се запамти које комбинације дају легални адресни начин рада. p Једноставно треба изабрати из сваке колоне следеће табеле највише један елемент. p