0f5404c735517de34b5212694058f5bd.ppt

- Количество слайдов: 48

Архитектура ЭВМ

Архитектура ЭВМ

I. Введение История развития вычислительной техники. Механические вычислительные устройства. Абак Машина Паскаля Машина Лейбница Машина Бэбиджа Архитектура ЭВМ Современные механические машины 2

I. Введение История развития вычислительной техники. Механические вычислительные устройства. Абак Машина Паскаля Машина Лейбница Машина Бэбиджа Архитектура ЭВМ Современные механические машины 2

Электромеханические счетные машины Машины Конрада Цузе (Z 1, Z 2, Z 3, Z 4) - Z 1 – полностью механическая машина (1936); - Z 2 – использование реле в арифметическом устройстве (1939); - Z 3 и Z 4 – электромеханические машины с механической памятью (1941 и 1945). Машина Z 4 Машина Z 3 Архитектура ЭВМ 3

Электромеханические счетные машины Машины Конрада Цузе (Z 1, Z 2, Z 3, Z 4) - Z 1 – полностью механическая машина (1936); - Z 2 – использование реле в арифметическом устройстве (1939); - Z 3 и Z 4 – электромеханические машины с механической памятью (1941 и 1945). Машина Z 4 Машина Z 3 Архитектура ЭВМ 3

Электронные вычислительные машины Первое поколение ЭВМ (с конца 30 -х до середины 50 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем I (с конца 30 -х до середины 50 -х) Электромагнитные реле; электронные лампы Линии задержки на электронные лучевых трубках, Ферритовые сердечники (~212216) Калькуляторы (ABC, ENIAC), Большие ЭВМ (MARK I, EDVAC, UNIVAC, БЭСМ, МЭСМ, IAS) Ручная коммутация, Машинные коды Ассемблер Индикаторы, Пульт управления, Перфокарты ЭВМ MARK I ЭВМ ENIAC Архитектура ЭВМ 4

Электронные вычислительные машины Первое поколение ЭВМ (с конца 30 -х до середины 50 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем I (с конца 30 -х до середины 50 -х) Электромагнитные реле; электронные лампы Линии задержки на электронные лучевых трубках, Ферритовые сердечники (~212216) Калькуляторы (ABC, ENIAC), Большие ЭВМ (MARK I, EDVAC, UNIVAC, БЭСМ, МЭСМ, IAS) Ручная коммутация, Машинные коды Ассемблер Индикаторы, Пульт управления, Перфокарты ЭВМ MARK I ЭВМ ENIAC Архитектура ЭВМ 4

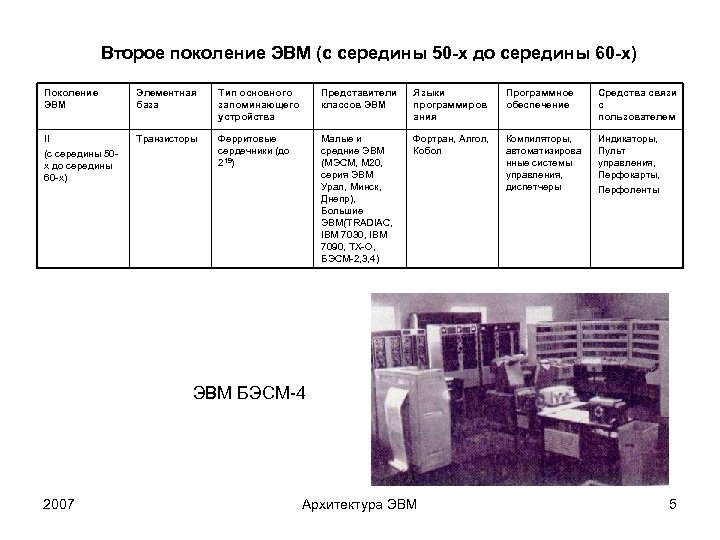

Второе поколение ЭВМ (с середины 50 -х до середины 60 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программиров ания Программное обеспечение Средства связи с пользователем II (с середины 50 х до середины 60 -х) Транзисторы Ферритовые сердечники (до 219) Малые и средние ЭВМ (МЭСМ, M 20, серия ЭВМ Урал, Минск, Днепр), Большие ЭВМ(TRADIAC, IBM 7030, IBM 7090, TX-O, БЭСМ-2, 3, 4) Фортран, Алгол, Кобол Компиляторы, автоматизирова нные системы управления, диспетчеры Индикаторы, Пульт управления, Перфокарты, Перфоленты ЭВМ БЭСМ-4 2007 Архитектура ЭВМ 5

Второе поколение ЭВМ (с середины 50 -х до середины 60 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программиров ания Программное обеспечение Средства связи с пользователем II (с середины 50 х до середины 60 -х) Транзисторы Ферритовые сердечники (до 219) Малые и средние ЭВМ (МЭСМ, M 20, серия ЭВМ Урал, Минск, Днепр), Большие ЭВМ(TRADIAC, IBM 7030, IBM 7090, TX-O, БЭСМ-2, 3, 4) Фортран, Алгол, Кобол Компиляторы, автоматизирова нные системы управления, диспетчеры Индикаторы, Пульт управления, Перфокарты, Перфоленты ЭВМ БЭСМ-4 2007 Архитектура ЭВМ 5

Третье поколение ЭВМ (с середины 60 -х до середины 70 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем III (с середины 60 -х до середины 70 х) Интегральные схемы малой и средней степени интеграции Полупроводни-ковые ЗУ на больших интегральных схемах (до 225) Мини и микро-ЭВМ (Мир-1, М 220), Средние и большие универсальные ЭВМ (ILLIAC IV, CDC 6600, CDC 7600, IBM 360, EC ЭВМ, СМ ЭВМ, БЭСМ-6) Фортран, Алгол, B, C ОС (UNIX, IBM DOS), СУБД, САПР, Пакеты прикладных программ Алфавитноцифровые дисплеи IBM 360 ЭВМ БЭСМ-6 Архитектура ЭВМ 6

Третье поколение ЭВМ (с середины 60 -х до середины 70 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем III (с середины 60 -х до середины 70 х) Интегральные схемы малой и средней степени интеграции Полупроводни-ковые ЗУ на больших интегральных схемах (до 225) Мини и микро-ЭВМ (Мир-1, М 220), Средние и большие универсальные ЭВМ (ILLIAC IV, CDC 6600, CDC 7600, IBM 360, EC ЭВМ, СМ ЭВМ, БЭСМ-6) Фортран, Алгол, B, C ОС (UNIX, IBM DOS), СУБД, САПР, Пакеты прикладных программ Алфавитноцифровые дисплеи IBM 360 ЭВМ БЭСМ-6 Архитектура ЭВМ 6

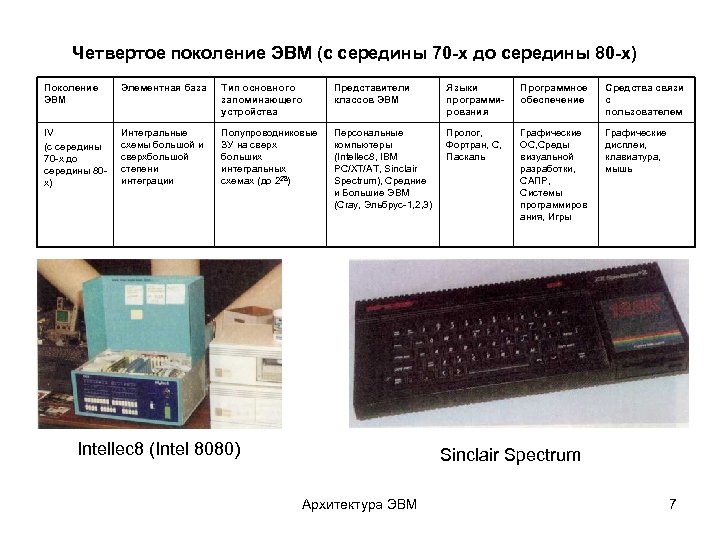

Четвертое поколение ЭВМ (с середины 70 -х до середины 80 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем IV (с середины 70 -х до середины 80 х) Интегральные схемы большой и сверхбольшой степени интеграции Полупроводниковые ЗУ на сверх больших интегральных схемах (до 228) Персональные компьютеры (Intellec 8, IBM PC/XT/AT, Sinclair Spectrum), Средние и Большие ЭВМ (Cray, Эльбрус-1, 2, 3) Пролог, Фортран, C, Паскаль Графические ОС, Среды визуальной разработки, САПР, Системы программиров ания, Игры Графические дисплеи, клавиатура, мышь Intellec 8 (Intel 8080) Sinclair Spectrum Архитектура ЭВМ 7

Четвертое поколение ЭВМ (с середины 70 -х до середины 80 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем IV (с середины 70 -х до середины 80 х) Интегральные схемы большой и сверхбольшой степени интеграции Полупроводниковые ЗУ на сверх больших интегральных схемах (до 228) Персональные компьютеры (Intellec 8, IBM PC/XT/AT, Sinclair Spectrum), Средние и Большие ЭВМ (Cray, Эльбрус-1, 2, 3) Пролог, Фортран, C, Паскаль Графические ОС, Среды визуальной разработки, САПР, Системы программиров ания, Игры Графические дисплеи, клавиатура, мышь Intellec 8 (Intel 8080) Sinclair Spectrum Архитектура ЭВМ 7

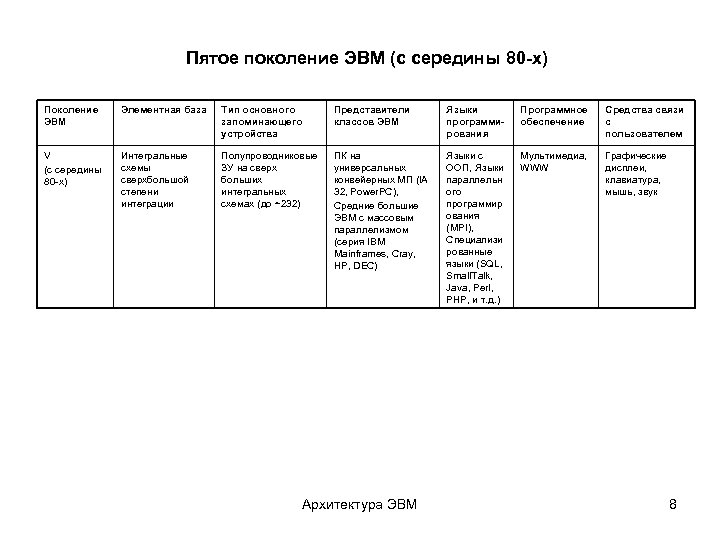

Пятое поколение ЭВМ (с середины 80 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем V (с середины 80 -х) Интегральные схемы сверхбольшой степени интеграции Полупроводниковые ЗУ на сверх больших интегральных схемах (до ~232) ПК на универсальных конвейерных МП (IA 32, Power. PC), Средние большие ЭВМ с массовым параллелизмом (серия IBM Mainframes, Cray, HP, DEC) Языки с ООП, Языки параллельн ого программир ования (MPI), Специализи рованные языки (SQL, Small. Talk, Java, Perl, PHP, и т. д. ) Мультимедиа, WWW Графические дисплеи, клавиатура, мышь, звук Архитектура ЭВМ 8

Пятое поколение ЭВМ (с середины 80 -х) Поколение ЭВМ Элементная база Тип основного запоминающего устройства Представители классов ЭВМ Языки программирования Программное обеспечение Средства связи с пользователем V (с середины 80 -х) Интегральные схемы сверхбольшой степени интеграции Полупроводниковые ЗУ на сверх больших интегральных схемах (до ~232) ПК на универсальных конвейерных МП (IA 32, Power. PC), Средние большие ЭВМ с массовым параллелизмом (серия IBM Mainframes, Cray, HP, DEC) Языки с ООП, Языки параллельн ого программир ования (MPI), Специализи рованные языки (SQL, Small. Talk, Java, Perl, PHP, и т. д. ) Мультимедиа, WWW Графические дисплеи, клавиатура, мышь, звук Архитектура ЭВМ 8

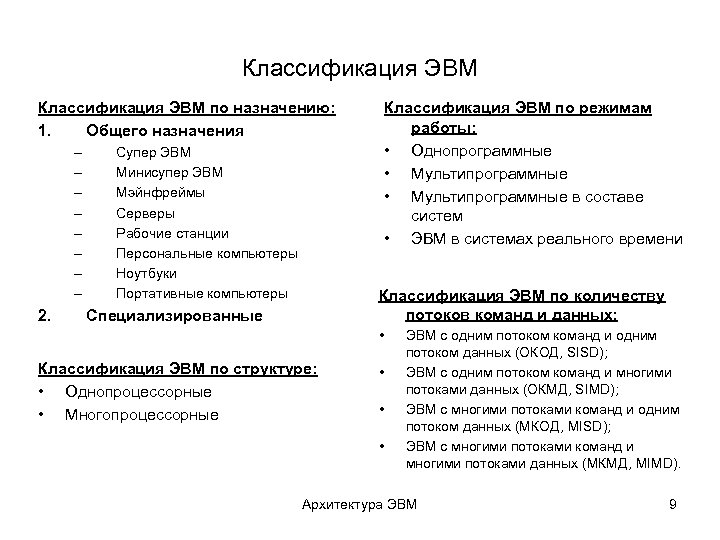

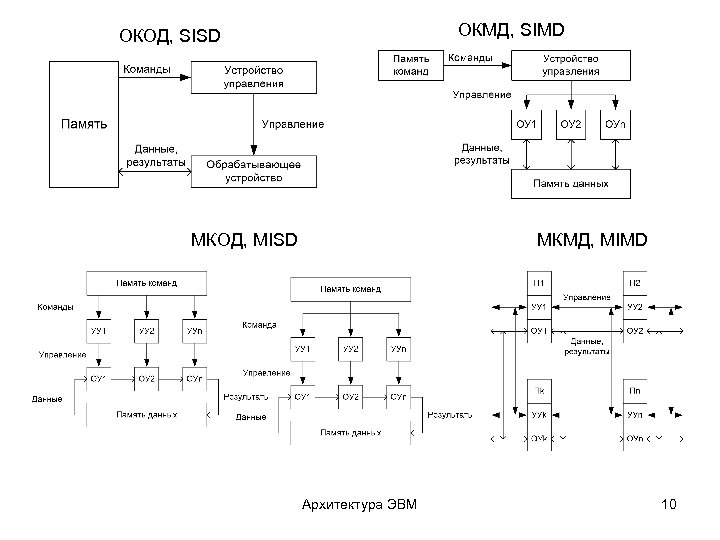

Классификация ЭВМ по назначению: 1. Общего назначения – – – – 2. Супер ЭВМ Минисупер ЭВМ Мэйнфреймы Серверы Рабочие станции Персональные компьютеры Ноутбуки Портативные компьютеры Классификация ЭВМ по режимам работы: • Однопрограммные • Мультипрограммные в составе систем • ЭВМ в системах реального времени Классификация ЭВМ по количеству потоков команд и данных: Специализированные • Классификация ЭВМ по структуре: • Однопроцессорные • Многопроцессорные • • • ЭВМ с одним потоком команд и одним потоком данных (ОКОД, SISD); ЭВМ с одним потоком команд и многими потоками данных (ОКМД, SIMD); ЭВМ с многими потоками команд и одним потоком данных (МКОД, MISD); ЭВМ с многими потоками команд и многими потоками данных (МКМД, MIMD). Архитектура ЭВМ 9

Классификация ЭВМ по назначению: 1. Общего назначения – – – – 2. Супер ЭВМ Минисупер ЭВМ Мэйнфреймы Серверы Рабочие станции Персональные компьютеры Ноутбуки Портативные компьютеры Классификация ЭВМ по режимам работы: • Однопрограммные • Мультипрограммные в составе систем • ЭВМ в системах реального времени Классификация ЭВМ по количеству потоков команд и данных: Специализированные • Классификация ЭВМ по структуре: • Однопроцессорные • Многопроцессорные • • • ЭВМ с одним потоком команд и одним потоком данных (ОКОД, SISD); ЭВМ с одним потоком команд и многими потоками данных (ОКМД, SIMD); ЭВМ с многими потоками команд и одним потоком данных (МКОД, MISD); ЭВМ с многими потоками команд и многими потоками данных (МКМД, MIMD). Архитектура ЭВМ 9

ОКМД, SIMD ОКОД, SISD МКОД, MISD МКМД, MIMD Архитектура ЭВМ 10

ОКМД, SIMD ОКОД, SISD МКОД, MISD МКМД, MIMD Архитектура ЭВМ 10

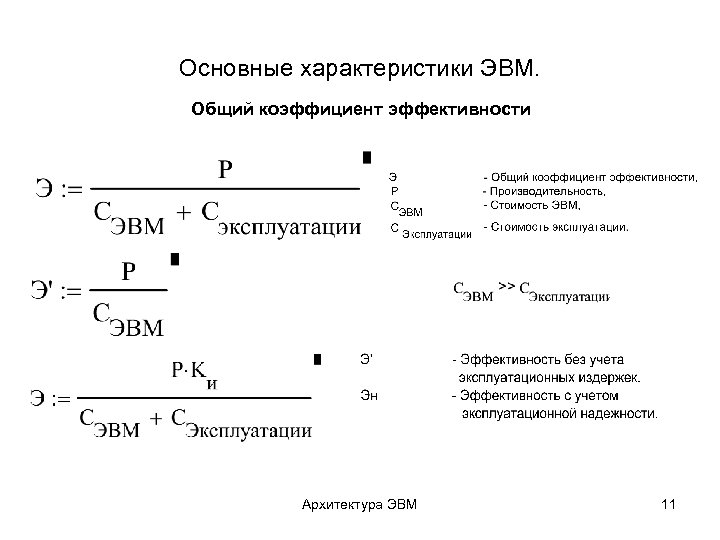

Основные характеристики ЭВМ. Общий коэффициент эффективности Архитектура ЭВМ 11

Основные характеристики ЭВМ. Общий коэффициент эффективности Архитектура ЭВМ 11

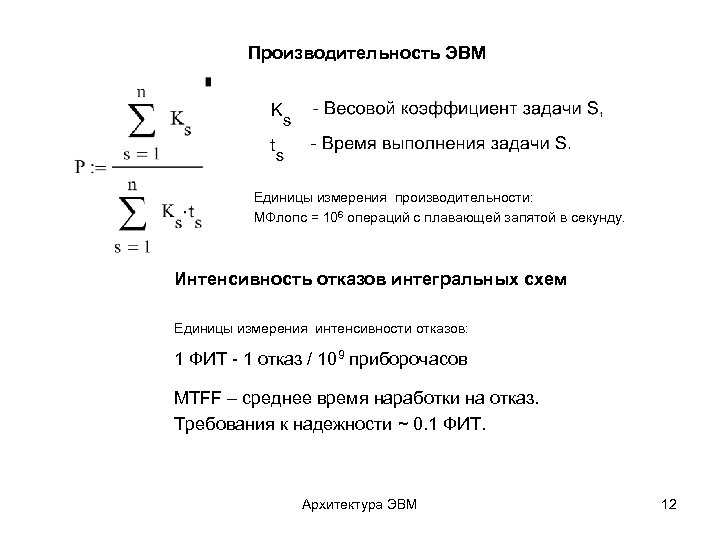

Производительность ЭВМ Единицы измерения производительности: МФлопс = 106 операций с плавающей запятой в секунду. Интенсивность отказов интегральных схем Единицы измерения интенсивности отказов: 1 ФИТ - 1 отказ / 109 приборочасов MTFF – среднее время наработки на отказ. Требования к надежности ~ 0. 1 ФИТ. Архитектура ЭВМ 12

Производительность ЭВМ Единицы измерения производительности: МФлопс = 106 операций с плавающей запятой в секунду. Интенсивность отказов интегральных схем Единицы измерения интенсивности отказов: 1 ФИТ - 1 отказ / 109 приборочасов MTFF – среднее время наработки на отказ. Требования к надежности ~ 0. 1 ФИТ. Архитектура ЭВМ 12

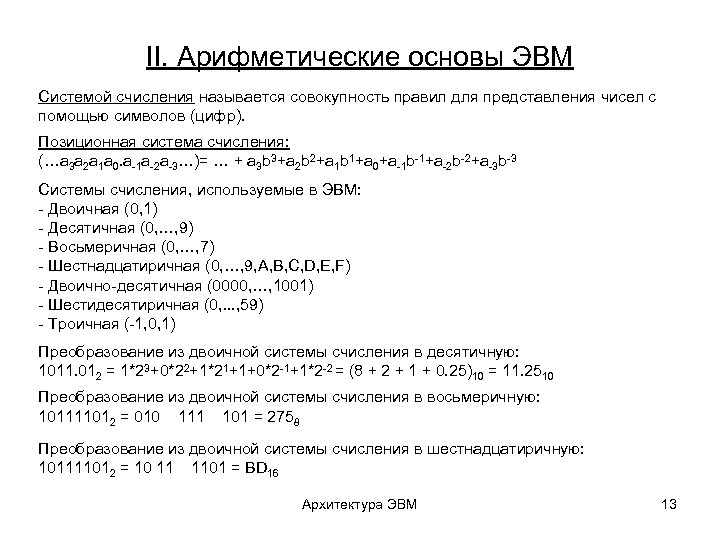

II. Арифметические основы ЭВМ Системой счисления называется совокупность правил для представления чисел с помощью символов (цифр). Позиционная система счисления: (…a 3 a 2 a 1 a 0. a-1 a-2 a-3…)= … + a 3 b 3+a 2 b 2+a 1 b 1+a 0+a-1 b-1+a-2 b-2+a-3 b-3 Системы счисления, используемые в ЭВМ: - Двоичная (0, 1) - Десятичная (0, …, 9) - Восьмеричная (0, …, 7) - Шестнадцатиричная (0, …, 9, A, B, C, D, E, F) - Двоично-десятичная (0000, …, 1001) - Шестидесятиричная (0, . . . , 59) - Троичная (-1, 0, 1) Преобразование из двоичной системы счисления в десятичную: 1011. 012 = 1*23+0*22+1*21+1+0*2 -1+1*2 -2 = (8 + 2 + 1 + 0. 25)10 = 11. 2510 Преобразование из двоичной системы счисления в восьмеричную: 101111012 = 010 111 101 = 2758 Преобразование из двоичной системы счисления в шестнадцатиричную: 101111012 = 10 11 1101 = BD 16 Архитектура ЭВМ 13

II. Арифметические основы ЭВМ Системой счисления называется совокупность правил для представления чисел с помощью символов (цифр). Позиционная система счисления: (…a 3 a 2 a 1 a 0. a-1 a-2 a-3…)= … + a 3 b 3+a 2 b 2+a 1 b 1+a 0+a-1 b-1+a-2 b-2+a-3 b-3 Системы счисления, используемые в ЭВМ: - Двоичная (0, 1) - Десятичная (0, …, 9) - Восьмеричная (0, …, 7) - Шестнадцатиричная (0, …, 9, A, B, C, D, E, F) - Двоично-десятичная (0000, …, 1001) - Шестидесятиричная (0, . . . , 59) - Троичная (-1, 0, 1) Преобразование из двоичной системы счисления в десятичную: 1011. 012 = 1*23+0*22+1*21+1+0*2 -1+1*2 -2 = (8 + 2 + 1 + 0. 25)10 = 11. 2510 Преобразование из двоичной системы счисления в восьмеричную: 101111012 = 010 111 101 = 2758 Преобразование из двоичной системы счисления в шестнадцатиричную: 101111012 = 10 11 1101 = BD 16 Архитектура ЭВМ 13

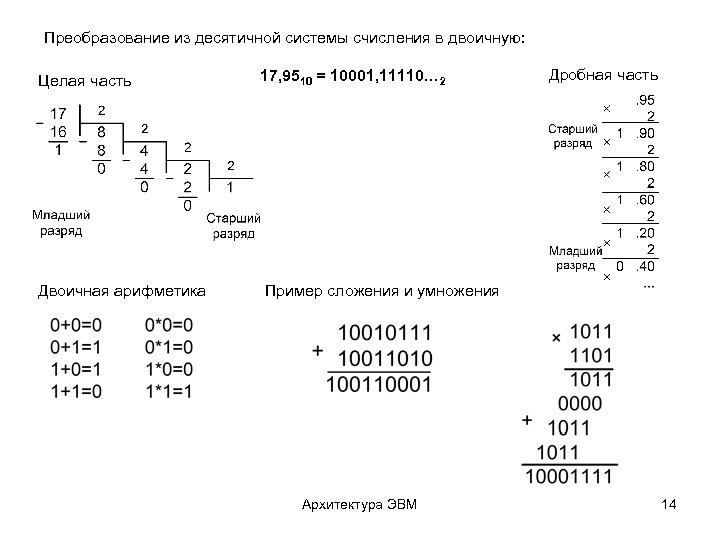

Преобразование из десятичной системы счисления в двоичную: Целая часть Двоичная арифметика 17, 9510 = 10001, 11110… 2 Дробная часть Пример сложения и умножения Архитектура ЭВМ 14

Преобразование из десятичной системы счисления в двоичную: Целая часть Двоичная арифметика 17, 9510 = 10001, 11110… 2 Дробная часть Пример сложения и умножения Архитектура ЭВМ 14

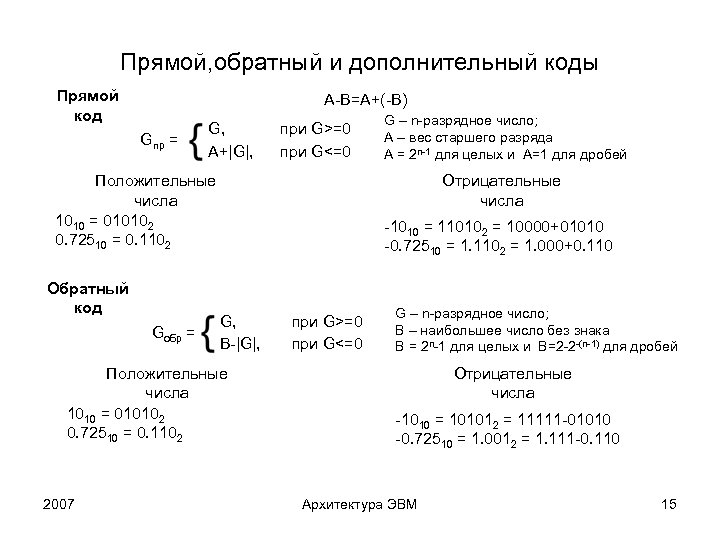

Прямой, обратный и дополнительный коды Прямой код A-B=A+(-B) Gпр = G, A+|G|, при G>=0 при G<=0 Положительные числа 1010 = 010102 0. 72510 = 0. 1102 Обратный код Gобр = Отрицательные числа -1010 = 110102 = 10000+01010 -0. 72510 = 1. 1102 = 1. 000+0. 110 G, B-|G|, Положительные числа 1010 = 010102 0. 72510 = 0. 1102 2007 G – n-разрядное число; A – вес старшего разряда A = 2 n-1 для целых и A=1 для дробей при G>=0 при G<=0 G – n-разрядное число; B – наибольшее число без знака B = 2 n-1 для целых и B=2 -2 -(n-1) для дробей Отрицательные числа -1010 = 101012 = 11111 -01010 -0. 72510 = 1. 0012 = 1. 111 -0. 110 Архитектура ЭВМ 15

Прямой, обратный и дополнительный коды Прямой код A-B=A+(-B) Gпр = G, A+|G|, при G>=0 при G<=0 Положительные числа 1010 = 010102 0. 72510 = 0. 1102 Обратный код Gобр = Отрицательные числа -1010 = 110102 = 10000+01010 -0. 72510 = 1. 1102 = 1. 000+0. 110 G, B-|G|, Положительные числа 1010 = 010102 0. 72510 = 0. 1102 2007 G – n-разрядное число; A – вес старшего разряда A = 2 n-1 для целых и A=1 для дробей при G>=0 при G<=0 G – n-разрядное число; B – наибольшее число без знака B = 2 n-1 для целых и B=2 -2 -(n-1) для дробей Отрицательные числа -1010 = 101012 = 11111 -01010 -0. 72510 = 1. 0012 = 1. 111 -0. 110 Архитектура ЭВМ 15

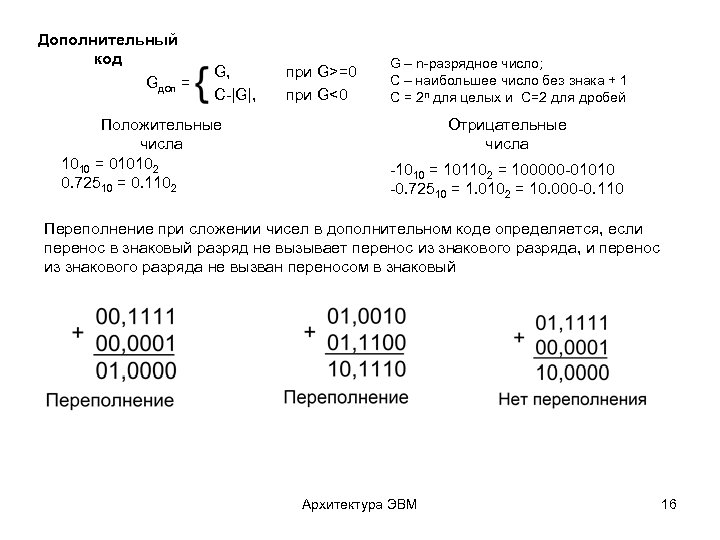

Дополнительный код Gдоп = G, С-|G|, Положительные числа 1010 = 010102 0. 72510 = 0. 1102 при G>=0 при G<0 G – n-разрядное число; С – наибольшее число без знака + 1 С = 2 n для целых и С=2 для дробей Отрицательные числа -1010 = 101102 = 100000 -01010 -0. 72510 = 1. 0102 = 10. 000 -0. 110 Переполнение при сложении чисел в дополнительном коде определяется, если перенос в знаковый разряд не вызывает перенос из знакового разряда, и перенос из знакового разряда не вызван переносом в знаковый Архитектура ЭВМ 16

Дополнительный код Gдоп = G, С-|G|, Положительные числа 1010 = 010102 0. 72510 = 0. 1102 при G>=0 при G<0 G – n-разрядное число; С – наибольшее число без знака + 1 С = 2 n для целых и С=2 для дробей Отрицательные числа -1010 = 101102 = 100000 -01010 -0. 72510 = 1. 0102 = 10. 000 -0. 110 Переполнение при сложении чисел в дополнительном коде определяется, если перенос в знаковый разряд не вызывает перенос из знакового разряда, и перенос из знакового разряда не вызван переносом в знаковый Архитектура ЭВМ 16

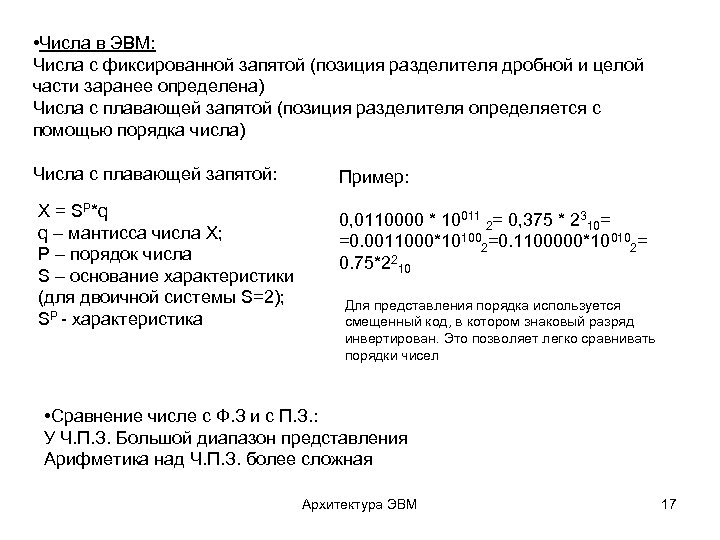

• Числа в ЭВМ: Числа с фиксированной запятой (позиция разделителя дробной и целой части заранее определена) Числа с плавающей запятой (позиция разделителя определяется с помощью порядка числа) Числа с плавающей запятой: X = SP*q q – мантисса числа X; P – порядок числа S – основание характеристики (для двоичной системы S=2); SP - характеристика Пример: 0, 0110000 * 10011 2= 0, 375 * 2310= =0. 0011000*101002=0. 1100000*100102= 0. 75*2210 Для представления порядка используется смещенный код, в котором знаковый разряд инвертирован. Это позволяет легко сравнивать порядки чисел • Сравнение числе с Ф. З и с П. З. : У Ч. П. З. Большой диапазон представления Арифметика над Ч. П. З. более сложная Архитектура ЭВМ 17

• Числа в ЭВМ: Числа с фиксированной запятой (позиция разделителя дробной и целой части заранее определена) Числа с плавающей запятой (позиция разделителя определяется с помощью порядка числа) Числа с плавающей запятой: X = SP*q q – мантисса числа X; P – порядок числа S – основание характеристики (для двоичной системы S=2); SP - характеристика Пример: 0, 0110000 * 10011 2= 0, 375 * 2310= =0. 0011000*101002=0. 1100000*100102= 0. 75*2210 Для представления порядка используется смещенный код, в котором знаковый разряд инвертирован. Это позволяет легко сравнивать порядки чисел • Сравнение числе с Ф. З и с П. З. : У Ч. П. З. Большой диапазон представления Арифметика над Ч. П. З. более сложная Архитектура ЭВМ 17

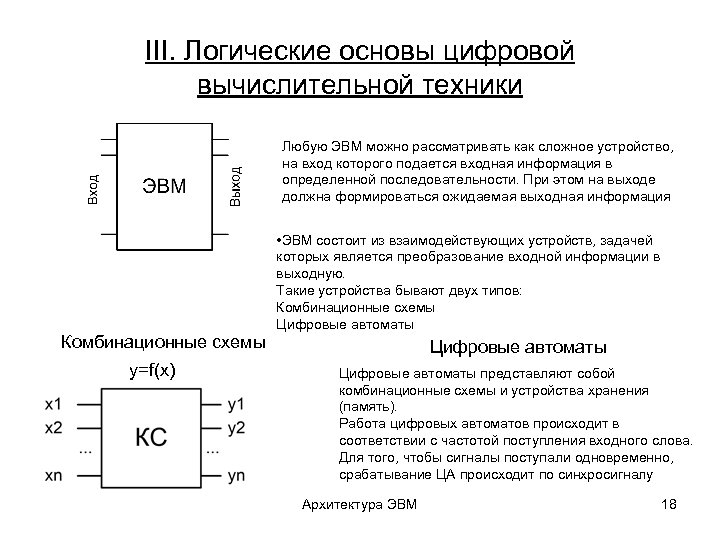

III. Логические основы цифровой вычислительной техники Любую ЭВМ можно рассматривать как сложное устройство, на вход которого подается входная информация в определенной последовательности. При этом на выходе должна формироваться ожидаемая выходная информация • ЭВМ состоит из взаимодействующих устройств, задачей которых является преобразование входной информации в выходную. Такие устройства бывают двух типов: Комбинационные схемы Цифровые автоматы Комбинационные схемы y=f(x) Цифровые автоматы представляют собой комбинационные схемы и устройства хранения (память). Работа цифровых автоматов происходит в соответствии с частотой поступления входного слова. Для того, чтобы сигналы поступали одновременно, срабатывание ЦА происходит по синхросигналу Архитектура ЭВМ 18

III. Логические основы цифровой вычислительной техники Любую ЭВМ можно рассматривать как сложное устройство, на вход которого подается входная информация в определенной последовательности. При этом на выходе должна формироваться ожидаемая выходная информация • ЭВМ состоит из взаимодействующих устройств, задачей которых является преобразование входной информации в выходную. Такие устройства бывают двух типов: Комбинационные схемы Цифровые автоматы Комбинационные схемы y=f(x) Цифровые автоматы представляют собой комбинационные схемы и устройства хранения (память). Работа цифровых автоматов происходит в соответствии с частотой поступления входного слова. Для того, чтобы сигналы поступали одновременно, срабатывание ЦА происходит по синхросигналу Архитектура ЭВМ 18

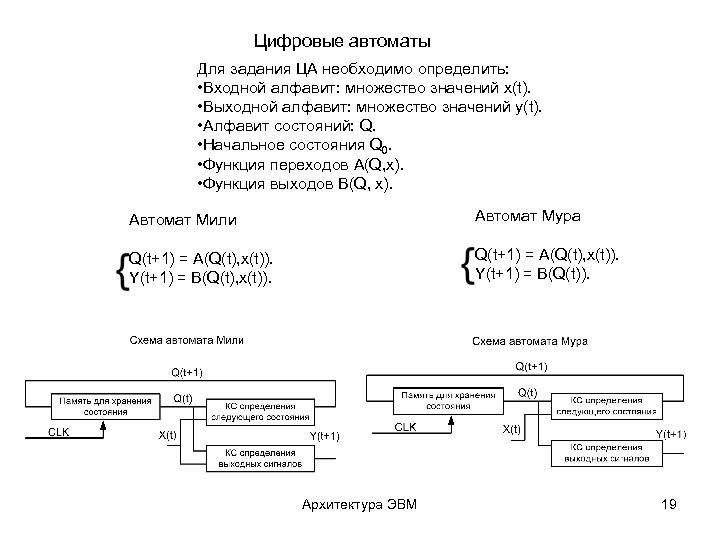

Цифровые автоматы Для задания ЦА необходимо определить: • Входной алфавит: множество значений x(t). • Выходной алфавит: множество значений y(t). • Алфавит состояний: Q. • Начальное состояния Q 0. • Функция переходов A(Q, x). • Функция выходов B(Q, x). Автомат Мили Автомат Мура Q(t+1) = A(Q(t), x(t)). Y(t+1) = B(Q(t), x(t)). Q(t+1) = A(Q(t), x(t)). Y(t+1) = B(Q(t)). Архитектура ЭВМ 19

Цифровые автоматы Для задания ЦА необходимо определить: • Входной алфавит: множество значений x(t). • Выходной алфавит: множество значений y(t). • Алфавит состояний: Q. • Начальное состояния Q 0. • Функция переходов A(Q, x). • Функция выходов B(Q, x). Автомат Мили Автомат Мура Q(t+1) = A(Q(t), x(t)). Y(t+1) = B(Q(t), x(t)). Q(t+1) = A(Q(t), x(t)). Y(t+1) = B(Q(t)). Архитектура ЭВМ 19

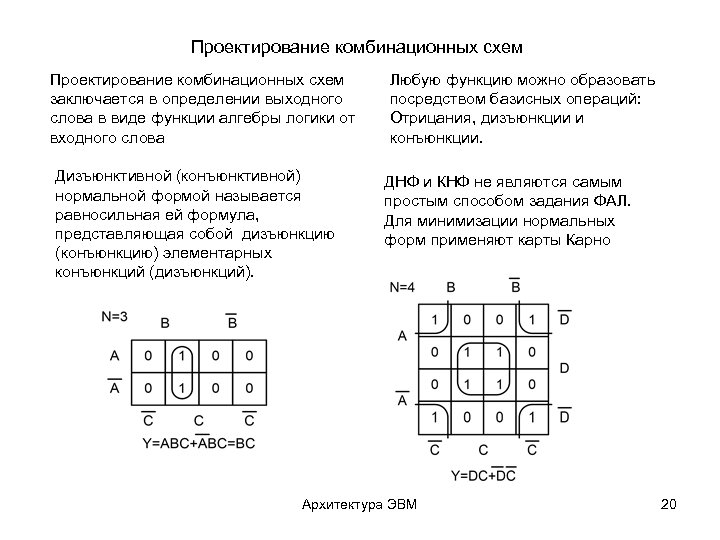

Проектирование комбинационных схем заключается в определении выходного слова в виде функции алгебры логики от входного слова Дизъюнктивной (конъюнктивной) нормальной формой называется равносильная ей формула, представляющая собой дизъюнкцию (конъюнкцию) элементарных конъюнкций (дизъюнкций). Любую функцию можно образовать посредством базисных операций: Отрицания, дизъюнкции и конъюнкции. ДНФ и КНФ не являются самым простым способом задания ФАЛ. Для минимизации нормальных форм применяют карты Карно Архитектура ЭВМ 20

Проектирование комбинационных схем заключается в определении выходного слова в виде функции алгебры логики от входного слова Дизъюнктивной (конъюнктивной) нормальной формой называется равносильная ей формула, представляющая собой дизъюнкцию (конъюнкцию) элементарных конъюнкций (дизъюнкций). Любую функцию можно образовать посредством базисных операций: Отрицания, дизъюнкции и конъюнкции. ДНФ и КНФ не являются самым простым способом задания ФАЛ. Для минимизации нормальных форм применяют карты Карно Архитектура ЭВМ 20

Логические функции A 0 0 1 1 B 0 1 Обозначение функции Название функции 0 1 1 1 AUB Дизъюнкция 0 0 0 1 A∩B Конъюнкция 1 1 0 0 A Отрицание A 0 0 1 0 A → B Запрет A → B 0 1 0 0 B → A Запрет A → B 0 1 1 0 A B Исключающее ИЛИ 1 0 0 0 A↓B Стрелка Пирса ИЛИ-НЕ 1 0 0 1 A~B Равнозначность 1 0 1 1 B→A Импликация от В к А 1 1 0 1 A→B Импликация от А к В 1 1 1 0 A/B Штрих Шеффера И-НЕ Архитектура ЭВМ 21

Логические функции A 0 0 1 1 B 0 1 Обозначение функции Название функции 0 1 1 1 AUB Дизъюнкция 0 0 0 1 A∩B Конъюнкция 1 1 0 0 A Отрицание A 0 0 1 0 A → B Запрет A → B 0 1 0 0 B → A Запрет A → B 0 1 1 0 A B Исключающее ИЛИ 1 0 0 0 A↓B Стрелка Пирса ИЛИ-НЕ 1 0 0 1 A~B Равнозначность 1 0 1 1 B→A Импликация от В к А 1 1 0 1 A→B Импликация от А к В 1 1 1 0 A/B Штрих Шеффера И-НЕ Архитектура ЭВМ 21

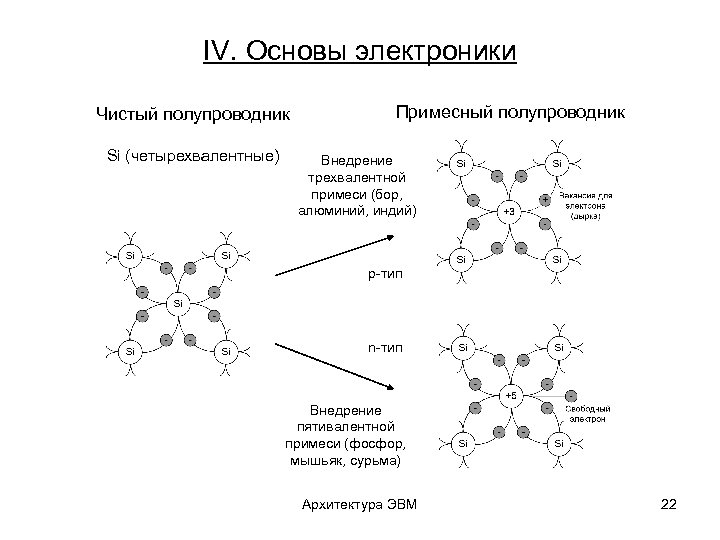

IV. Основы электроники Чистый полупроводник Si (четырехвалентные) Примесный полупроводник Внедрение трехвалентной примеси (бор, алюминий, индий) p-тип n-тип Внедрение пятивалентной примеси (фосфор, мышьяк, сурьма) Архитектура ЭВМ 22

IV. Основы электроники Чистый полупроводник Si (четырехвалентные) Примесный полупроводник Внедрение трехвалентной примеси (бор, алюминий, индий) p-тип n-тип Внедрение пятивалентной примеси (фосфор, мышьяк, сурьма) Архитектура ЭВМ 22

Контакт двух полупроводников На границе полупроводников различного типа проводимости происходит диффузия электронов из полупроводника n-типа в полупроводник p-типа, а дырок в обратном направлении. Концентрация свободных носителей в приграничной области сокращается вследствие рекомбинации. Возникает обедненный слой (переход), имеющий большое удельное сопротивление. Условное обозначение диода Iпр Iобр Архитектура ЭВМ 23

Контакт двух полупроводников На границе полупроводников различного типа проводимости происходит диффузия электронов из полупроводника n-типа в полупроводник p-типа, а дырок в обратном направлении. Концентрация свободных носителей в приграничной области сокращается вследствие рекомбинации. Возникает обедненный слой (переход), имеющий большое удельное сопротивление. Условное обозначение диода Iпр Iобр Архитектура ЭВМ 23

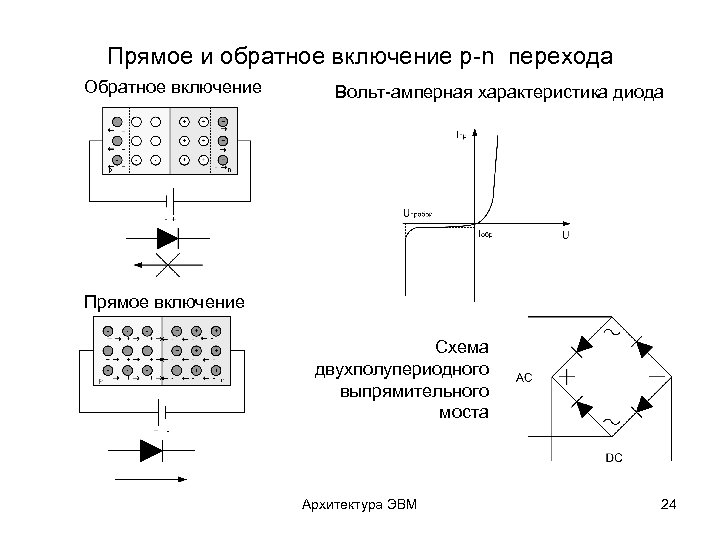

Прямое и обратное включение p-n перехода Обратное включение Вольт-амперная характеристика диода Прямое включение Схема двухполупериодного выпрямительного моста Архитектура ЭВМ 24

Прямое и обратное включение p-n перехода Обратное включение Вольт-амперная характеристика диода Прямое включение Схема двухполупериодного выпрямительного моста Архитектура ЭВМ 24

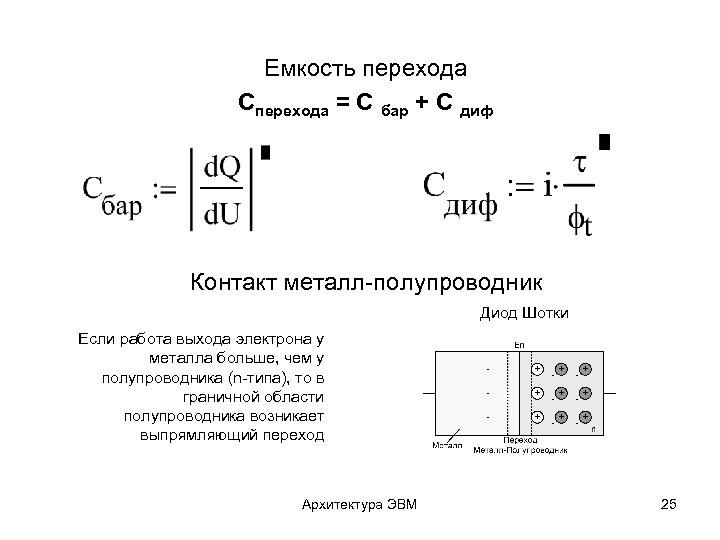

Емкость перехода Сперехода = С бар + С диф Контакт металл-полупроводник Диод Шотки Если работа выхода электрона у металла больше, чем у полупроводника (n-типа), то в граничной области полупроводника возникает выпрямляющий переход Архитектура ЭВМ 25

Емкость перехода Сперехода = С бар + С диф Контакт металл-полупроводник Диод Шотки Если работа выхода электрона у металла больше, чем у полупроводника (n-типа), то в граничной области полупроводника возникает выпрямляющий переход Архитектура ЭВМ 25

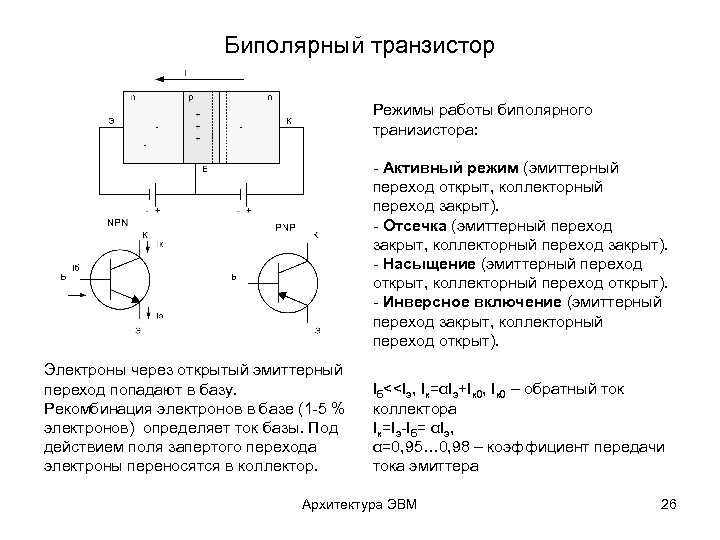

Биполярный транзистор Режимы работы биполярного транизистора: - Активный режим (эмиттерный переход открыт, коллекторный переход закрыт). - Отсечка (эмиттерный переход закрыт, коллекторный переход закрыт). - Насыщение (эмиттерный переход открыт, коллекторный переход открыт). - Инверсное включение (эмиттерный переход закрыт, коллекторный переход открыт). Электроны через открытый эмиттерный переход попадают в базу. Рекомбинация электронов в базе (1 -5 % электронов) определяет ток базы. Под действием поля запертого перехода электроны переносятся в коллектор. Iб<

Биполярный транзистор Режимы работы биполярного транизистора: - Активный режим (эмиттерный переход открыт, коллекторный переход закрыт). - Отсечка (эмиттерный переход закрыт, коллекторный переход закрыт). - Насыщение (эмиттерный переход открыт, коллекторный переход открыт). - Инверсное включение (эмиттерный переход закрыт, коллекторный переход открыт). Электроны через открытый эмиттерный переход попадают в базу. Рекомбинация электронов в базе (1 -5 % электронов) определяет ток базы. Под действием поля запертого перехода электроны переносятся в коллектор. Iб<

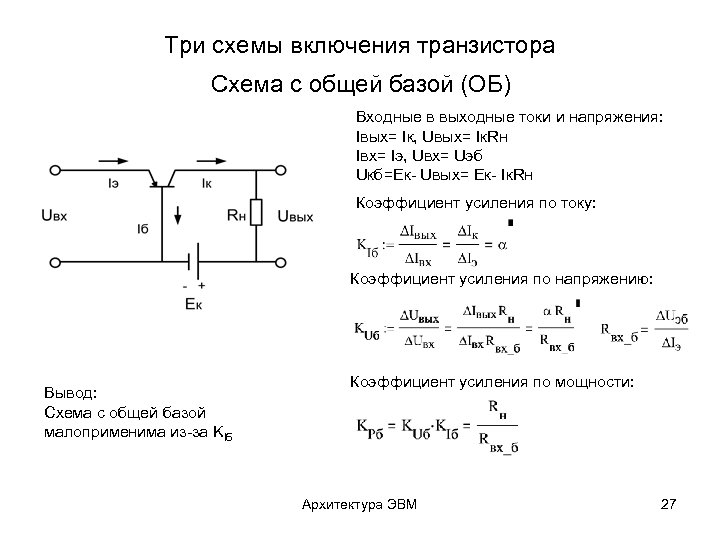

Три схемы включения транзистора Схема с общей базой (ОБ) Входные в выходные токи и напряжения: Iвых= Iк, Uвых= Iк. Rн Iвх= Iэ, Uвх= Uэб Uкб=Eк- Uвых= Eк- Iк. Rн Коэффициент усиления по току: Коэффициент усиления по напряжению: Вывод: Схема с общей базой малоприменима из-за KIб Коэффициент усиления по мощности: Архитектура ЭВМ 27

Три схемы включения транзистора Схема с общей базой (ОБ) Входные в выходные токи и напряжения: Iвых= Iк, Uвых= Iк. Rн Iвх= Iэ, Uвх= Uэб Uкб=Eк- Uвых= Eк- Iк. Rн Коэффициент усиления по току: Коэффициент усиления по напряжению: Вывод: Схема с общей базой малоприменима из-за KIб Коэффициент усиления по мощности: Архитектура ЭВМ 27

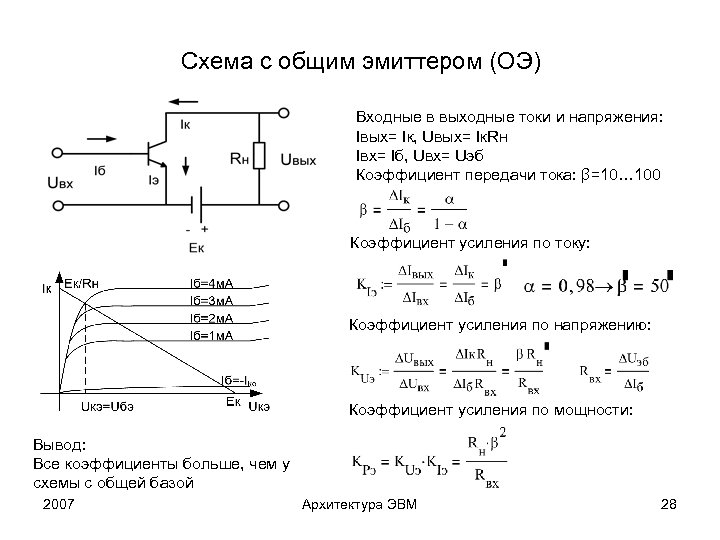

Схема с общим эмиттером (ОЭ) Входные в выходные токи и напряжения: Iвых= Iк, Uвых= Iк. Rн Iвх= Iб, Uвх= Uэб Коэффициент передачи тока: β=10… 100 Коэффициент усиления по току: Коэффициент усиления по напряжению: Коэффициент усиления по мощности: Вывод: Все коэффициенты больше, чем у схемы с общей базой 2007 Архитектура ЭВМ 28

Схема с общим эмиттером (ОЭ) Входные в выходные токи и напряжения: Iвых= Iк, Uвых= Iк. Rн Iвх= Iб, Uвх= Uэб Коэффициент передачи тока: β=10… 100 Коэффициент усиления по току: Коэффициент усиления по напряжению: Коэффициент усиления по мощности: Вывод: Все коэффициенты больше, чем у схемы с общей базой 2007 Архитектура ЭВМ 28

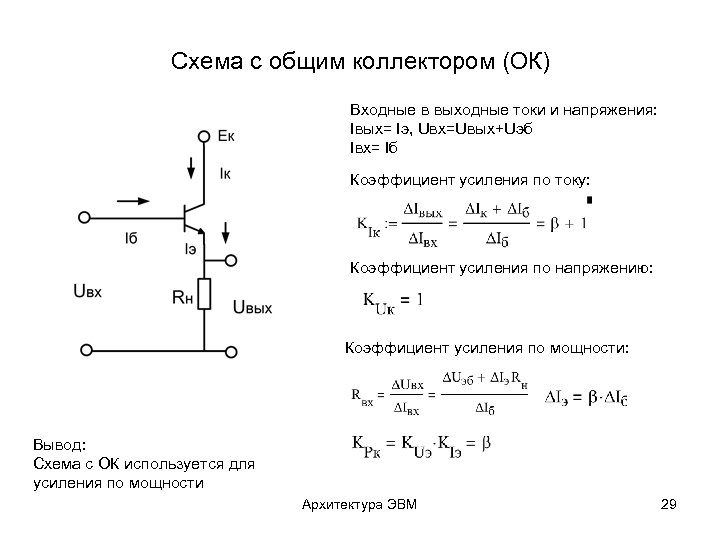

Схема с общим коллектором (ОК) Входные в выходные токи и напряжения: Iвых= Iэ, Uвх=Uвых+Uэб Iвх= Iб Коэффициент усиления по току: Коэффициент усиления по напряжению: Коэффициент усиления по мощности: Вывод: Схема с ОК используется для усиления по мощности Архитектура ЭВМ 29

Схема с общим коллектором (ОК) Входные в выходные токи и напряжения: Iвых= Iэ, Uвх=Uвых+Uэб Iвх= Iб Коэффициент усиления по току: Коэффициент усиления по напряжению: Коэффициент усиления по мощности: Вывод: Схема с ОК используется для усиления по мощности Архитектура ЭВМ 29

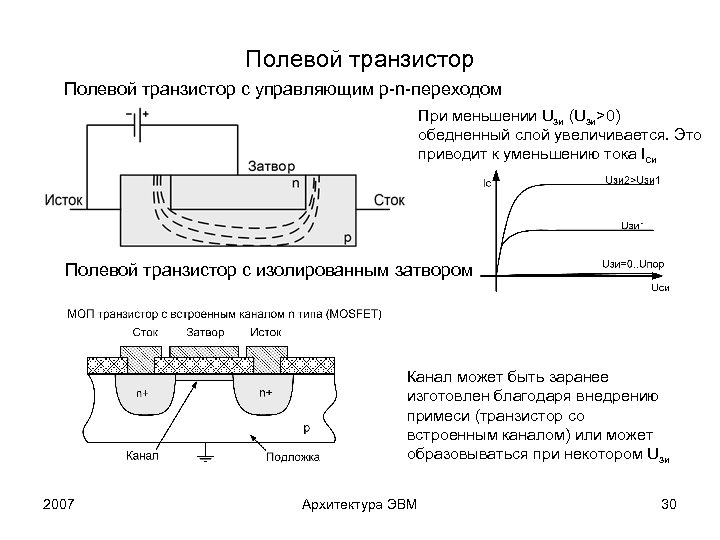

Полевой транзистор с управляющим p-n-переходом При меньшении Uзи (Uзи>0) обедненный слой увеличивается. Это приводит к уменьшению тока Iси Полевой транзистор с изолированным затвором Канал может быть заранее изготовлен благодаря внедрению примеси (транзистор со встроенным каналом) или может образовываться при некотором Uзи 2007 Архитектура ЭВМ 30

Полевой транзистор с управляющим p-n-переходом При меньшении Uзи (Uзи>0) обедненный слой увеличивается. Это приводит к уменьшению тока Iси Полевой транзистор с изолированным затвором Канал может быть заранее изготовлен благодаря внедрению примеси (транзистор со встроенным каналом) или может образовываться при некотором Uзи 2007 Архитектура ЭВМ 30

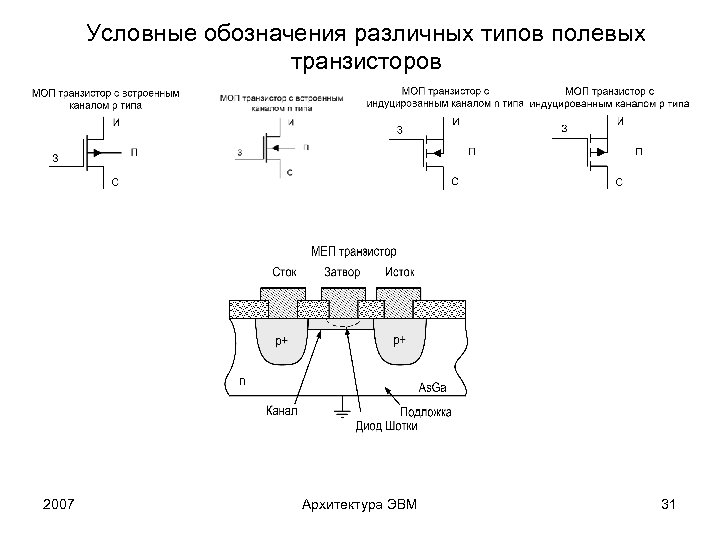

Условные обозначения различных типов полевых транзисторов 2007 Архитектура ЭВМ 31

Условные обозначения различных типов полевых транзисторов 2007 Архитектура ЭВМ 31

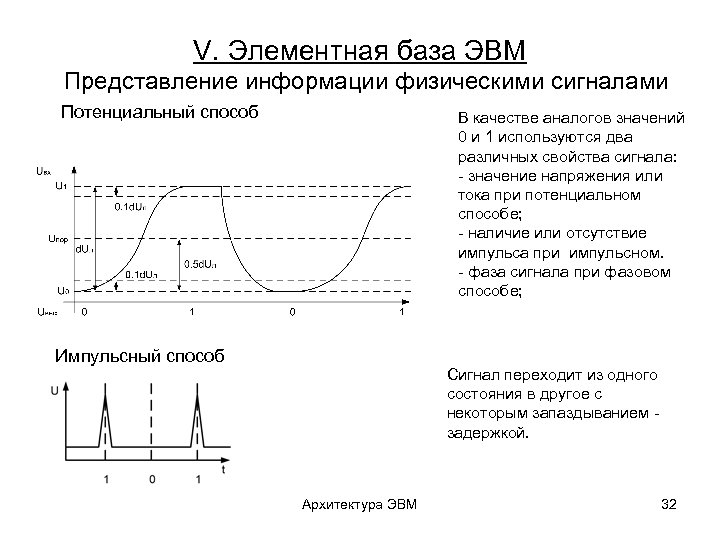

V. Элементная база ЭВМ Представление информации физическими сигналами Потенциальный способ В качестве аналогов значений 0 и 1 используются два различных свойства сигнала: - значение напряжения или тока при потенциальном способе; - наличие или отсутствие импульса при импульсном. - фаза сигнала при фазовом способе; Импульсный способ Сигнал переходит из одного состояния в другое с некоторым запаздыванием задержкой. Архитектура ЭВМ 32

V. Элементная база ЭВМ Представление информации физическими сигналами Потенциальный способ В качестве аналогов значений 0 и 1 используются два различных свойства сигнала: - значение напряжения или тока при потенциальном способе; - наличие или отсутствие импульса при импульсном. - фаза сигнала при фазовом способе; Импульсный способ Сигнал переходит из одного состояния в другое с некоторым запаздыванием задержкой. Архитектура ЭВМ 32

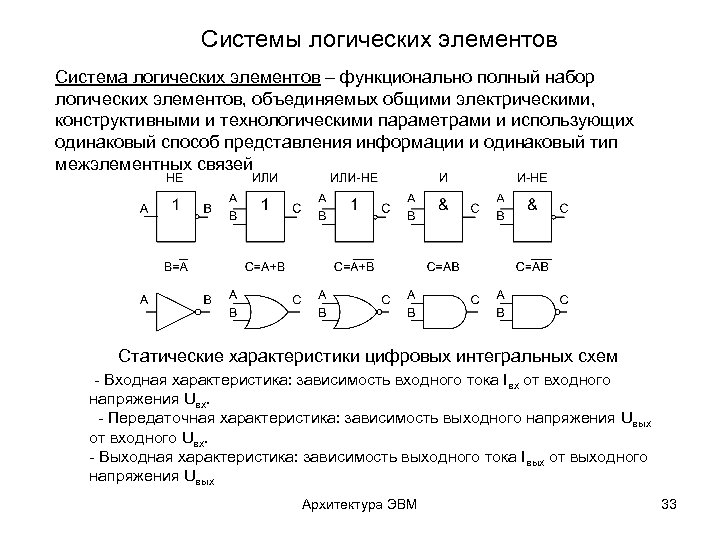

Системы логических элементов Система логических элементов – функционально полный набор логических элементов, объединяемых общими электрическими, конструктивными и технологическими параметрами и использующих одинаковый способ представления информации и одинаковый тип межэлементных связей Статические характеристики цифровых интегральных схем - Входная характеристика: зависимость входного тока Iвх от входного напряжения Uвх. - Передаточная характеристика: зависимость выходного напряжения Uвых от входного Uвх. - Выходная характеристика: зависимость выходного тока Iвых от выходного напряжения Uвых Архитектура ЭВМ 33

Системы логических элементов Система логических элементов – функционально полный набор логических элементов, объединяемых общими электрическими, конструктивными и технологическими параметрами и использующих одинаковый способ представления информации и одинаковый тип межэлементных связей Статические характеристики цифровых интегральных схем - Входная характеристика: зависимость входного тока Iвх от входного напряжения Uвх. - Передаточная характеристика: зависимость выходного напряжения Uвых от входного Uвх. - Выходная характеристика: зависимость выходного тока Iвых от выходного напряжения Uвых Архитектура ЭВМ 33

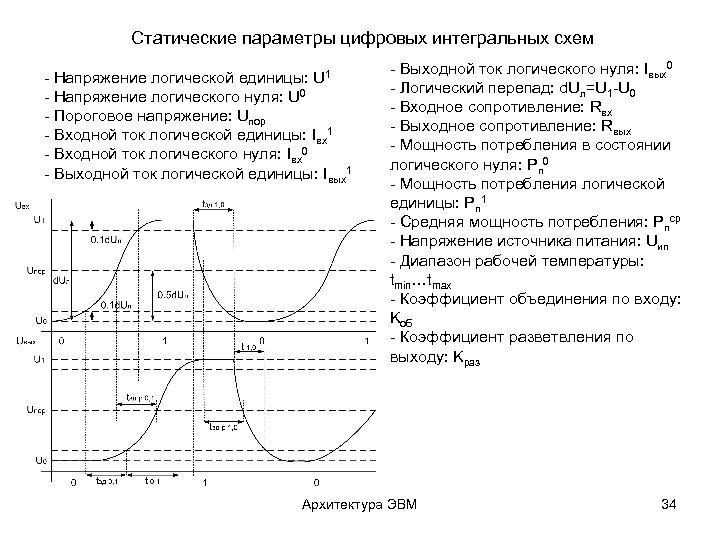

Статические параметры цифровых интегральных схем - Напряжение логической единицы: U 1 - Напряжение логического нуля: U 0 - Пороговое напряжение: Uпор - Входной ток логической единицы: Iвх1 - Входной ток логического нуля: Iвх0 - Выходной ток логической единицы: Iвых1 - Выходной ток логического нуля: Iвых0 - Логический перепад: d. Uл=U 1 -U 0 - Входное сопротивление: Rвх - Выходное сопротивление: Rвых - Мощность потребления в состоянии логического нуля: Pп 0 - Мощность потребления логической единицы: Pп 1 - Средняя мощность потребления: Pпср - Напряжение источника питания: Uип - Диапазон рабочей температуры: tmin…tmax - Коэффициент объединения по входу: Kоб - Коэффициент разветвления по выходу: Kраз Архитектура ЭВМ 34

Статические параметры цифровых интегральных схем - Напряжение логической единицы: U 1 - Напряжение логического нуля: U 0 - Пороговое напряжение: Uпор - Входной ток логической единицы: Iвх1 - Входной ток логического нуля: Iвх0 - Выходной ток логической единицы: Iвых1 - Выходной ток логического нуля: Iвых0 - Логический перепад: d. Uл=U 1 -U 0 - Входное сопротивление: Rвх - Выходное сопротивление: Rвых - Мощность потребления в состоянии логического нуля: Pп 0 - Мощность потребления логической единицы: Pп 1 - Средняя мощность потребления: Pпср - Напряжение источника питания: Uип - Диапазон рабочей температуры: tmin…tmax - Коэффициент объединения по входу: Kоб - Коэффициент разветвления по выходу: Kраз Архитектура ЭВМ 34

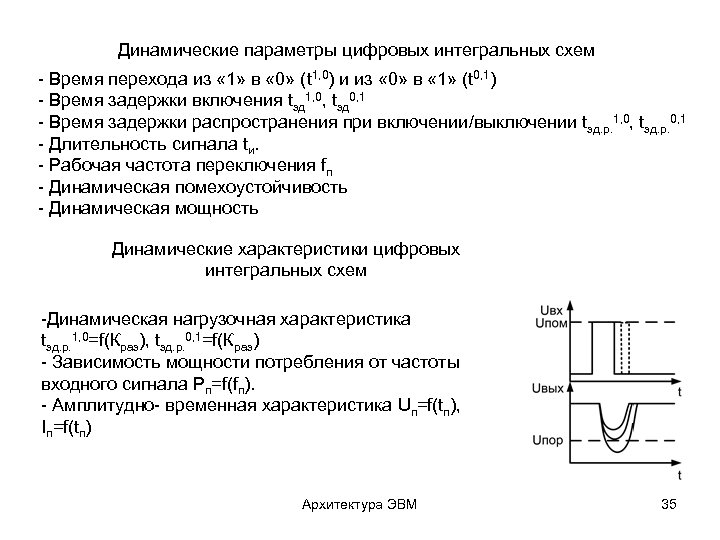

Динамические параметры цифровых интегральных схем - Время перехода из « 1» в « 0» (t 1, 0) и из « 0» в « 1» (t 0, 1) - Время задержки включения tзд 1, 0, tзд 0, 1 - Время задержки распространения при включении/выключении tзд. р. 1, 0, tзд. р. 0, 1 - Длительность сигнала tи. - Рабочая частота переключения fп - Динамическая помехоустойчивость - Динамическая мощность Динамические характеристики цифровых интегральных схем -Динамическая нагрузочная характеристика tзд. р. 1, 0=f(Краз), tзд. р. 0, 1=f(Краз) - Зависимость мощности потребления от частоты входного сигнала Pп=f(fп). - Амплитудно- временная характеристика Uп=f(tп), Iп=f(tп) Архитектура ЭВМ 35

Динамические параметры цифровых интегральных схем - Время перехода из « 1» в « 0» (t 1, 0) и из « 0» в « 1» (t 0, 1) - Время задержки включения tзд 1, 0, tзд 0, 1 - Время задержки распространения при включении/выключении tзд. р. 1, 0, tзд. р. 0, 1 - Длительность сигнала tи. - Рабочая частота переключения fп - Динамическая помехоустойчивость - Динамическая мощность Динамические характеристики цифровых интегральных схем -Динамическая нагрузочная характеристика tзд. р. 1, 0=f(Краз), tзд. р. 0, 1=f(Краз) - Зависимость мощности потребления от частоты входного сигнала Pп=f(fп). - Амплитудно- временная характеристика Uп=f(tп), Iп=f(tп) Архитектура ЭВМ 35

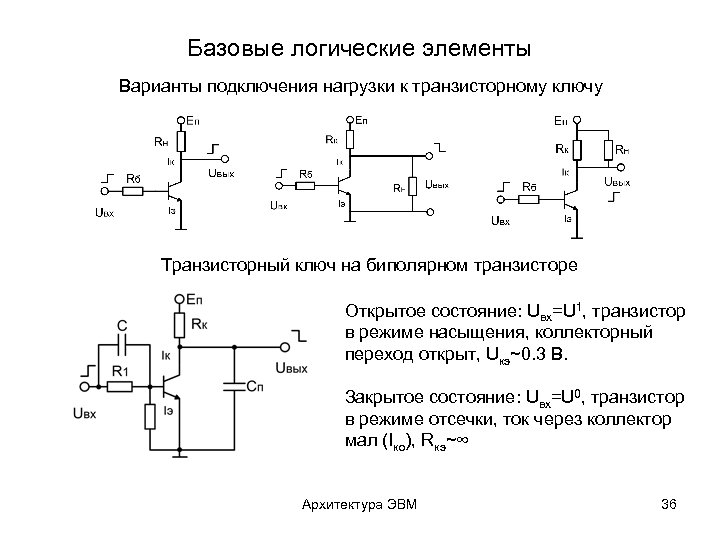

Базовые логические элементы Варианты подключения нагрузки к транзисторному ключу Транзисторный ключ на биполярном транзисторе Открытое состояние: Uвх=U 1, транзистор в режиме насыщения, коллекторный переход открыт, Uкэ~0. 3 В. Закрытое состояние: Uвх=U 0, транзистор в режиме отсечки, ток через коллектор мал (Iко), Rкэ~∞ Архитектура ЭВМ 36

Базовые логические элементы Варианты подключения нагрузки к транзисторному ключу Транзисторный ключ на биполярном транзисторе Открытое состояние: Uвх=U 1, транзистор в режиме насыщения, коллекторный переход открыт, Uкэ~0. 3 В. Закрытое состояние: Uвх=U 0, транзистор в режиме отсечки, ток через коллектор мал (Iко), Rкэ~∞ Архитектура ЭВМ 36

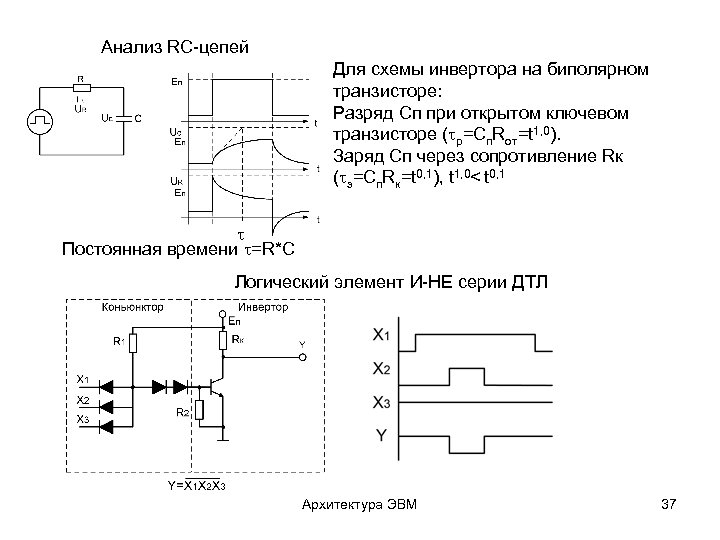

Анализ RC-цепей Для схемы инвертора на биполярном транзисторе: Разряд Cп при открытом ключевом транзисторе ( р=Сп. Rот=t 1, 0). Заряд Сп через сопротивление Rк ( з=Сп. Rк=t 0, 1), t 1, 0< t 0, 1 Постоянная времени =R*C Логический элемент И-НЕ серии ДТЛ Архитектура ЭВМ 37

Анализ RC-цепей Для схемы инвертора на биполярном транзисторе: Разряд Cп при открытом ключевом транзисторе ( р=Сп. Rот=t 1, 0). Заряд Сп через сопротивление Rк ( з=Сп. Rк=t 0, 1), t 1, 0< t 0, 1 Постоянная времени =R*C Логический элемент И-НЕ серии ДТЛ Архитектура ЭВМ 37

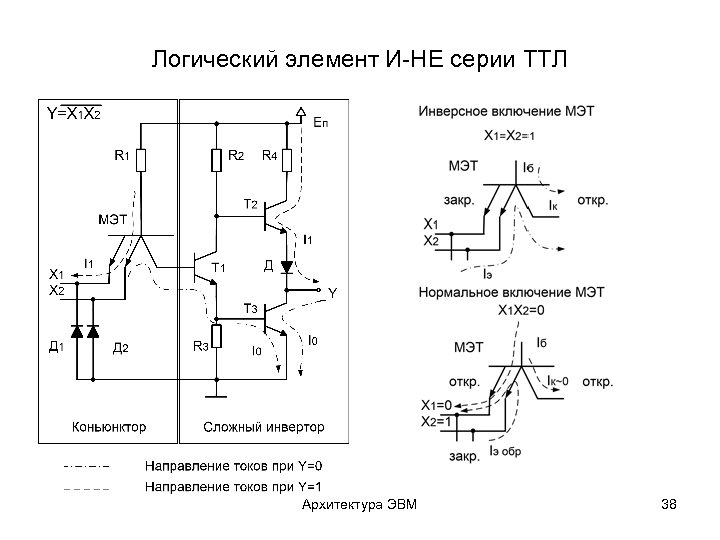

Логический элемент И-НЕ серии ТТЛ Архитектура ЭВМ 38

Логический элемент И-НЕ серии ТТЛ Архитектура ЭВМ 38

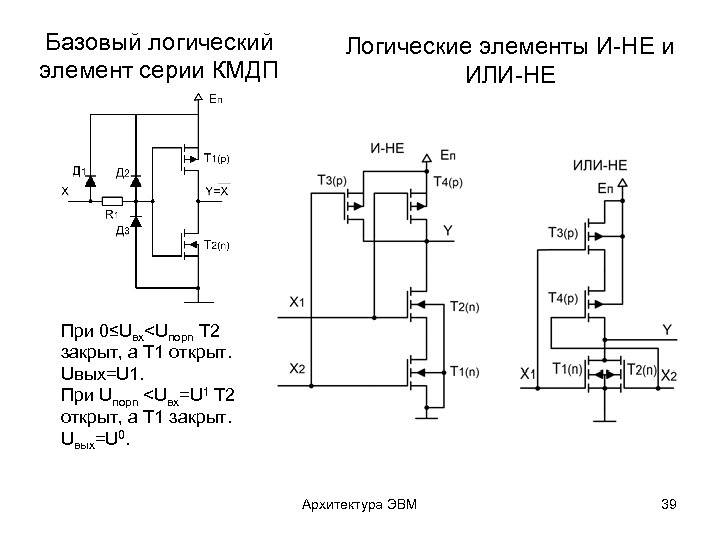

Базовый логический элемент серии КМДП Логические элементы И-НЕ и ИЛИ-НЕ При 0≤Uвх

Базовый логический элемент серии КМДП Логические элементы И-НЕ и ИЛИ-НЕ При 0≤Uвх

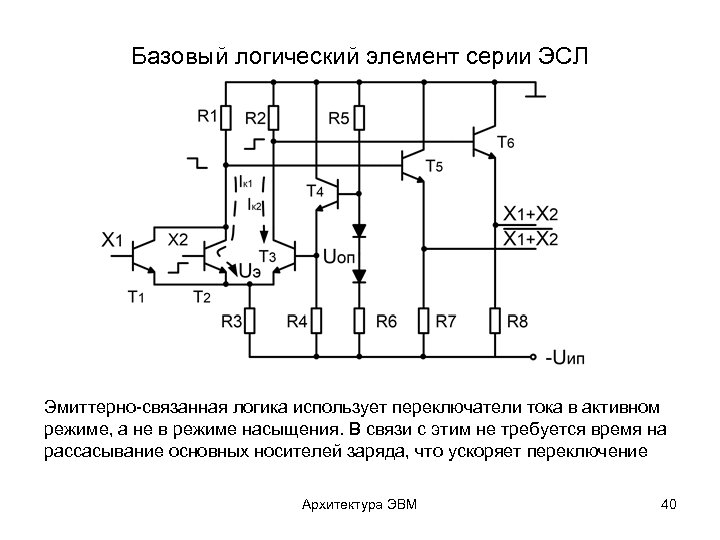

Базовый логический элемент серии ЭСЛ Эмиттерно-связанная логика использует переключатели тока в активном режиме, а не в режиме насыщения. В связи с этим не требуется время на рассасывание основных носителей заряда, что ускоряет переключение Архитектура ЭВМ 40

Базовый логический элемент серии ЭСЛ Эмиттерно-связанная логика использует переключатели тока в активном режиме, а не в режиме насыщения. В связи с этим не требуется время на рассасывание основных носителей заряда, что ускоряет переключение Архитектура ЭВМ 40

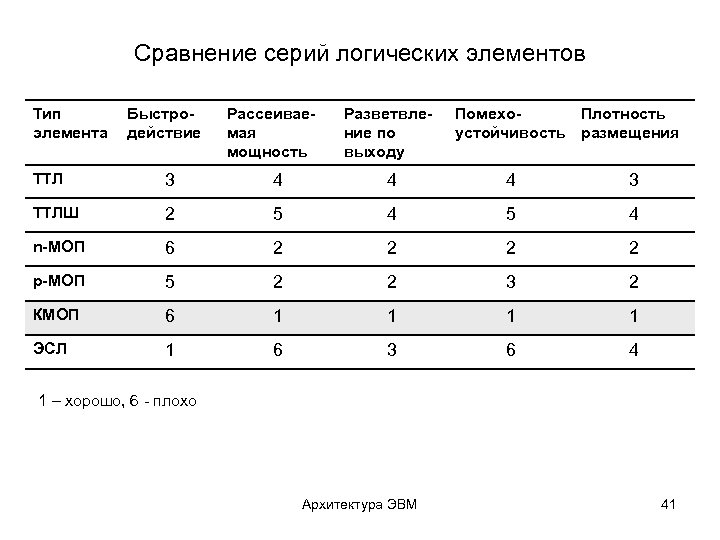

Сравнение серий логических элементов Тип элемента Быстродействие Рассеиваемая мощность Разветвление по выходу Помехо. Плотность устойчивость размещения ТТЛ 3 4 4 4 3 ТТЛШ 2 5 4 n-МОП 6 2 2 p-МОП 5 2 2 3 2 КМОП 6 1 1 ЭСЛ 1 6 3 6 4 1 – хорошо, 6 - плохо Архитектура ЭВМ 41

Сравнение серий логических элементов Тип элемента Быстродействие Рассеиваемая мощность Разветвление по выходу Помехо. Плотность устойчивость размещения ТТЛ 3 4 4 4 3 ТТЛШ 2 5 4 n-МОП 6 2 2 p-МОП 5 2 2 3 2 КМОП 6 1 1 ЭСЛ 1 6 3 6 4 1 – хорошо, 6 - плохо Архитектура ЭВМ 41

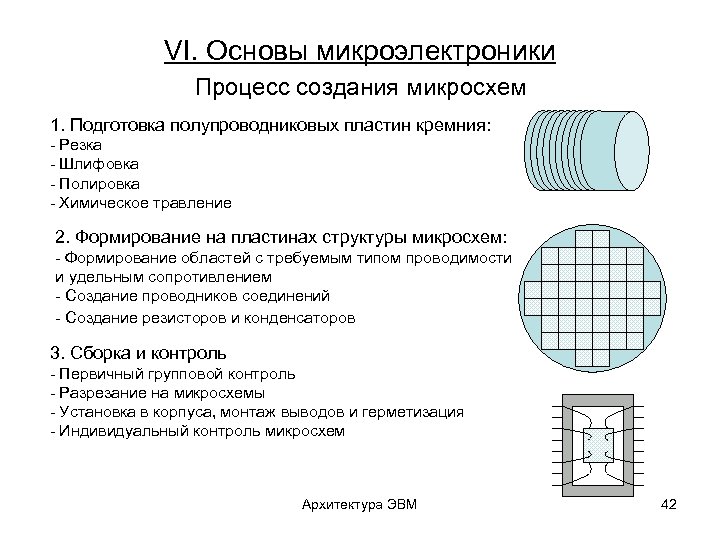

VI. Основы микроэлектроники Процесс создания микросхем 1. Подготовка полупроводниковых пластин кремния: - Резка - Шлифовка - Полировка - Химическое травление 2. Формирование на пластинах структуры микросхем: - Формирование областей с требуемым типом проводимости и удельным сопротивлением - Создание проводников соединений - Создание резисторов и конденсаторов 3. Сборка и контроль - Первичный групповой контроль - Разрезание на микросхемы - Установка в корпуса, монтаж выводов и герметизация - Индивидуальный контроль микросхем Архитектура ЭВМ 42

VI. Основы микроэлектроники Процесс создания микросхем 1. Подготовка полупроводниковых пластин кремния: - Резка - Шлифовка - Полировка - Химическое травление 2. Формирование на пластинах структуры микросхем: - Формирование областей с требуемым типом проводимости и удельным сопротивлением - Создание проводников соединений - Создание резисторов и конденсаторов 3. Сборка и контроль - Первичный групповой контроль - Разрезание на микросхемы - Установка в корпуса, монтаж выводов и герметизация - Индивидуальный контроль микросхем Архитектура ЭВМ 42

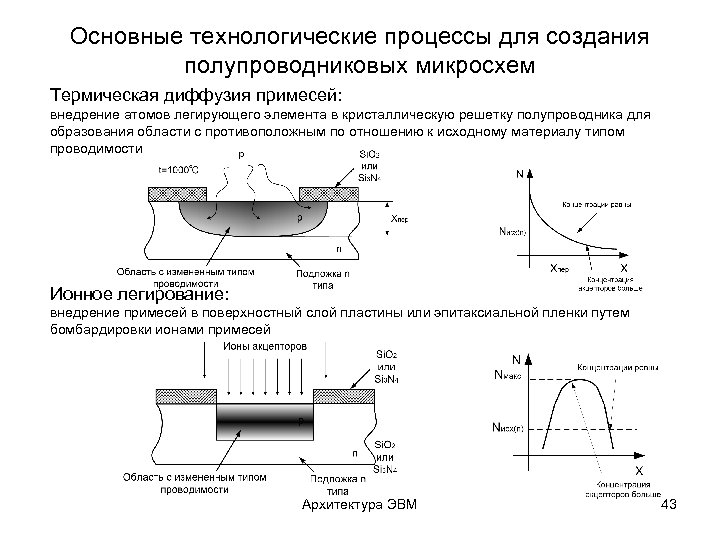

Основные технологические процессы для создания полупроводниковых микросхем Термическая диффузия примесей: внедрение атомов легирующего элемента в кристаллическую решетку полупроводника для образования области с противоположным по отношению к исходному материалу типом проводимости Ионное легирование: внедрение примесей в поверхностный слой пластины или эпитаксиальной пленки путем бомбардировки ионами примесей Архитектура ЭВМ 43

Основные технологические процессы для создания полупроводниковых микросхем Термическая диффузия примесей: внедрение атомов легирующего элемента в кристаллическую решетку полупроводника для образования области с противоположным по отношению к исходному материалу типом проводимости Ионное легирование: внедрение примесей в поверхностный слой пластины или эпитаксиальной пленки путем бомбардировки ионами примесей Архитектура ЭВМ 43

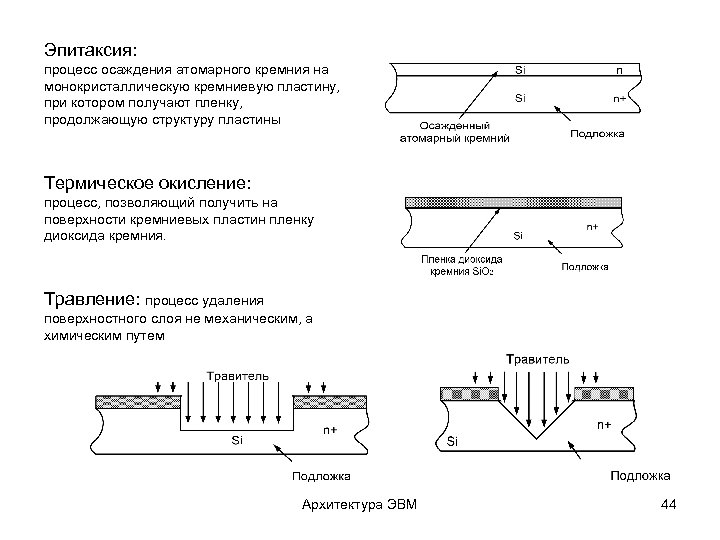

Эпитаксия: процесс осаждения атомарного кремния на монокристаллическую кремниевую пластину, при котором получают пленку, продолжающую структуру пластины Термическое окисление: процесс, позволяющий получить на поверхности кремниевых пластин пленку диоксида кремния. Травление: процесс удаления поверхностного слоя не механическим, а химическим путем Архитектура ЭВМ 44

Эпитаксия: процесс осаждения атомарного кремния на монокристаллическую кремниевую пластину, при котором получают пленку, продолжающую структуру пластины Термическое окисление: процесс, позволяющий получить на поверхности кремниевых пластин пленку диоксида кремния. Травление: процесс удаления поверхностного слоя не механическим, а химическим путем Архитектура ЭВМ 44

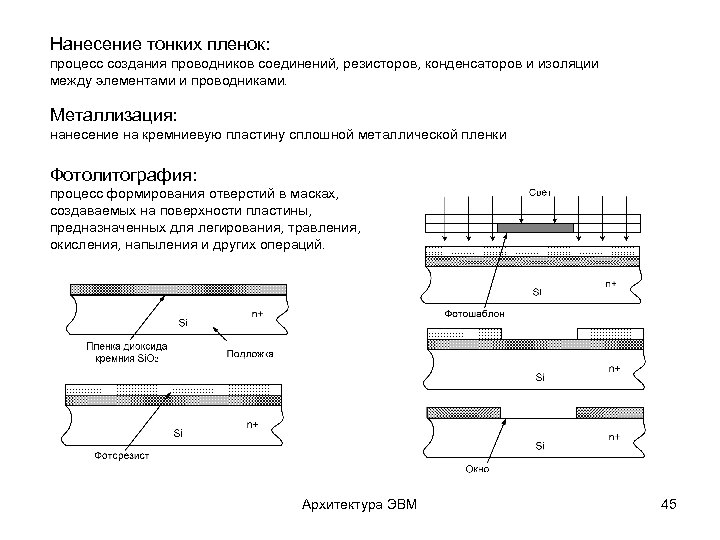

Нанесение тонких пленок: процесс создания проводников соединений, резисторов, конденсаторов и изоляции между элементами и проводниками. Металлизация: нанесение на кремниевую пластину сплошной металлической пленки Фотолитография: процесс формирования отверстий в масках, создаваемых на поверхности пластины, предназначенных для легирования, травления, окисления, напыления и других операций. Архитектура ЭВМ 45

Нанесение тонких пленок: процесс создания проводников соединений, резисторов, конденсаторов и изоляции между элементами и проводниками. Металлизация: нанесение на кремниевую пластину сплошной металлической пленки Фотолитография: процесс формирования отверстий в масках, создаваемых на поверхности пластины, предназначенных для легирования, травления, окисления, напыления и других операций. Архитектура ЭВМ 45

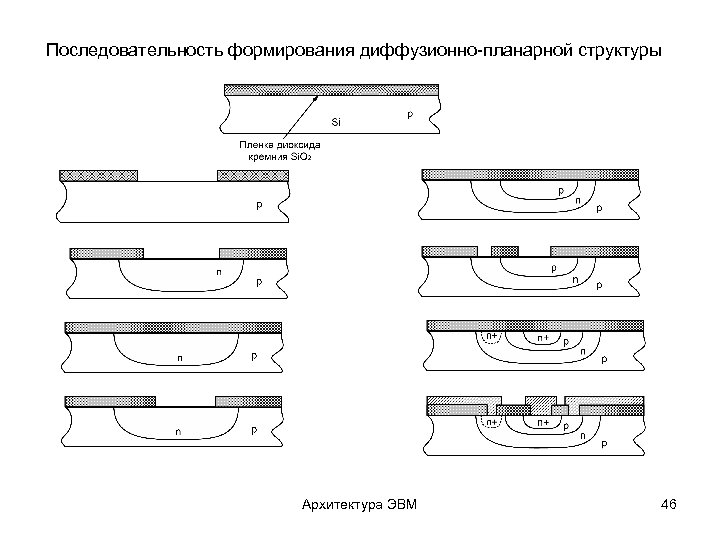

Последовательность формирования диффузионно-планарной структуры Архитектура ЭВМ 46

Последовательность формирования диффузионно-планарной структуры Архитектура ЭВМ 46

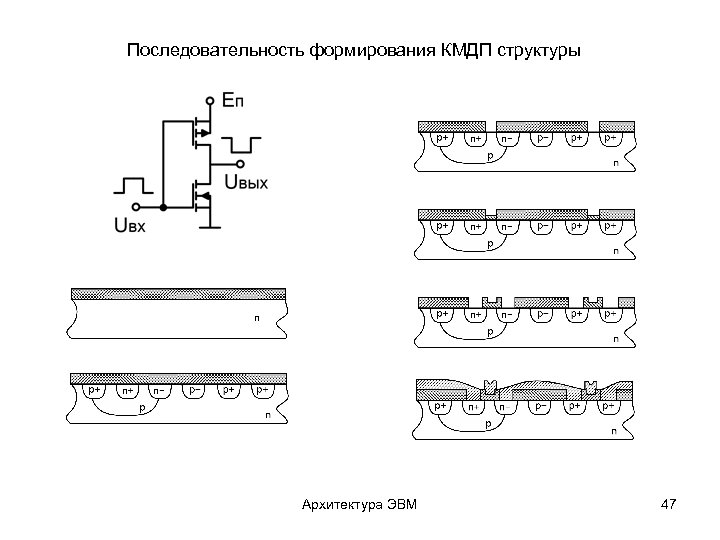

Последовательность формирования КМДП структуры Архитектура ЭВМ 47

Последовательность формирования КМДП структуры Архитектура ЭВМ 47

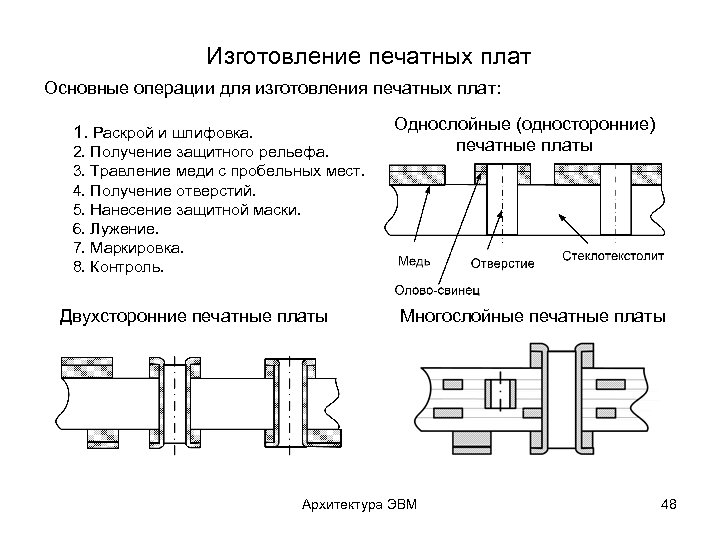

Изготовление печатных плат Основные операции для изготовления печатных плат: 1. Раскрой и шлифовка. 2. Получение защитного рельефа. 3. Травление меди с пробельных мест. 4. Получение отверстий. 5. Нанесение защитной маски. 6. Лужение. 7. Маркировка. 8. Контроль. Двухсторонние печатные платы Однослойные (односторонние) печатные платы Многослойные печатные платы Архитектура ЭВМ 48

Изготовление печатных плат Основные операции для изготовления печатных плат: 1. Раскрой и шлифовка. 2. Получение защитного рельефа. 3. Травление меди с пробельных мест. 4. Получение отверстий. 5. Нанесение защитной маски. 6. Лужение. 7. Маркировка. 8. Контроль. Двухсторонние печатные платы Однослойные (односторонние) печатные платы Многослойные печатные платы Архитектура ЭВМ 48