Лекция Арх тема 1.9.pptx

- Количество слайдов: 13

Архитектура ЭВМ и ВС Тема 1. 9. Режимы работы процессора Преподаватель: Шершова Л. Н.

Архитектура ЭВМ и ВС Тема 1. 9. Режимы работы процессора Преподаватель: Шершова Л. Н.

Тема 1. 9. Режимы работы процессора Занятие 27. Режимы работы процессора. Характеристика реального режима процессора 8086. Адресация памяти реального режима. Основные понятия защищенного режима. Адресация в защищенном режиме. Дескрипторы и таблицы. Системы привилегий. Защита. Переключение задач. Страничное управление памятью. Виртуализация прерываний. Переключение между реальным и защищенным режимами.

Тема 1. 9. Режимы работы процессора Занятие 27. Режимы работы процессора. Характеристика реального режима процессора 8086. Адресация памяти реального режима. Основные понятия защищенного режима. Адресация в защищенном режиме. Дескрипторы и таблицы. Системы привилегий. Защита. Переключение задач. Страничное управление памятью. Виртуализация прерываний. Переключение между реальным и защищенным режимами.

Тема 1. 9. Режимы работы процессора ОБЩИЕ ПОНЯТИЯ по КУРСУ «Архитектура ЭВМ и ВС» : 1. Структурно любая ЭВМ состоит из процессора, памяти и устройств ввода-вывода. 2. Память ЭВМ состоит из ячеек одинакового размера, каждая из которых имеет свой уникальный номер - адрес и может хранить команду или число. Количество элементов памяти (число битов), из которых составлена каждая ячейка, определяет разрядность машинных слов - команд и данных или их частей. 3. Все команды в качестве одной (может быть единственной) части содержат код операции, задающий действие, исполняемое по этой команде. Кроме кода операции команда может иметь несколько адресных частей, содержащих адреса операндов, результата и следующей команды. 4. В микро. ЭВМ используются безадресные, одноадресные и реже двухадресные команды. В одноадресных командах один из операндов выбирается из специального регистра - аккумулятора. В него же заносится и результат операции. Безадресные команды или задают какое-либо действие с устройствами ЭВМ (например, останов), или используются для работы с операндами, имеющими фиксированное расположение (чаще всего с аккумулятором). 5. Процессор - это совокупность устройства управления, арифметико-логического устройства и связанных с ними регистров. Он организует процесс обработки информации путем выборки и последовательного выполнения команд программы, находящейся в памяти ЭВМ. 6. Арифметико-логическое устройство выполняет ряд арифметических и логических операций над одним или двумя операндами, пересылаемыми в него из памяти и (или) регистров процессора. Результат операции пересылается в один из регистров процессора. 7. Устройство управления, используя регистры процессора, управляет обменом информации между памятью, устройствами ввода-вывода и АЛУ, а также выполнением операций в АЛУ. 8. Регистры процессора служат для хранения промежуточных результатов вычислений и различной управляющей информации. Наиболее важные из них - это регистр команд (содержит исполняемую команду) и счетчик команд (содержит адрес следующей команды). В процессе работы ЭВМ последовательно выполняет набор достаточно простых операций: выборку команды, определение ее типа, исполнение команды и определение адреса следующей команды. Разнообразие же решаемых на ЭВМ задач определяется не ее устройством, а программой и возможностями подключаемых к ЭВМ устройств ввода-вывода.

Тема 1. 9. Режимы работы процессора ОБЩИЕ ПОНЯТИЯ по КУРСУ «Архитектура ЭВМ и ВС» : 1. Структурно любая ЭВМ состоит из процессора, памяти и устройств ввода-вывода. 2. Память ЭВМ состоит из ячеек одинакового размера, каждая из которых имеет свой уникальный номер - адрес и может хранить команду или число. Количество элементов памяти (число битов), из которых составлена каждая ячейка, определяет разрядность машинных слов - команд и данных или их частей. 3. Все команды в качестве одной (может быть единственной) части содержат код операции, задающий действие, исполняемое по этой команде. Кроме кода операции команда может иметь несколько адресных частей, содержащих адреса операндов, результата и следующей команды. 4. В микро. ЭВМ используются безадресные, одноадресные и реже двухадресные команды. В одноадресных командах один из операндов выбирается из специального регистра - аккумулятора. В него же заносится и результат операции. Безадресные команды или задают какое-либо действие с устройствами ЭВМ (например, останов), или используются для работы с операндами, имеющими фиксированное расположение (чаще всего с аккумулятором). 5. Процессор - это совокупность устройства управления, арифметико-логического устройства и связанных с ними регистров. Он организует процесс обработки информации путем выборки и последовательного выполнения команд программы, находящейся в памяти ЭВМ. 6. Арифметико-логическое устройство выполняет ряд арифметических и логических операций над одним или двумя операндами, пересылаемыми в него из памяти и (или) регистров процессора. Результат операции пересылается в один из регистров процессора. 7. Устройство управления, используя регистры процессора, управляет обменом информации между памятью, устройствами ввода-вывода и АЛУ, а также выполнением операций в АЛУ. 8. Регистры процессора служат для хранения промежуточных результатов вычислений и различной управляющей информации. Наиболее важные из них - это регистр команд (содержит исполняемую команду) и счетчик команд (содержит адрес следующей команды). В процессе работы ЭВМ последовательно выполняет набор достаточно простых операций: выборку команды, определение ее типа, исполнение команды и определение адреса следующей команды. Разнообразие же решаемых на ЭВМ задач определяется не ее устройством, а программой и возможностями подключаемых к ЭВМ устройств ввода-вывода.

Тема 1. 9. Режимы работы процессора Наиболее важными компонентами любого компьютера, обусловливающими его основные характеристики, являются микропроцессоры, системные платы и интерфейсы. 1. Микропроцессоры Микропроцессор (МП), или central processing unit (CPU) — функционально-законченное программноуправляемое устройство обработки информации, выполненное в виде одной или нескольких больших (БИС) или сверхбольших (СБИС) интегральных схем. Микропроцессор выполняет следующие функции: 1)вычисление адресов команд и операндов; 2) выборку и дешифрацию команд из основной памяти (ОП); 3)выборку данных из ОП, регистров МПП и регистров адаптеров внешних устройств (ВУ); прием и обработку запросов и команд от адаптеров на обслуживание ВУ; обработку данных и их запись в ОП, регистры МПП и регистры адаптеров ВУ; выработку управляющих сигналов для всех прочих узлов и блоков ПК; переход к следующей команде. Основными параметрами микропроцессоров являются: q разрядность; q рабочая тактовая частота; q размер кэш-памяти; q состав инструкций; q конструктив; q рабочее напряжение и т. п.

Тема 1. 9. Режимы работы процессора Наиболее важными компонентами любого компьютера, обусловливающими его основные характеристики, являются микропроцессоры, системные платы и интерфейсы. 1. Микропроцессоры Микропроцессор (МП), или central processing unit (CPU) — функционально-законченное программноуправляемое устройство обработки информации, выполненное в виде одной или нескольких больших (БИС) или сверхбольших (СБИС) интегральных схем. Микропроцессор выполняет следующие функции: 1)вычисление адресов команд и операндов; 2) выборку и дешифрацию команд из основной памяти (ОП); 3)выборку данных из ОП, регистров МПП и регистров адаптеров внешних устройств (ВУ); прием и обработку запросов и команд от адаптеров на обслуживание ВУ; обработку данных и их запись в ОП, регистры МПП и регистры адаптеров ВУ; выработку управляющих сигналов для всех прочих узлов и блоков ПК; переход к следующей команде. Основными параметрами микропроцессоров являются: q разрядность; q рабочая тактовая частота; q размер кэш-памяти; q состав инструкций; q конструктив; q рабочее напряжение и т. п.

Тема 1. 9. Режимы работы процессора Разрядность шины данных микропроцессора определяет количество разрядов, над которыми одновременно могут выполняться операции; разрядность шины адреса МП определяет его адресное пространство. Адресное пространство — это максимальное количество ячеек основной памяти, которое может быть непосредственно адресовано микропроцессором. Рабочая тактовая частота МП во многом определяет его внутреннее быстродействие, ибо каждая команда выполняется за определенное количество тактов. Быстродействие (производительность) ПК зависит также и от тактовой частоты шины материнской платы, с которой работает МП. Кэш-память, устанавливаемая на плате МП, имеет два-три уровня: L 1 - память 1 -го уровня, находящаяся внутри основной микросхемы (ядра) МП и работающая всегда на полной частоте МП (впервые L 1 был введен в МП 486 и 386 SLC); L 2 - память 2 -го уровня - кристалл, размещаемый на плате МП и связанный с ядром внутренней микропроцессорной шиной (впервые введен в МП Pentium II). Память L 2 может работать на полной или половинной частоте МП. Эффективность этой кэшпамяти зависит и от пропускной способности микропроцессорной шины. Состав инструкций — перечень, вид и тип команд, автоматически исполняемых МП. От типа команд зависит даже классификационная группа МП (CISC, RISC, VLIM). Перечень и вид команд определяют непосредственно те процедуры, которые могут выполняться над данными в МП, и те категории данных, над которыми могут выполняться эти процедуры. Дополнительные инструкции в небольших количествах вводились во многих МП (286, 486, Pentium Pro и т. д. ). Но существенное изменение состава инструкций произошло в МП 386 (этот состав далее принят за базовый), Pentium MMX, Pentium III, Pentium 4 и т. д. Конструктив определяет те физические разъемные соединения, в которые устанавливается МП и которые определяют пригодность материнской платы для установки МП. Разные разъемы имеют разную конструкцию (например, Slot — это щелевой разъем, Socket — разъем-гнездо). При этом имеется разное количество контактов, на которые подаются сигналы и рабочие напряжения. Рабочее напряжение также определяет пригодность материнской платы для установки МП. Первый микропроцессор был выпущен в 1971 году фирмой Intel (США) — МП 4004. В настоящее время разными фирмами выпускается много десятков различных микропроцессоров, но наиболее популярными и распространенными являются микропроцессоры фирмы Intel, AMD и им подобные.

Тема 1. 9. Режимы работы процессора Разрядность шины данных микропроцессора определяет количество разрядов, над которыми одновременно могут выполняться операции; разрядность шины адреса МП определяет его адресное пространство. Адресное пространство — это максимальное количество ячеек основной памяти, которое может быть непосредственно адресовано микропроцессором. Рабочая тактовая частота МП во многом определяет его внутреннее быстродействие, ибо каждая команда выполняется за определенное количество тактов. Быстродействие (производительность) ПК зависит также и от тактовой частоты шины материнской платы, с которой работает МП. Кэш-память, устанавливаемая на плате МП, имеет два-три уровня: L 1 - память 1 -го уровня, находящаяся внутри основной микросхемы (ядра) МП и работающая всегда на полной частоте МП (впервые L 1 был введен в МП 486 и 386 SLC); L 2 - память 2 -го уровня - кристалл, размещаемый на плате МП и связанный с ядром внутренней микропроцессорной шиной (впервые введен в МП Pentium II). Память L 2 может работать на полной или половинной частоте МП. Эффективность этой кэшпамяти зависит и от пропускной способности микропроцессорной шины. Состав инструкций — перечень, вид и тип команд, автоматически исполняемых МП. От типа команд зависит даже классификационная группа МП (CISC, RISC, VLIM). Перечень и вид команд определяют непосредственно те процедуры, которые могут выполняться над данными в МП, и те категории данных, над которыми могут выполняться эти процедуры. Дополнительные инструкции в небольших количествах вводились во многих МП (286, 486, Pentium Pro и т. д. ). Но существенное изменение состава инструкций произошло в МП 386 (этот состав далее принят за базовый), Pentium MMX, Pentium III, Pentium 4 и т. д. Конструктив определяет те физические разъемные соединения, в которые устанавливается МП и которые определяют пригодность материнской платы для установки МП. Разные разъемы имеют разную конструкцию (например, Slot — это щелевой разъем, Socket — разъем-гнездо). При этом имеется разное количество контактов, на которые подаются сигналы и рабочие напряжения. Рабочее напряжение также определяет пригодность материнской платы для установки МП. Первый микропроцессор был выпущен в 1971 году фирмой Intel (США) — МП 4004. В настоящее время разными фирмами выпускается много десятков различных микропроцессоров, но наиболее популярными и распространенными являются микропроцессоры фирмы Intel, AMD и им подобные.

Тема 1. 9. Режимы работы процессора На одном кристалле микропроцессора содержатся: центральный процессор ALU, блок процессора с плавающей точкой FPU, устройство управления УУ, диспетчер памяти MMU, блок предвыборки команд и данных БПКи. Д, интерфейс магистрали ИМ. Рассмотрим на примере 32 разрядного МП. ЦП включает в себя арифметическо-логическое устройство ALU –arithmetic-logical unit, восемь 32 -разрядных регистров общего назначения и многоразрядный сдвигатель, используемый при арифметических и циклических сдвигах, операциях умножения и деления. Блок процессора с плавающей точкой (FPU – floating point unit) имеет собственные регистры данных и управления, работает параллельно с ЦП и обеспечивает обработку данных с плавающей точкой. Устройство управления включает дешифратор команд, которые поступают из блока предварительной обработки (очереди команд), и блока микропрограммного управления, содержащего ПЗУ микрокоманд. УУ формирует последовательность микрокоманд, которые поступают на все блоки МП, обеспечивающие выполнение очередной команды и переход на следующую. Диспетчер памяти MMU (memory management unit) состоит из блока сегментации и блока страничной адресации. Он осуществляет 2 -ступенчатое формирование адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Здесь обеспечивается режим работы реальных адресов (реальный режим) и режим защищѐнных виртуальных адресов (защищѐнный режим). В первом случае реализуется расширенный набор команд и допускается увеличение разрядности адресов и операндов до 32. формирование адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. В защищѐнномрежиме могут одновременно выполняться несколько задач. Сегментация является средством управления пространством логических адресов, она обеспечивает мобильность и повышает защищѐнность программ. Сегментированная память представляет собой набор блоков, характеризуемых определѐнными атрибутами: расположение, размер, тип (программа, данные), характеристики защиты. Блок страничной адресации действует на более низком уровне, разбиение на страницы возможно только в защищѐнномрежиме. Каждый сегмент делится на страницы по 4 Кбайт, которые могут размещаться в любом месте памяти ОЗУ. Блок предвыборки команд и данных включает устройство предвыборки команд и внутреннюю кэш-память. Первое осуществляет заполнение очереди команд длиной 32 бита, приѐм и выборка байтов из памяти производится в промежутках между магистральными циклами команд. Внутренняя кэш-память позволяет существенно повысить производительность МП за счѐт буферизации в ней часто используемых команд и данных, сокращения числа обращений к внешней памяти. Интерфейс магистрали ИМ реализует протоколы обмена МП с памятью, другими активными устройствами системы.

Тема 1. 9. Режимы работы процессора На одном кристалле микропроцессора содержатся: центральный процессор ALU, блок процессора с плавающей точкой FPU, устройство управления УУ, диспетчер памяти MMU, блок предвыборки команд и данных БПКи. Д, интерфейс магистрали ИМ. Рассмотрим на примере 32 разрядного МП. ЦП включает в себя арифметическо-логическое устройство ALU –arithmetic-logical unit, восемь 32 -разрядных регистров общего назначения и многоразрядный сдвигатель, используемый при арифметических и циклических сдвигах, операциях умножения и деления. Блок процессора с плавающей точкой (FPU – floating point unit) имеет собственные регистры данных и управления, работает параллельно с ЦП и обеспечивает обработку данных с плавающей точкой. Устройство управления включает дешифратор команд, которые поступают из блока предварительной обработки (очереди команд), и блока микропрограммного управления, содержащего ПЗУ микрокоманд. УУ формирует последовательность микрокоманд, которые поступают на все блоки МП, обеспечивающие выполнение очередной команды и переход на следующую. Диспетчер памяти MMU (memory management unit) состоит из блока сегментации и блока страничной адресации. Он осуществляет 2 -ступенчатое формирование адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Здесь обеспечивается режим работы реальных адресов (реальный режим) и режим защищѐнных виртуальных адресов (защищѐнный режим). В первом случае реализуется расширенный набор команд и допускается увеличение разрядности адресов и операндов до 32. формирование адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. В защищѐнномрежиме могут одновременно выполняться несколько задач. Сегментация является средством управления пространством логических адресов, она обеспечивает мобильность и повышает защищѐнность программ. Сегментированная память представляет собой набор блоков, характеризуемых определѐнными атрибутами: расположение, размер, тип (программа, данные), характеристики защиты. Блок страничной адресации действует на более низком уровне, разбиение на страницы возможно только в защищѐнномрежиме. Каждый сегмент делится на страницы по 4 Кбайт, которые могут размещаться в любом месте памяти ОЗУ. Блок предвыборки команд и данных включает устройство предвыборки команд и внутреннюю кэш-память. Первое осуществляет заполнение очереди команд длиной 32 бита, приѐм и выборка байтов из памяти производится в промежутках между магистральными циклами команд. Внутренняя кэш-память позволяет существенно повысить производительность МП за счѐт буферизации в ней часто используемых команд и данных, сокращения числа обращений к внешней памяти. Интерфейс магистрали ИМ реализует протоколы обмена МП с памятью, другими активными устройствами системы.

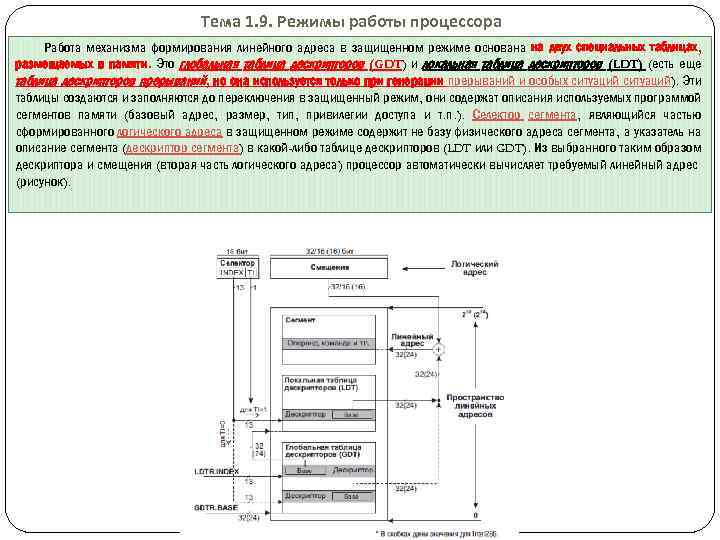

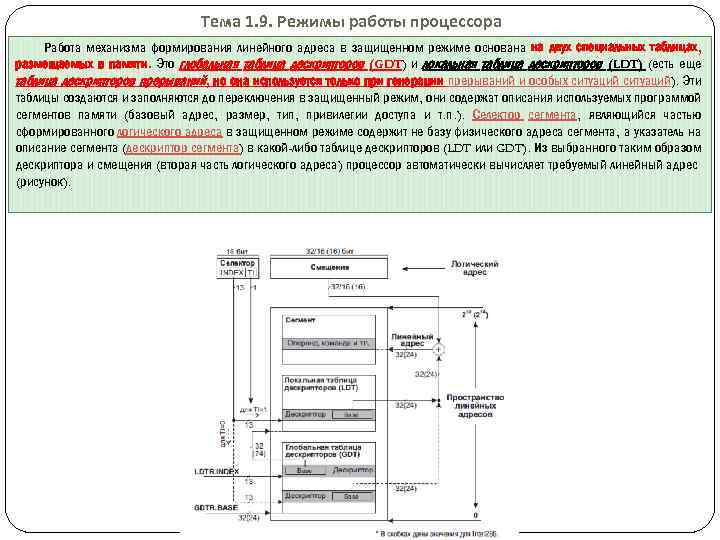

Тема 1. 9. Режимы работы процессора Работа механизма формирования линейного адреса в защищенном режиме основана на двух специальных таблицах, размещаемых в памяти. Это глобальная таблица дескрипторов (GDT) и локальная таблица дескрипторов (LDT) (есть еще таблица дескрипторов прерываний, но она используется только при генерации прерываний и особых ситуаций). Эти таблицы создаются и заполняются до переключения в защищенный режим, они содержат описания используемых программой сегментов памяти (базовый адрес, размер, тип, привилегии доступа и т. п. ). Селектор сегмента, являющийся частью сформированного логического адреса в защищенном режиме содержит не базу физического адреса сегмента, а указатель на описание сегмента (дескриптор сегмента) в какой-либо таблице дескрипторов (LDT или GDT). Из выбранного таким образом дескриптора и смещения (вторая часть логического адреса) процессор автоматически вычисляет требуемый линейный адрес (рисунок).

Тема 1. 9. Режимы работы процессора Работа механизма формирования линейного адреса в защищенном режиме основана на двух специальных таблицах, размещаемых в памяти. Это глобальная таблица дескрипторов (GDT) и локальная таблица дескрипторов (LDT) (есть еще таблица дескрипторов прерываний, но она используется только при генерации прерываний и особых ситуаций). Эти таблицы создаются и заполняются до переключения в защищенный режим, они содержат описания используемых программой сегментов памяти (базовый адрес, размер, тип, привилегии доступа и т. п. ). Селектор сегмента, являющийся частью сформированного логического адреса в защищенном режиме содержит не базу физического адреса сегмента, а указатель на описание сегмента (дескриптор сегмента) в какой-либо таблице дескрипторов (LDT или GDT). Из выбранного таким образом дескриптора и смещения (вторая часть логического адреса) процессор автоматически вычисляет требуемый линейный адрес (рисунок).

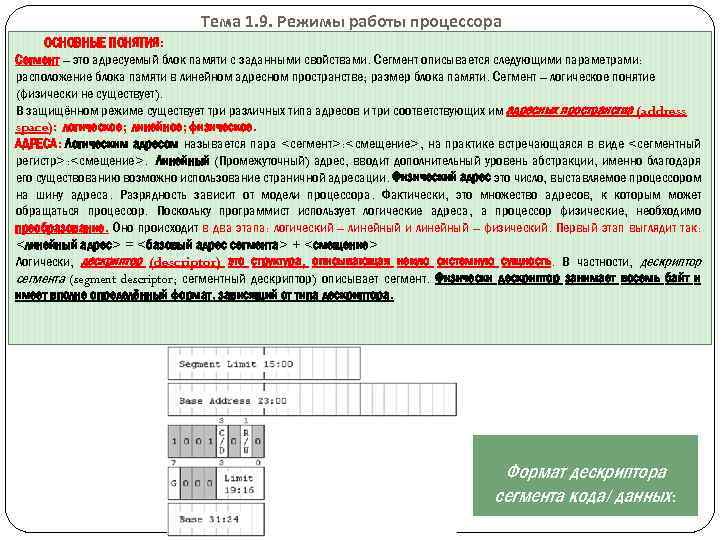

Тема 1. 9. Режимы работы процессора ОСНОВНЫЕ ПОНЯТИЯ: Сегмент – это адресуемый блок памяти с заданными свойствами. Сегмент описывается следующими параметрами: расположение блока памяти в линейном адресном пространстве; размер блока памяти. Сегмент – логическое понятие (физически не существует). В защищённом режиме существует три различных типа адресов и три соответствующих им адресных пространства (address space): логическое; линейное; физическое. АДРЕСА: Логическим адресом называется пара <сегмент>: <смещение>, на практике встречающаяся в виде <сегментный регистр>: <смещение>. Линейный (Промежуточный) адрес, вводит дополнительный уровень абстракции, именно благодаря его существованию возможно использование страничной адресации. Физический адрес это число, выставляемое процессором на шину адреса. Разрядность зависит от модели процессора. Фактически, это множество адресов, к которым может обращаться процессор. Поскольку программист использует логические адреса, а процессор физические, необходимо преобразование. Оно происходит в два этапа: логический – линейный и линейный – физический. Первый этап выглядит так: <линейный адрес> = <базовый адрес сегмента> + <смещение> Логически, дескриптор (descriptor) это структура, описывающая некую системную сущность. В частности, дескриптор сегмента (segment descriptor; сегментный дескриптор) описывает сегмент. Физически дескриптор занимает восемь байт и имеет вполне определённый формат, зависящий от типа дескриптора. Формат дескриптора сегмента кода/данных:

Тема 1. 9. Режимы работы процессора ОСНОВНЫЕ ПОНЯТИЯ: Сегмент – это адресуемый блок памяти с заданными свойствами. Сегмент описывается следующими параметрами: расположение блока памяти в линейном адресном пространстве; размер блока памяти. Сегмент – логическое понятие (физически не существует). В защищённом режиме существует три различных типа адресов и три соответствующих им адресных пространства (address space): логическое; линейное; физическое. АДРЕСА: Логическим адресом называется пара <сегмент>: <смещение>, на практике встречающаяся в виде <сегментный регистр>: <смещение>. Линейный (Промежуточный) адрес, вводит дополнительный уровень абстракции, именно благодаря его существованию возможно использование страничной адресации. Физический адрес это число, выставляемое процессором на шину адреса. Разрядность зависит от модели процессора. Фактически, это множество адресов, к которым может обращаться процессор. Поскольку программист использует логические адреса, а процессор физические, необходимо преобразование. Оно происходит в два этапа: логический – линейный и линейный – физический. Первый этап выглядит так: <линейный адрес> = <базовый адрес сегмента> + <смещение> Логически, дескриптор (descriptor) это структура, описывающая некую системную сущность. В частности, дескриптор сегмента (segment descriptor; сегментный дескриптор) описывает сегмент. Физически дескриптор занимает восемь байт и имеет вполне определённый формат, зависящий от типа дескриптора. Формат дескриптора сегмента кода/данных:

Тема 1. 9. Режимы работы процессора Работа механизма формирования линейного адреса в защищенном режиме основана на двух специальных таблицах, размещаемых в памяти. Это глобальная таблица дескрипторов (GDT) и локальная таблица дескрипторов (LDT) (есть еще таблица дескрипторов прерываний, но она используется только при генерации прерываний и особых ситуаций). Эти таблицы создаются и заполняются до переключения в защищенный режим, они содержат описания используемых программой сегментов памяти (базовый адрес, размер, тип, привилегии доступа и т. п. ). Селектор сегмента, являющийся частью сформированного логического адреса в защищенном режиме содержит не базу физического адреса сегмента, а указатель на описание сегмента (дескриптор сегмента) в какой-либо таблице дескрипторов (LDT или GDT). Из выбранного таким образом дескриптора и смещения (вторая часть логического адреса) процессор автоматически вычисляет требуемый линейный адрес (рисунок).

Тема 1. 9. Режимы работы процессора Работа механизма формирования линейного адреса в защищенном режиме основана на двух специальных таблицах, размещаемых в памяти. Это глобальная таблица дескрипторов (GDT) и локальная таблица дескрипторов (LDT) (есть еще таблица дескрипторов прерываний, но она используется только при генерации прерываний и особых ситуаций). Эти таблицы создаются и заполняются до переключения в защищенный режим, они содержат описания используемых программой сегментов памяти (базовый адрес, размер, тип, привилегии доступа и т. п. ). Селектор сегмента, являющийся частью сформированного логического адреса в защищенном режиме содержит не базу физического адреса сегмента, а указатель на описание сегмента (дескриптор сегмента) в какой-либо таблице дескрипторов (LDT или GDT). Из выбранного таким образом дескриптора и смещения (вторая часть логического адреса) процессор автоматически вычисляет требуемый линейный адрес (рисунок).

Тема 1. 9. Режимы работы процессора Для того, чтобы микропроцессор мог выполнить ту или иную операцию, необходимы инструкции, или команды. Команды хранятся в основной памяти. Каждая команда – это группа битов, соответствующая определённой операции. Обычно команда делится на поля, каждое из которых определяет какой-либо атрибут команды, а поле операции в ней определяет саму выполняемую операцию (сложение, пересылка, дополнение и т. д. ). Код каждой операции – это уникальная последовательность битов длиной от 1 до 2 байт. Поле регистра определяет номер регистра, который содержит данные, принимающие участие в операции, а адресное поле служит для определения участка памяти, содержащего данные, используемые при вычислениях (длина от 0 до 8 байт). Команды размещают в ОП в определѐнной последовательности – по порядку выполнения. Очередная выполняемая команда определяется с помощью содержимого специального регистра – счѐтчикакоманд. Последний содержит адрес области памяти, в которой расположена следующая выполняемая команда. Микропроцессор использует содержимое счѐтчикакоманд для выборки из памяти этой команды. Во время выполнения команда хранится в регистре команд. Различные команды для размещения в ОП используют различное количество битов, так как в некоторых командах есть адресное поле, а в некоторых нет. А потому ЭВМ использует команды переменной длины: 1, 2, …, 11 байт. В зависимости от этой длины, в счѐтчикдобавляется число 1, 2, …, 11 (по количеству байт). Работа процессора сводится к выполнению повторяющихся рабочих циклов, каждый из которых соответствует определѐнной выполняемой команде. Есть операции над целыми числами: команды пересылки, арифметических, логических, битовых операций, сдвигов и операций со строками символов. Операции над числами с плавающей точкой выполняются тоже в процессоре: пересылки данных, арифметические, сравнения и команды управления FPU. Кроме этих операций, есть ещѐ команды управления программой, защиты памяти и поддержки языков высокого уровня. Выполнение любой команды начинается с анализа запроса прерывания. Если прерывания нет, то выбирается команда, а иначе обрабатывается прерывание. После выборки команды сразу формируется адрес следующей команды, и анализируется код операции текущей команды. В зависимости от кода, формируются адреса операндов команды или выполняются действия по кодам операций управления. Затем выполняются сами операции, формируются признаки результата и запоминается результат. После этого управление передаётся на выполнение следующей команды.

Тема 1. 9. Режимы работы процессора Для того, чтобы микропроцессор мог выполнить ту или иную операцию, необходимы инструкции, или команды. Команды хранятся в основной памяти. Каждая команда – это группа битов, соответствующая определённой операции. Обычно команда делится на поля, каждое из которых определяет какой-либо атрибут команды, а поле операции в ней определяет саму выполняемую операцию (сложение, пересылка, дополнение и т. д. ). Код каждой операции – это уникальная последовательность битов длиной от 1 до 2 байт. Поле регистра определяет номер регистра, который содержит данные, принимающие участие в операции, а адресное поле служит для определения участка памяти, содержащего данные, используемые при вычислениях (длина от 0 до 8 байт). Команды размещают в ОП в определѐнной последовательности – по порядку выполнения. Очередная выполняемая команда определяется с помощью содержимого специального регистра – счѐтчикакоманд. Последний содержит адрес области памяти, в которой расположена следующая выполняемая команда. Микропроцессор использует содержимое счѐтчикакоманд для выборки из памяти этой команды. Во время выполнения команда хранится в регистре команд. Различные команды для размещения в ОП используют различное количество битов, так как в некоторых командах есть адресное поле, а в некоторых нет. А потому ЭВМ использует команды переменной длины: 1, 2, …, 11 байт. В зависимости от этой длины, в счѐтчикдобавляется число 1, 2, …, 11 (по количеству байт). Работа процессора сводится к выполнению повторяющихся рабочих циклов, каждый из которых соответствует определѐнной выполняемой команде. Есть операции над целыми числами: команды пересылки, арифметических, логических, битовых операций, сдвигов и операций со строками символов. Операции над числами с плавающей точкой выполняются тоже в процессоре: пересылки данных, арифметические, сравнения и команды управления FPU. Кроме этих операций, есть ещѐ команды управления программой, защиты памяти и поддержки языков высокого уровня. Выполнение любой команды начинается с анализа запроса прерывания. Если прерывания нет, то выбирается команда, а иначе обрабатывается прерывание. После выборки команды сразу формируется адрес следующей команды, и анализируется код операции текущей команды. В зависимости от кода, формируются адреса операндов команды или выполняются действия по кодам операций управления. Затем выполняются сами операции, формируются признаки результата и запоминается результат. После этого управление передаётся на выполнение следующей команды.

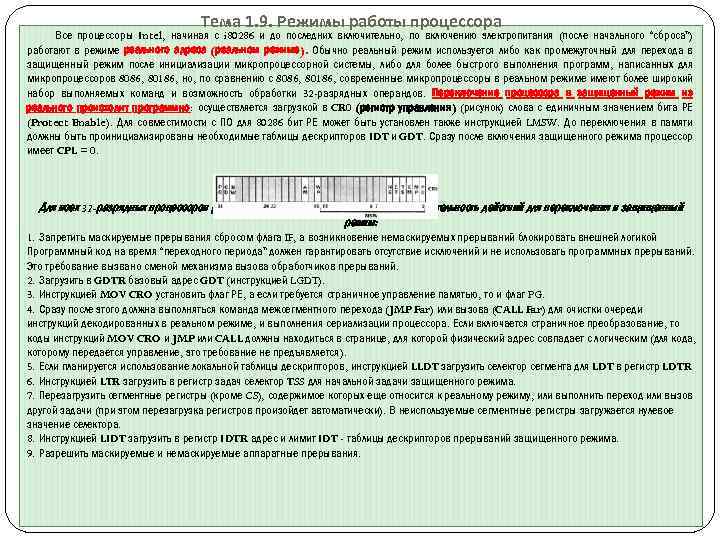

Тема 1. 9. Режимы работы процессора Все процессоры Intel, начиная с i 80286 и до последних включительно, по включению электропитания (после начального “сброса”) работают в режиме реального адреса (реальном режиме). Обычно реальный режим используется либо как промежуточный для перехода в защищенный режим после инициализации микропроцессорной системы, либо для более быстрого выполнения программ, написанных для микропроцессоров 8086, 80186, но, по сравнению с 8086, 80186, современные микропроцессоры в реальном режиме имеют более широкий набор выполняемых команд и возможность обработки 32 -разрядных операндов. Переключение процессора в защищенный режим из реального происходит программно: осуществляется загрузкой в CR 0 (регистр управления) (рисунок) слова с единичным значением бита РЕ (Protect Enable). Для совместимости с ПО для 80286 бит РЕ может быть установлен также инструкцией LMSW. До переключения в памяти должны быть проинициализированы необходимые таблицы дескрипторов IDT и GDT. Сразу после включения защищенного режима процессор имеет CPL = 0. Для всех 32 -разрядных процессоров рекомендуется выполнять следующую последовательность действий для переключения в защищенный режим: 1. Запретить маскируемые прерывания сбросом флага IF, а возникновение немаскируемых прерываний блокировать внешней логикой Программный код на время “переходного периода” должен гарантировать отсутствие исключений и не использовать программных прерываний. Это требование вызвано сменой механизма вызова обработчиков прерываний. 2. Загрузить в GDTR базовый адрес GDT (инструкцией LGDT). 3. Инструкцией MOV CRO установить флаг РЕ, а если требуется страничное управление памятью, то и флаг PG. 4. Сразу после этого должна выполняться команда межсегментного перехода (JMP Far) или вызова (CALL Far) для очистки очереди инструкций декодированных в реальном режиме, и выполнения сериализации процессора. Если включается страничное преобразование, то коды инструкций MOV CRO и JMP или CALL должны находиться в странице, для которой физический адрес совпадает с логическим (для кода, которому передается управление, это требование не предъявляется). 5. Если планируется использование локальной таблицы дескрипторов, инструкцией LLDT загрузить селектор сегмента для LDT в регистр LDTR 6. Инструкцией LTR загрузить в регистр задач селектор TSS для начальной задачи защищенного режима. 7. Перезагрузить сегментные регистры (кроме CS), содержимое которых еще относится к реальному режиму, или выполнить переход или вызов другой задачи (при этом перезагрузка регистров произойдет автоматически). В неиспользуемые сегментные регистры загружается нулевое значение селектора. 8. Инструкцией LIDT загрузить в регистр IDTR адрес и лимит IDT - таблицы дескрипторов прерываний защищенного режима. 9. Разрешить маскируемые и немаскируемые аппаратные прерывания.

Тема 1. 9. Режимы работы процессора Все процессоры Intel, начиная с i 80286 и до последних включительно, по включению электропитания (после начального “сброса”) работают в режиме реального адреса (реальном режиме). Обычно реальный режим используется либо как промежуточный для перехода в защищенный режим после инициализации микропроцессорной системы, либо для более быстрого выполнения программ, написанных для микропроцессоров 8086, 80186, но, по сравнению с 8086, 80186, современные микропроцессоры в реальном режиме имеют более широкий набор выполняемых команд и возможность обработки 32 -разрядных операндов. Переключение процессора в защищенный режим из реального происходит программно: осуществляется загрузкой в CR 0 (регистр управления) (рисунок) слова с единичным значением бита РЕ (Protect Enable). Для совместимости с ПО для 80286 бит РЕ может быть установлен также инструкцией LMSW. До переключения в памяти должны быть проинициализированы необходимые таблицы дескрипторов IDT и GDT. Сразу после включения защищенного режима процессор имеет CPL = 0. Для всех 32 -разрядных процессоров рекомендуется выполнять следующую последовательность действий для переключения в защищенный режим: 1. Запретить маскируемые прерывания сбросом флага IF, а возникновение немаскируемых прерываний блокировать внешней логикой Программный код на время “переходного периода” должен гарантировать отсутствие исключений и не использовать программных прерываний. Это требование вызвано сменой механизма вызова обработчиков прерываний. 2. Загрузить в GDTR базовый адрес GDT (инструкцией LGDT). 3. Инструкцией MOV CRO установить флаг РЕ, а если требуется страничное управление памятью, то и флаг PG. 4. Сразу после этого должна выполняться команда межсегментного перехода (JMP Far) или вызова (CALL Far) для очистки очереди инструкций декодированных в реальном режиме, и выполнения сериализации процессора. Если включается страничное преобразование, то коды инструкций MOV CRO и JMP или CALL должны находиться в странице, для которой физический адрес совпадает с логическим (для кода, которому передается управление, это требование не предъявляется). 5. Если планируется использование локальной таблицы дескрипторов, инструкцией LLDT загрузить селектор сегмента для LDT в регистр LDTR 6. Инструкцией LTR загрузить в регистр задач селектор TSS для начальной задачи защищенного режима. 7. Перезагрузить сегментные регистры (кроме CS), содержимое которых еще относится к реальному режиму, или выполнить переход или вызов другой задачи (при этом перезагрузка регистров произойдет автоматически). В неиспользуемые сегментные регистры загружается нулевое значение селектора. 8. Инструкцией LIDT загрузить в регистр IDTR адрес и лимит IDT - таблицы дескрипторов прерываний защищенного режима. 9. Разрешить маскируемые и немаскируемые аппаратные прерывания.

Тема 1. 9. Режимы работы процессора Контрольные вопросы: 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. Структурно любая ЭВМ состоит из…? Память ЭВМ состоит из …? Что содержат все команды в качестве одной части? Что может содержать команда кроме кода операции? Какие команды используются в Микро. ЭВМ? Что в одноадресных командах выбирается из специального регистра? Процессор – это…? Что делает процессор? Что выполняет Арифметико-логическое устройство? Что делает Устройство Управления? Для чего служат регистры процессора? Чем определяется разнообразие решаемых на ЭВМ задач? Что такое микропроцессор? Какие функции выполняет микропроцессор (подробнее, чем на вопрос 8)? Назовите основные параметры микропроцессора и дайте определение каждому. Что содержится на одном кристалле микропроцессора (на примере 32 -разрядного МП)? Из чего состоит диспетчер памяти и что он осуществляет и обеспечивает? Что позволяет реализовать реальный режим работы МП? Что характеризует защищенный режим МП? Чем является сегментация и что она обеспечивает? Какой является защита на уровне сегментов и в чем основа ее функционирования? Что представляет собой сегментированная память? В каком режиме возможно разбиение на страницы? На чем основана работа механизма формирования линейного адреса в защищенном режиме? Сегмент – это…?

Тема 1. 9. Режимы работы процессора Контрольные вопросы: 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. Структурно любая ЭВМ состоит из…? Память ЭВМ состоит из …? Что содержат все команды в качестве одной части? Что может содержать команда кроме кода операции? Какие команды используются в Микро. ЭВМ? Что в одноадресных командах выбирается из специального регистра? Процессор – это…? Что делает процессор? Что выполняет Арифметико-логическое устройство? Что делает Устройство Управления? Для чего служат регистры процессора? Чем определяется разнообразие решаемых на ЭВМ задач? Что такое микропроцессор? Какие функции выполняет микропроцессор (подробнее, чем на вопрос 8)? Назовите основные параметры микропроцессора и дайте определение каждому. Что содержится на одном кристалле микропроцессора (на примере 32 -разрядного МП)? Из чего состоит диспетчер памяти и что он осуществляет и обеспечивает? Что позволяет реализовать реальный режим работы МП? Что характеризует защищенный режим МП? Чем является сегментация и что она обеспечивает? Какой является защита на уровне сегментов и в чем основа ее функционирования? Что представляет собой сегментированная память? В каком режиме возможно разбиение на страницы? На чем основана работа механизма формирования линейного адреса в защищенном режиме? Сегмент – это…?

Тема 1. 9. Режимы работы процессора Контрольные вопросы: 26. 27. 28. 29. 30. 31. 32. 33. Какими параметрами описывается сегмент? Что называется логическим адресом? Что позволяет использовать линейный адрес? Что такое физический адрес, от чего он зависит? Как происходит преобразование адресов? Что такое дескриптор? В каком режиме после включения ПК работают процессоры Intel? Как происходит переключение из реального режима в защищенный режим?

Тема 1. 9. Режимы работы процессора Контрольные вопросы: 26. 27. 28. 29. 30. 31. 32. 33. Какими параметрами описывается сегмент? Что называется логическим адресом? Что позволяет использовать линейный адрес? Что такое физический адрес, от чего он зависит? Как происходит преобразование адресов? Что такое дескриптор? В каком режиме после включения ПК работают процессоры Intel? Как происходит переключение из реального режима в защищенный режим?