организация микросхем памяти2012.ppt

- Количество слайдов: 31

Аппаратные средства вычислительной техники Лекция Организация памяти в ЭВМ Доцент кафедры ИТ Крюкова Л. В.

Аппаратные средства вычислительной техники Лекция Организация памяти в ЭВМ Доцент кафедры ИТ Крюкова Л. В.

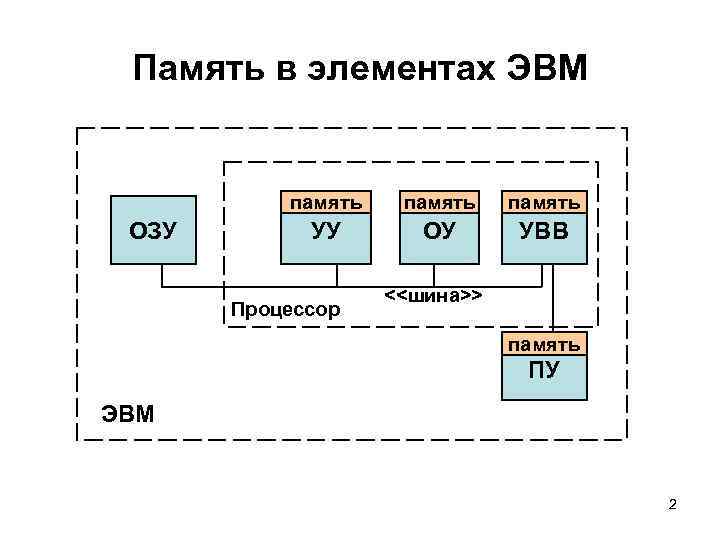

Память в элементах ЭВМ память ОЗУ память УУ ОУ УВВ Процессор <<шина>> память ПУ ЭВМ 2

Память в элементах ЭВМ память ОЗУ память УУ ОУ УВВ Процессор <<шина>> память ПУ ЭВМ 2

Памятью ЭВМ называется совокупность устройств, служащих для запоминания, хранения и выдачи информации. Отдельные устройства, входящие в эту совокупность, называются запоминающими устройствами (ЗУ) того или иного типа. Запоминающие устройства играют важную роль в общей структуре ЭВМ. По некоторым оценкам производительность компьютера на разных классах задач на 40 50% определяется характеристиками ЗУ различных типов, входящих в его состав. 3

Памятью ЭВМ называется совокупность устройств, служащих для запоминания, хранения и выдачи информации. Отдельные устройства, входящие в эту совокупность, называются запоминающими устройствами (ЗУ) того или иного типа. Запоминающие устройства играют важную роль в общей структуре ЭВМ. По некоторым оценкам производительность компьютера на разных классах задач на 40 50% определяется характеристиками ЗУ различных типов, входящих в его состав. 3

Основные параметры, характеризующие ЗУ емкость и быстродействие. Емкость памяти это максимальное количество данных, которое в ней может храниться. Емкость запоминающего устройства измеряется количеством адресуемых элементов (ячеек) ЗУ и длиной ячейки в битах. В настоящее время практически все запоминающие устройства в качестве минимально адресуемого элемента используют 1 байт. Емкость памяти обычно определяется в байтах, килобайтах (1 Кбайт=210 байт), мегабайтах (1 Мбайт = 220 байт), гигабайтах (1 Гбайт = 230 байт) и т. д. За одно обращение к запоминающему устройству производится считывание или запись некоторой единицы данных, называемой словом, различной для устройств разного типа. Это определяет разную организацию памяти. Например, память объемом 1 мегабайт может быть организована как 1 М слов по 1 байту, или 512 К слов по 2 байта каждое, или 256 К слов по 4 байта и т. д. В то же время, в каждой ЭВМ используется свое понятие машинного слова, которое применяется при определении архитектуры компьютера, в частности при его программировании, и не зависит от размерности слова памяти, используемой для построения данной ЭВМ. Например, компьютеры с архитектурой IBM PC имеют машинное слово длиной 2 байта. Быстродействие памяти определяется продолжительностью операции обращения, то есть временем, затрачиваемым на поиск нужной информации в памяти и на ее считывание, или временем на поиск места в памяти, предназначаемого для хранения данной информации, и на ее запись: tобр = max(tобр сч, tобр зп), где tобр сч быстродействие ЗУ при считывании информации; tобр зп быстродействие ЗУ при записи. 4

Основные параметры, характеризующие ЗУ емкость и быстродействие. Емкость памяти это максимальное количество данных, которое в ней может храниться. Емкость запоминающего устройства измеряется количеством адресуемых элементов (ячеек) ЗУ и длиной ячейки в битах. В настоящее время практически все запоминающие устройства в качестве минимально адресуемого элемента используют 1 байт. Емкость памяти обычно определяется в байтах, килобайтах (1 Кбайт=210 байт), мегабайтах (1 Мбайт = 220 байт), гигабайтах (1 Гбайт = 230 байт) и т. д. За одно обращение к запоминающему устройству производится считывание или запись некоторой единицы данных, называемой словом, различной для устройств разного типа. Это определяет разную организацию памяти. Например, память объемом 1 мегабайт может быть организована как 1 М слов по 1 байту, или 512 К слов по 2 байта каждое, или 256 К слов по 4 байта и т. д. В то же время, в каждой ЭВМ используется свое понятие машинного слова, которое применяется при определении архитектуры компьютера, в частности при его программировании, и не зависит от размерности слова памяти, используемой для построения данной ЭВМ. Например, компьютеры с архитектурой IBM PC имеют машинное слово длиной 2 байта. Быстродействие памяти определяется продолжительностью операции обращения, то есть временем, затрачиваемым на поиск нужной информации в памяти и на ее считывание, или временем на поиск места в памяти, предназначаемого для хранения данной информации, и на ее запись: tобр = max(tобр сч, tобр зп), где tобр сч быстродействие ЗУ при считывании информации; tобр зп быстродействие ЗУ при записи. 4

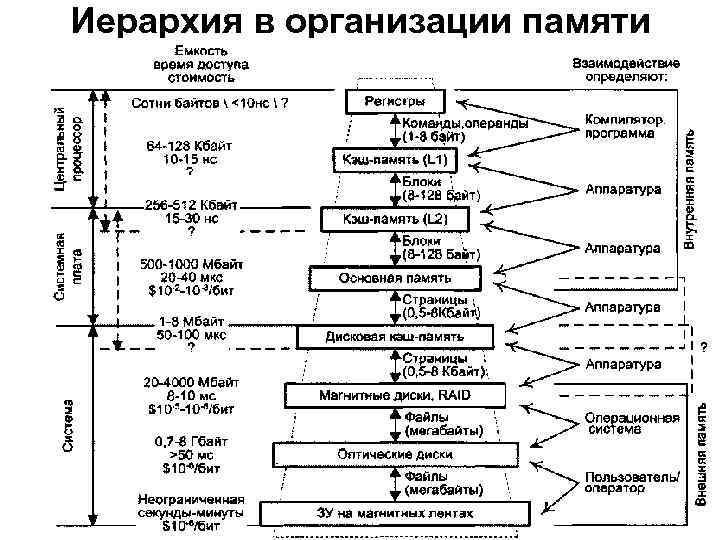

Идеальное запоминающее устройство должно обладать: Ø бесконечно большой емкостью и Ø иметь бесконечно малое время обращения На практике эти параметры находятся в противоречии другу: в рамках одного типа ЗУ улучшение одного из них ведет к ухудшению значения другого. К тому же следует иметь в виду и экономическую целесообразность построения запоминающего устройства с теми или иными характеристиками при данном уровне развития технологии. В настоящее время запоминающие устройства компьютера, как это и предполагал Нейман, строятся по иерархическому принципу. 5

Идеальное запоминающее устройство должно обладать: Ø бесконечно большой емкостью и Ø иметь бесконечно малое время обращения На практике эти параметры находятся в противоречии другу: в рамках одного типа ЗУ улучшение одного из них ведет к ухудшению значения другого. К тому же следует иметь в виду и экономическую целесообразность построения запоминающего устройства с теми или иными характеристиками при данном уровне развития технологии. В настоящее время запоминающие устройства компьютера, как это и предполагал Нейман, строятся по иерархическому принципу. 5

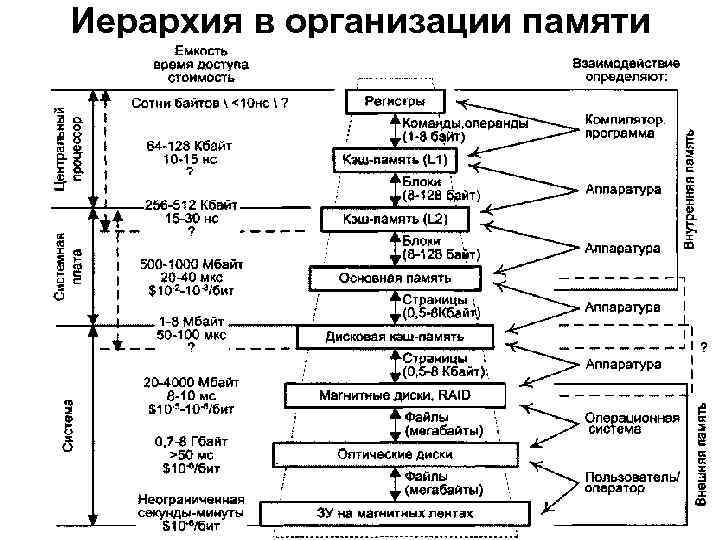

Иерархия в организации памяти 6

Иерархия в организации памяти 6

Классификация памяти по признакам 7

Классификация памяти по признакам 7

По типу обращения ЗУ делятся на устройства, допускающие как чтение, так и запись информации, и постоянные запоминающие устройства (ПЗУ), предназначенные только для чтения записанных в них данных (ROM read only memory). ЗУ первого типа используются в процессе работы процессора для хранения выполняемых программ, исходных данных, промежуточных и окончательных результатов. В ПЗУ, как правило, хранятся системные программы, необходимые для запуска компьютера в работу, а также константы. В некоторых ЭВМ, предназначенных, например, для работы в системах управления по одним и тем же неизменяемым алгоритмам, все программное обеспечение может храниться в ПЗУ. В ЗУ с произвольным доступом (RAM - random access memory) время доступа не зависит от места расположения участка памяти (например, ОЗУ). В ЗУ с прямым (циклическим) доступом благодаря непрерывному вращению носителя информации (например, магнитный диск МД) возможность обращения к некоторому участку носителя циклически повторяется. Время доступа здесь зависит от взаимного расположения этого участка и головок чтения/записи и во многом определяется скоростью вращения носителя. В ЗУ с последовательным доступом производится последовательный просмотр участков носителя информации, пока нужный участок не займет некоторое нужное положение напротив головок чтения/записи (например, магнитные ленты МЛ). 8

По типу обращения ЗУ делятся на устройства, допускающие как чтение, так и запись информации, и постоянные запоминающие устройства (ПЗУ), предназначенные только для чтения записанных в них данных (ROM read only memory). ЗУ первого типа используются в процессе работы процессора для хранения выполняемых программ, исходных данных, промежуточных и окончательных результатов. В ПЗУ, как правило, хранятся системные программы, необходимые для запуска компьютера в работу, а также константы. В некоторых ЭВМ, предназначенных, например, для работы в системах управления по одним и тем же неизменяемым алгоритмам, все программное обеспечение может храниться в ПЗУ. В ЗУ с произвольным доступом (RAM - random access memory) время доступа не зависит от места расположения участка памяти (например, ОЗУ). В ЗУ с прямым (циклическим) доступом благодаря непрерывному вращению носителя информации (например, магнитный диск МД) возможность обращения к некоторому участку носителя циклически повторяется. Время доступа здесь зависит от взаимного расположения этого участка и головок чтения/записи и во многом определяется скоростью вращения носителя. В ЗУ с последовательным доступом производится последовательный просмотр участков носителя информации, пока нужный участок не займет некоторое нужное положение напротив головок чтения/записи (например, магнитные ленты МЛ). 8

Физико-технические процессы электронные переключательные процессы магнитные, электромагнитные (фиритные ячейки памяти) оптические 9

Физико-технические процессы электронные переключательные процессы магнитные, электромагнитные (фиритные ячейки памяти) оптические 9

Организация доступа к элементам памяти параллельный (прямой) доступ время доступа = 2*T последовательный доступ время доступа = (L/2)*T L – длина последовательной памяти 10

Организация доступа к элементам памяти параллельный (прямой) доступ время доступа = 2*T последовательный доступ время доступа = (L/2)*T L – длина последовательной памяти 10

Классификация памяти по типу записи постоянные запоминающие устройства (ПЗУ, ROM) память чтения записи (RAM) 11

Классификация памяти по типу записи постоянные запоминающие устройства (ПЗУ, ROM) память чтения записи (RAM) 11

Классификация памяти по продолжительности хранения статическая память (SRAM) динамическая память (DRAM) (хранение осуществляется на паразитных плоскостях pn переходов) 12

Классификация памяти по продолжительности хранения статическая память (SRAM) динамическая память (DRAM) (хранение осуществляется на паразитных плоскостях pn переходов) 12

Чем характеризуется любая память? глубиной и шириной «выборки» продолжительностью цикла обращения (быстродействием) надежностью 13

Чем характеризуется любая память? глубиной и шириной «выборки» продолжительностью цикла обращения (быстродействием) надежностью 13

Единица информации • Байт (8 бит) слово 16 бит двойное слово 32 бита квадрослово 64 бита • Булева переменная Доступа к отдельным битам нет « 0» 0000 « 1» 1111 14

Единица информации • Байт (8 бит) слово 16 бит двойное слово 32 бита квадрослово 64 бита • Булева переменная Доступа к отдельным битам нет « 0» 0000 « 1» 1111 14

Иерархия в организации памяти 15

Иерархия в организации памяти 15

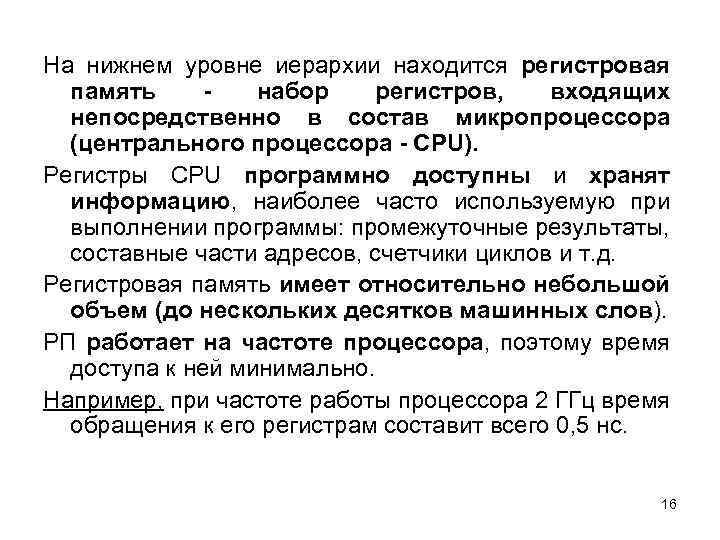

На нижнем уровне иерархии находится регистровая память набор регистров, входящих непосредственно в состав микропроцессора (центрального процессора - CPU). Регистры CPU программно доступны и хранят информацию, наиболее часто используемую при выполнении программы: промежуточные результаты, составные части адресов, счетчики циклов и т. д. Регистровая память имеет относительно небольшой объем (до нескольких десятков машинных слов). РП работает на частоте процессора, поэтому время доступа к ней минимально. Например, при частоте работы процессора 2 ГГц время обращения к его регистрам составит всего 0, 5 нс. 16

На нижнем уровне иерархии находится регистровая память набор регистров, входящих непосредственно в состав микропроцессора (центрального процессора - CPU). Регистры CPU программно доступны и хранят информацию, наиболее часто используемую при выполнении программы: промежуточные результаты, составные части адресов, счетчики циклов и т. д. Регистровая память имеет относительно небольшой объем (до нескольких десятков машинных слов). РП работает на частоте процессора, поэтому время доступа к ней минимально. Например, при частоте работы процессора 2 ГГц время обращения к его регистрам составит всего 0, 5 нс. 16

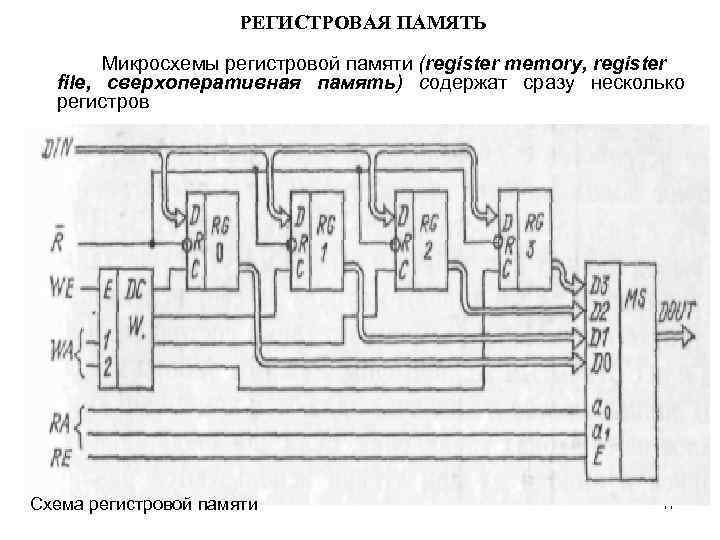

РЕГИСТРОВАЯ ПАМЯТЬ Микросхемы регистровой памяти (register memory, register file, сверхоперативная память) содержат сразу несколько регистров Схема регистровой памяти 17

РЕГИСТРОВАЯ ПАМЯТЬ Микросхемы регистровой памяти (register memory, register file, сверхоперативная память) содержат сразу несколько регистров Схема регистровой памяти 17

Входы Dt четырех или восьми регистров, как правило 4 разрядных, подключены к общей входной шине данных DIN (data in). Вход загрузки требуемого регистра выбирается дешифратором записи DCW на основании поступающего на вход DCW адреса записи WA (wri e address), т. е. кода номера загружаемого регистра. t Запись данных, присутствующих на шине DIN, происходит в момент поступления сигнала разрешения записи WE (wri e enable). t Выходы регистров мультиплексором MS подключаются к выходной шине DOUT (data out). Номер регистра, с которого происходит чтение, определяет код адреса чтения RA (read address). Выдачу данных в шину DOUT разрешает сигнал RE (read enable). Поскольку дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими ав тономные адресные входы WA и RA, регистровая память может одновременно записывать число в один из регистров и читать число из другого. Описанная структура использована в кристалле микросхемы К. 155 РШ. Аналогичные, но более развитые структуры имеют регистровые памяти ИР 11 и ИР 12 серий К 561 и 564. 18

Входы Dt четырех или восьми регистров, как правило 4 разрядных, подключены к общей входной шине данных DIN (data in). Вход загрузки требуемого регистра выбирается дешифратором записи DCW на основании поступающего на вход DCW адреса записи WA (wri e address), т. е. кода номера загружаемого регистра. t Запись данных, присутствующих на шине DIN, происходит в момент поступления сигнала разрешения записи WE (wri e enable). t Выходы регистров мультиплексором MS подключаются к выходной шине DOUT (data out). Номер регистра, с которого происходит чтение, определяет код адреса чтения RA (read address). Выдачу данных в шину DOUT разрешает сигнал RE (read enable). Поскольку дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими ав тономные адресные входы WA и RA, регистровая память может одновременно записывать число в один из регистров и читать число из другого. Описанная структура использована в кристалле микросхемы К. 155 РШ. Аналогичные, но более развитые структуры имеют регистровые памяти ИР 11 и ИР 12 серий К 561 и 564. 18

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН) и других специализированных блоков памяти небольшого объема, предназначенных для временного хранения исходных данных и промежуточных результатов в цифровом устройстве. 19

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН) и других специализированных блоков памяти небольшого объема, предназначенных для временного хранения исходных данных и промежуточных результатов в цифровом устройстве. 19

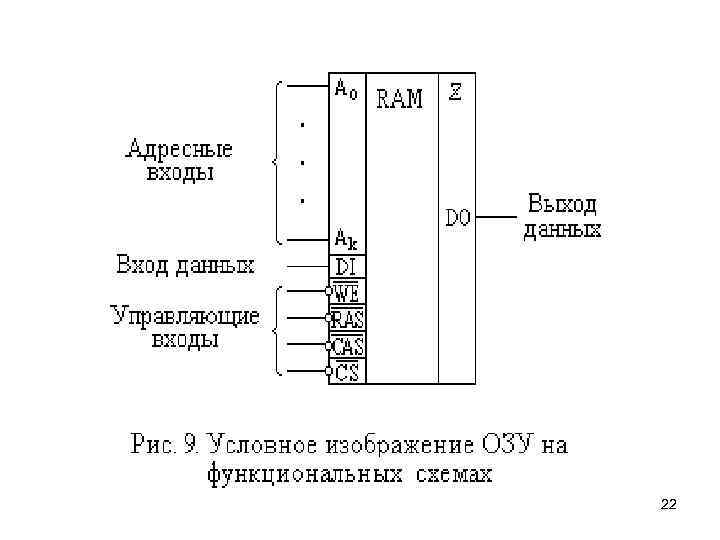

По мере увеличения числа регистров памяти разработчики отказываются от независимой адресации регистров при записи и чтении. Остается лишь один комплекс адресных входов и один дешифратор адреса, которые используются и при записи, и при считывании. Такую схему регистровой памятью уже не называют. По ЕСКД она обозначается RAM (random access memory, т. е. память с произвольным доступом). Используются также термины: запоминающее устройство с произвольной выборкой (ЗУПВ), оперативное запоминающее устройство (ОЗУ), оперативная память, а иногда — просто память. 20

По мере увеличения числа регистров памяти разработчики отказываются от независимой адресации регистров при записи и чтении. Остается лишь один комплекс адресных входов и один дешифратор адреса, которые используются и при записи, и при считывании. Такую схему регистровой памятью уже не называют. По ЕСКД она обозначается RAM (random access memory, т. е. память с произвольным доступом). Используются также термины: запоминающее устройство с произвольной выборкой (ЗУПВ), оперативное запоминающее устройство (ОЗУ), оперативная память, а иногда — просто память. 20

Оперативная память это устройство, которое служит для хранения информации (программ, исходных данных, промежуточных и конечных результатов обработки), непосредственно используемой в ходе выполнения программы в процессоре. В настоящее время объем ОП персональных компьютеров составляет несколько сотен мегабайт. Оперативная память работает на частоте системной шины и требует 6 -8 циклов синхронизации шины для обращения к ней. Например, при частоте работы системной шины 100 МГц (при этом период равен 10 нс) время обращения к оперативной памяти составит несколько десятков наносекунд. 21

Оперативная память это устройство, которое служит для хранения информации (программ, исходных данных, промежуточных и конечных результатов обработки), непосредственно используемой в ходе выполнения программы в процессоре. В настоящее время объем ОП персональных компьютеров составляет несколько сотен мегабайт. Оперативная память работает на частоте системной шины и требует 6 -8 циклов синхронизации шины для обращения к ней. Например, при частоте работы системной шины 100 МГц (при этом период равен 10 нс) время обращения к оперативной памяти составит несколько десятков наносекунд. 21

22

22

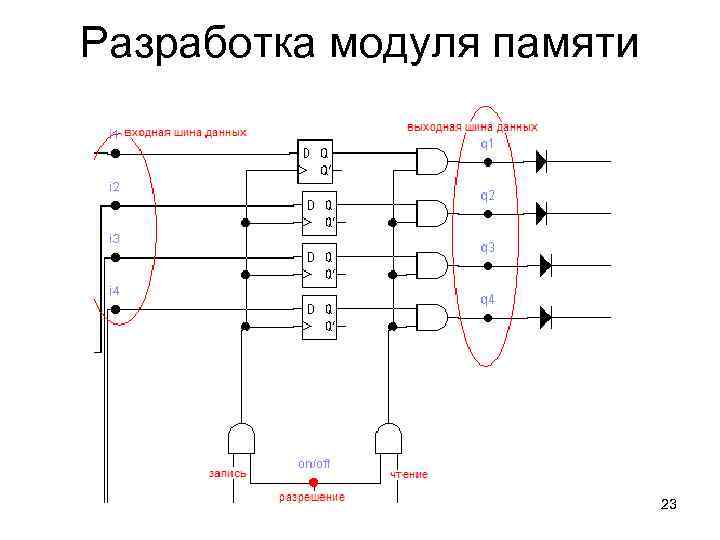

Разработка модуля памяти 23

Разработка модуля памяти 23

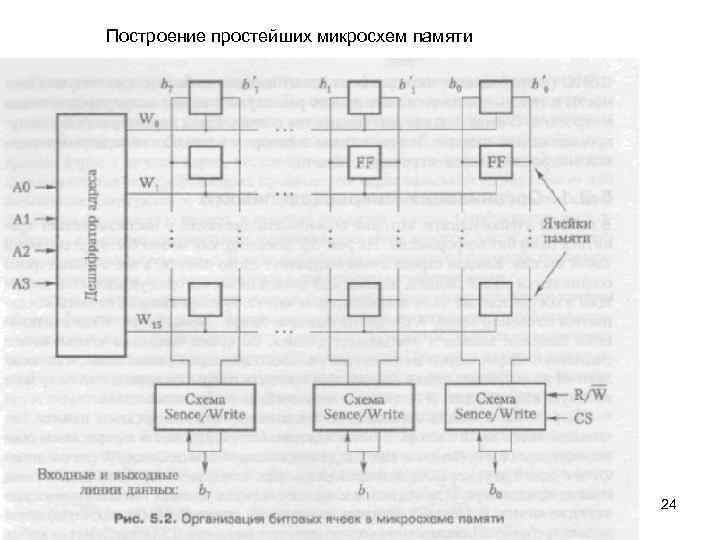

Построение простейших микросхем памяти 24

Построение простейших микросхем памяти 24

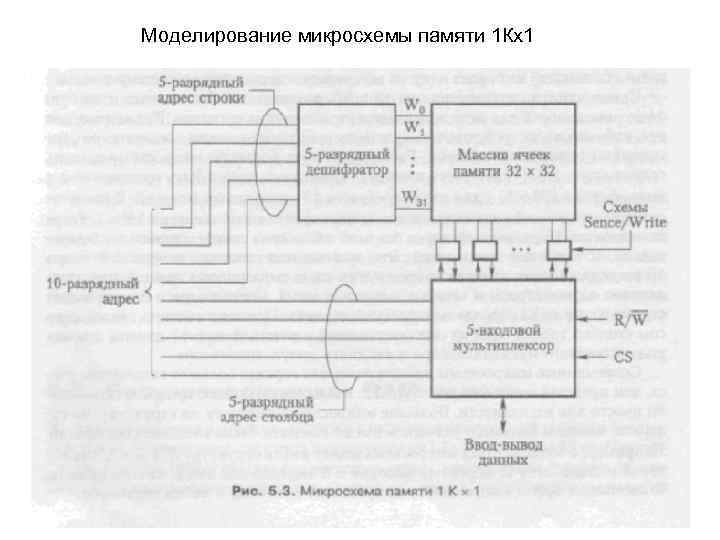

Моделирование микросхемы памяти 1 Кх1 25

Моделирование микросхемы памяти 1 Кх1 25

26

26

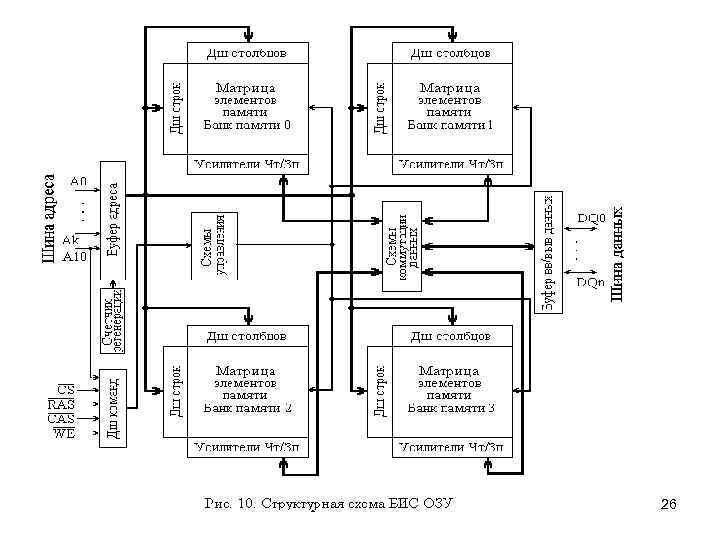

буфер адреса, фиксирующий адреса строки и столбца; счетчик регенерации, формирующий адрес строки, в которой должна выполняться очередная регенерация; дешифратор команд, определяющий, какое действие (команду) должна выполнить микросхема в соответствии с поданными управляющими сигналами (и сигналом. A 10); схемы управления, формирующие управляющие сигналы для остальных узлов микросхемы; схемы коммутации данных, передающие читаемые или записываемые данные из/в банки памяти; буфер ввода/вывода данных, обеспечивающий связь микросхемы памяти с шиной данных. Адресный сигнал A 10 выделен среди других адресных линий, так как он имеет специальное назначение: при подаче адреса столбца этот сигнал указывает на особенности выполнения последующего (пакетного) чтения или записи, задавая (при единичном значении) режим так называемого автоматического подзаряда банка памяти. 27

буфер адреса, фиксирующий адреса строки и столбца; счетчик регенерации, формирующий адрес строки, в которой должна выполняться очередная регенерация; дешифратор команд, определяющий, какое действие (команду) должна выполнить микросхема в соответствии с поданными управляющими сигналами (и сигналом. A 10); схемы управления, формирующие управляющие сигналы для остальных узлов микросхемы; схемы коммутации данных, передающие читаемые или записываемые данные из/в банки памяти; буфер ввода/вывода данных, обеспечивающий связь микросхемы памяти с шиной данных. Адресный сигнал A 10 выделен среди других адресных линий, так как он имеет специальное назначение: при подаче адреса столбца этот сигнал указывает на особенности выполнения последующего (пакетного) чтения или записи, задавая (при единичном значении) режим так называемого автоматического подзаряда банка памяти. 27

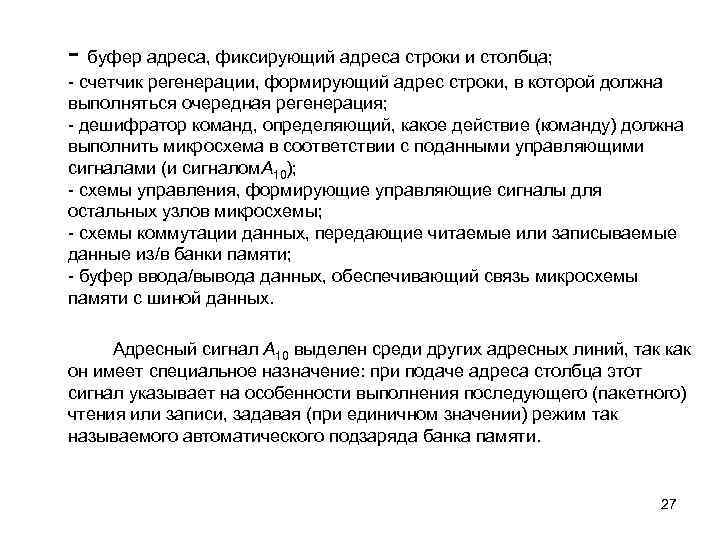

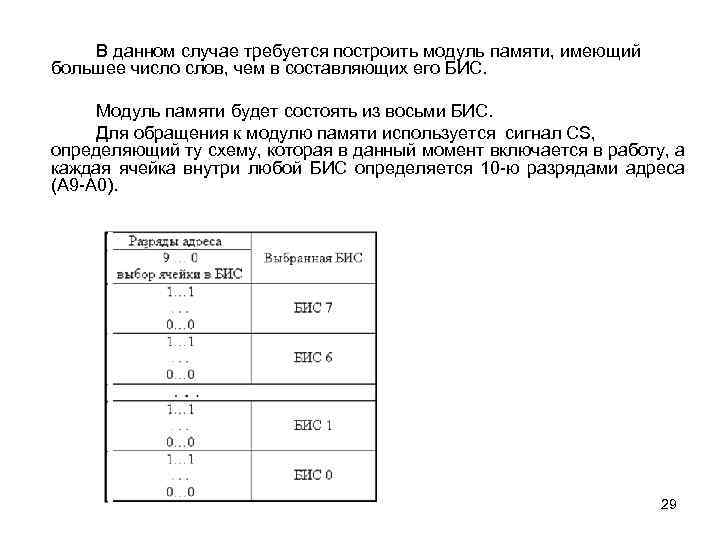

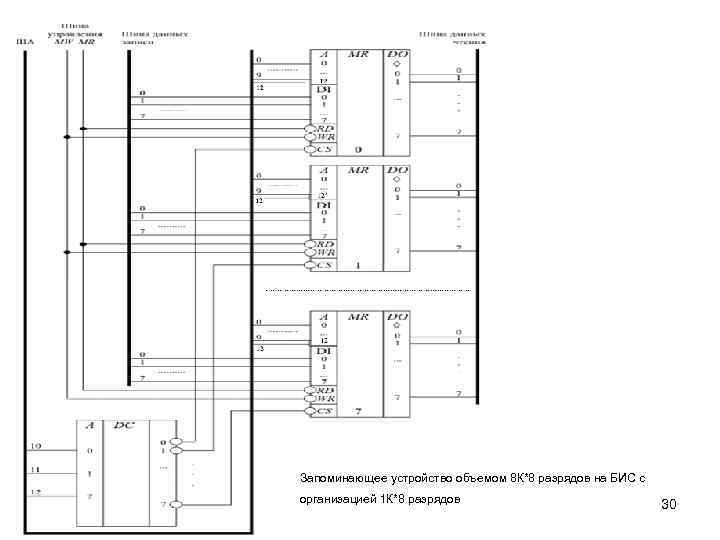

ПОСТРОЕНИЕ ЗУ С ЗАДАННОЙ ОРГАНИЗАЦИЕЙ Рассмотрим варианты построения блока памяти необходимой организации при наличии заданных БИС памяти. Задача 1. Построить ОЗУ с организацией 8 К*8 разрядов на БИС с организацией 1 К*8 разрядов. Условно графические обозначения запоминающих устройств различной организацией: а 1 К*8 разрядов; б 8 К*8 разрядов с 28

ПОСТРОЕНИЕ ЗУ С ЗАДАННОЙ ОРГАНИЗАЦИЕЙ Рассмотрим варианты построения блока памяти необходимой организации при наличии заданных БИС памяти. Задача 1. Построить ОЗУ с организацией 8 К*8 разрядов на БИС с организацией 1 К*8 разрядов. Условно графические обозначения запоминающих устройств различной организацией: а 1 К*8 разрядов; б 8 К*8 разрядов с 28

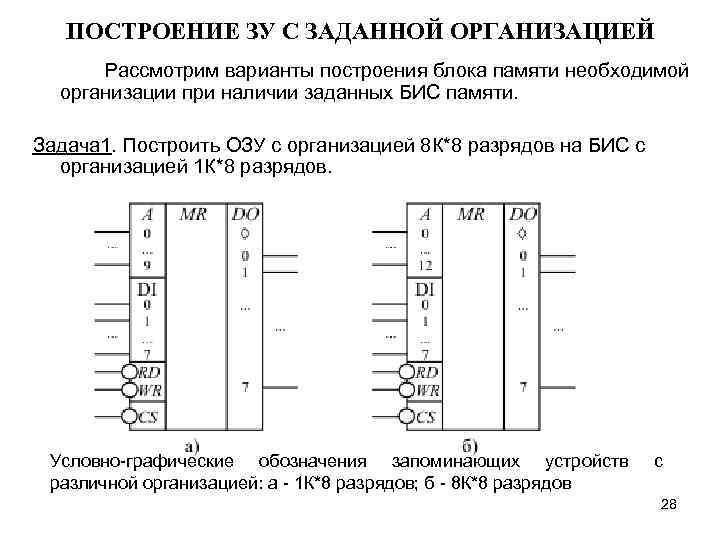

В данном случае требуется построить модуль памяти, имеющий большее число слов, чем в составляющих его БИС. Модуль памяти будет состоять из восьми БИС. Для обращения к модулю памяти используется сигнал CS, определяющий ту схему, которая в данный момент включается в работу, а каждая ячейка внутри любой БИС определяется 10 ю разрядами адреса (А 9 А 0). 29

В данном случае требуется построить модуль памяти, имеющий большее число слов, чем в составляющих его БИС. Модуль памяти будет состоять из восьми БИС. Для обращения к модулю памяти используется сигнал CS, определяющий ту схему, которая в данный момент включается в работу, а каждая ячейка внутри любой БИС определяется 10 ю разрядами адреса (А 9 А 0). 29

Запоминающее устройство объемом 8 К*8 разрядов на БИС с организацией 1 К*8 разрядов 30

Запоминающее устройство объемом 8 К*8 разрядов на БИС с организацией 1 К*8 разрядов 30

• В реальных микросхемах шины данных записи и чтения (DI и DO) обычно представляют собой общую двунаправленную шину. • Сигналы на шине управления означают: MW сигнал записи в память, MR сигнал чтения из памяти. • Сигнал выбора микросхемы CS# (Chip Select). • Этот вход обычно является инверсным и при единичном значении на нем микросхема переходит в "выключенное" состояние (выход данных микросхемы переходит в состояние высокого выходного сопротивления, если он является z выходом, или в состояние "1", если это инверсный выход с открытым коллектором). При нулевом значении сигнала на входе CS# микросхема находится в активном состоянии. 31

• В реальных микросхемах шины данных записи и чтения (DI и DO) обычно представляют собой общую двунаправленную шину. • Сигналы на шине управления означают: MW сигнал записи в память, MR сигнал чтения из памяти. • Сигнал выбора микросхемы CS# (Chip Select). • Этот вход обычно является инверсным и при единичном значении на нем микросхема переходит в "выключенное" состояние (выход данных микросхемы переходит в состояние высокого выходного сопротивления, если он является z выходом, или в состояние "1", если это инверсный выход с открытым коллектором). При нулевом значении сигнала на входе CS# микросхема находится в активном состоянии. 31