Аппаратные средства ВТ Узлы и блоки ЭВМ Лекция 1 Арифметико-логическое устройство Доцент кафедры ИТ Крюкова Л. В.

Декомпозиция вычислительного устройства на операционный и управляющий блоки. Как показал акад. В. М. Глушков, в любом устройстве обработки цифровой информации можно выделить операционный и управляющий блоки. Такой подход упрощает проектирование, а также облегчает понимание процесса функционирования вычислительного устройства. 2

Декомпозиция цифрового вычисли тельного устройства Рис 1. Операционные и управляю блоки цифрового устройства 3

Операционный блок состоит из регистров, сумматоров и других узлов, производящих прием из внешней среды и хранение кодов слов, их преобразование и выдачу во внешнюю среду результата преобразования, а также выдачу в управляющий блок и внешнюю среду оповещающих сигналов, принадлежащих к множеству: 4

Процесс функционирования во времени устройства обработки цифровой информации состоит из последовательности тактовых интервалов, в которых операционный блок производит определенные элементарные операции преобразования слов. Операционный блок выполняет некоторый набор элементарных преобразований информации, например таких, как передача слова из одного в другой, взятие обратного кода, сдвиг и др. Выполнение этих элементарных операций инициируется поступлением в операционный блок соответствующих управляющих сигналов из некоторого множества сигналов 5

Элементарная функциональная операция, выполняемая за один тактовый интервал и приводи мая в действие управляющим сигналом, называется микрооперацией. 6

В некоторые такты могут поступать несколько управляющих сигналов, вызывая параллельное во времени выполнение не скольких микроопераций. Такая совокупность микроопераций называется микрокомандой. В частности, микрокоманда может состоять из одной микрооперации. 7

Управляющий блок (или управляю автомат) вырабатывает распределенную во времени последовательность управляющих сигналов порождающих в операционном блоке нужную последовательность микроопераций. 8

Последовательность управляющих сигналов определяется сигналами Х кода операции, поступающими в управляющий блок извне, и сигналами У, зависящими от операндов и промежуточных результатов преобразований. Операционный блок задается его структурой, т. е. составом узлов и связями между ними, и выполняемым операционным блоком набором микроопераций. 9

• Последовательность микрокоманд, обеспечивающая выполнение данной операции (например, операции нормализации числа с плавающей точкой), называется микропрограммой данной операции. • Функционирование вычислительного устройства может быть описано совокупностью реализуемых в нем микропрограмм. Это в ряде случаев удобный, хотя и не единственно возможный способ описания цифровых устройств. 10

Арифметико-логическое устройство (АЛУ) В современных ЭВМ арифметикологическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер. 11

ПРИНЦИПЫ ОРГАНИЗАЦИИ АРИФМЕТИКО-ЛОГИЧЕСКИХ УСТРОЙСТВ Общие сведения. Арифметическо-логические устройства (АЛУ) служат для выполнения арифметических и логических преобразований над словами, называемыми в этом случае операндами. 12

Операции, выполняемые в АЛУ можно разделить на следующие группы: • операции двоичной арифметики для чисел с фиксированной точкой; операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой; • операции десятичной арифметики; • операции индексной арифметики (при модификации адресов команд); • операции специальной арифметики; • операции над логическими кодами (логические операции); • операции над алфавитно-цифровыми полями. 13

Современные ЭВМ общего назначения обычно реализуют операции всех приведенных выше групп, а малые и микро. ЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитноцифровыми полями. В этом случае эти операции выполняются специальными подпрограммами 14

• К арифметическим операциям относятся сложение, вычитание модулей ( «короткие операции» ) и умножение и деление ( «длинные операции» ). • Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство. • Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остается на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами). Обширна группа операций редактирования алфавитно-цифровой информации. 15

Классификация АЛУ • • • По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов. По способу представления чисел различают АЛУ: 1) для чисел с фиксированной точкой; 2) для чисел с плавающей точкой; З) для десятичных чисел. По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в от дельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые комму тируются нужным образом в зависимости от требуемого режима работы. 16

• По своим функциям АЛУ является операционным блоком (см. рис 1), выполняющим микрооперации, обеспечивающие прием из других устройств (например, памяти) операндов, их пре образование и выдачу результатов преобразования в другие устройства. • Работа АЛУ организуется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определенных микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами. 17

Синтез АЛУ проходит в несколько этапов. 1. Выбрать метод, по которому предполагается выполнение операции, и составить алгоритм соответствующих действий. 2. Определить набор составляющих АЛУ элементов, исходя из алгоритма и формата исходных данных. 3. Определить связи между элементами, установить порядок функционирования устройства и временную диаграмму управляющих сигналов, которые должны быть поданы на АЛУ от устройства управления. 18

19

Алгоритм операции умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя 20

Каждой переменной, представленной в алгоритме, в схеме должен соответствовать элемент хранения. Разрядность модуля произведения равна сумме разрядностей сомножителей. Умножение двоичного числа на 2 -i обеспечивается сдвигом этого числа вправо на соответствующее количество разрядов. Переход к анализу очередного разряда множителя (i = i + 1) может быть обеспечен сдвигом регистра множителя на один разряд в сторону старших разрядов. 21

Состав оборудования, необходимого для реализации АЛУ заданного типа для n = 4 Таблица 1. Разряд нос ть Функции Управляющи й сигнал Регистр модуля множимого RGX 8 Загрузка. Сдвиг в сторону младших разрядов. УС 1 УС 2 Регистр модуля множителя RGY 4 Загрузка. Сдвиг в сторону старших разрядов. УС 3 УС 4 Регистр модуля результата RGZ 8 Загрузка. Установка в "0". УС 5 УС 6 Триггер знака множимого TX Загрузка УС 7 Триггер знака множителя TY Загрузка УС 8 Триггер знака результата TZ Загрузка УС 9 Комбинационный сумматор – Получение на входе АЛУ сигналов "0" или RGX в зависимости от значения yi – Схема АЛУ Комбинационные схемы 8 22

Структурная схема арифметического устройства для выполнения операции умножения со старших разрядов множителя чисел, заданных в прямом коде. 23

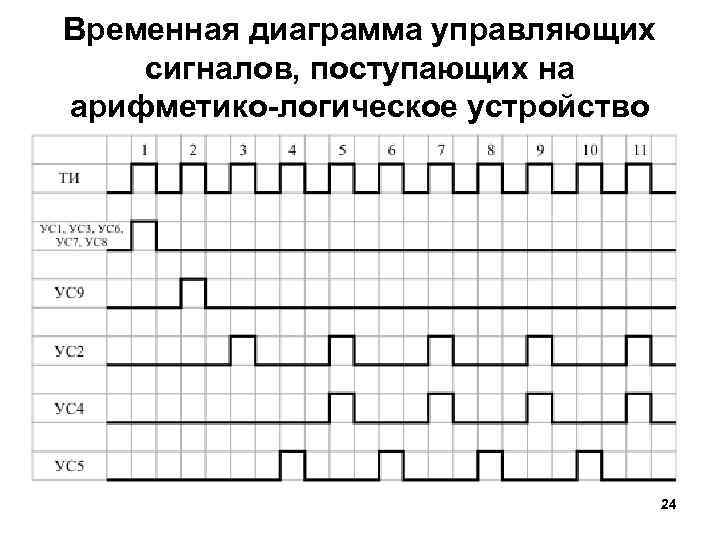

Временная диаграмма управляющих сигналов, поступающих на арифметико-логическое устройство 24

Работа схемы Такт 1. Загрузка модулей операндов в регистры RGX, RGY, а их знаков – в триггеры TX и TY. Сброс в "0" регистра результата RGZ. Такт 2. Запись знака результата в триггер TZ. Такт 3. Сдвиг регистра RGX на один разряд вправо. Через время, равное задержке на переключение регистров и комбинационных схем, на выходе комбинационного сумматора и, следовательно, на входе регистра RGZ устанавливается результат 0+y 1 • |X| • 2 -1. Такт 4. Загрузка RGZ: |Z|=|Z|+y 1 • |X| • 2 -1. Такт 5. Сдвиг RGX на 1 разряд вправо: |X| = |X| • 2 -1. Сдвиг RGY на 1 разряд влево: i=i+1. Устройство управления проверяет условие окончания операции: i > n. Такты (6, 7), (8, 9), (10, 11). . . Повтор действий тактов (4, 5) с анализом других значений yi. В такте 10 в регистре RGZ формируется модуль произведения. Такт 11 используется лишь для определения условия окончания операции умножения. 25

Универсальные (АЛУ) • Выполняют арифметические и логические операции над двумя операндами. • Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛУ и обеспечивающей перестройку с одной операции на другую. Обычно АЛУ четырех разрядные и для наращивания разрядности объединяются. 26

Условное обозначение АЛУ Перечень выполняемых АЛУ операций дан в табл. . 27

В ИС имеются входы операндов А и В, входы выбора операций , вход переноса С из младшего разряда и вход М, сигнал которого задает тип выполняемых операций: логические (М= 1) или арифметикологические (М=О). Результат операции вырабатывается на выходах Е. Выходы С и Н используются для организации параллельных переносов при наращивании разрядности обрабатываемых слов. Сигнал С —- выход ной перенос в старший разряд, а выход «А = В» выход, равный « 1» при условии А = В. 28

• При операциях над словами большой разрядности АЛУ соединяются друг с другом с организацией последовательных и параллельных переносов. Соединение микросхем АЛУ в первом случае аналогично соединению сумматоров в схеме с последовательным переносом: выход С предыдущей микросхемы соединяется с входом С, последующей. Если используется организация с параллельными переносами, то совместно с АЛУ применяют специальные микросхемы — блоки ускоренного переноса. • Один блок ускоренного переноса обеспечивает анализ специальных вспомогательных сигналов Си II, формируемых всеми микросхемами АЛУ, и формирование для них сигналов переноса С, Сигналы переноса в старший разряд С при этом не используются. 29