f1749e16251b1cc9d11a5a4ebaee01ad.ppt

- Количество слайдов: 30

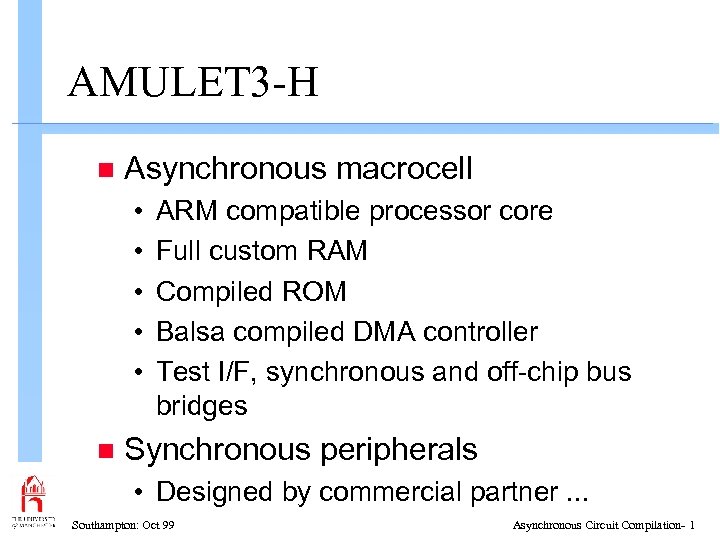

AMULET 3 -H n Asynchronous macrocell • • • n ARM compatible processor core Full custom RAM Compiled ROM Balsa compiled DMA controller Test I/F, synchronous and off-chip bus bridges Synchronous peripherals • Designed by commercial partner. . . Southampton: Oct 99 Asynchronous Circuit Compilation- 1

AMULET 3 -H n Asynchronous macrocell • • • n ARM compatible processor core Full custom RAM Compiled ROM Balsa compiled DMA controller Test I/F, synchronous and off-chip bus bridges Synchronous peripherals • Designed by commercial partner. . . Southampton: Oct 99 Asynchronous Circuit Compilation- 1

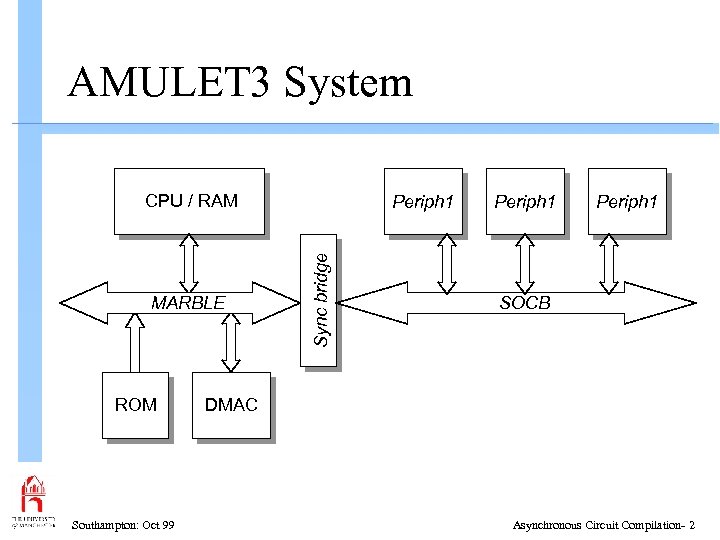

AMULET 3 System CPU / RAM ROM Southampton: Oct 99 Sync bridge MARBLE Periph 1 SOCB DMAC Asynchronous Circuit Compilation- 2

AMULET 3 System CPU / RAM ROM Southampton: Oct 99 Sync bridge MARBLE Periph 1 SOCB DMAC Asynchronous Circuit Compilation- 2

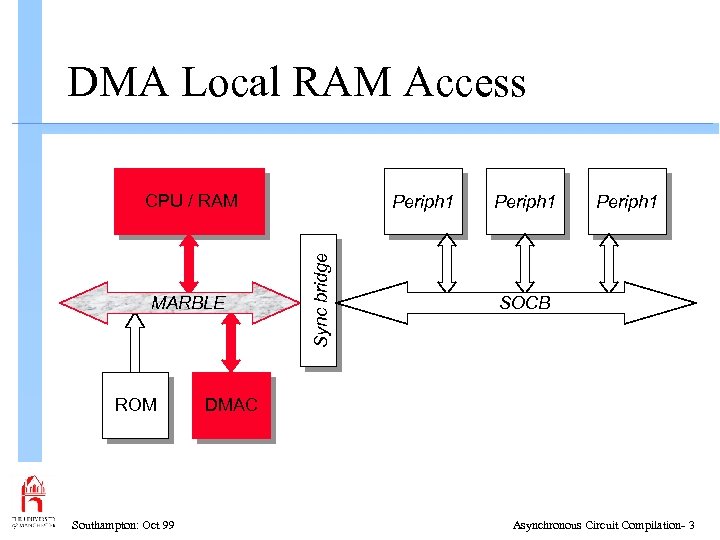

DMA Local RAM Access CPU / RAM ROM Southampton: Oct 99 Sync bridge MARBLE Periph 1 SOCB DMAC Asynchronous Circuit Compilation- 3

DMA Local RAM Access CPU / RAM ROM Southampton: Oct 99 Sync bridge MARBLE Periph 1 SOCB DMAC Asynchronous Circuit Compilation- 3

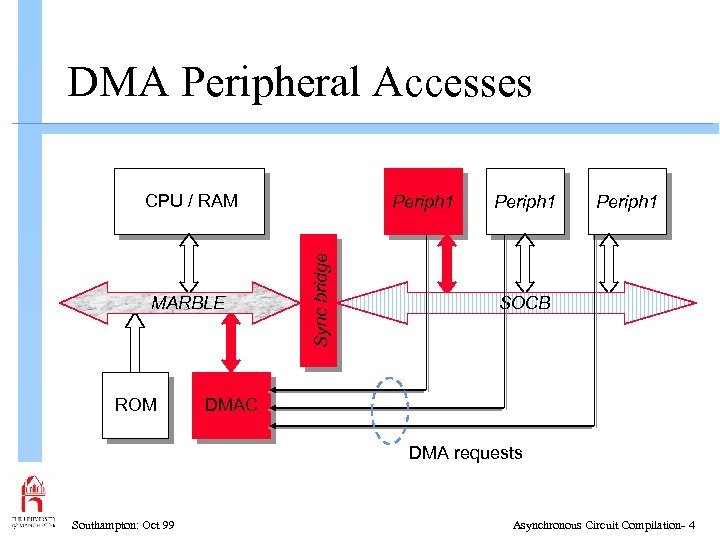

DMA Peripheral Accesses CPU / RAM ROM Sync bridge MARBLE Periph 1 SOCB DMAC DMA requests Southampton: Oct 99 Asynchronous Circuit Compilation- 4

DMA Peripheral Accesses CPU / RAM ROM Sync bridge MARBLE Periph 1 SOCB DMAC DMA requests Southampton: Oct 99 Asynchronous Circuit Compilation- 4

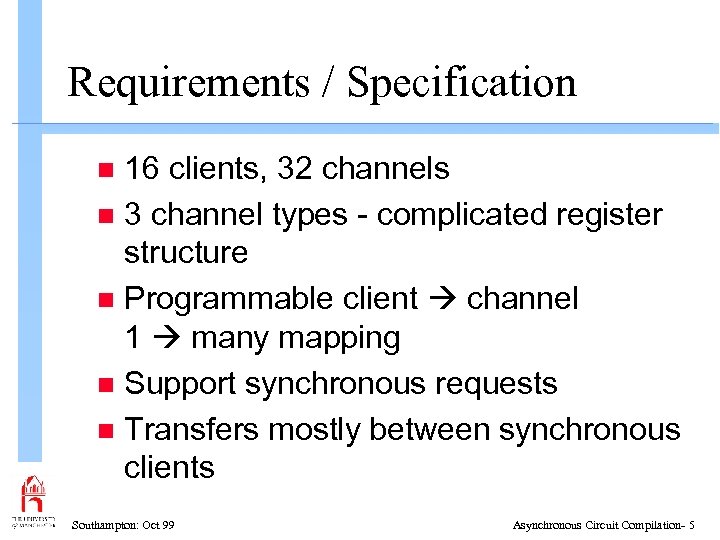

Requirements / Specification 16 clients, 32 channels n 3 channel types - complicated register structure n Programmable client channel 1 many mapping n Support synchronous requests n Transfers mostly between synchronous clients n Southampton: Oct 99 Asynchronous Circuit Compilation- 5

Requirements / Specification 16 clients, 32 channels n 3 channel types - complicated register structure n Programmable client channel 1 many mapping n Support synchronous requests n Transfers mostly between synchronous clients n Southampton: Oct 99 Asynchronous Circuit Compilation- 5

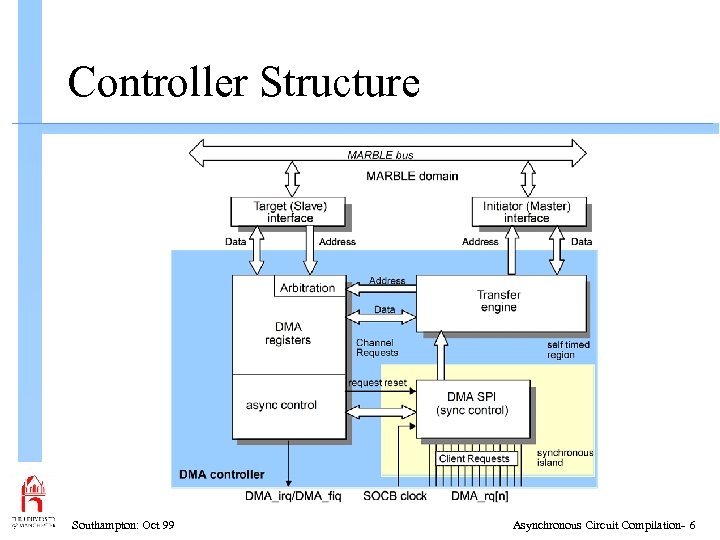

Controller Structure Southampton: Oct 99 Asynchronous Circuit Compilation- 6

Controller Structure Southampton: Oct 99 Asynchronous Circuit Compilation- 6

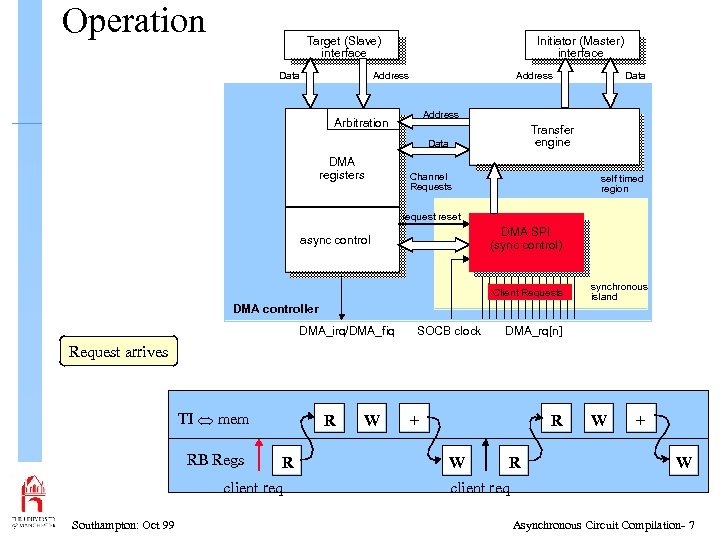

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] Request arrives TI Û mem RB Regs R R client req Southampton: Oct 99 W + R W + W client req Asynchronous Circuit Compilation- 7

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] Request arrives TI Û mem RB Regs R R client req Southampton: Oct 99 W + R W + W client req Asynchronous Circuit Compilation- 7

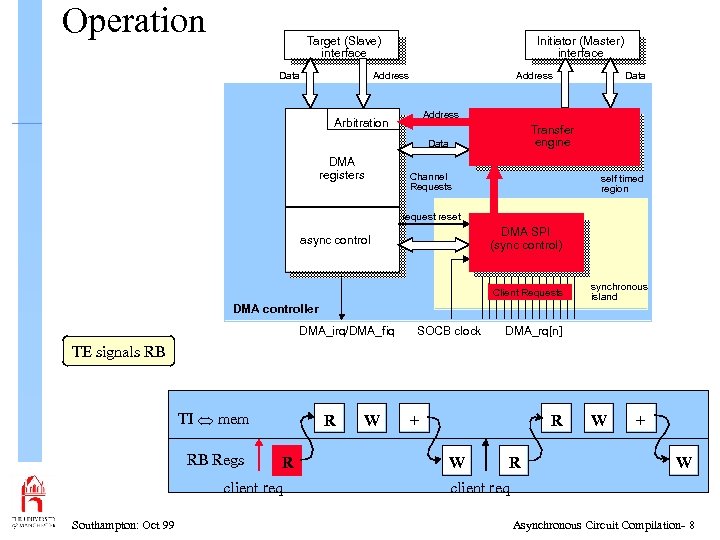

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] TE signals RB TI Û mem RB Regs R R client req Southampton: Oct 99 W + R W + W client req Asynchronous Circuit Compilation- 8

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] TE signals RB TI Û mem RB Regs R R client req Southampton: Oct 99 W + R W + W client req Asynchronous Circuit Compilation- 8

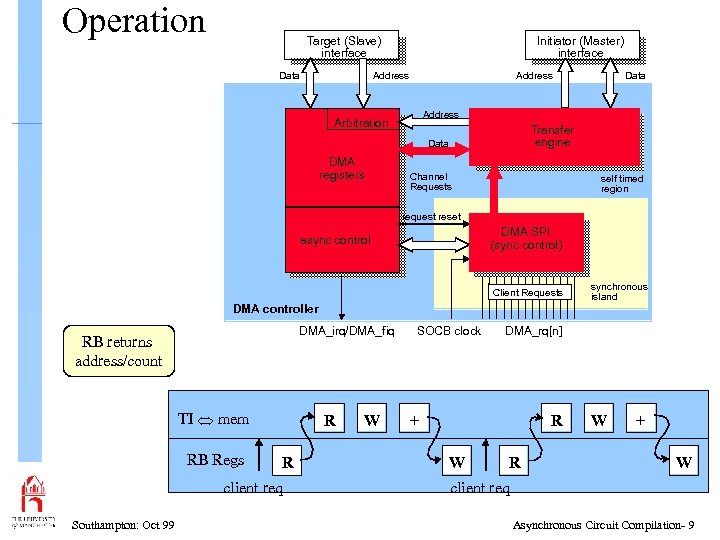

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq RB returns address/count TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 9

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq RB returns address/count TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 9

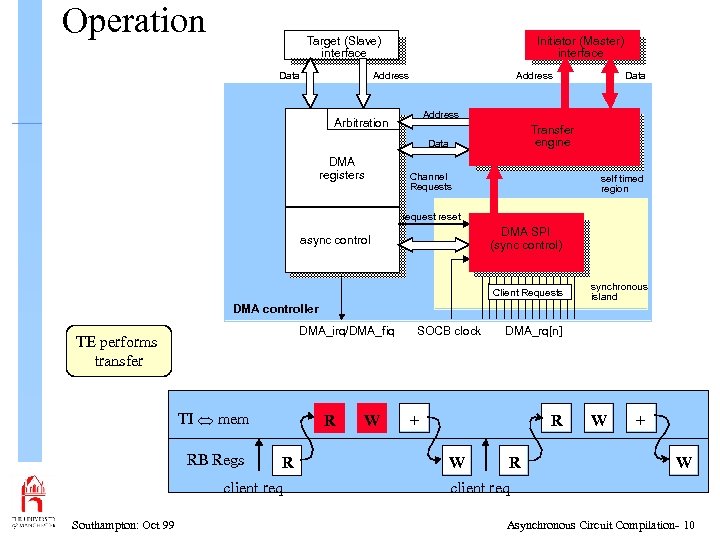

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq TE performs transfer TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 10

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq TE performs transfer TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 10

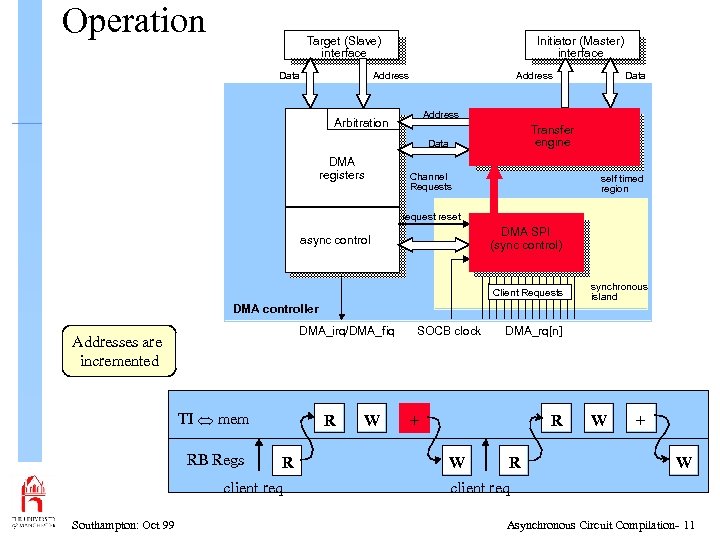

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq Addresses are incremented TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 11

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq Addresses are incremented TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 11

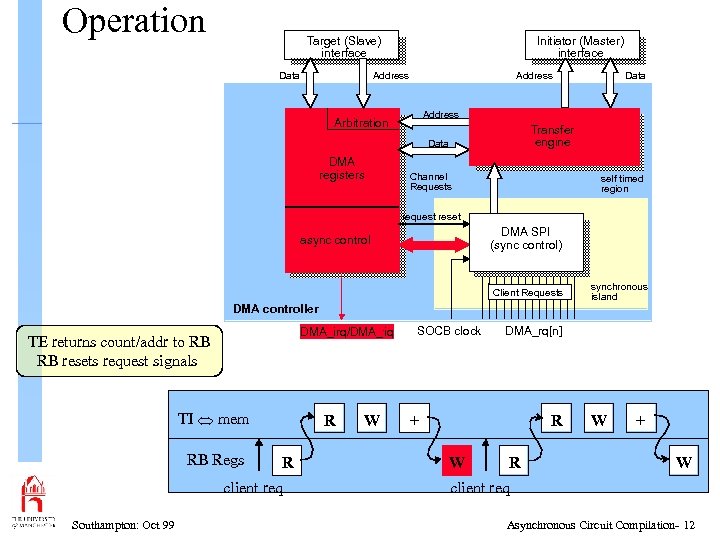

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fq i TE returns count/addr to RB RB resets request signals TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 12

Operation Target (Slave) interface Data Initiator (Master) interface Address Arbitration Transfer engine Data DMA registers Data Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fq i TE returns count/addr to RB RB resets request signals TI Û mem RB Regs R R client req Southampton: Oct 99 W SOCB clock DMA_rq[n] + R W synchronous island R W + W client req Asynchronous Circuit Compilation- 12

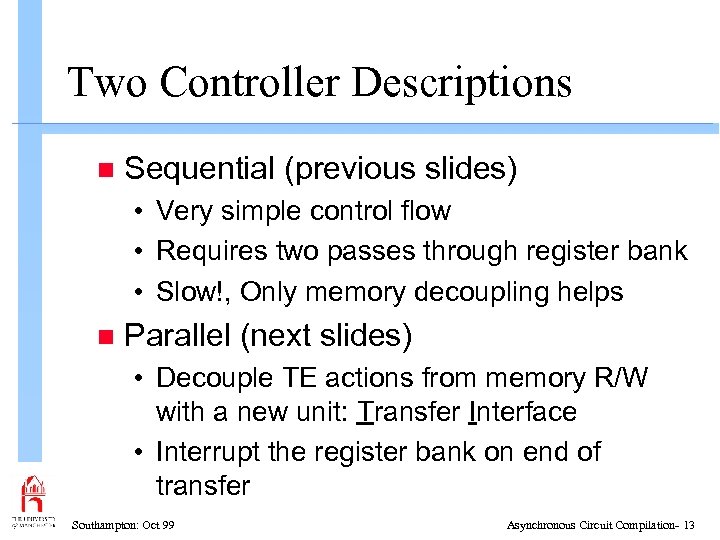

Two Controller Descriptions n Sequential (previous slides) • Very simple control flow • Requires two passes through register bank • Slow!, Only memory decoupling helps n Parallel (next slides) • Decouple TE actions from memory R/W with a new unit: Transfer Interface • Interrupt the register bank on end of transfer Southampton: Oct 99 Asynchronous Circuit Compilation- 13

Two Controller Descriptions n Sequential (previous slides) • Very simple control flow • Requires two passes through register bank • Slow!, Only memory decoupling helps n Parallel (next slides) • Decouple TE actions from memory R/W with a new unit: Transfer Interface • Interrupt the register bank on end of transfer Southampton: Oct 99 Asynchronous Circuit Compilation- 13

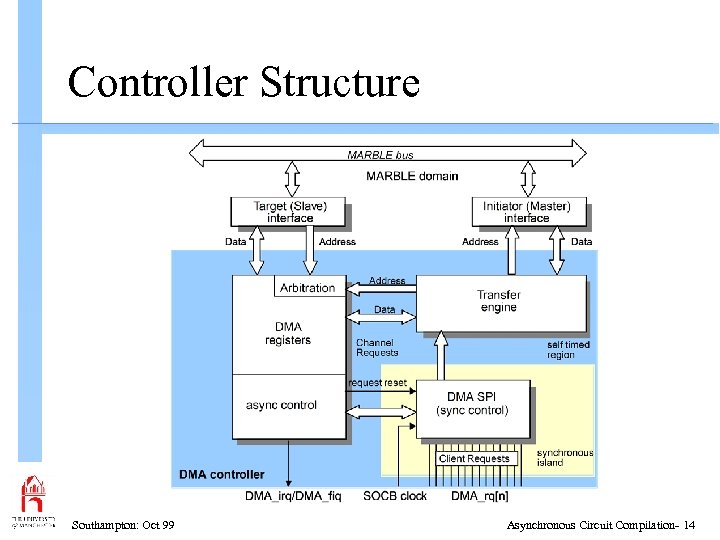

Controller Structure Southampton: Oct 99 Asynchronous Circuit Compilation- 14

Controller Structure Southampton: Oct 99 Asynchronous Circuit Compilation- 14

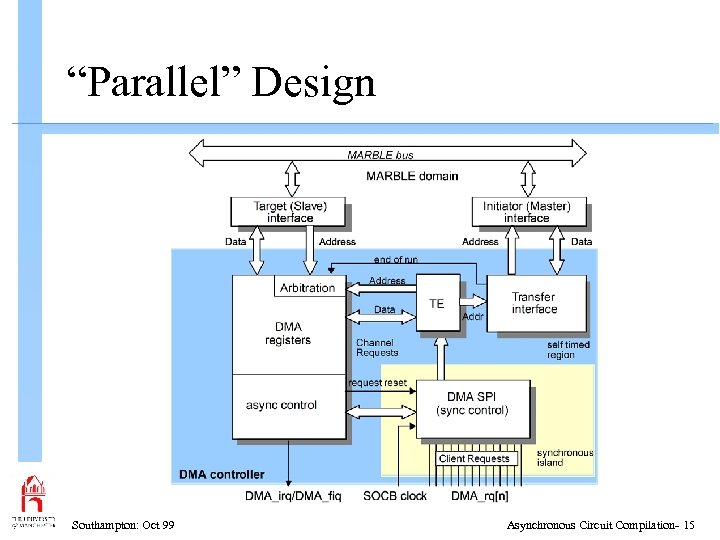

“Parallel” Design Southampton: Oct 99 Asynchronous Circuit Compilation- 15

“Parallel” Design Southampton: Oct 99 Asynchronous Circuit Compilation- 15

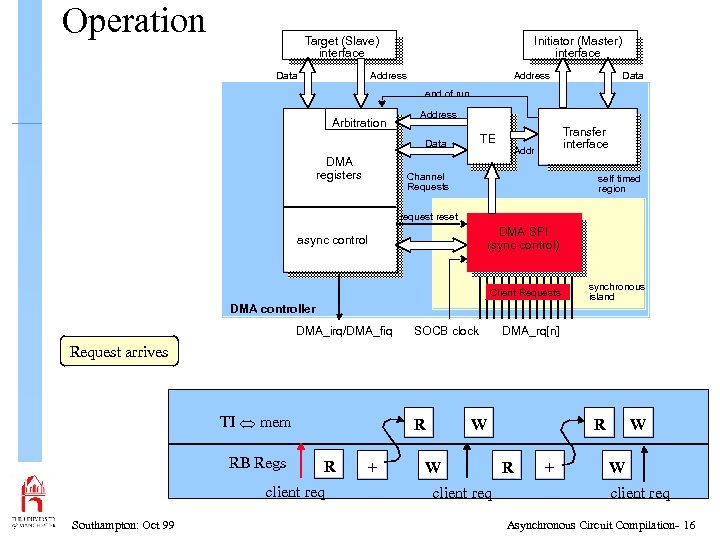

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] Request arrives TI Û mem RB Regs R R client req Southampton: Oct 99 + W W client req R R + W W client req Asynchronous Circuit Compilation- 16

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] Request arrives TI Û mem RB Regs R R client req Southampton: Oct 99 + W W client req R R + W W client req Asynchronous Circuit Compilation- 16

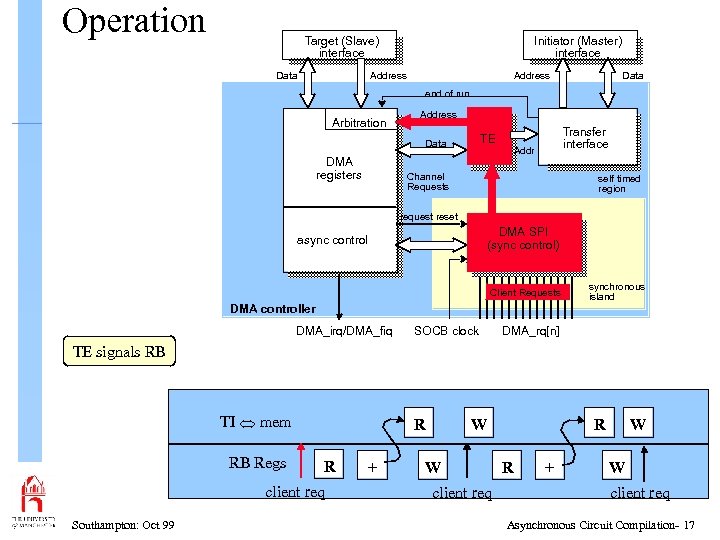

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] TE signals RB TI Û mem RB Regs R R client req Southampton: Oct 99 + W W client req R R + W W client req Asynchronous Circuit Compilation- 17

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] TE signals RB TI Û mem RB Regs R R client req Southampton: Oct 99 + W W client req R R + W W client req Asynchronous Circuit Compilation- 17

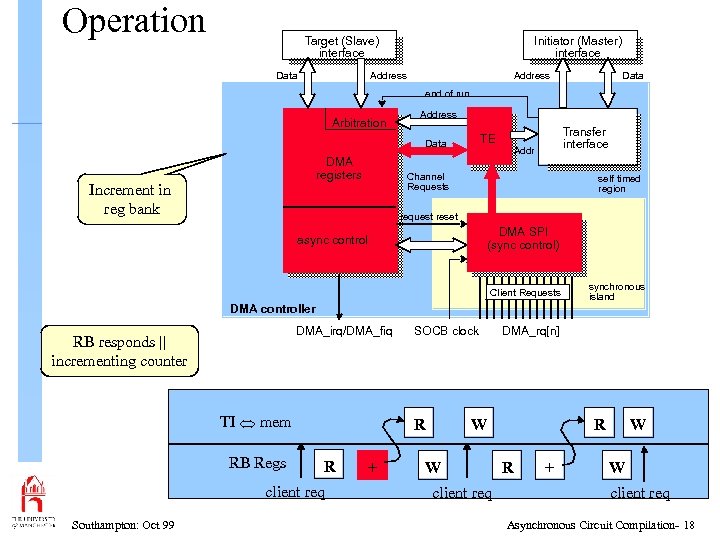

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Increment in reg bank Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq RB responds || incrementing counter TI Û mem RB Regs R R client req Southampton: Oct 99 SOCB clock + DMA_rq[n] W W client req synchronous island R R + W W client req Asynchronous Circuit Compilation- 18

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Increment in reg bank Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq RB responds || incrementing counter TI Û mem RB Regs R R client req Southampton: Oct 99 SOCB clock + DMA_rq[n] W W client req synchronous island R R + W W client req Asynchronous Circuit Compilation- 18

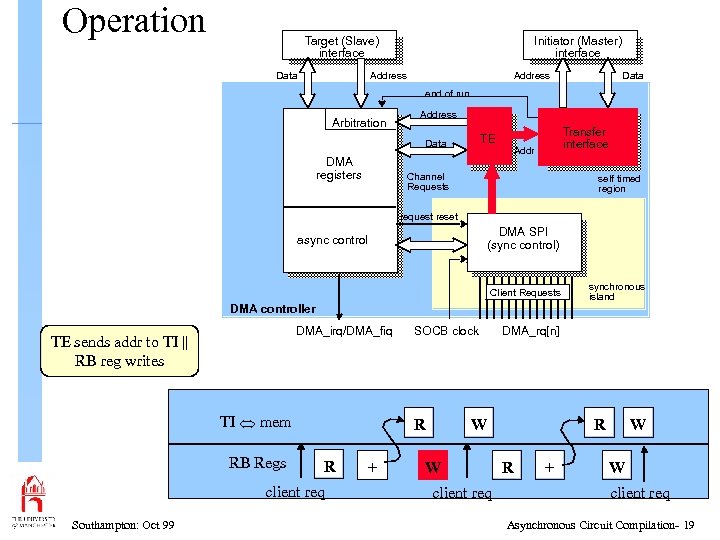

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq TE sends addr to TI || RB reg writes TI Û mem RB Regs R R client req Southampton: Oct 99 SOCB clock + DMA_rq[n] W W client req synchronous island R R + W W client req Asynchronous Circuit Compilation- 19

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq TE sends addr to TI || RB reg writes TI Û mem RB Regs R R client req Southampton: Oct 99 SOCB clock + DMA_rq[n] W W client req synchronous island R R + W W client req Asynchronous Circuit Compilation- 19

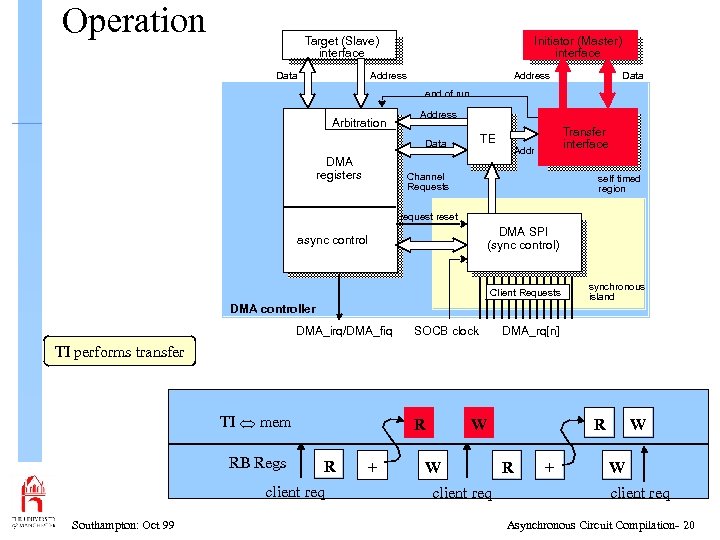

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] TI performs transfer TI Û mem RB Regs R R client req Southampton: Oct 99 + W W client req R R + W W client req Asynchronous Circuit Compilation- 20

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq SOCB clock synchronous island DMA_rq[n] TI performs transfer TI Û mem RB Regs R R client req Southampton: Oct 99 + W W client req R R + W W client req Asynchronous Circuit Compilation- 20

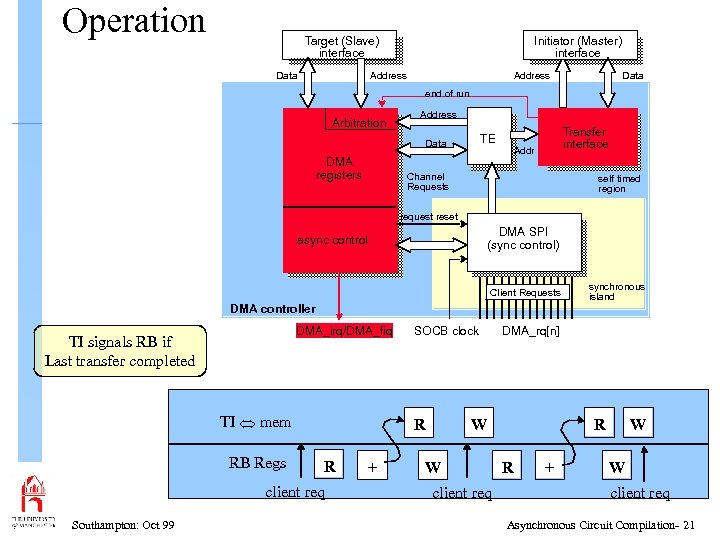

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq TI signals RB if Last transfer completed TI Û mem RB Regs R R client req Southampton: Oct 99 SOCB clock + DMA_rq[n] W W client req synchronous island R R + W W client req Asynchronous Circuit Compilation- 21

Operation Target (Slave) interface Data Initiator (Master) interface Address Data end of run Arbitration Address TE Data DMA registers Transfer engine interface Addr Channel Requests self timed region request reset DMA SPI (sync control) async control Client Requests DMA controller DMA_irq/DMA_fiq TI signals RB if Last transfer completed TI Û mem RB Regs R R client req Southampton: Oct 99 SOCB clock + DMA_rq[n] W W client req synchronous island R R + W W client req Asynchronous Circuit Compilation- 21

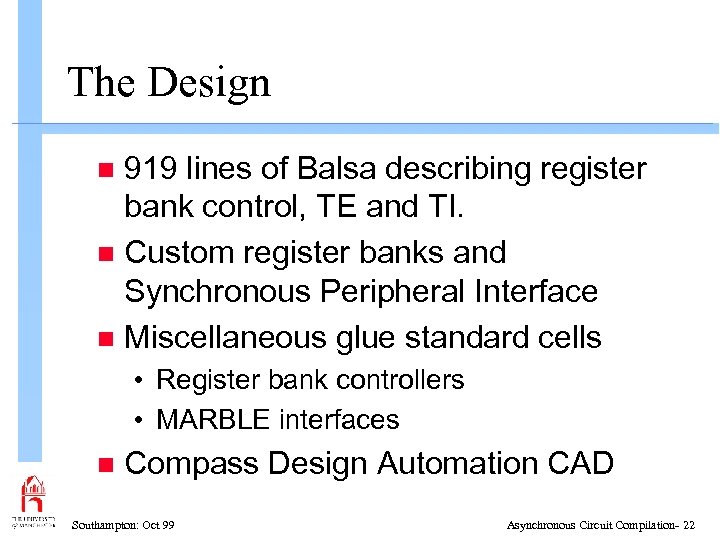

The Design 919 lines of Balsa describing register bank control, TE and TI. n Custom register banks and Synchronous Peripheral Interface n Miscellaneous glue standard cells n • Register bank controllers • MARBLE interfaces n Compass Design Automation CAD Southampton: Oct 99 Asynchronous Circuit Compilation- 22

The Design 919 lines of Balsa describing register bank control, TE and TI. n Custom register banks and Synchronous Peripheral Interface n Miscellaneous glue standard cells n • Register bank controllers • MARBLE interfaces n Compass Design Automation CAD Southampton: Oct 99 Asynchronous Circuit Compilation- 22

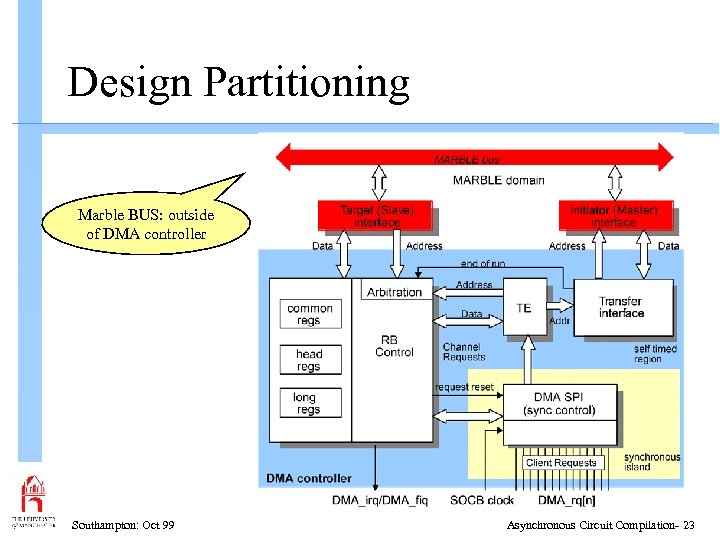

Design Partitioning Marble BUS: outside of DMA controller Southampton: Oct 99 Asynchronous Circuit Compilation- 23

Design Partitioning Marble BUS: outside of DMA controller Southampton: Oct 99 Asynchronous Circuit Compilation- 23

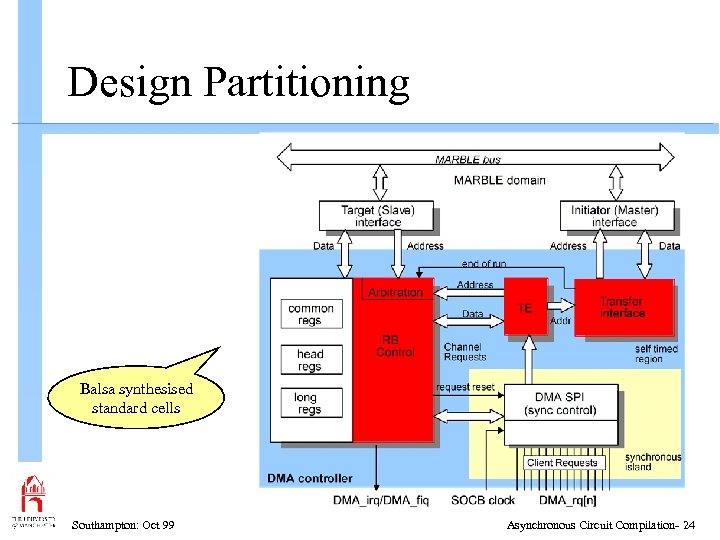

Design Partitioning Balsa synthesised standard cells Southampton: Oct 99 Asynchronous Circuit Compilation- 24

Design Partitioning Balsa synthesised standard cells Southampton: Oct 99 Asynchronous Circuit Compilation- 24

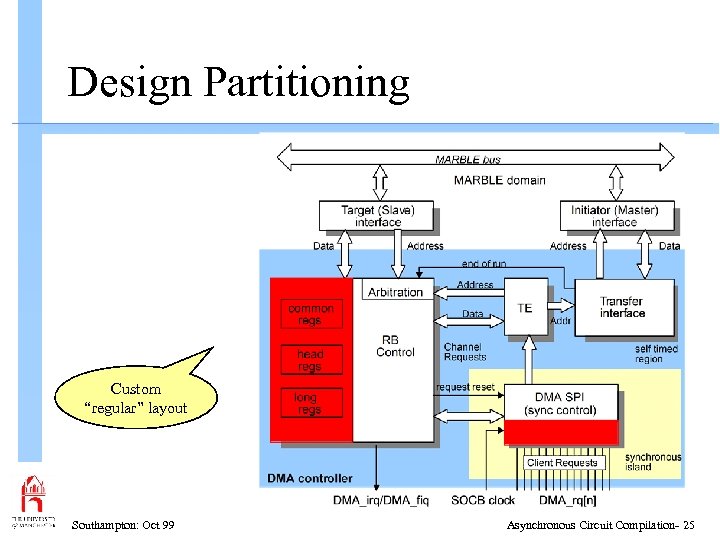

Design Partitioning Custom “regular” layout Southampton: Oct 99 Asynchronous Circuit Compilation- 25

Design Partitioning Custom “regular” layout Southampton: Oct 99 Asynchronous Circuit Compilation- 25

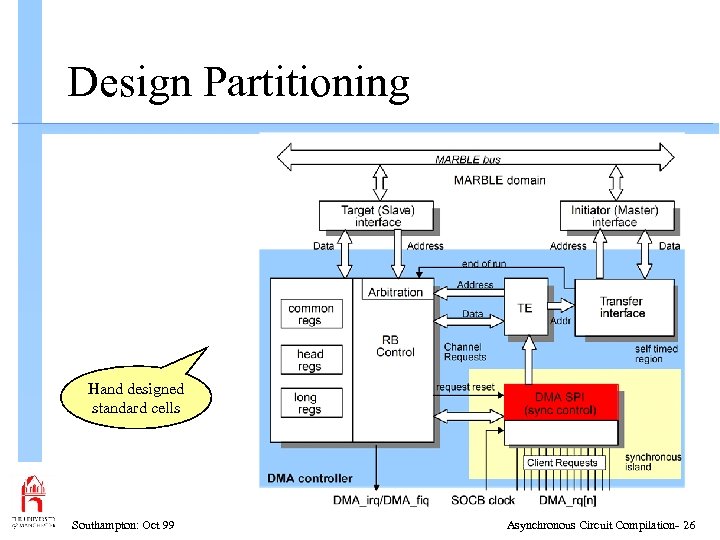

Design Partitioning Hand designed standard cells Southampton: Oct 99 Asynchronous Circuit Compilation- 26

Design Partitioning Hand designed standard cells Southampton: Oct 99 Asynchronous Circuit Compilation- 26

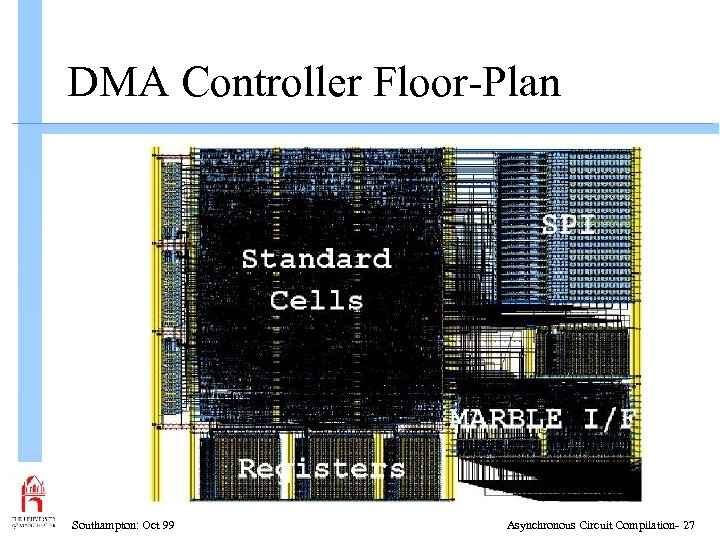

DMA Controller Floor-Plan Southampton: Oct 99 Asynchronous Circuit Compilation- 27

DMA Controller Floor-Plan Southampton: Oct 99 Asynchronous Circuit Compilation- 27

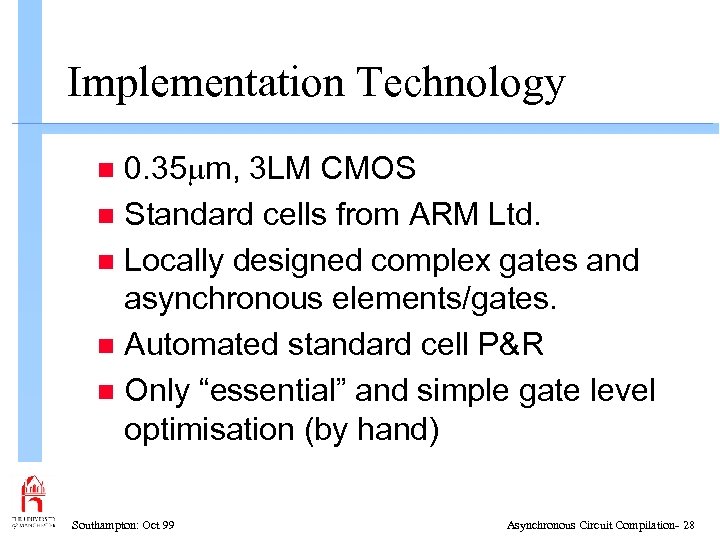

Implementation Technology 0. 35 m, 3 LM CMOS n Standard cells from ARM Ltd. n Locally designed complex gates and asynchronous elements/gates. n Automated standard cell P&R n Only “essential” and simple gate level optimisation (by hand) n Southampton: Oct 99 Asynchronous Circuit Compilation- 28

Implementation Technology 0. 35 m, 3 LM CMOS n Standard cells from ARM Ltd. n Locally designed complex gates and asynchronous elements/gates. n Automated standard cell P&R n Only “essential” and simple gate level optimisation (by hand) n Southampton: Oct 99 Asynchronous Circuit Compilation- 28

Simulation LARD behavioural modelling n EPIC Time. Mill transistor level simulation n • on schematic • on cap. Extracted netlist Time. Mill is calibrated using SPICE, claims to be within a few % of SPICE n Results measured for run of 16 mem To mem transfers. n Southampton: Oct 99 Asynchronous Circuit Compilation- 29

Simulation LARD behavioural modelling n EPIC Time. Mill transistor level simulation n • on schematic • on cap. Extracted netlist Time. Mill is calibrated using SPICE, claims to be within a few % of SPICE n Results measured for run of 16 mem To mem transfers. n Southampton: Oct 99 Asynchronous Circuit Compilation- 29

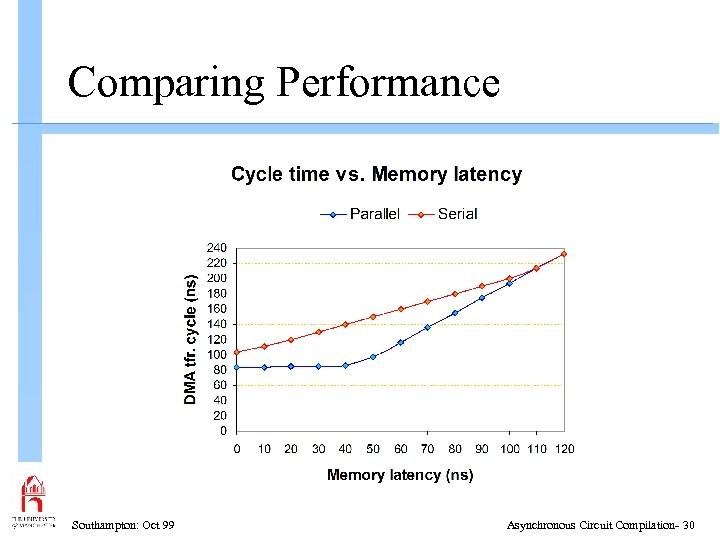

Comparing Performance Southampton: Oct 99 Asynchronous Circuit Compilation- 30

Comparing Performance Southampton: Oct 99 Asynchronous Circuit Compilation- 30