997873a365b55705d5fac40254691a60.ppt

- Количество слайдов: 27

Agilent Technologies Accelerating the Future of DFT Tom Newsom Vice President & General Manager SOC Business Unit May 2003

Agilent Technologies Accelerating the Future of DFT Tom Newsom Vice President & General Manager SOC Business Unit May 2003

Overview Increasing Market Momentum Agilent Introduces the FIRST for DFT CTL: what is it, why it’s important Design-to-Test Process Agilent’s Power of DFT The Future…What’s Next? CTL Press Event May 2003 3 Solution Browser

Overview Increasing Market Momentum Agilent Introduces the FIRST for DFT CTL: what is it, why it’s important Design-to-Test Process Agilent’s Power of DFT The Future…What’s Next? CTL Press Event May 2003 3 Solution Browser

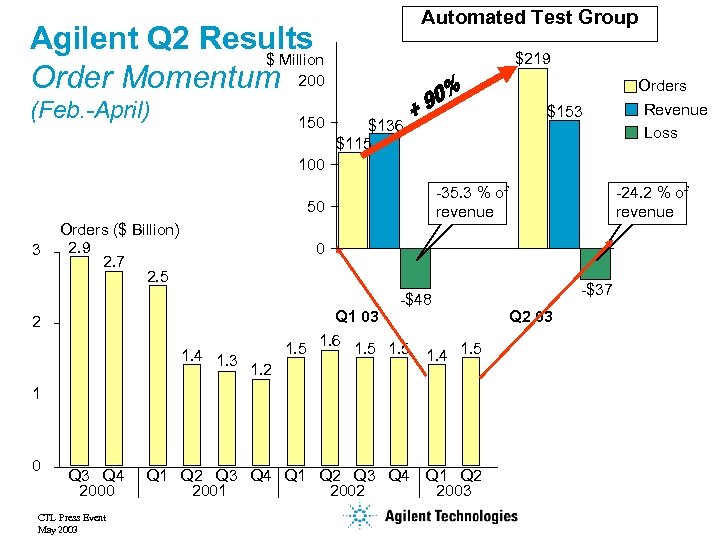

Automated Test Group Agilent Q 2 Results $ Million Order Momentum 200 (Feb. -April) 150 $219 Orders $153 $136 $115 Revenue Loss 100 -35. 3 % of revenue 50 3 Orders ($ Billion) 2. 9 2. 7 2. 5 0 Q 1 03 2 1. 4 1. 3 1. 2 -$48 1. 5 1. 6 1. 5 1. 4 1. 5 1 0 Q 3 Q 4 2000 CTL Press Event May 2003 -24. 2 % of revenue Q 1 Q 2 Q 3 Q 4 2001 2002 Q 1 Q 2 2003 -$37 Q 2 03

Automated Test Group Agilent Q 2 Results $ Million Order Momentum 200 (Feb. -April) 150 $219 Orders $153 $136 $115 Revenue Loss 100 -35. 3 % of revenue 50 3 Orders ($ Billion) 2. 9 2. 7 2. 5 0 Q 1 03 2 1. 4 1. 3 1. 2 -$48 1. 5 1. 6 1. 5 1. 4 1. 5 1 0 Q 3 Q 4 2000 CTL Press Event May 2003 -24. 2 % of revenue Q 1 Q 2 Q 3 Q 4 2001 2002 Q 1 Q 2 2003 -$37 Q 2 03

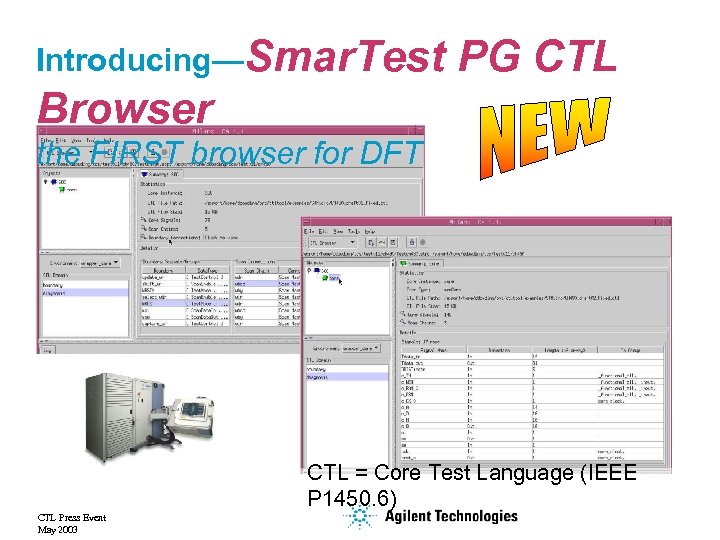

Introducing—Smar. Test PG CTL Browser the FIRST browser for DFT CTL = Core Test Language (IEEE P 1450. 6) CTL Press Event May 2003

Introducing—Smar. Test PG CTL Browser the FIRST browser for DFT CTL = Core Test Language (IEEE P 1450. 6) CTL Press Event May 2003

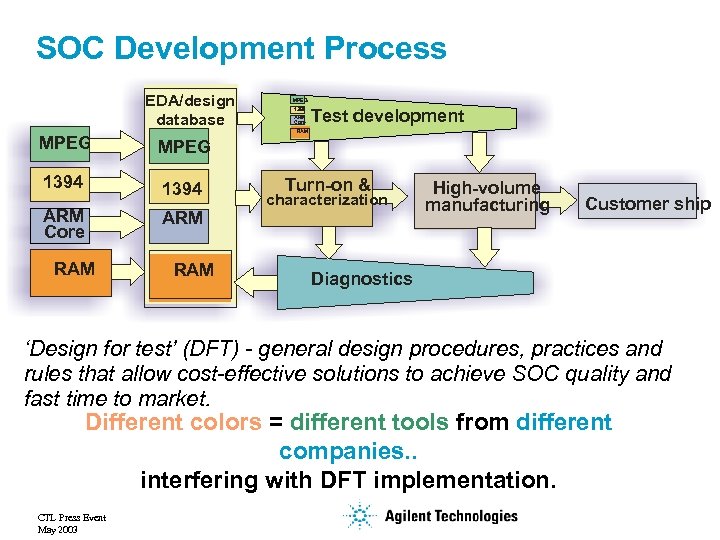

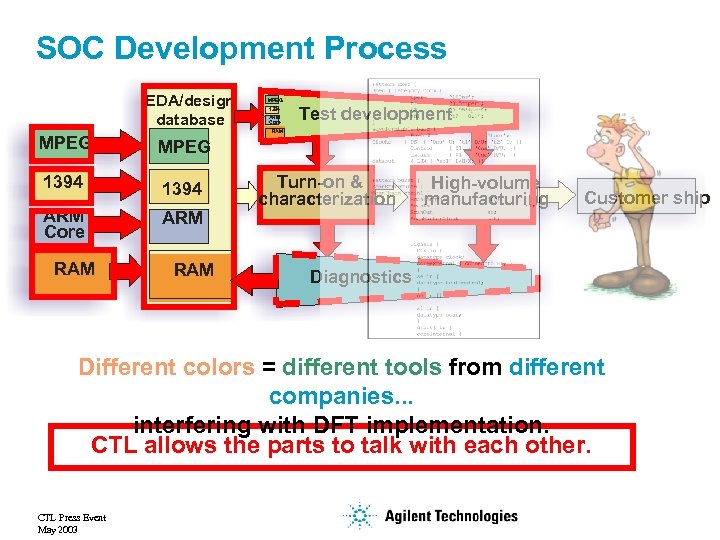

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics ‘Design for test’ (DFT) - general design procedures, practices and rules that allow cost-effective solutions to achieve SOC quality and fast time to market. Different colors = different tools from different companies. . interfering with DFT implementation. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics ‘Design for test’ (DFT) - general design procedures, practices and rules that allow cost-effective solutions to achieve SOC quality and fast time to market. Different colors = different tools from different companies. . interfering with DFT implementation. CTL Press Event May 2003

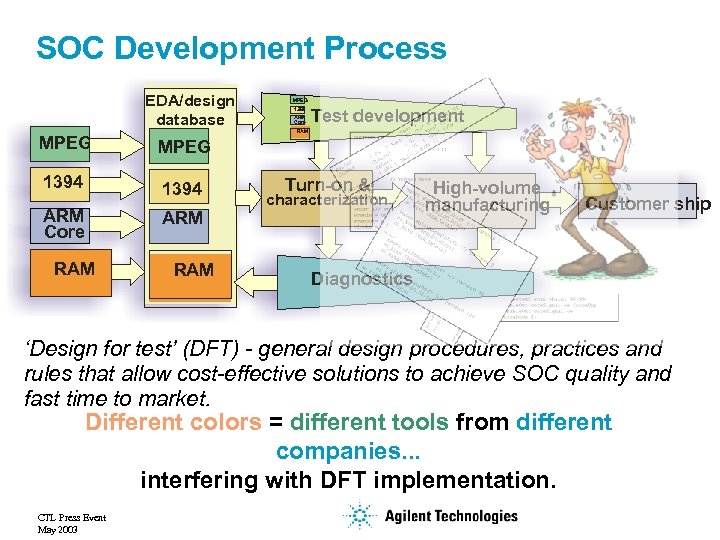

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics ‘Design for test’ (DFT) - general design procedures, practices and rules that allow cost-effective solutions to achieve SOC quality and fast time to market. Different colors = different tools from different companies. . . interfering with DFT implementation. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics ‘Design for test’ (DFT) - general design procedures, practices and rules that allow cost-effective solutions to achieve SOC quality and fast time to market. Different colors = different tools from different companies. . . interfering with DFT implementation. CTL Press Event May 2003

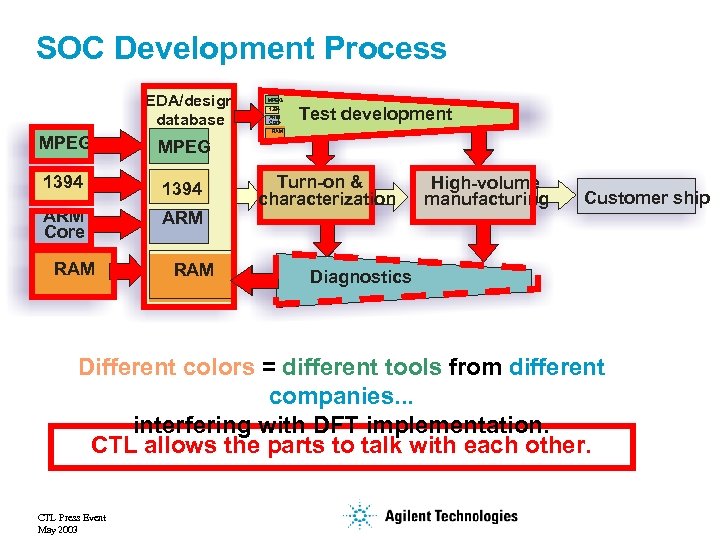

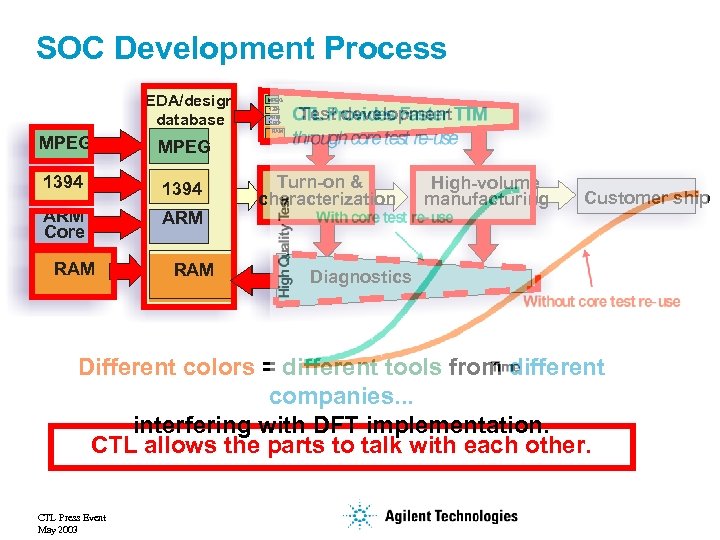

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics Different colors = different tools from different companies. . . interfering with DFT implementation. CTL allows the parts to talk with each other. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics Different colors = different tools from different companies. . . interfering with DFT implementation. CTL allows the parts to talk with each other. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics Different colors = different tools from different companies. . . interfering with DFT implementation. CTL allows the parts to talk with each other. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics Different colors = different tools from different companies. . . interfering with DFT implementation. CTL allows the parts to talk with each other. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics Different colors = different tools from different companies. . . interfering with DFT implementation. CTL allows the parts to talk with each other. CTL Press Event May 2003

SOC Development Process EDA/design database MPEG 1394 ARM Core Test development RAM MPEG 1394 MPEG RAM Turn-on & characterization High-volume manufacturing Customer ship Diagnostics Different colors = different tools from different companies. . . interfering with DFT implementation. CTL allows the parts to talk with each other. CTL Press Event May 2003

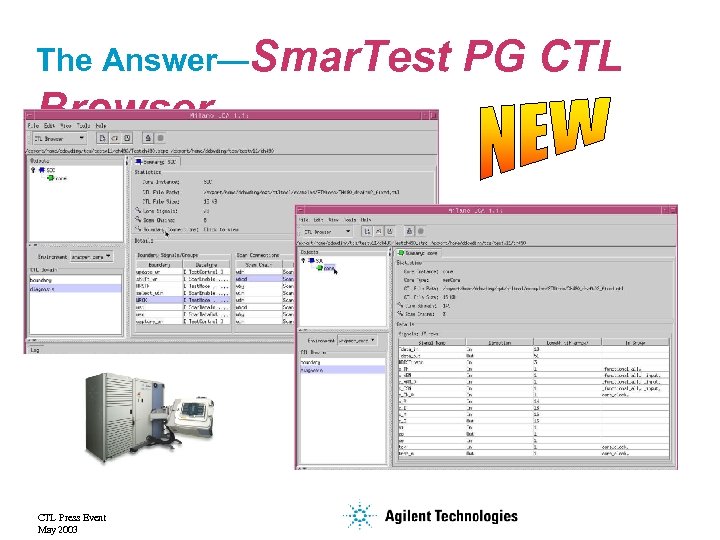

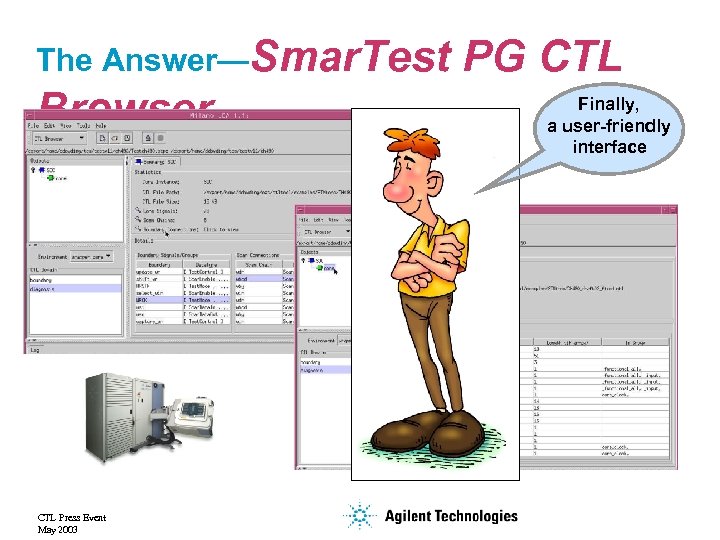

The Answer—Smar. Test Browser CTL Press Event May 2003 PG CTL

The Answer—Smar. Test Browser CTL Press Event May 2003 PG CTL

The Answer—Smar. Test Browser CTL Press Event May 2003 PG CTL Finally, a user-friendly interface

The Answer—Smar. Test Browser CTL Press Event May 2003 PG CTL Finally, a user-friendly interface

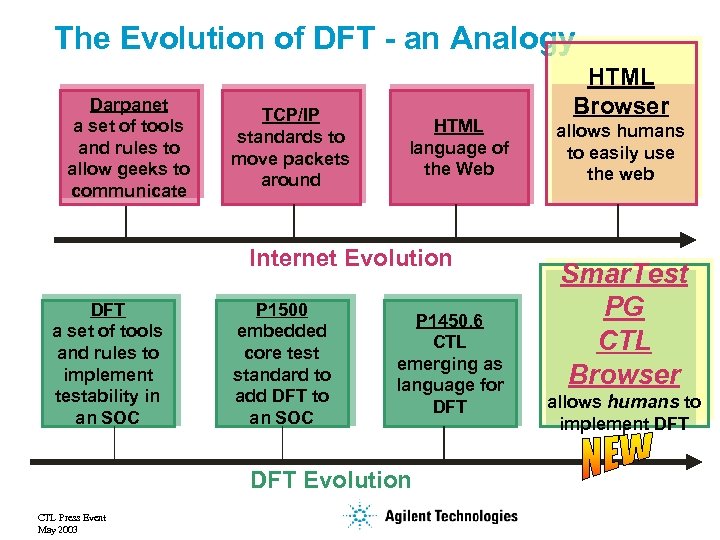

The Evolution of DFT - an Analogy Darpanet a set of tools and rules to allow geeks to communicate TCP/IP standards to move packets around HTML language of the Web Internet Evolution DFT a set of tools and rules to implement testability in an SOC P 1500 embedded core test standard to add DFT to an SOC P 1450. 6 CTL emerging as language for DFT Evolution CTL Press Event May 2003 HTML Browser allows humans to easily use the web Smar. Test PG CTL Browser allows humans to implement DFT

The Evolution of DFT - an Analogy Darpanet a set of tools and rules to allow geeks to communicate TCP/IP standards to move packets around HTML language of the Web Internet Evolution DFT a set of tools and rules to implement testability in an SOC P 1500 embedded core test standard to add DFT to an SOC P 1450. 6 CTL emerging as language for DFT Evolution CTL Press Event May 2003 HTML Browser allows humans to easily use the web Smar. Test PG CTL Browser allows humans to implement DFT

![HTM L Shift { C {si[1]=#; si[0]=#; so[1]=#; } V { si_m 123='d[0. . HTM L Shift { C {si[1]=#; si[0]=#; so[1]=#; } V { si_m 123='d[0. .](https://present5.com/presentation/997873a365b55705d5fac40254691a60/image-13.jpg) HTM L Shift { C {si[1]=#; si[0]=#; so[1]=#; } V { si_m 123='d[0. . 4] si[1] si[0]'; so_m 123='so[1] so[0] q[0. . 2]'; clk=P; WRCK=P; }} V { clk=0; WRCK=0; sc=0; Capture. WR=1; Shift. WR=0; } V { clk=P; WRCK=P; } V { Capture. WR=0; clk=0; WRCK=0; } } } Active. State U; Pattern Pat 1 { M do_intest { d[0. . 4]=00000; si[0]=111000; si[1]=11110000; } M do_intest { so[0]=001 X 11; so[1]=111100 X 1; q[0. . 2]=001; d[0. . 4]=01101; si[0]=011010; si[1]=01011101; } M do_intest { so[0]=1100 X 1; so[1]=10110000; q[0. . 2]=110; d[0. . 4]=11001; si[0]=110010; si[1]=00011100; } M do_intest { so[0]=010001; so[1]=1 X 110100; q[0. . 2]=00 X; d[0. . 4]=01010; si[0]=001101; si[1]=10011101; } M do_intest { d[0. . 4]=00000; si[0]=111000; si[1]=11110000; } M do_intest { so[0]=001 X 11; so[1]=111100 X 1; q[0. . 2]=001; d[0. . 4]=01101; si[0]=011010; si[1]=01011101; } M do_intest { so[0]=1100 X 1; so[1]=10110000; q[0. . 2]=110; d[0. . 4]=11001; si[0]=110010; si[1]=00011100; } M do_intest { so[0]=010001; so[1]=1 X 110100; q[0. . 2]=00 X; CTL Press Event May 2003 The Power of the Browser CTL

HTM L Shift { C {si[1]=#; si[0]=#; so[1]=#; } V { si_m 123='d[0. . 4] si[1] si[0]'; so_m 123='so[1] so[0] q[0. . 2]'; clk=P; WRCK=P; }} V { clk=0; WRCK=0; sc=0; Capture. WR=1; Shift. WR=0; } V { clk=P; WRCK=P; } V { Capture. WR=0; clk=0; WRCK=0; } } } Active. State U; Pattern Pat 1 { M do_intest { d[0. . 4]=00000; si[0]=111000; si[1]=11110000; } M do_intest { so[0]=001 X 11; so[1]=111100 X 1; q[0. . 2]=001; d[0. . 4]=01101; si[0]=011010; si[1]=01011101; } M do_intest { so[0]=1100 X 1; so[1]=10110000; q[0. . 2]=110; d[0. . 4]=11001; si[0]=110010; si[1]=00011100; } M do_intest { so[0]=010001; so[1]=1 X 110100; q[0. . 2]=00 X; d[0. . 4]=01010; si[0]=001101; si[1]=10011101; } M do_intest { d[0. . 4]=00000; si[0]=111000; si[1]=11110000; } M do_intest { so[0]=001 X 11; so[1]=111100 X 1; q[0. . 2]=001; d[0. . 4]=01101; si[0]=011010; si[1]=01011101; } M do_intest { so[0]=1100 X 1; so[1]=10110000; q[0. . 2]=110; d[0. . 4]=11001; si[0]=110010; si[1]=00011100; } M do_intest { so[0]=010001; so[1]=1 X 110100; q[0. . 2]=00 X; CTL Press Event May 2003 The Power of the Browser CTL

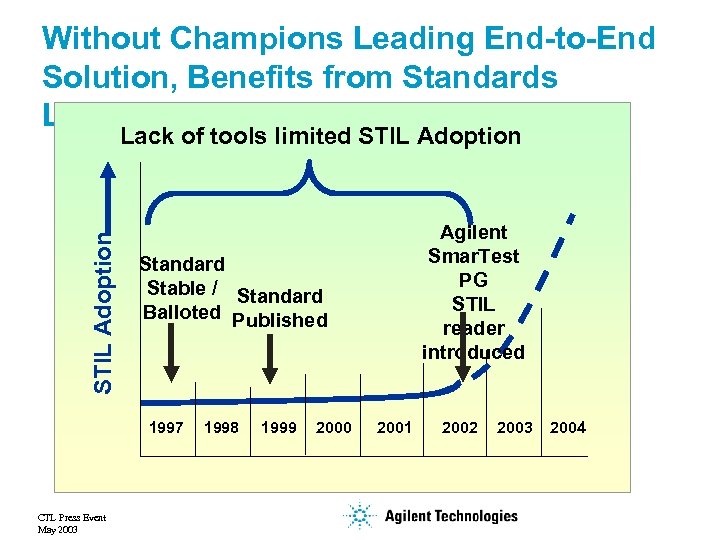

Without Champions Leading End-to-End Solution, Benefits from Standards Languish STIL Adoption Lack of tools limited STIL Adoption Standard Stable / Standard Balloted Published 1997 CTL Press Event May 2003 Agilent Smar. Test PG STIL reader introduced 1998 1999 2000 2001 2002 2003 2004

Without Champions Leading End-to-End Solution, Benefits from Standards Languish STIL Adoption Lack of tools limited STIL Adoption Standard Stable / Standard Balloted Published 1997 CTL Press Event May 2003 Agilent Smar. Test PG STIL reader introduced 1998 1999 2000 2001 2002 2003 2004

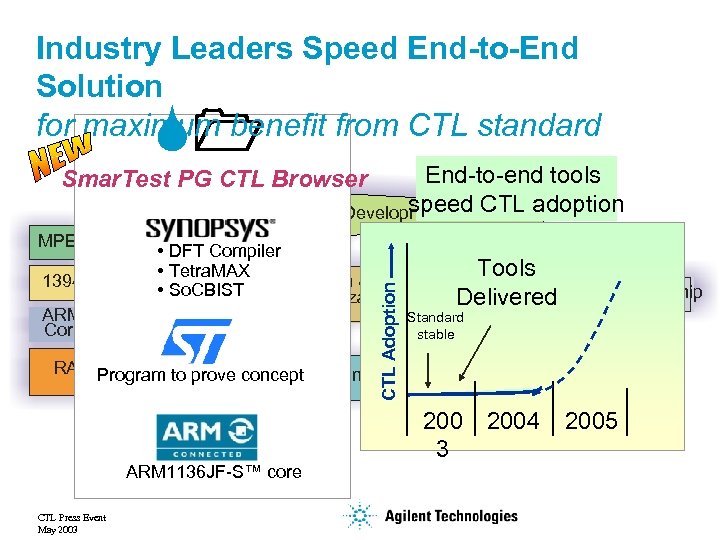

Industry Leaders Speed End-to-End Solution for maximum benefit from CTL standard S 1 End-to-end tools speed CTL adoption Test Development Smar. Test PG CTL Browser EDA/Design Database 1394 ARM Core RAM MPEG • DFT Compiler • Tetra. MAX Turn-On & • 1394 So. CBIST Characterization ARM Core CTL Adoption MPEG Tools High-Volume Manufacturing Delivered Customer Ship Standard stable RAM Program to prove concept Diagnostics RAM ARM 1136 JF-S™ core CTL Press Event May 2003 2004 3 2005

Industry Leaders Speed End-to-End Solution for maximum benefit from CTL standard S 1 End-to-end tools speed CTL adoption Test Development Smar. Test PG CTL Browser EDA/Design Database 1394 ARM Core RAM MPEG • DFT Compiler • Tetra. MAX Turn-On & • 1394 So. CBIST Characterization ARM Core CTL Adoption MPEG Tools High-Volume Manufacturing Delivered Customer Ship Standard stable RAM Program to prove concept Diagnostics RAM ARM 1136 JF-S™ core CTL Press Event May 2003 2004 3 2005

CTL Press Event May 2003

CTL Press Event May 2003

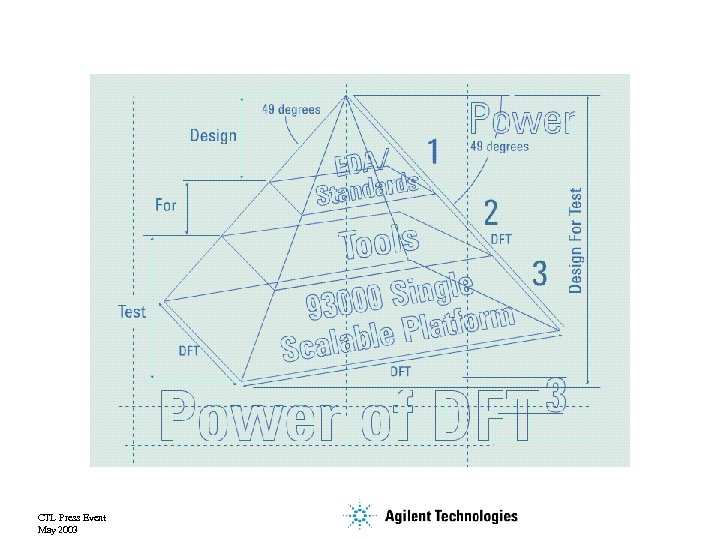

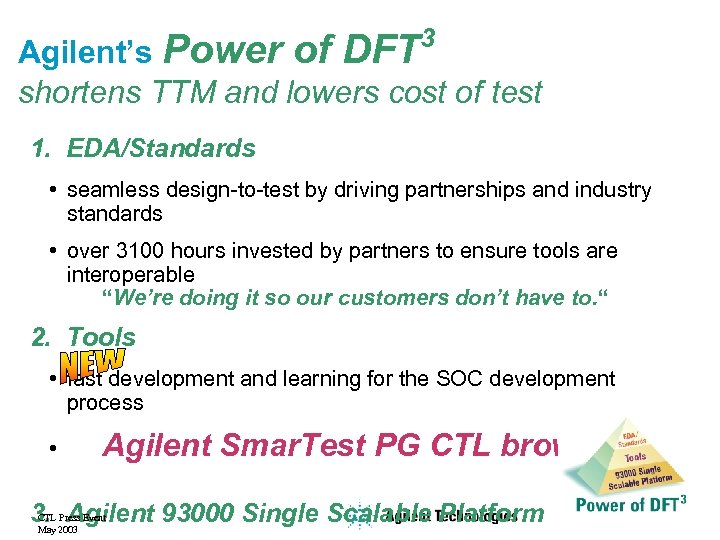

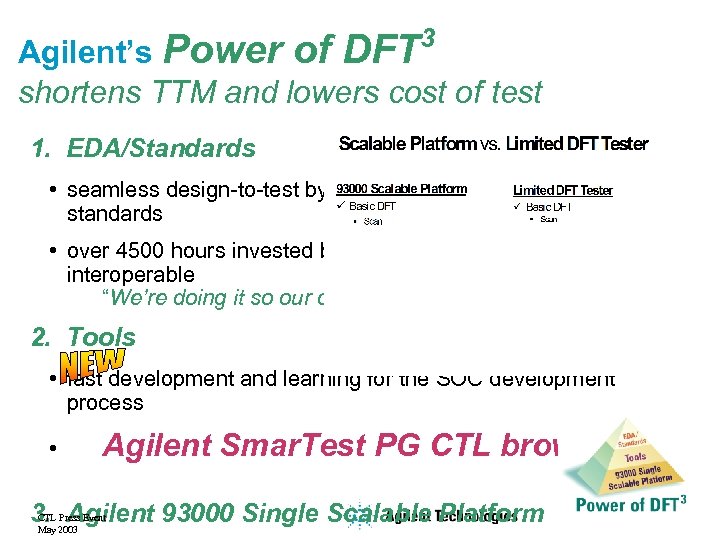

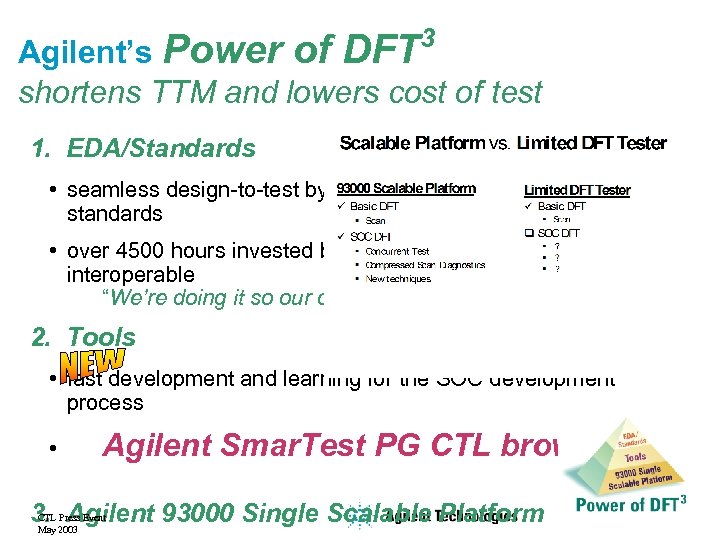

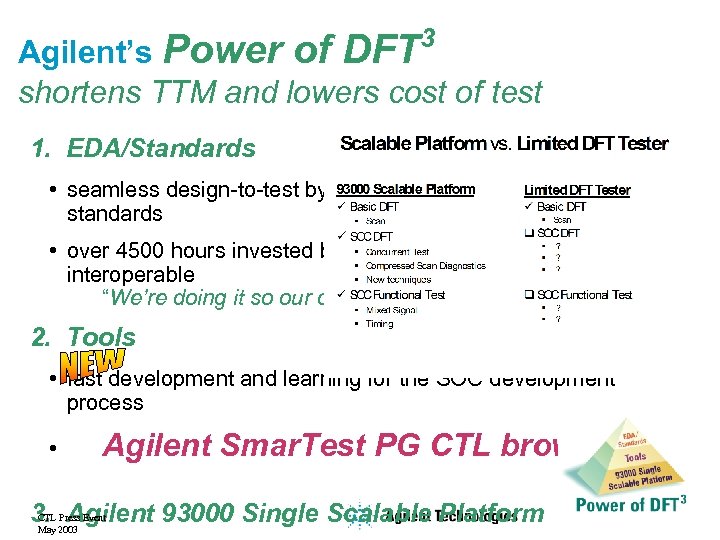

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 3100 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 3100 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 4500 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 4500 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 4500 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 4500 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 4500 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

3 Agilent’s Power of DFT shortens TTM and lowers cost of test 1. EDA/Standards • seamless design-to-test by driving partnerships and industry standards • over 4500 hours invested by partners to ensure tools are interoperable “We’re doing it so our customers don’t have to. “ 2. Tools • fast development and learning for the SOC development process • Agilent Smar. Test PG CTL browser 3. Agilent 93000 Single Scalable Platform CTL Press Event May 2003

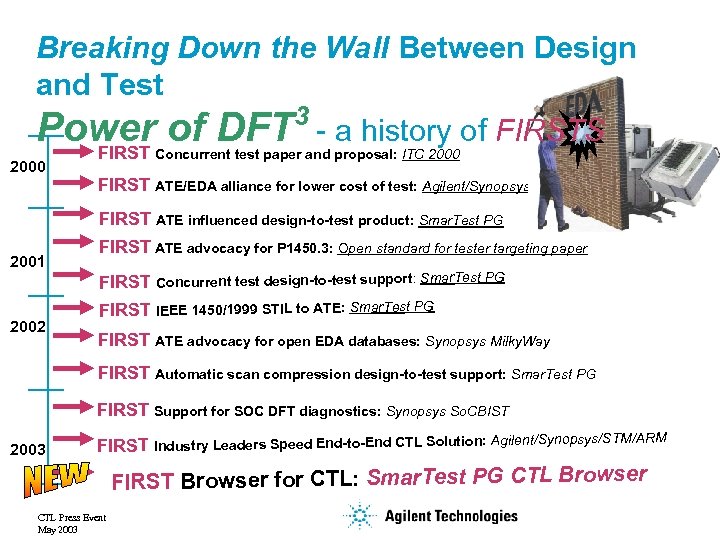

Breaking Down the Wall Between Design and Test 3 Power of DFT - a history of FIRSTS 2000 FIRST Concurrent test paper and proposal: ITC 2000 FIRST ATE/EDA alliance for lower cost of test: Agilent/Synopsys FIRST ATE influenced design-to-test product: Smar. Test PG 2001 2002 FIRST ATE advocacy for P 1450. 3: Open standard for tester targeting paper FIRST Concurrent test design-to-test support: Smar. Test PG FIRST IEEE 1450/1999 STIL to ATE: Smar. Test PG FIRST ATE advocacy for open EDA databases: Synopsys Milky. Way FIRST Automatic scan compression design-to-test support: Smar. Test PG FIRST Support for SOC DFT diagnostics: Synopsys So. CBIST 2003 M/ARM FIRST Industry Leaders Speed End-to-End CTL Solution: Agilent/Synopsys/ST FIRST Browser for CTL: Smar. Test PG CTL Browser CTL Press Event May 2003

Breaking Down the Wall Between Design and Test 3 Power of DFT - a history of FIRSTS 2000 FIRST Concurrent test paper and proposal: ITC 2000 FIRST ATE/EDA alliance for lower cost of test: Agilent/Synopsys FIRST ATE influenced design-to-test product: Smar. Test PG 2001 2002 FIRST ATE advocacy for P 1450. 3: Open standard for tester targeting paper FIRST Concurrent test design-to-test support: Smar. Test PG FIRST IEEE 1450/1999 STIL to ATE: Smar. Test PG FIRST ATE advocacy for open EDA databases: Synopsys Milky. Way FIRST Automatic scan compression design-to-test support: Smar. Test PG FIRST Support for SOC DFT diagnostics: Synopsys So. CBIST 2003 M/ARM FIRST Industry Leaders Speed End-to-End CTL Solution: Agilent/Synopsys/ST FIRST Browser for CTL: Smar. Test PG CTL Browser CTL Press Event May 2003

Power of DFT 3 shortens TTM and lowers cost of test 1. EDA/Standards • Agilent will make CTL the language of DFT 2. Tools Smar. Test PG CTL Browser See demo of complete SOC development process Semicon West Booth #10516 3. Agilent 93000 Single Scalable Platform • DFT solution available TODAY! New announcements & demo planned for Semicon West CTL Press Event May 2003

Power of DFT 3 shortens TTM and lowers cost of test 1. EDA/Standards • Agilent will make CTL the language of DFT 2. Tools Smar. Test PG CTL Browser See demo of complete SOC development process Semicon West Booth #10516 3. Agilent 93000 Single Scalable Platform • DFT solution available TODAY! New announcements & demo planned for Semicon West CTL Press Event May 2003

Visit Agilent at Semicon West Booth # 10516 • Talk to industry CTL experts • Hear real customer stories • Meet with Agilent IEEE committee members • See LIVE demonstrations: • Power of DFT 3 solution in process TODAY!! - meet w/Agilent partners and customers - see SOC DFT process demo at Semicon West • Smar. Test CTL Browser announced TODAY!! - see live demo at Semicon West • Agilent 93000 DFT solution available TODAY !! - new announcements at Semicon West CTL Press Event May 2003

Visit Agilent at Semicon West Booth # 10516 • Talk to industry CTL experts • Hear real customer stories • Meet with Agilent IEEE committee members • See LIVE demonstrations: • Power of DFT 3 solution in process TODAY!! - meet w/Agilent partners and customers - see SOC DFT process demo at Semicon West • Smar. Test CTL Browser announced TODAY!! - see live demo at Semicon West • Agilent 93000 DFT solution available TODAY !! - new announcements at Semicon West CTL Press Event May 2003

CTL Press Event May 2003

CTL Press Event May 2003

Appendix CTL Press Event May 2003

Appendix CTL Press Event May 2003

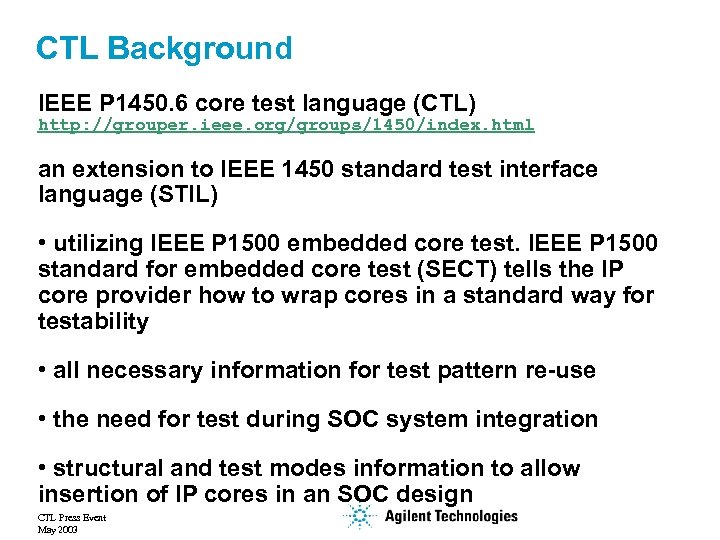

CTL Background IEEE P 1450. 6 core test language (CTL) http: //grouper. ieee. org/groups/1450/index. html an extension to IEEE 1450 standard test interface language (STIL) • utilizing IEEE P 1500 embedded core test. IEEE P 1500 standard for embedded core test (SECT) tells the IP core provider how to wrap cores in a standard way for testability • all necessary information for test pattern re-use • the need for test during SOC system integration • structural and test modes information to allow insertion of IP cores in an SOC design CTL Press Event May 2003

CTL Background IEEE P 1450. 6 core test language (CTL) http: //grouper. ieee. org/groups/1450/index. html an extension to IEEE 1450 standard test interface language (STIL) • utilizing IEEE P 1500 embedded core test. IEEE P 1500 standard for embedded core test (SECT) tells the IP core provider how to wrap cores in a standard way for testability • all necessary information for test pattern re-use • the need for test during SOC system integration • structural and test modes information to allow insertion of IP cores in an SOC design CTL Press Event May 2003

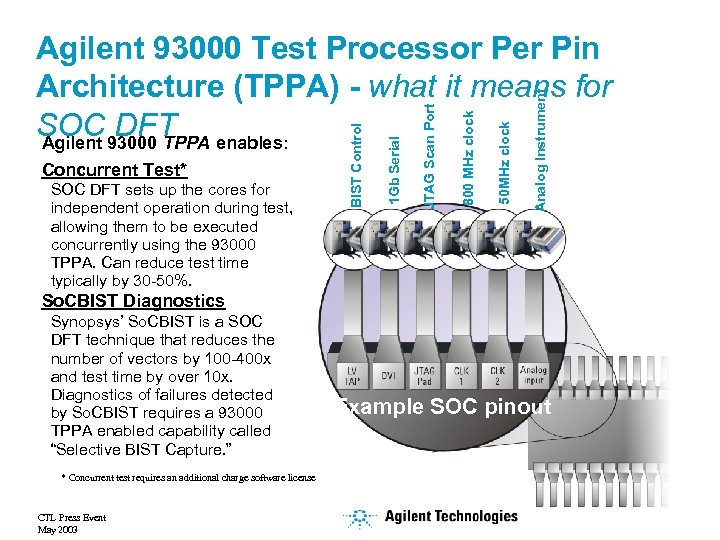

Analog Instrument 50 MHz clock 800 MHz clock JTAG Scan Port SOC DFT sets up the cores for independent operation during test, allowing them to be executed concurrently using the 93000 TPPA. Can reduce test time typically by 30 -50%. 1 Gb Serial Concurrent Test* BIST Control Agilent 93000 Test Processor Per Pin Architecture (TPPA) - what it means for SOC 93000 TPPA enables: DFT Agilent So. CBIST Diagnostics Synopsys’ So. CBIST is a SOC DFT technique that reduces the number of vectors by 100 -400 x and test time by over 10 x. Diagnostics of failures detected by So. CBIST requires a 93000 TPPA enabled capability called “Selective BIST Capture. ” * Concurrent test requires an additional charge software license CTL Press Event May 2003 Example SOC pinout

Analog Instrument 50 MHz clock 800 MHz clock JTAG Scan Port SOC DFT sets up the cores for independent operation during test, allowing them to be executed concurrently using the 93000 TPPA. Can reduce test time typically by 30 -50%. 1 Gb Serial Concurrent Test* BIST Control Agilent 93000 Test Processor Per Pin Architecture (TPPA) - what it means for SOC 93000 TPPA enables: DFT Agilent So. CBIST Diagnostics Synopsys’ So. CBIST is a SOC DFT technique that reduces the number of vectors by 100 -400 x and test time by over 10 x. Diagnostics of failures detected by So. CBIST requires a 93000 TPPA enabled capability called “Selective BIST Capture. ” * Concurrent test requires an additional charge software license CTL Press Event May 2003 Example SOC pinout