57bf9a1648d1cc71ac43aa2843bdcb37.ppt

- Количество слайдов: 34

Advances in 3 D Bob Patti, CTO rpatti@tezzaron. com Tezzaron Semiconductor 03/18/10 1

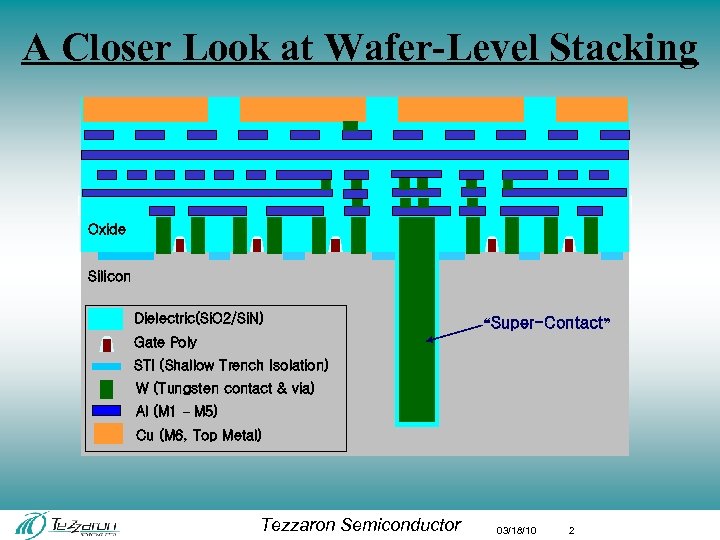

A Closer Look at Wafer-Level Stacking Oxide Silicon Dielectric(Si. O 2/Si. N) “Super-Contact” Gate Poly STI (Shallow Trench Isolation) W (Tungsten contact & via) Al (M 1 – M 5) Cu (M 6, Top Metal) Tezzaron Semiconductor 03/18/10 2

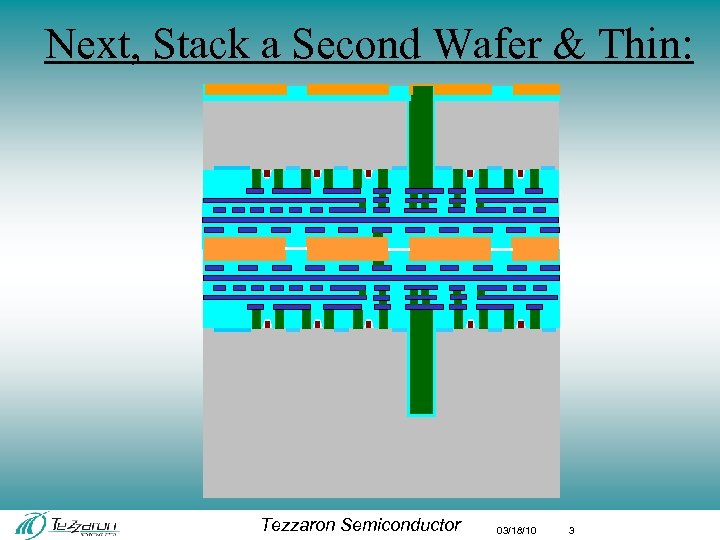

Next, Stack a Second Wafer & Thin: Tezzaron Semiconductor 03/18/10 3

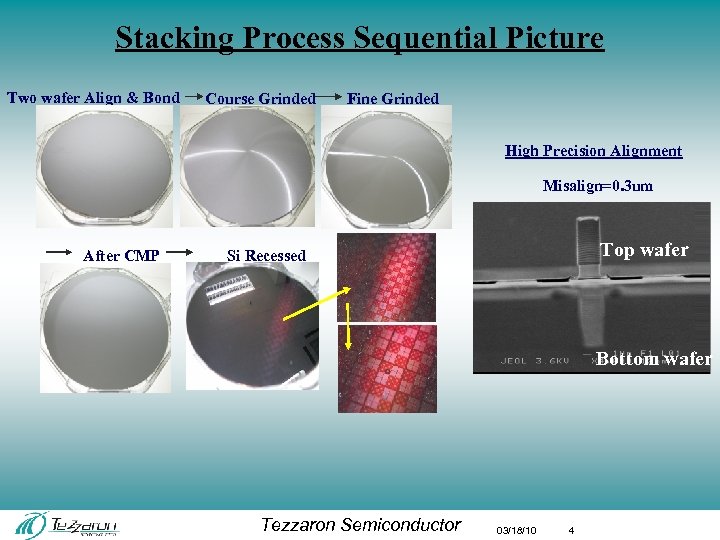

Stacking Process Sequential Picture Two wafer Align & Bond Course Grinded Fine Grinded High Precision Alignment Misalign=0. 3 um After CMP Top wafer Si Recessed Bottom wafer Tezzaron Semiconductor 03/18/10 4

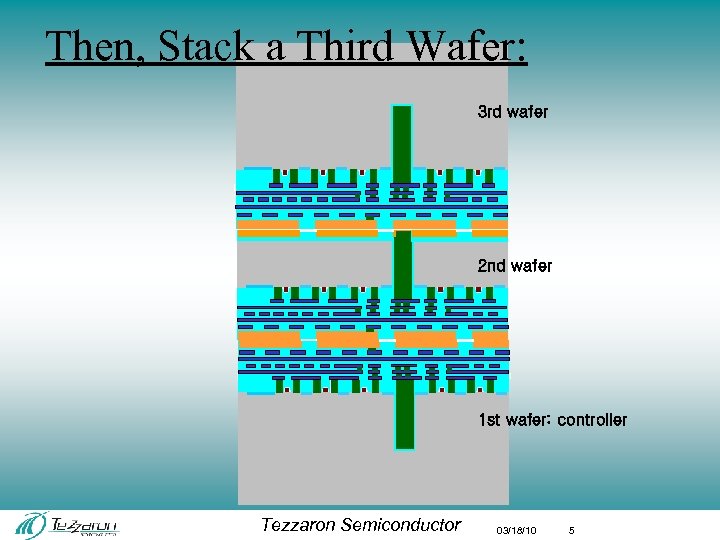

Then, Stack a Third Wafer: 3 rd wafer 2 nd wafer 1 st wafer: controller Tezzaron Semiconductor 03/18/10 5

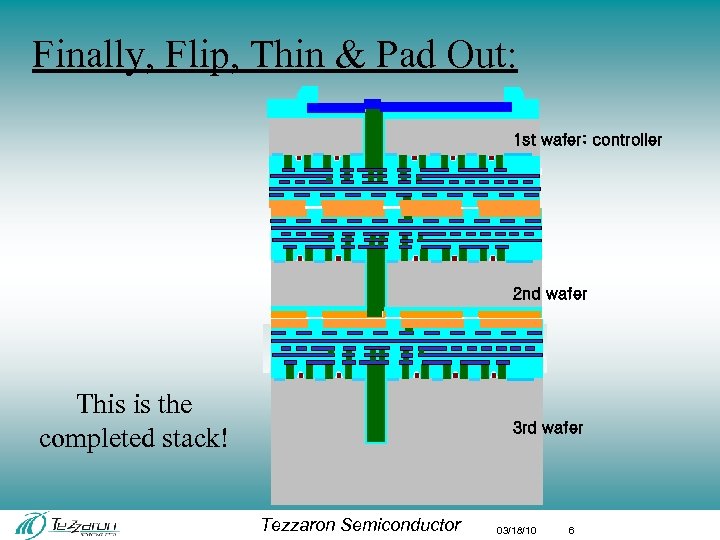

Finally, Flip, Thin & Pad Out: 1 st wafer: controller 2 nd wafer This is the completed stack! 3 rd wafer Tezzaron Semiconductor 03/18/10 6

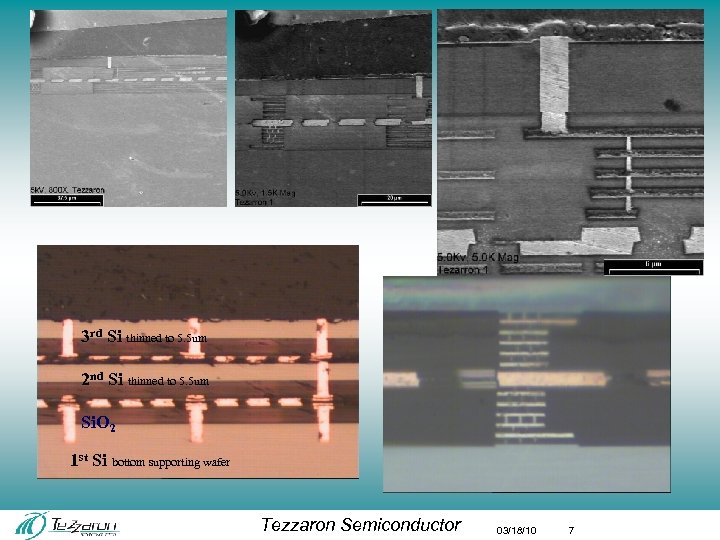

3 rd Si thinned to 5. 5 um 2 nd Si thinned to 5. 5 um Si. O 2 1 st Si bottom supporting wafer Tezzaron Semiconductor 03/18/10 7

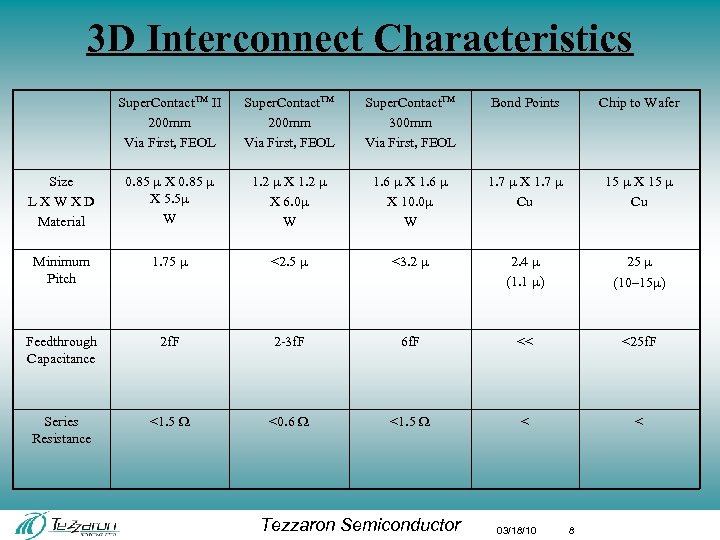

3 D Interconnect Characteristics Super. Contact. TM II 200 mm Via First, FEOL Super. Contact. TM 300 mm Via First, FEOL Bond Points Chip to Wafer Size LXWXD Material 0. 85 X 5. 5 W 1. 2 X 6. 0 W 1. 6 X 10. 0 W 1. 7 X 1. 7 Cu 15 X 15 Cu Minimum Pitch 1. 75 <2. 5 <3. 2 2. 4 (1. 1 ) 25 (10 -15 ) Feedthrough Capacitance 2 f. F 2 -3 f. F 6 f. F << <25 f. F Series Resistance <1. 5 W <0. 6 W <1. 5 W < < Tezzaron Semiconductor 03/18/10 8

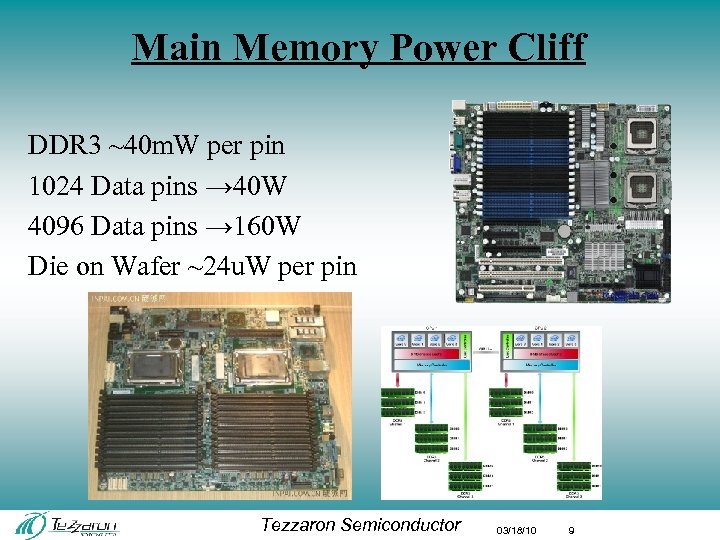

Main Memory Power Cliff DDR 3 ~40 m. W per pin 1024 Data pins → 40 W 4096 Data pins → 160 W Die on Wafer ~24 u. W per pin Tezzaron Semiconductor 03/18/10 9

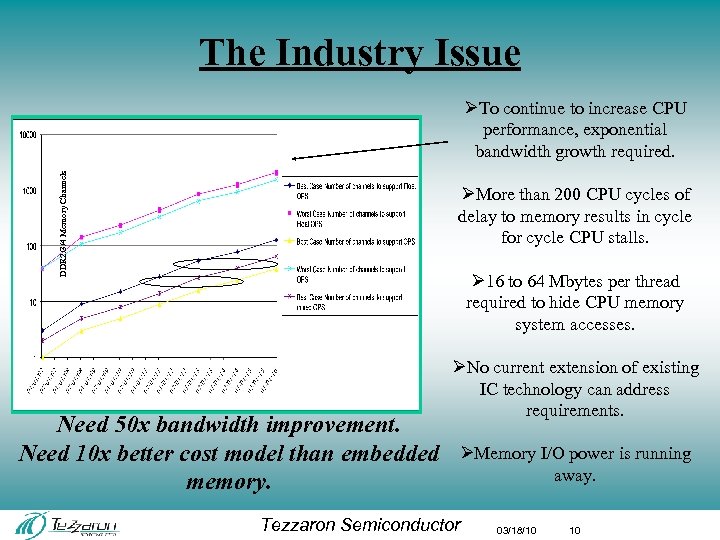

The Industry Issue DDR 2/3/4 Memory Channels ØTo continue to increase CPU performance, exponential bandwidth growth required. ØMore than 200 CPU cycles of delay to memory results in cycle for cycle CPU stalls. Ø 16 to 64 Mbytes per thread required to hide CPU memory system accesses. Need 50 x bandwidth improvement. Need 10 x better cost model than embedded memory. ØNo current extension of existing IC technology can address requirements. ØMemory I/O power is running away. Tezzaron Semiconductor 03/18/10 10

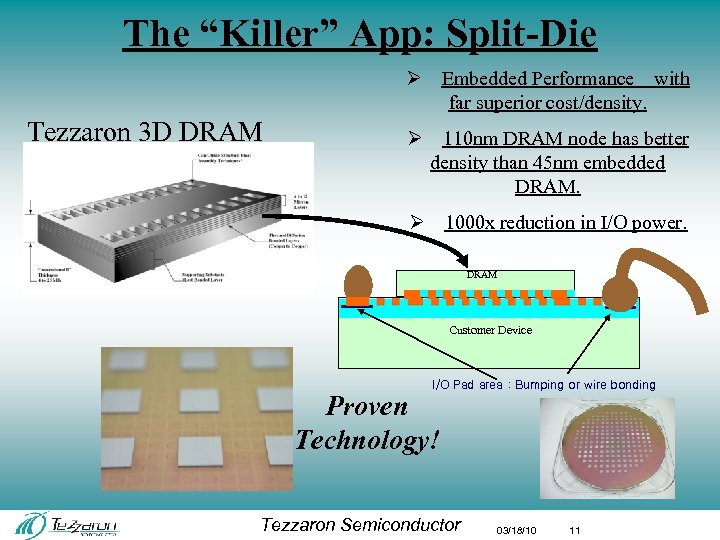

The “Killer” App: Split-Die Ø Embedded Performance with far superior cost/density. Tezzaron 3 D DRAM Ø 110 nm DRAM node has better density than 45 nm embedded DRAM. Ø 1000 x reduction in I/O power. DRAM Customer Device I/O Pad area : Bumping or wire bonding Proven Technology! Tezzaron Semiconductor 03/18/10 11

Coming Soon… Tezzaron Semiconductor 03/18/10 12

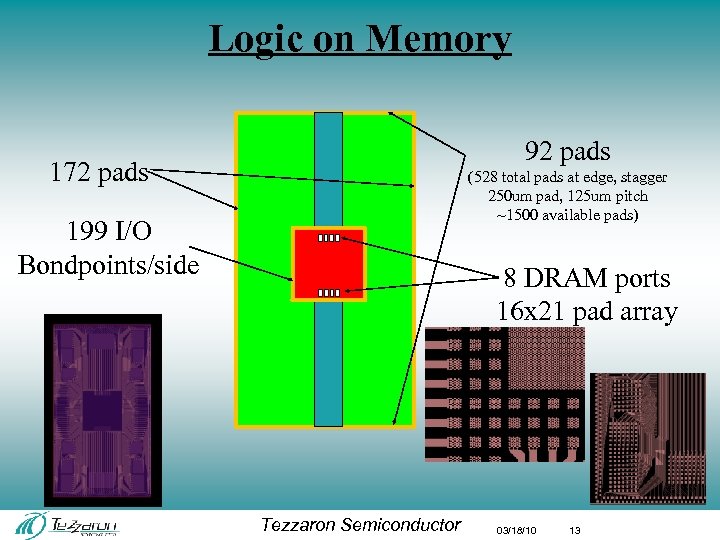

Logic on Memory 92 pads 172 pads (528 total pads at edge, stagger 250 um pad, 125 um pitch ~1500 available pads) 199 I/O Bondpoints/side 8 DRAM ports 16 x 21 pad array Tezzaron Semiconductor 03/18/10 13

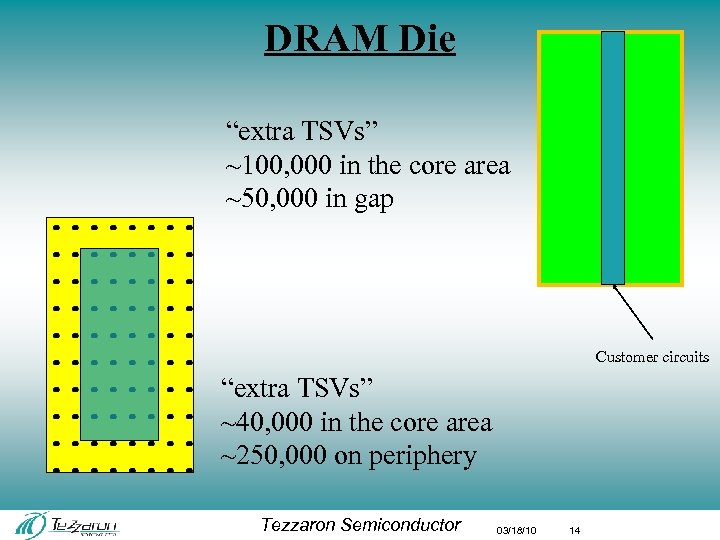

DRAM Die “extra TSVs” ~100, 000 in the core area ~50, 000 in gap Customer circuits “extra TSVs” ~40, 000 in the core area ~250, 000 on periphery Tezzaron Semiconductor 03/18/10 14

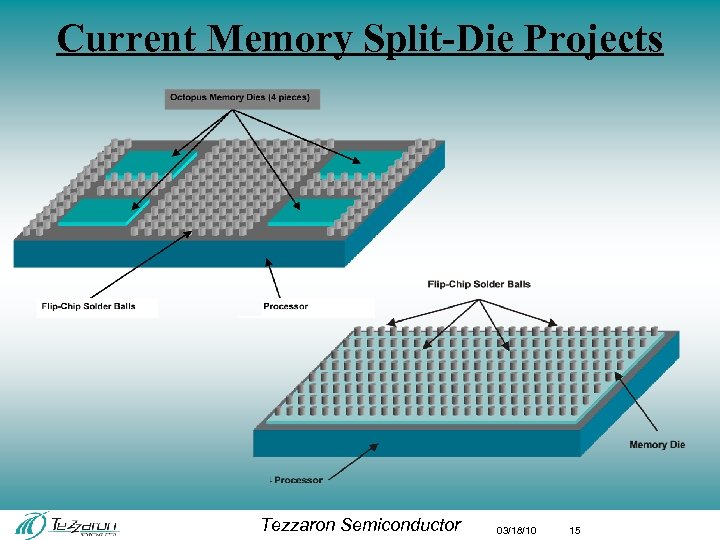

Current Memory Split-Die Projects Tezzaron Semiconductor 03/18/10 15

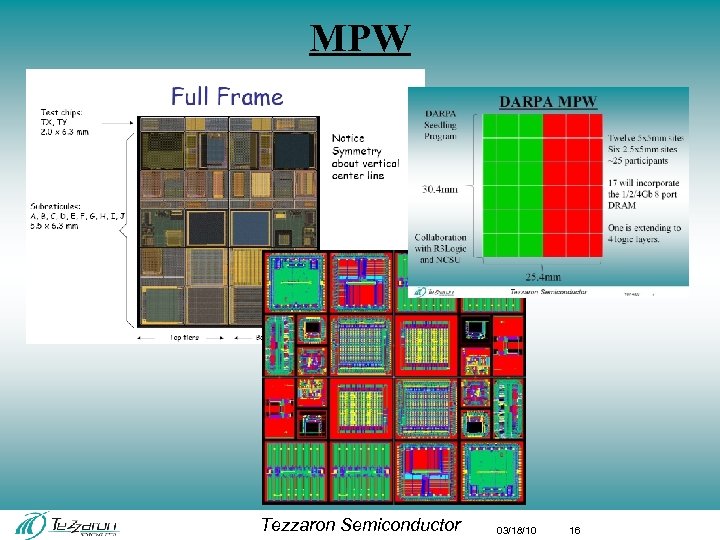

MPW Tezzaron Semiconductor 03/18/10 16

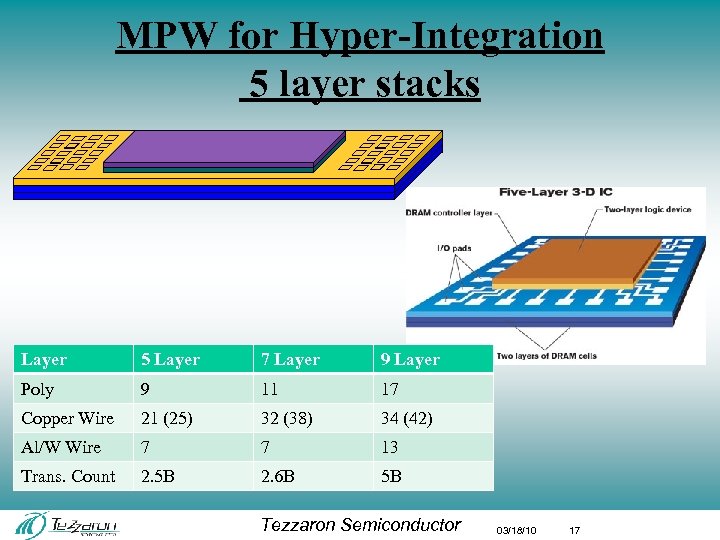

MPW for Hyper-Integration 5 layer stacks Layer 5 Layer 7 Layer 9 Layer Poly 9 11 17 Copper Wire 21 (25) 32 (38) 34 (42) Al/W Wire 7 7 13 Trans. Count 2. 5 B 2. 6 B 5 B Tezzaron Semiconductor 03/18/10 17

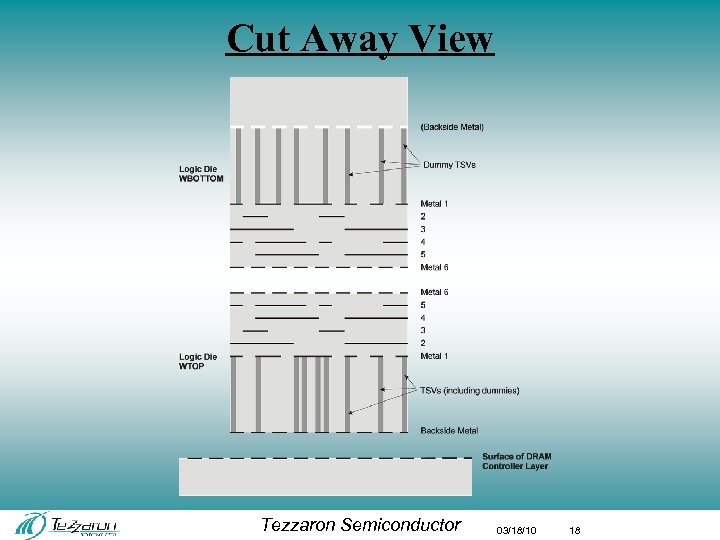

Cut Away View Tezzaron Semiconductor 03/18/10 18

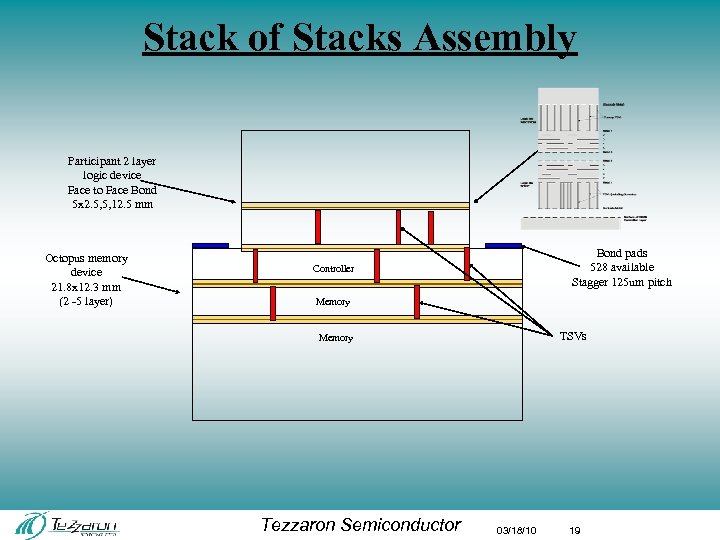

Stack of Stacks Assembly Participant 2 layer logic device Face to Face Bond 5 x 2. 5, 5, 12. 5 mm Octopus memory device 21. 8 x 12. 3 mm (2 -5 layer) Bond pads 528 available Stagger 125 um pitch Controller Memory TSVs Memory Tezzaron Semiconductor 03/18/10 19

Si. CB Design Targets Tezzaron Semiconductor 03/18/10

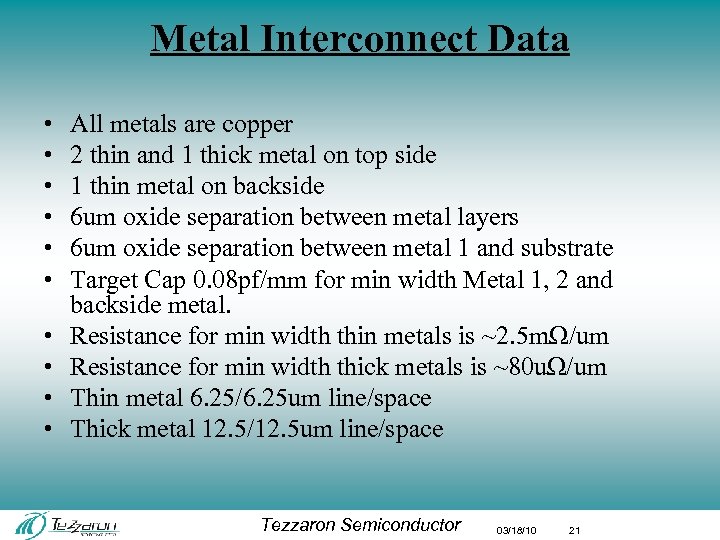

Metal Interconnect Data • • • All metals are copper 2 thin and 1 thick metal on top side 1 thin metal on backside 6 um oxide separation between metal layers 6 um oxide separation between metal 1 and substrate Target Cap 0. 08 pf/mm for min width Metal 1, 2 and backside metal. Resistance for min width thin metals is ~2. 5 mΩ/um Resistance for min width thick metals is ~80 uΩ/um Thin metal 6. 25/6. 25 um line/space Thick metal 12. 5/12. 5 um line/space Tezzaron Semiconductor 03/18/10 21

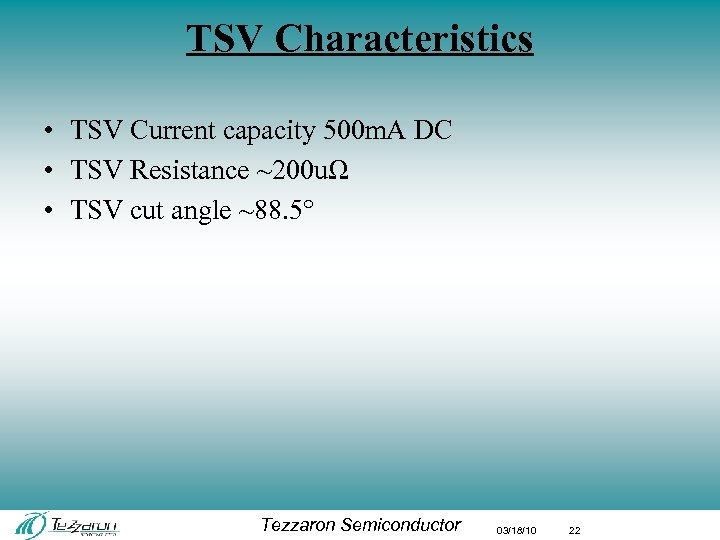

TSV Characteristics • TSV Current capacity 500 m. A DC • TSV Resistance ~200 uΩ • TSV cut angle ~88. 5° Tezzaron Semiconductor 03/18/10 22

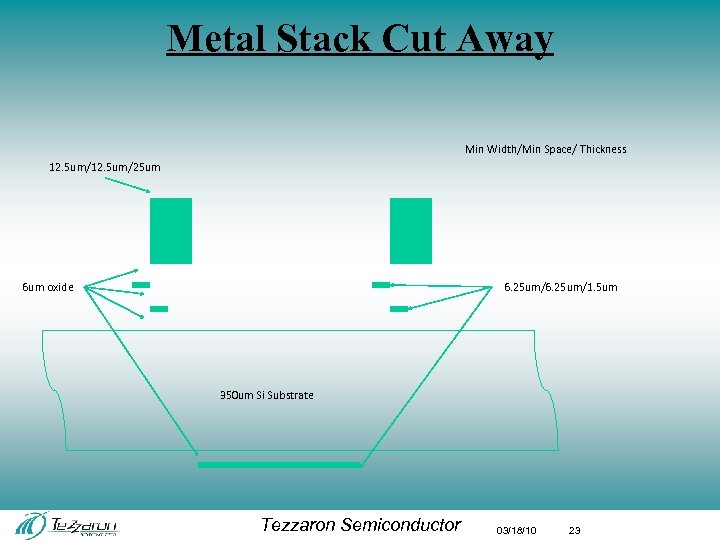

Metal Stack Cut Away Min Width/Min Space/ Thickness 12. 5 um/25 um 6 um oxide 6. 25 um/1. 5 um 350 um Si Substrate Tezzaron Semiconductor 03/18/10 23

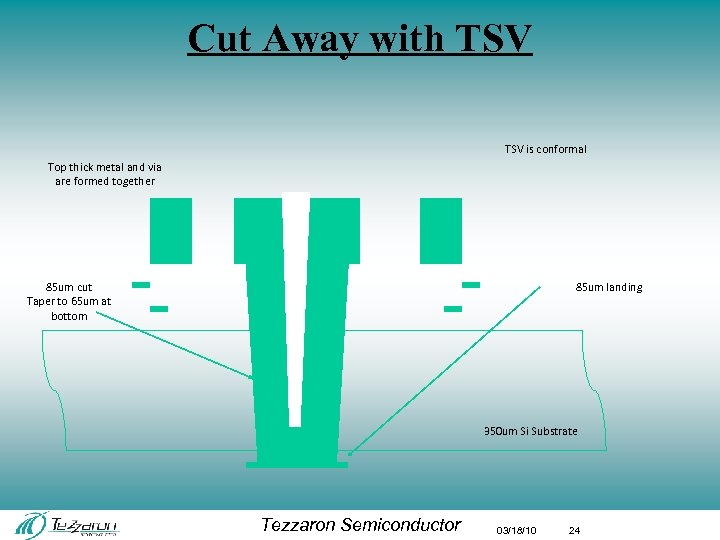

Cut Away with TSV is conformal Top thick metal and via are formed together 85 um cut Taper to 65 um at bottom 85 um landing 350 um Si Substrate Tezzaron Semiconductor 03/18/10 24

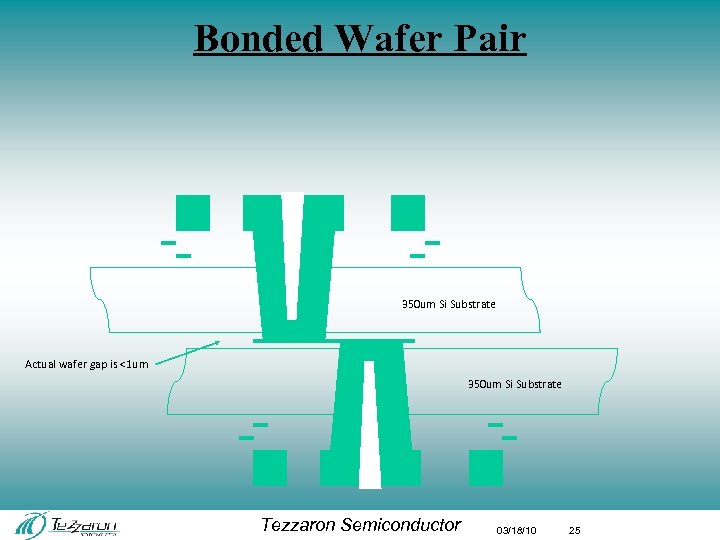

Bonded Wafer Pair 350 um Si Substrate Actual wafer gap is <1 um 350 um Si Substrate Tezzaron Semiconductor 03/18/10 25

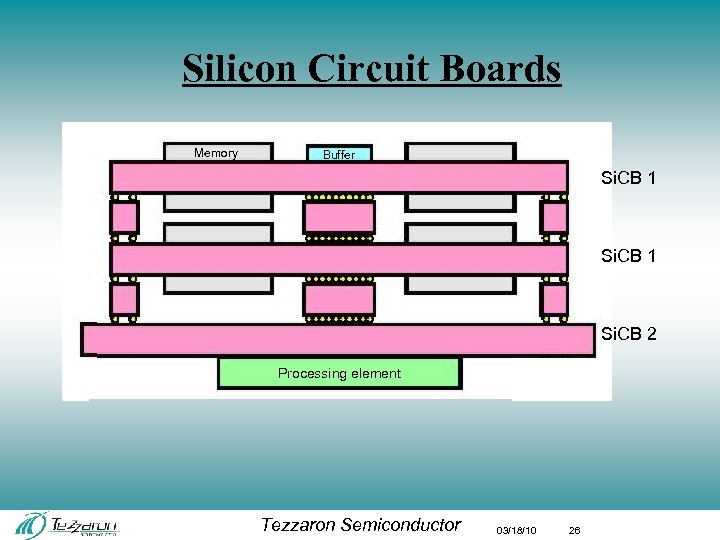

Silicon Circuit Boards Memory Buffer Si. CB 1 Si. CB 2 Processing element Tezzaron Semiconductor 03/18/10 26

DRC, LVS, Transistor synthesis, Crossprobing. Multiple tapeouts, 0. 35 um-45 nm >20 GB, ~10 B devices Tezzaron Semiconductor 03/18/10 27

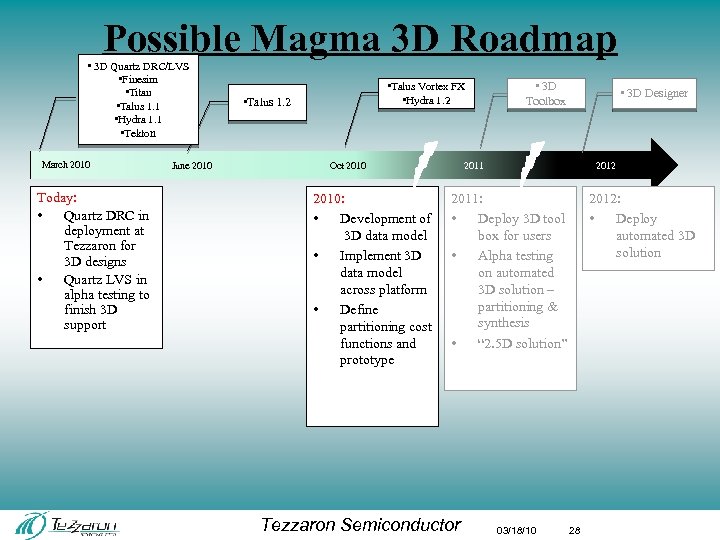

Possible Magma 3 D Roadmap • 3 D Quartz DRC/LVS • Finesim • Titan • Talus 1. 1 • Hydra 1. 1 • Tekton March 2010 Today: • Quartz DRC in deployment at Tezzaron for 3 D designs • Quartz LVS in alpha testing to finish 3 D support • Talus Vortex FX • Hydra 1. 2 • Talus 1. 2 June 2010 Oct 2010: • Development of 3 D data model • Implement 3 D data model across platform • Define partitioning cost functions and prototype • 3 D Toolbox • 3 D Designer 2011 2012 2011: • Deploy 3 D tool box for users • Alpha testing on automated 3 D solution – partitioning & synthesis • “ 2. 5 D solution” Tezzaron Semiconductor 03/18/10 2012: • Deploy automated 3 D solution 28

3 D Issues • Highly complex supply chain – 2 chips, 6 designs, 5 fabs, 6 mask sets – ETS/ Alignment keys • New design issues – 2. 3 M ports for LVS • Material information exchange • 3 D construction information – Orientation, notch location – Front view, back view, fab view, wafer view Tezzaron Semiconductor 03/18/10 29

Industry Trends • Cu, Ni, W TSVs – Lots of Cu activity • Who does the 3 D assembly? • Big test concerns • Tools are coming on line – Magma – Synopsis Tezzaron Semiconductor 03/18/10 30

Commercialization • Now – CMOS Sensors (1/2 Layer) • Near term – Memory (2/4/8 Layer) – Logic/memory combo • Next 2 -3 years – Mixed signal/logic – Smart(er) Power • 5 years – Logic/Logic Tezzaron Semiconductor 03/18/10 31

Other Developments • • • 9 metal layers Backside inductors Backside metal alignment now 0. 5 um 300 mm by year end White light frontside to frontside alignment First SVTC processed Al test wafers out of fab 3/17/10 – Copper due out 3/19/10 • Improved chip to wafer work on going – 3 -5 um target alignment Tezzaron Semiconductor 03/18/10 32

Other Developments • • • 28 3 D devices completed or in fab 20 more devices will go into fab in April SOI with 0. 35 um TSVs in review Transition TSVs to “normal” process Customer 4 layer logic going into fab in April – Then it will be chip to wafer stacked Tezzaron Semiconductor 03/18/10 33

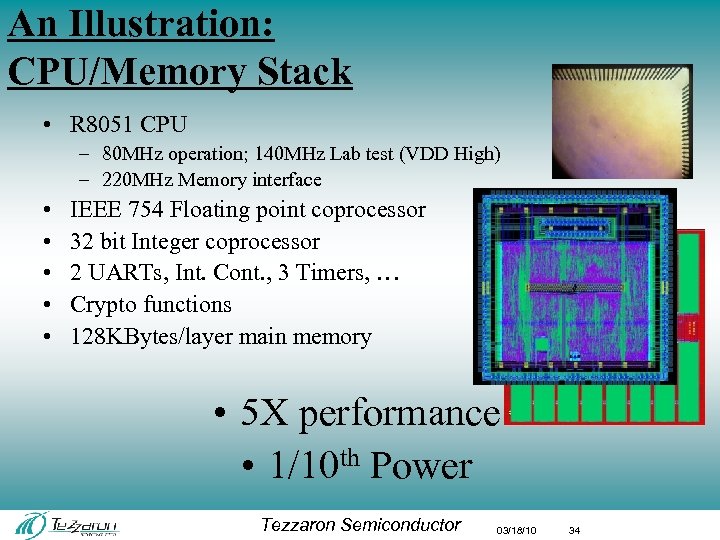

An Illustration: CPU/Memory Stack • R 8051 CPU – 80 MHz operation; 140 MHz Lab test (VDD High) – 220 MHz Memory interface • • • IEEE 754 Floating point coprocessor 32 bit Integer coprocessor 2 UARTs, Int. Cont. , 3 Timers, … Crypto functions 128 KBytes/layer main memory • 5 X performance • 1/10 th Power Tezzaron Semiconductor 03/18/10 34

57bf9a1648d1cc71ac43aa2843bdcb37.ppt