65ad76ca21dc78610417986e463f3e58.ppt

- Количество слайдов: 99

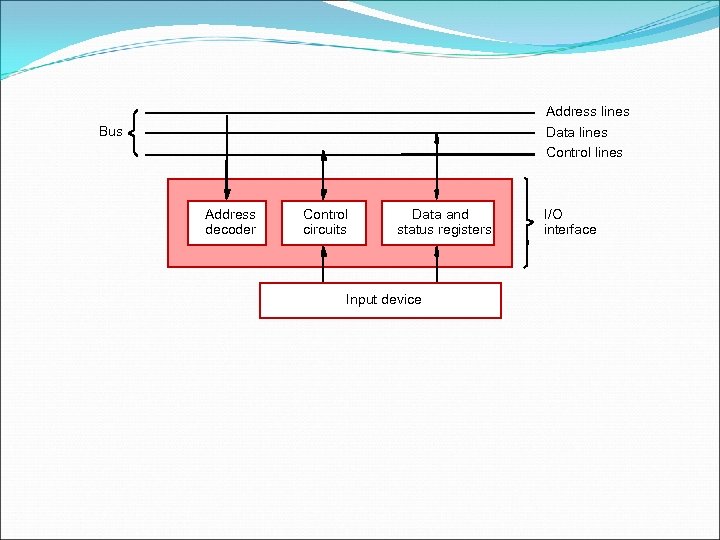

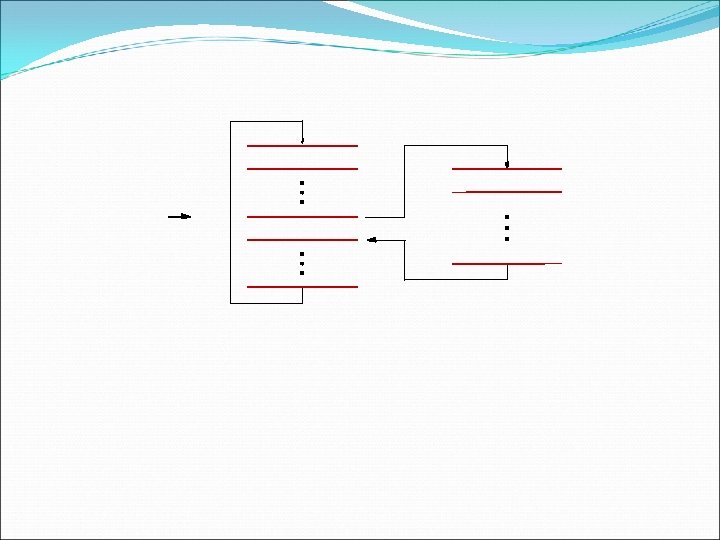

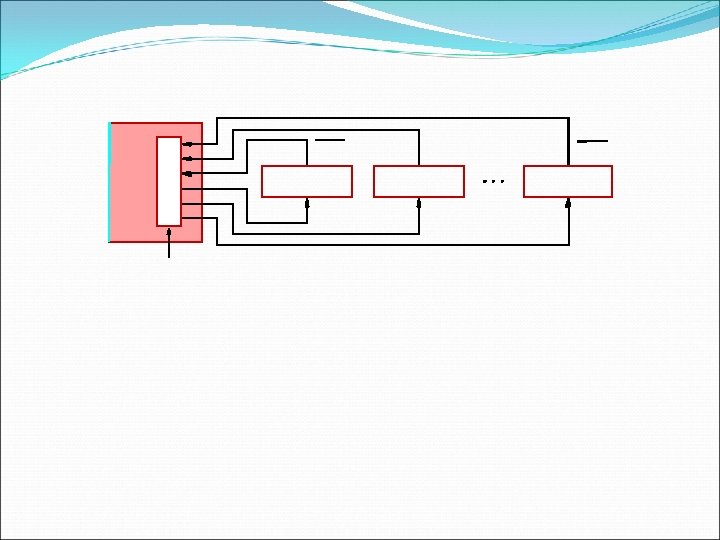

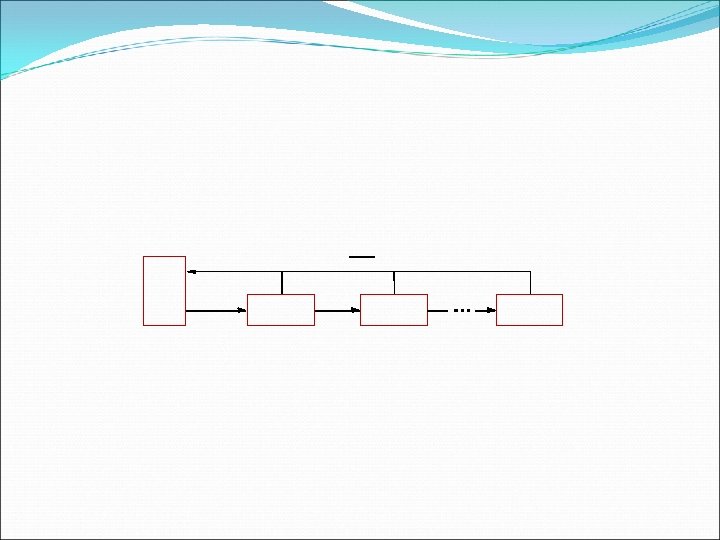

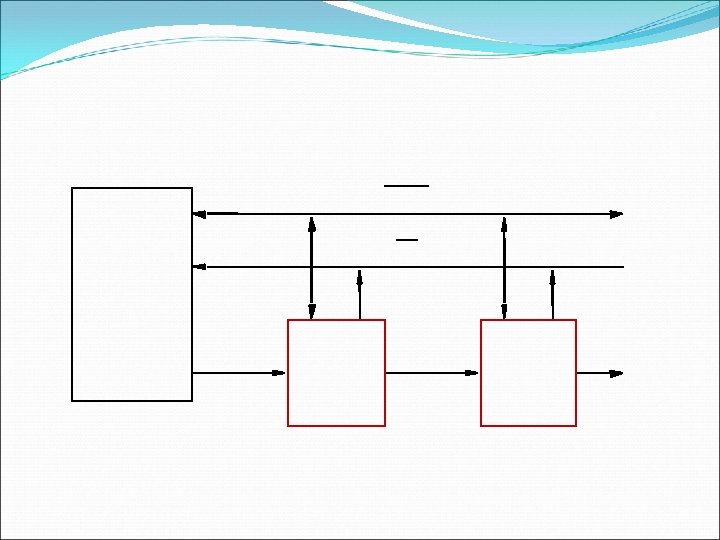

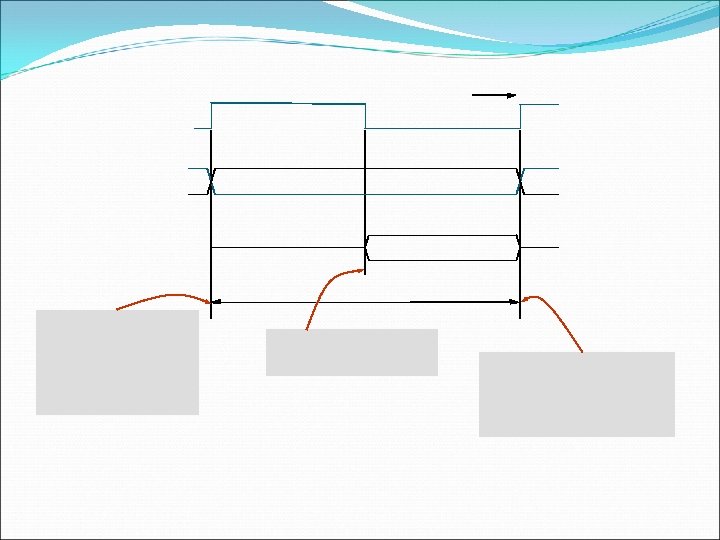

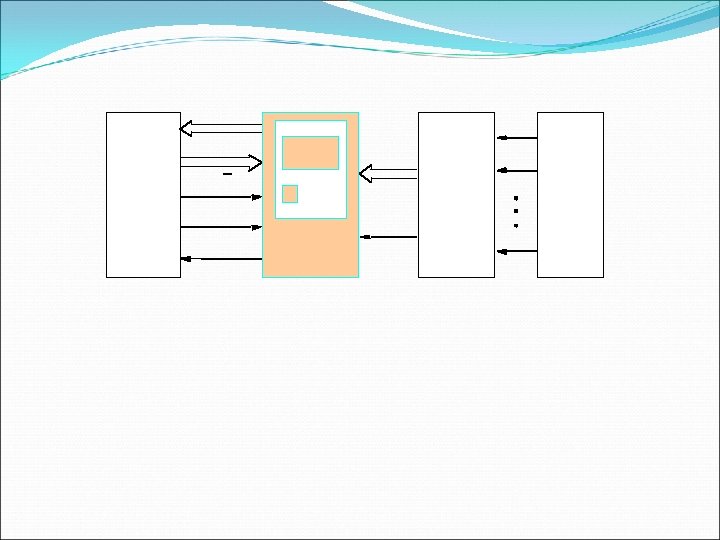

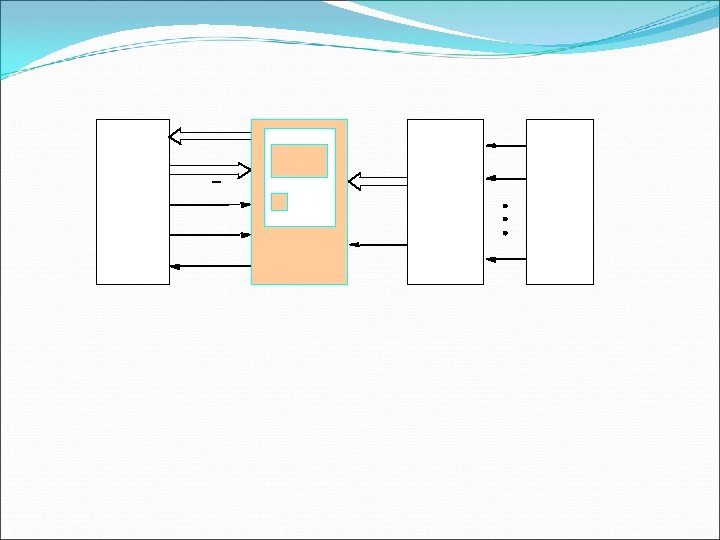

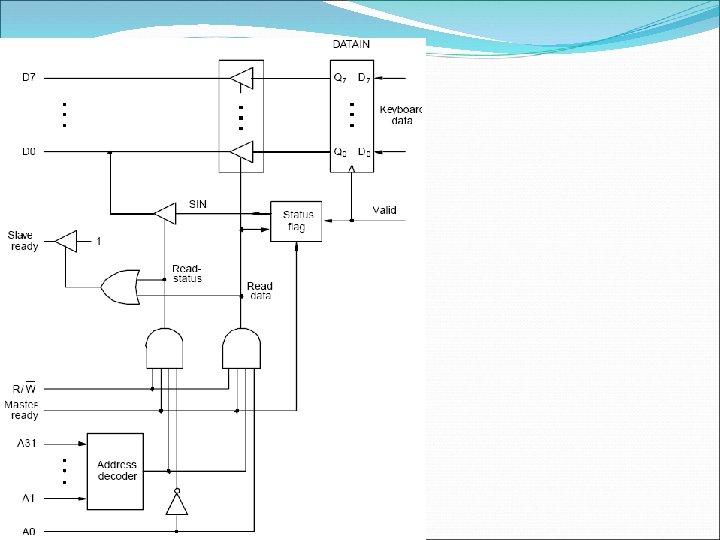

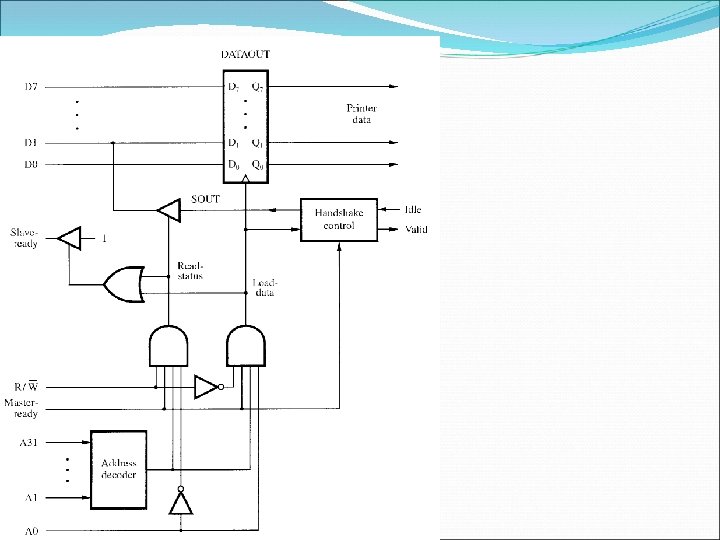

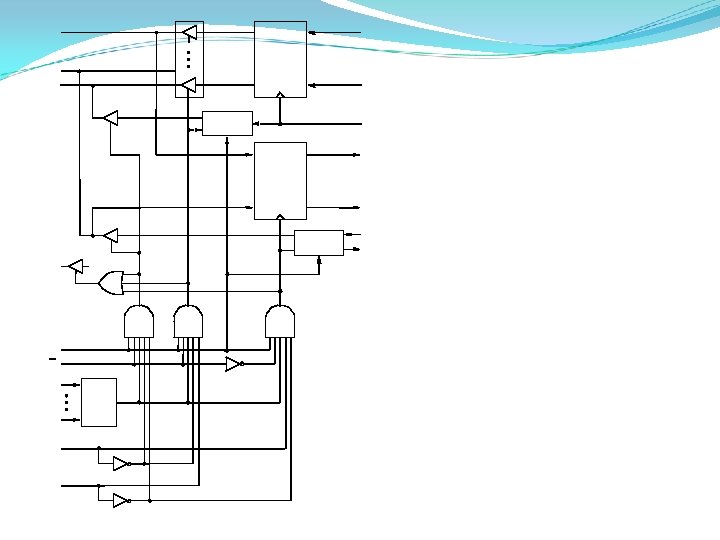

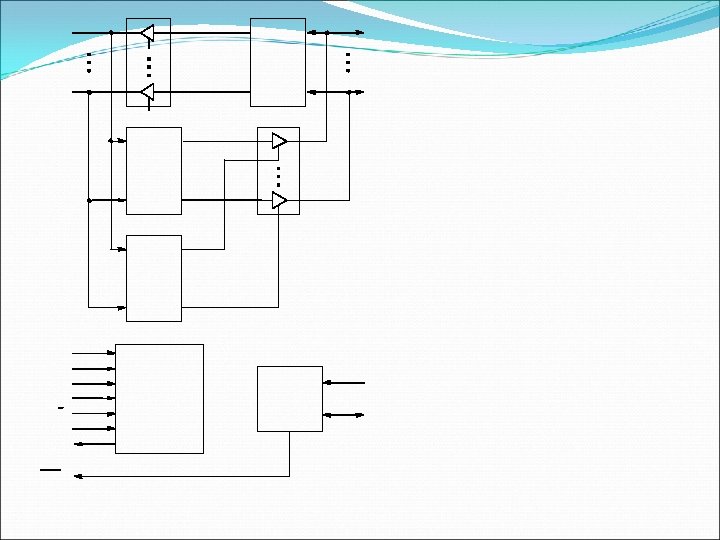

Address lines Bus Data lines Control lines Address decoder Control circuits Data and status registers Input device I/O interface

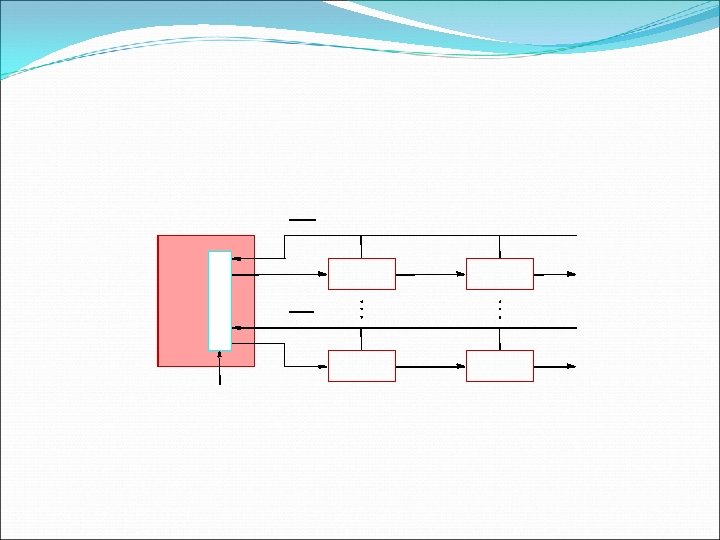

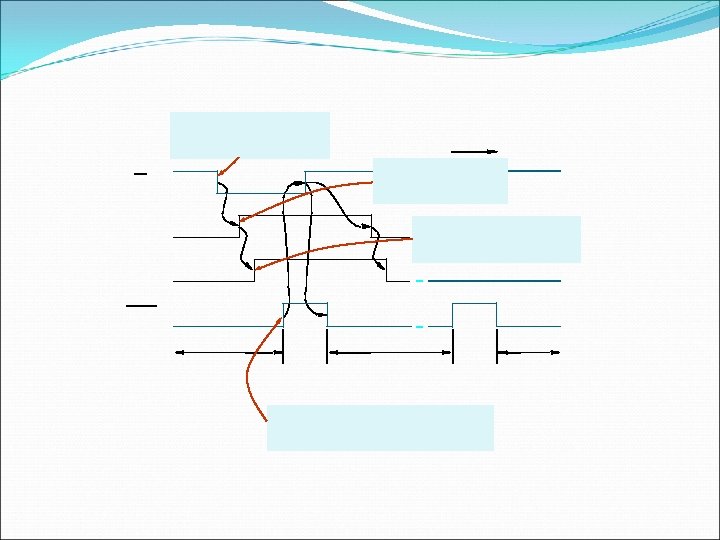

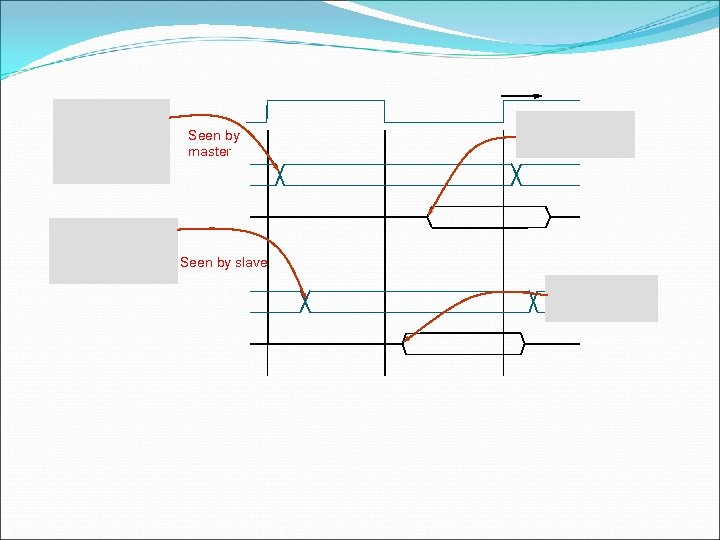

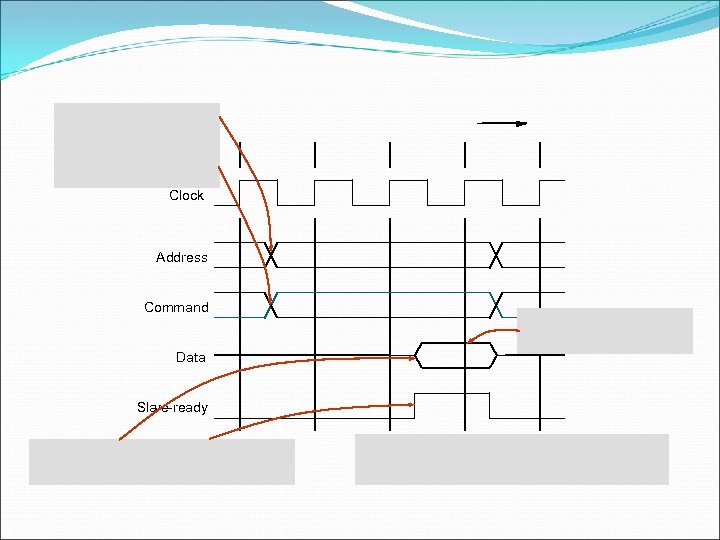

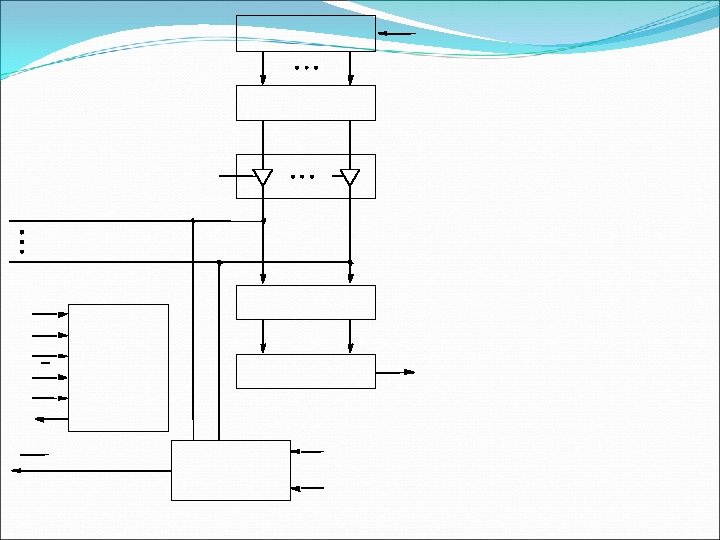

Seen by master Seen by slave

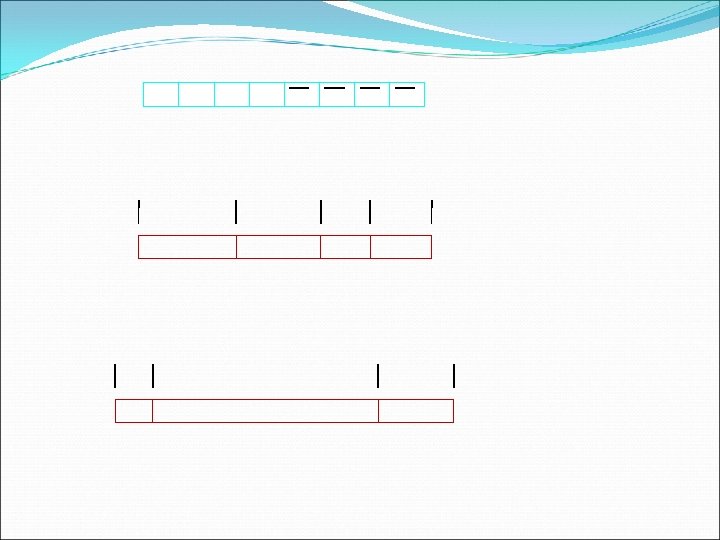

Clock Address Command Data Sla ve-ready

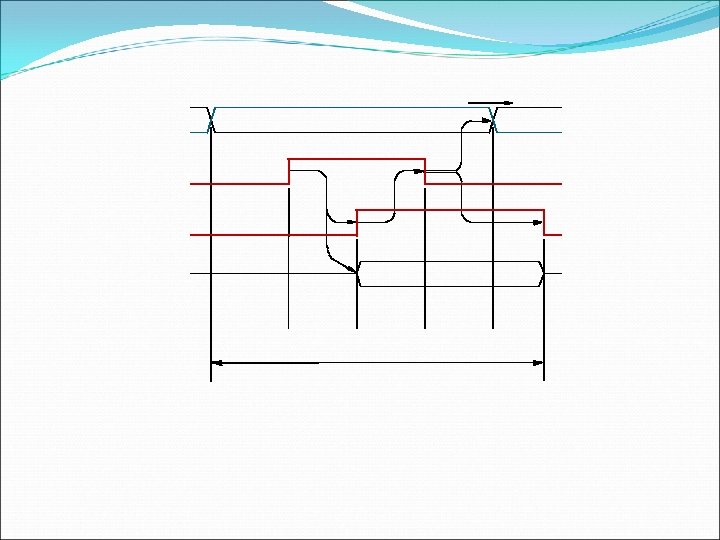

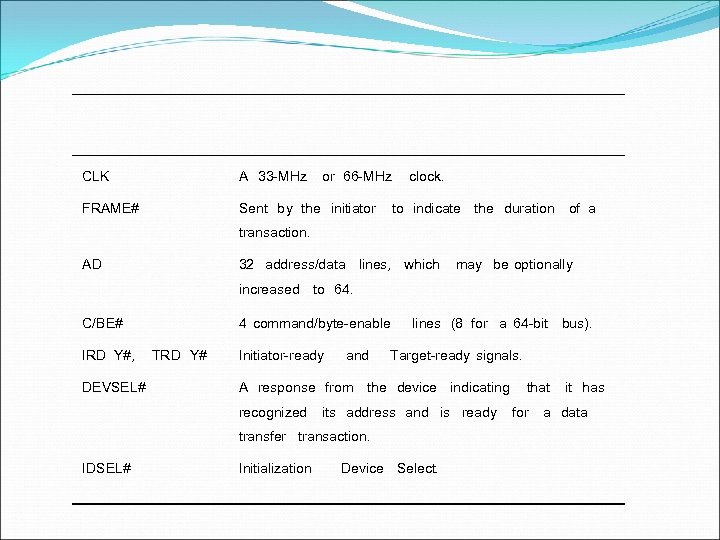

CLK A 33 -MHz or 66 -MHz FRAME# Sent by the initiator clock. to indicate the duration of a transaction. AD 32 address/data lines, which may be optionally increased to 64. C/BE# IRD Y#, DEVSEL# 4 command/byte-enable TRD Y# Initiator-ready and lines (8 for a 64 -bit bus). Target-ready signals. A response from the device indicating recognized its address and is ready transfer transaction. IDSEL# Initialization Device Select. that for it has a data

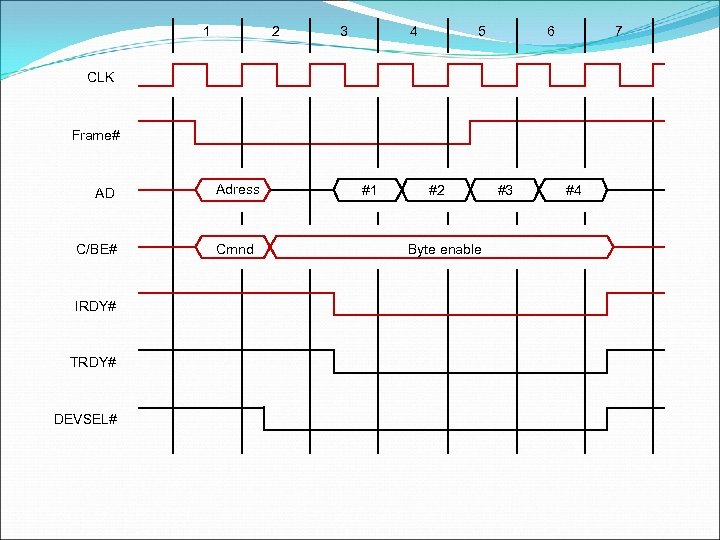

1 2 3 4 5 6 7 CLK Frame# AD C/BE# IRDY# TRDY# DEVSEL# Adress Cmnd #1 #2 Byte enable #3 #4

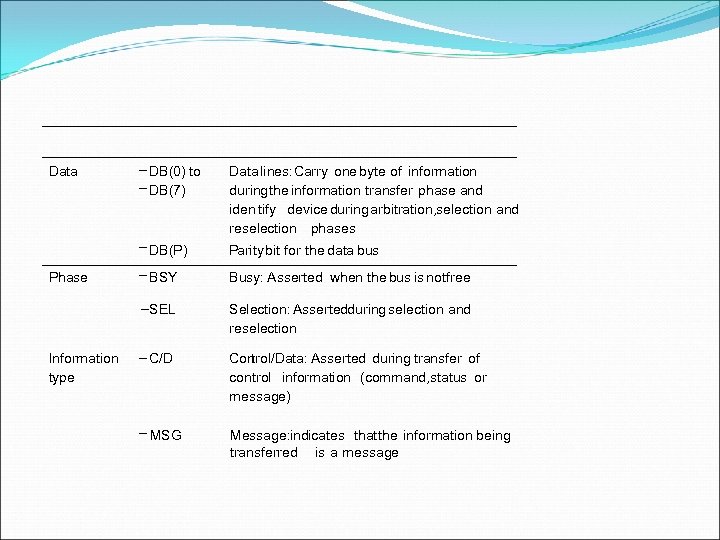

Information type Data lines: Carry one byte of information duringthe information transfer phase and iden tify device during arbitration, selection and reselection phases Parit y bit for the data bus – BSY Busy: Asserted when the bus is notfree – SEL Phase – DB(0) to – DB(7) – DB(P) Data Selection: Assertedduring selection and reselection – C/D Con trol/Data: Asserted during transfer of control information (command, status or message) – MSG Message: indicates thatthe information being transferred is a message

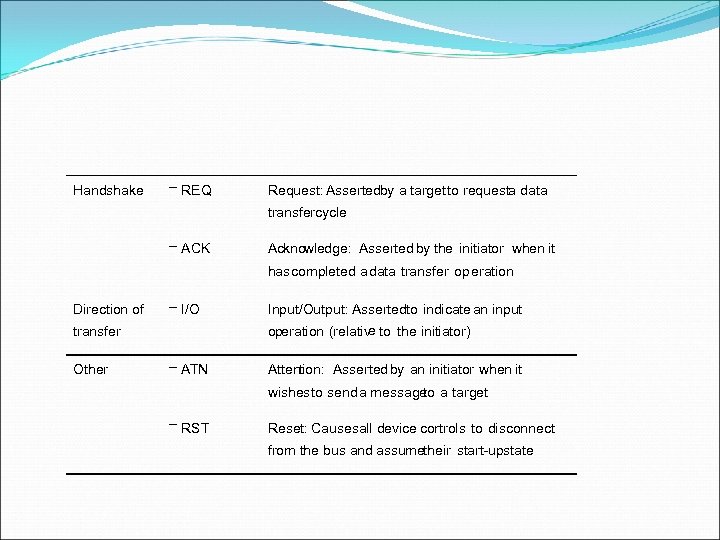

Handshake – REQ Request: Assertedby a targetto requesta data transfercycle – ACK Acknowledge: Asserted by the initiator when it hascompleted a data transfer op eration Direction of – I/O e operation (relativ to the initiator) transfer Other Input/Output: Assertedto indicate an input – ATN Attention: Asserted by an initiator when it wishesto send a message a target to – RST Reset: Causesall device con trols to disconnect from the bus and assumetheir start-upstate

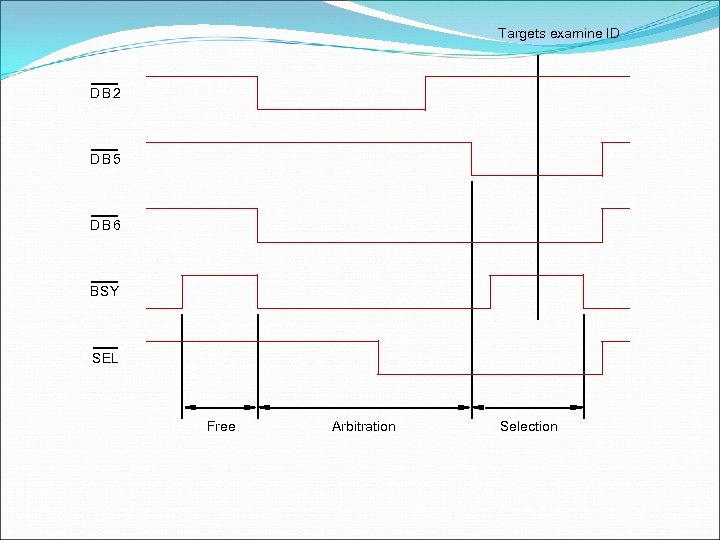

Targets examine ID DB 2 DB 5 DB 6 BSY SEL Free Arbitration Selection

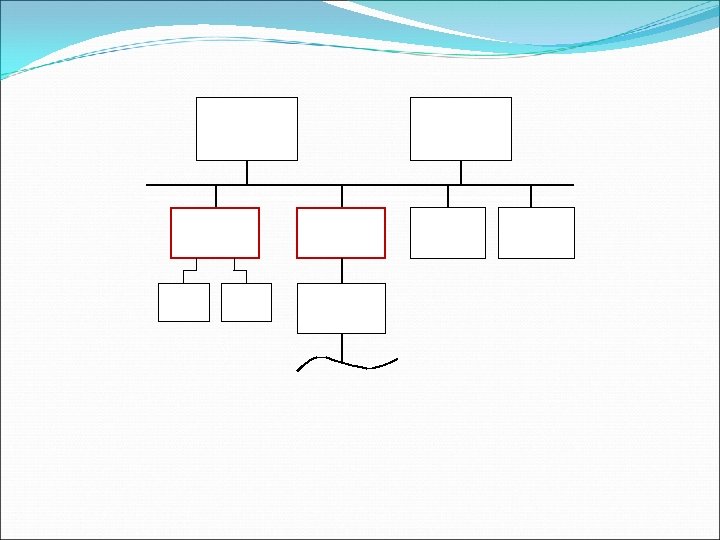

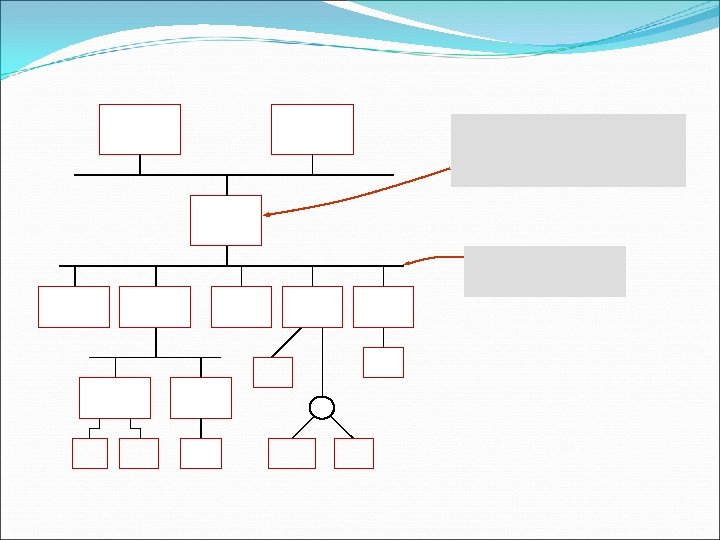

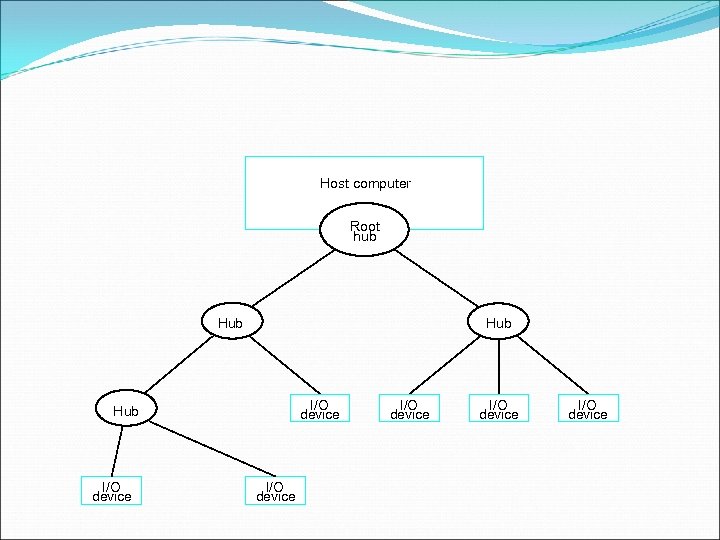

Host computer Root hub Hub I/O device I/O device

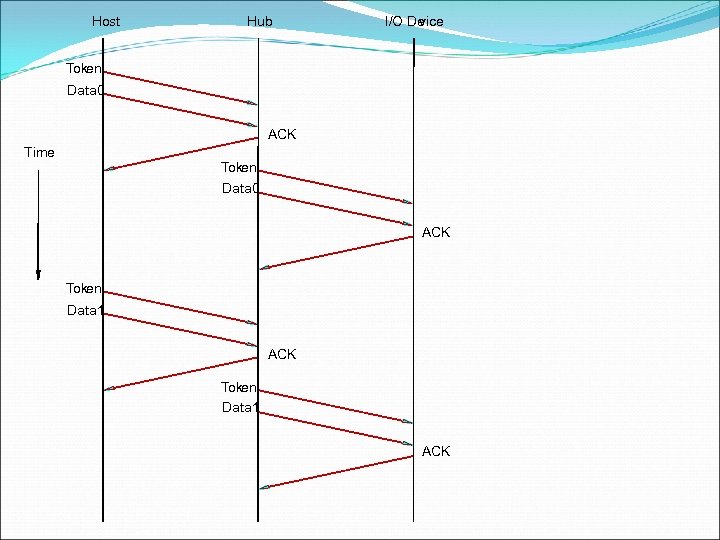

Host Hub I/O De vice Token Data 0 ACK Time Token Data 0 ACK Token Data 1 ACK

65ad76ca21dc78610417986e463f3e58.ppt