d3add6c015f6d6ee597d23368dacffa1.ppt

- Количество слайдов: 9

Activities Associated With Working With Xilinx to Develop A Space Flow for Virtex Family of FPGA’s Larry Harzstark The Aerospace Corporation Associate Director, Parts, Materials and Processes Department 06 -26 -06 1 © 2006 The Aerospace Corporation

Activities Associated With Working With Xilinx to Develop A Space Flow for Virtex Family of FPGA’s Larry Harzstark The Aerospace Corporation Associate Director, Parts, Materials and Processes Department 06 -26 -06 1 © 2006 The Aerospace Corporation

Background • • In recent years, the government, during acquisition reform, has not required space systems manufacturers to absolutely utilize space-qualified parts in their systems. Systems manufacturers have evaluated the best part available and determined through a self-selected series of tests and analyses that a specific device is acceptable and meets the system performance and reliability requirements. However, based on a number of recent problems experienced, which have had a critical impact upon launch schedules as well as on-orbit performance, it has been determined that a more stringent approach to parts, materials and processes must be followed. Therefore, a review of the space level requirements for utilization was begun. The government is intending to re-invigorate specs and standards on contract for the space user community The specs and standards will require the use of a full-up space qualified part Non-space qualified parts will be by exception only and will still require the same types of analysis and testing

Background • • In recent years, the government, during acquisition reform, has not required space systems manufacturers to absolutely utilize space-qualified parts in their systems. Systems manufacturers have evaluated the best part available and determined through a self-selected series of tests and analyses that a specific device is acceptable and meets the system performance and reliability requirements. However, based on a number of recent problems experienced, which have had a critical impact upon launch schedules as well as on-orbit performance, it has been determined that a more stringent approach to parts, materials and processes must be followed. Therefore, a review of the space level requirements for utilization was begun. The government is intending to re-invigorate specs and standards on contract for the space user community The specs and standards will require the use of a full-up space qualified part Non-space qualified parts will be by exception only and will still require the same types of analysis and testing

Background • • • Presented an overview to Xilinx in December 2004 of space requirements for new technology Meeting held with Xilinx in March 2005 to discuss space requirements – Some space contractors part of meeting (General Dynamics, Honeywell, JPL, Lockheed Martin) – Boeing started to work with Xilinx at a later time period Weekly telecons held with Xilinx starting April 2005 to develop a flow for hermetic and flip-chip devices Started with MIL-PRF-38535 Class V Flow – Flip-chip devices had to take into account tests and inspections that do not make sense – Flip-chip devices also require tests/inspections that hermetic devices do not require Flow also required to account for column grid array packaging

Background • • • Presented an overview to Xilinx in December 2004 of space requirements for new technology Meeting held with Xilinx in March 2005 to discuss space requirements – Some space contractors part of meeting (General Dynamics, Honeywell, JPL, Lockheed Martin) – Boeing started to work with Xilinx at a later time period Weekly telecons held with Xilinx starting April 2005 to develop a flow for hermetic and flip-chip devices Started with MIL-PRF-38535 Class V Flow – Flip-chip devices had to take into account tests and inspections that do not make sense – Flip-chip devices also require tests/inspections that hermetic devices do not require Flow also required to account for column grid array packaging

Current Status • • • Preliminary flow developed Xilinx has generated procedures and process documents Aerospace in the process of reviewing procedures and process documents – Provided comments to Xilinx and just received responses – Requires review of Xilinx responses Aerospace requires information from the foundry relating to wafer level reliability – Need to understand data that we have and determine what technologies it is applicable to – 0. 25 um, 0. 15 um, 90 nm, 65 nm ? ? – May need additional data from foundry Reviewed requirements for new technology insertion with Xilinx – Wafer foundry data will satisfy many of the requirements – Still need to work long term reliability (life test) data for 6000 hrs

Current Status • • • Preliminary flow developed Xilinx has generated procedures and process documents Aerospace in the process of reviewing procedures and process documents – Provided comments to Xilinx and just received responses – Requires review of Xilinx responses Aerospace requires information from the foundry relating to wafer level reliability – Need to understand data that we have and determine what technologies it is applicable to – 0. 25 um, 0. 15 um, 90 nm, 65 nm ? ? – May need additional data from foundry Reviewed requirements for new technology insertion with Xilinx – Wafer foundry data will satisfy many of the requirements – Still need to work long term reliability (life test) data for 6000 hrs

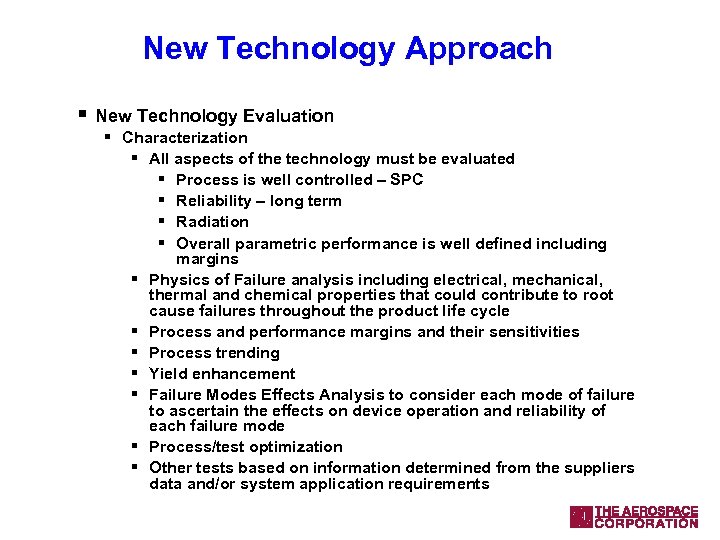

New Technology Approach § New Technology Evaluation § Characterization § All aspects of the technology must be evaluated § Process is well controlled – SPC § Reliability – long term § Radiation § Overall parametric performance is well defined including margins § Physics of Failure analysis including electrical, mechanical, thermal and chemical properties that could contribute to root cause failures throughout the product life cycle § Process and performance margins and their sensitivities § Process trending § Yield enhancement § Failure Modes Effects Analysis to consider each mode of failure to ascertain the effects on device operation and reliability of each failure mode § Process/test optimization § Other tests based on information determined from the suppliers data and/or system application requirements

New Technology Approach § New Technology Evaluation § Characterization § All aspects of the technology must be evaluated § Process is well controlled – SPC § Reliability – long term § Radiation § Overall parametric performance is well defined including margins § Physics of Failure analysis including electrical, mechanical, thermal and chemical properties that could contribute to root cause failures throughout the product life cycle § Process and performance margins and their sensitivities § Process trending § Yield enhancement § Failure Modes Effects Analysis to consider each mode of failure to ascertain the effects on device operation and reliability of each failure mode § Process/test optimization § Other tests based on information determined from the suppliers data and/or system application requirements

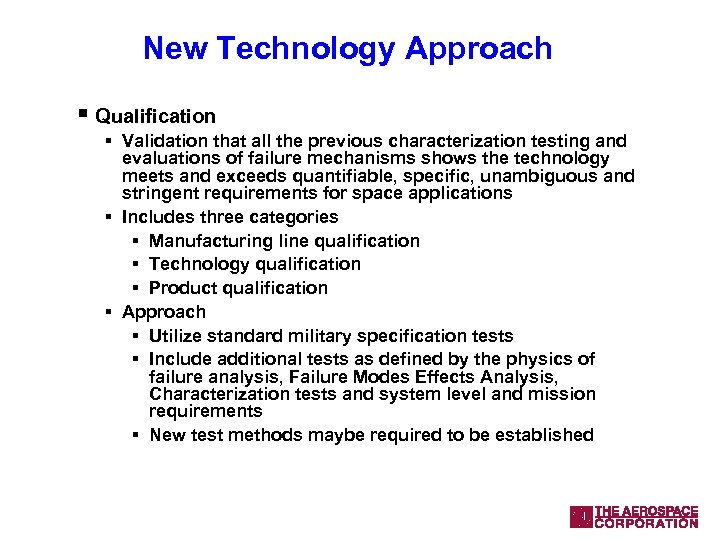

New Technology Approach § Qualification § Validation that all the previous characterization testing and evaluations of failure mechanisms shows the technology meets and exceeds quantifiable, specific, unambiguous and stringent requirements for space applications § Includes three categories § Manufacturing line qualification § Technology qualification § Product qualification § Approach § Utilize standard military specification tests § Include additional tests as defined by the physics of failure analysis, Failure Modes Effects Analysis, Characterization tests and system level and mission requirements § New test methods maybe required to be established

New Technology Approach § Qualification § Validation that all the previous characterization testing and evaluations of failure mechanisms shows the technology meets and exceeds quantifiable, specific, unambiguous and stringent requirements for space applications § Includes three categories § Manufacturing line qualification § Technology qualification § Product qualification § Approach § Utilize standard military specification tests § Include additional tests as defined by the physics of failure analysis, Failure Modes Effects Analysis, Characterization tests and system level and mission requirements § New test methods maybe required to be established

Next Steps • With the support of Xilinx, complete space flow and documentation reviews • Space community review of flow • Resolution of any open issues • Work with DSCC to begin the QML Class V (space) audit requirements – Certification audit of Xilinx facility – Audit of foundry – Qualification of Virtex to space requirements

Next Steps • With the support of Xilinx, complete space flow and documentation reviews • Space community review of flow • Resolution of any open issues • Work with DSCC to begin the QML Class V (space) audit requirements – Certification audit of Xilinx facility – Audit of foundry – Qualification of Virtex to space requirements

Summary • Working with Xilinx to develop a space flow for new technology insertion of Virtex family of FPGA’s • Broader space community involvement required to ensure buy-in • DSCC involvement needed for approval of QML Class V • Good support from Xilinx has been very helpful in this undertaking

Summary • Working with Xilinx to develop a space flow for new technology insertion of Virtex family of FPGA’s • Broader space community involvement required to ensure buy-in • DSCC involvement needed for approval of QML Class V • Good support from Xilinx has been very helpful in this undertaking