0e4aea4a469372af7ce7d47786abcf47.ppt

- Количество слайдов: 32

ABEL SOC 연구실 최지호 원천관 339 -2호 (zigprid@ajou. ac. kr/219 -2390) 2004/07/08 1/8

PLD 란? PLD (Programmable Logic Device) PLD는 사용자가 필요로 하는 논리기능을 직접 program하여 사용할 수 있는 IC PROM (Programmable Read Only Memory) PLA (Programmable Logic Array) PAL (Programmable Array Logic) SPLD (Simple Programmable Logic Device) CPLD (Complex Programmable Logic Device) FPGA (Field Programmable Gate Array) 2

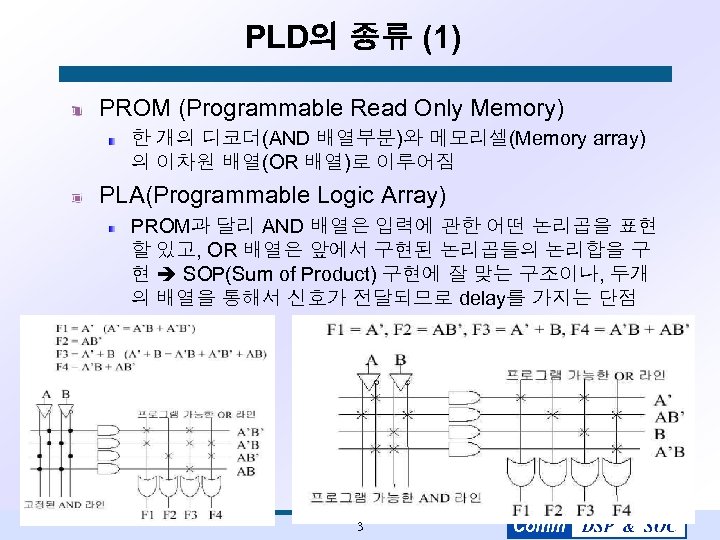

PLD의 종류 (1) PROM (Programmable Read Only Memory) 한 개의 디코더(AND 배열부분)와 메모리셀(Memory array) 의 이차원 배열(OR 배열)로 이루어짐 PLA(Programmable Logic Array) PROM과 달리 AND 배열은 입력에 관한 어떤 논리곱을 표현 할 있고, OR 배열은 앞에서 구현된 논리곱들의 논리합을 구 현 SOP(Sum of Product) 구현에 잘 맞는 구조이나, 두개 의 배열을 통해서 신호가 전달되므로 delay를 가지는 단점 3

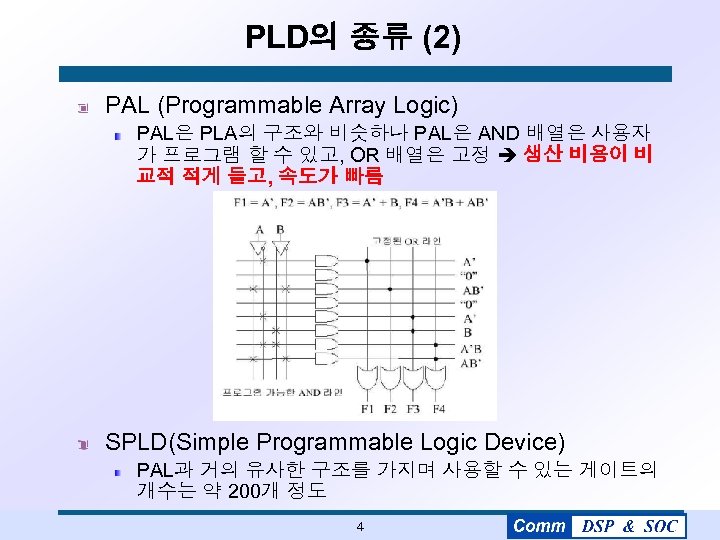

PLD의 종류 (2) PAL (Programmable Array Logic) PAL은 PLA의 구조와 비슷하나 PAL은 AND 배열은 사용자 가 프로그램 할 수 있고, OR 배열은 고정 생산 비용이 비 교적 적게 들고, 속도가 빠름 SPLD(Simple Programmable Logic Device) PAL과 거의 유사한 구조를 가지며 사용할 수 있는 게이트의 개수는 약 200개 정도 4

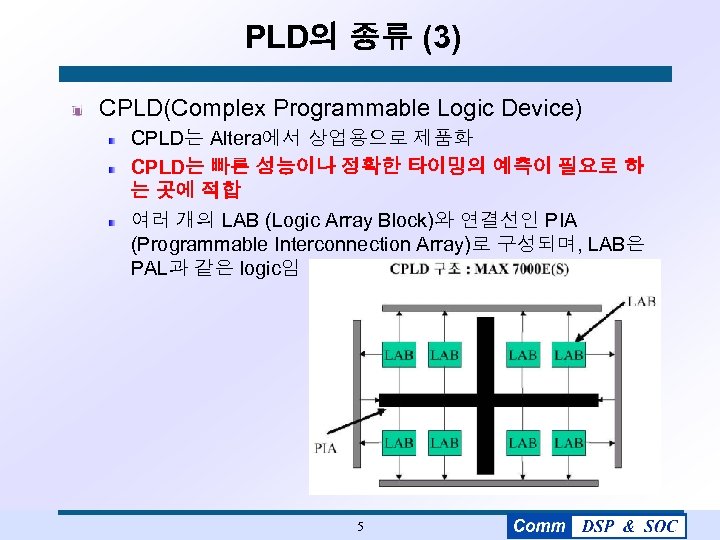

PLD의 종류 (3) CPLD(Complex Programmable Logic Device) CPLD는 Altera에서 상업용으로 제품화 CPLD는 빠른 성능이나 정확한 타이밍의 예측이 필요로 하 는 곳에 적합 여러 개의 LAB (Logic Array Block)와 연결선인 PIA (Programmable Interconnection Array)로 구성되며, LAB은 PAL과 같은 logic임 5

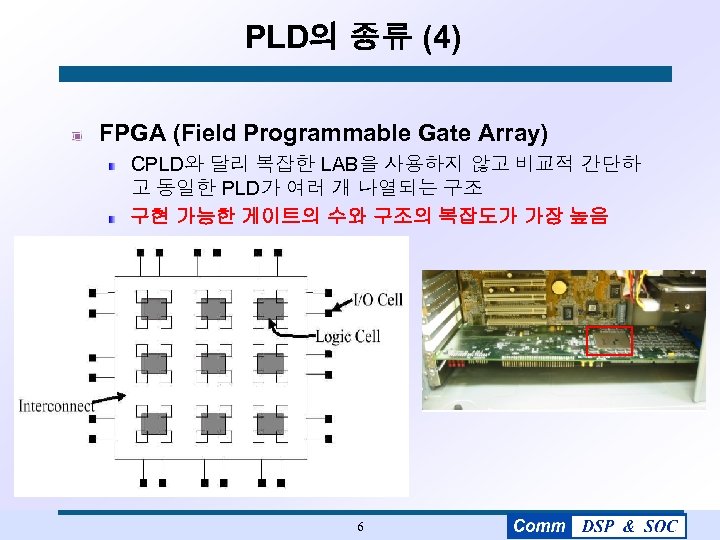

PLD의 종류 (4) FPGA (Field Programmable Gate Array) CPLD와 달리 복잡한 LAB을 사용하지 않고 비교적 간단하 고 동일한 PLD가 여러 개 나열되는 구조 구현 가능한 게이트의 수와 구조의 복잡도가 가장 높음 6

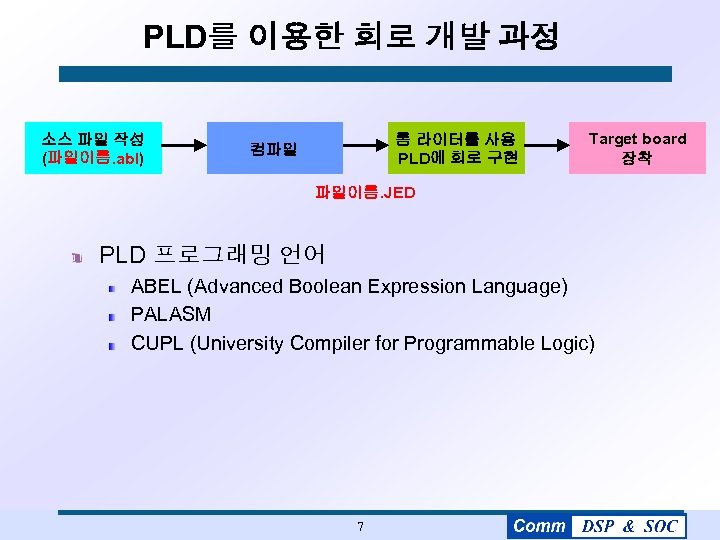

PLD를 이용한 회로 개발 과정 소스 파일 작성 (파일이름. abl) 롬 라이터를 사용 PLD에 회로 구현 컴파일 Target board 장착 파일이름. JED PLD 프로그래밍 언어 ABEL (Advanced Boolean Expression Language) PALASM CUPL (University Compiler for Programmable Logic) 7

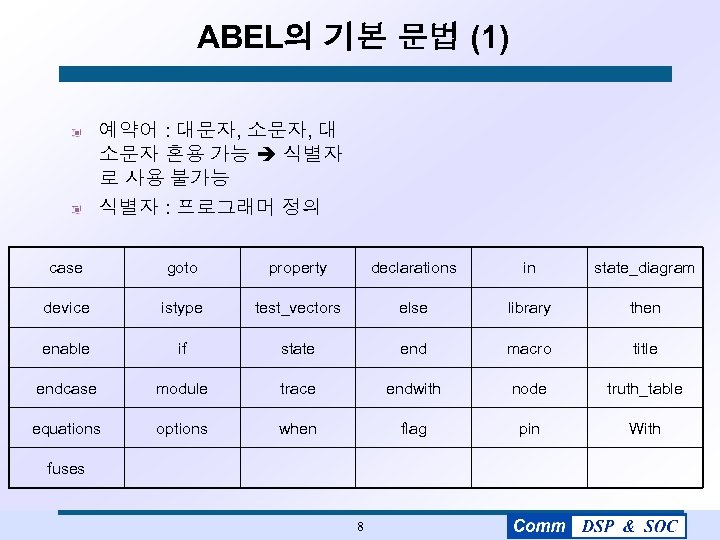

ABEL의 기본 문법 (1) 예약어 : 대문자, 소문자, 대 소문자 혼용 가능 식별자 로 사용 불가능 식별자 : 프로그래머 정의 case goto property declarations in state_diagram device istype test_vectors else library then enable if state end macro title endcase module trace endwith node truth_table equations options when flag pin With fuses 8

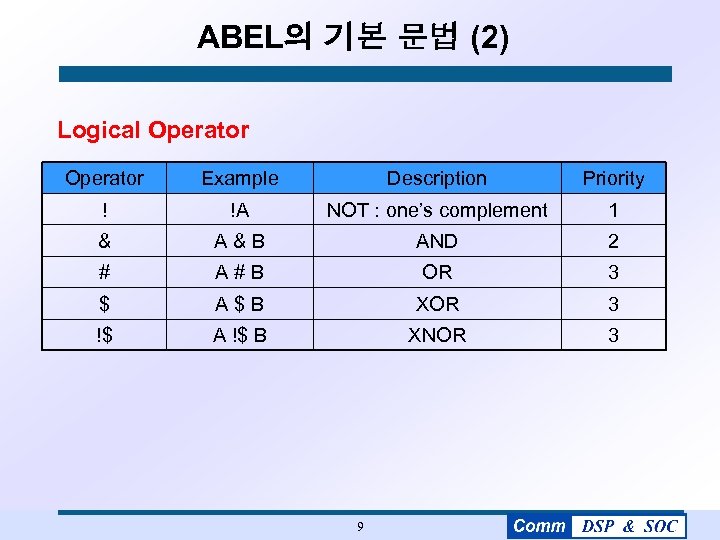

ABEL의 기본 문법 (2) Logical Operator Example Description Priority ! !A NOT : one’s complement 1 & A&B AND 2 # A#B OR 3 $ A$B XOR 3 !$ A !$ B XNOR 3 9

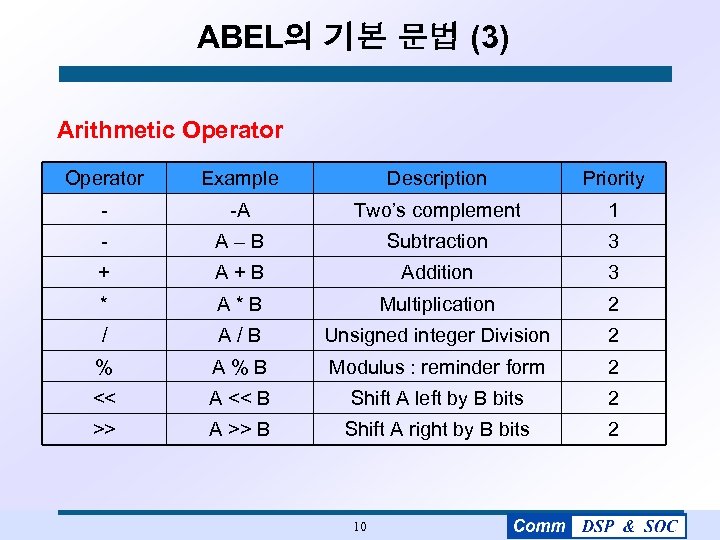

ABEL의 기본 문법 (3) Arithmetic Operator Example Description Priority - -A Two’s complement 1 - A–B Subtraction 3 + A+B Addition 3 * A*B Multiplication 2 / A/B Unsigned integer Division 2 % A%B Modulus : reminder form 2 << A << B Shift A left by B bits 2 >> A >> B Shift A right by B bits 2 10

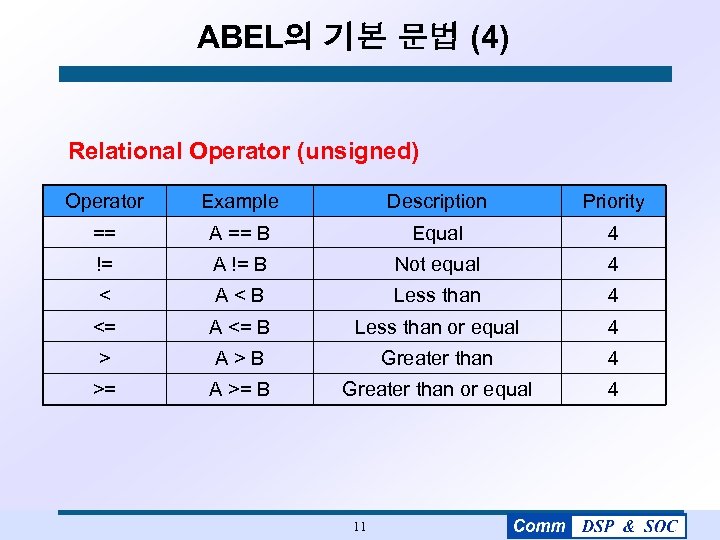

ABEL의 기본 문법 (4) Relational Operator (unsigned) Operator Example Description Priority == A == B Equal 4 != A != B Not equal 4 < A<B Less than 4 <= A <= B Less than or equal 4 > A>B Greater than 4 >= A >= B Greater than or equal 4 11

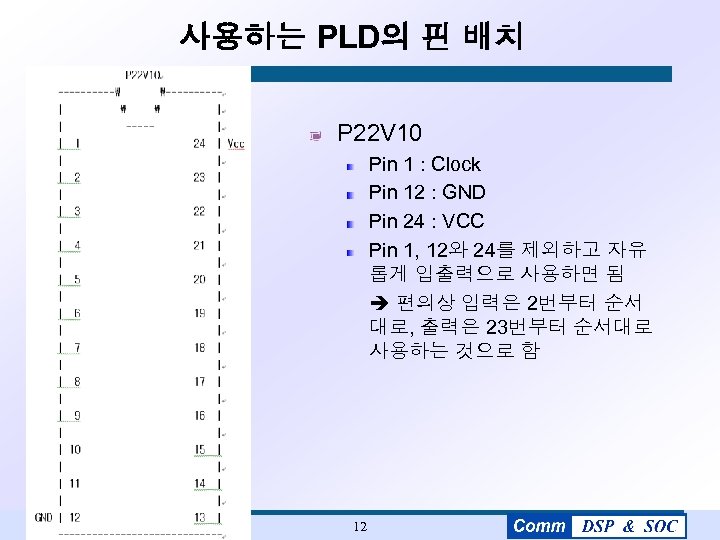

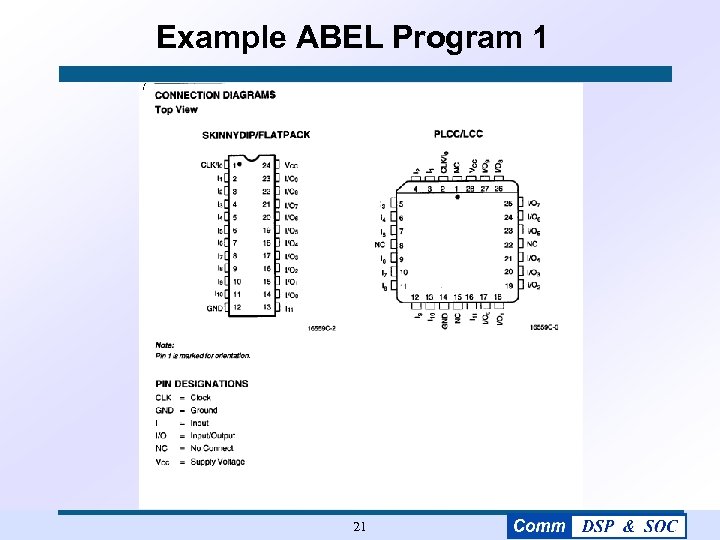

사용하는 PLD의 핀 배치 P 22 V 10 Pin 1 : Clock Pin 12 : GND Pin 24 : VCC Pin 1, 12와 24를 제외하고 자유 롭게 입출력으로 사용하면 됨 편의상 입력은 2번부터 순서 대로, 출력은 23번부터 순서대로 사용하는 것으로 함 12

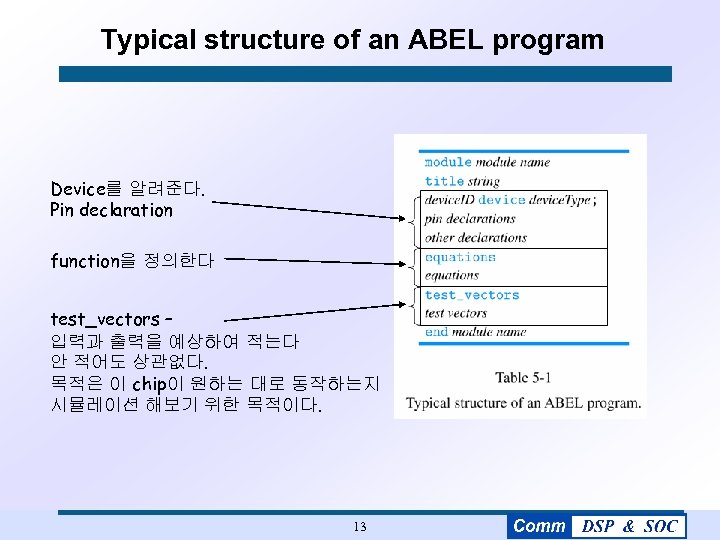

Typical structure of an ABEL program Device를 알려준다. Pin declaration function을 정의한다 test_vectors – 입력과 출력을 예상하여 적는다 안 적어도 상관없다. 목적은 이 chip이 원하는 대로 동작하는지 시뮬레이션 해보기 위한 목적이다. 13

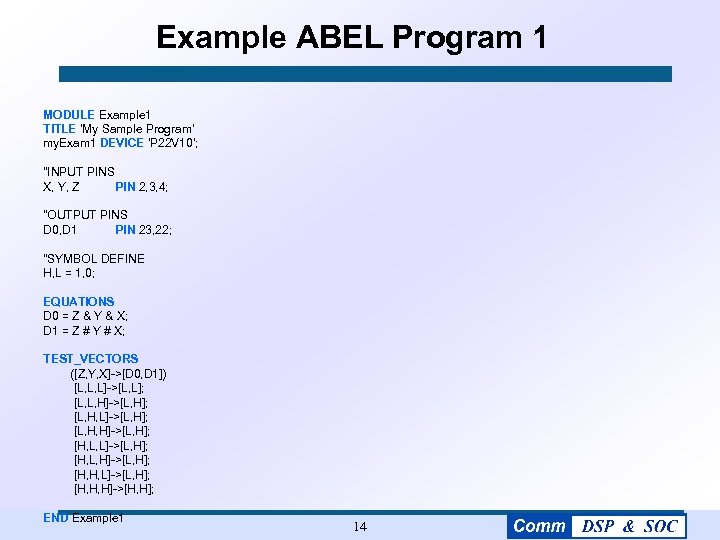

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 14

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; 1. Module Name을 시작과 끝을 항상 일치시켜줌 u 어떤 이름이든 관계는 없음 u 편의상 자신이 짜는 프로그램과 관계 있는 것으로 함 "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; X Y Z 3 input AND 3 input OR TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 15 D 0 D 1

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; 1. Module Name을 시작과 끝을 항상 일치시켜줌 2. Title Name은 어떤 이름이든 상관 없음 "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 16

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; 1. Module Name을 시작과 끝을 항상 일치시켜줌 2. Title Name은 어떤 이름이든 상관 없음 3. Device. Name이 출력파일의 이름 저장하는 소스 파일의 이름과 일치 시키는 것이 좋음(편의상) Device. Name. JED 즉, 오류없이 올바로 수행되면 결과물로 my. Exam 1. JED파일이 생성되며, 이 파일을 이용하여 롬라이터로 P 22 v 10을 구울수 있음 TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 17

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; 1. Module Name을 시작과 끝을 항상 일치시켜줌 2. Title Name은 어떤 이름이든 상관 없음 3. Device. Name이 출력파일의 이름 Device. Name. JED 즉, 오류없이 올바로 수행되면 결과물로 my. Exam 1. JED파일이 생성되며, 이 파일을 이용하여 롬라이터로 P 22 v 10을 구울수 있음 4. Device. Type을 적어준다. 여러 종류가 있을 수 있는데, 여기에선 P 22 v 10을 사용 TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 18

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; 1. Module Name을 시작과 끝을 항상 일치시켜줌 2. Title Name은 어떤 이름이든 상관 없음 3. Device. Name이 출력파일의 이름 Device. Name. JED 즉, 오류없이 올바로 수행되면 결과물로 my. Exam 1. JED파일이 생성되며, 이 파일을 이용하여 롬라이터로 P 22 v 10을 구울수 있음 EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; 4. Device. Type을 적어준다. 여러 종류가 있을 수 있는데, 여기에선 P 22 v 10을 사용 TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; 5. P 22 v 10에 대해 Input Output pin declaration 을 한다. 아무렇게나 할 수 있는 것이 아니고 datasheet를 참고하여 작성 교재의 경우 Output Pin에는 istype ‘com’을 기술하나 제공한 컴파일러는 인식하지 못함 END Example 1 19

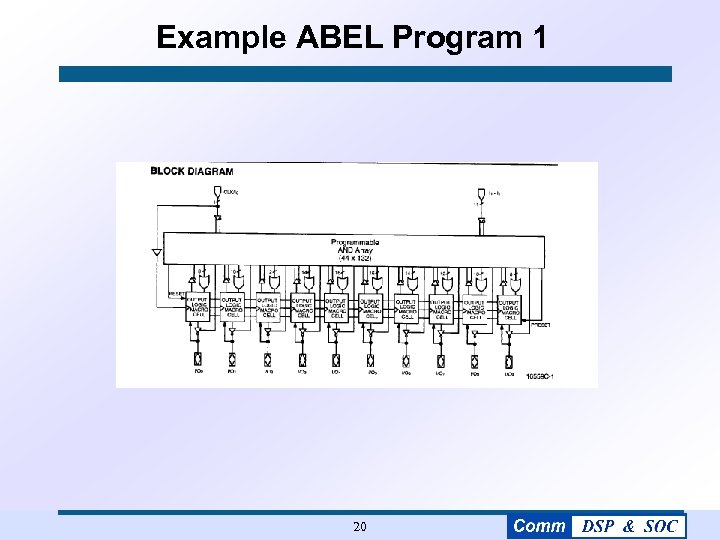

Example ABEL Program 1 20

Example ABEL Program 1 21

Example ABEL Program 1 22

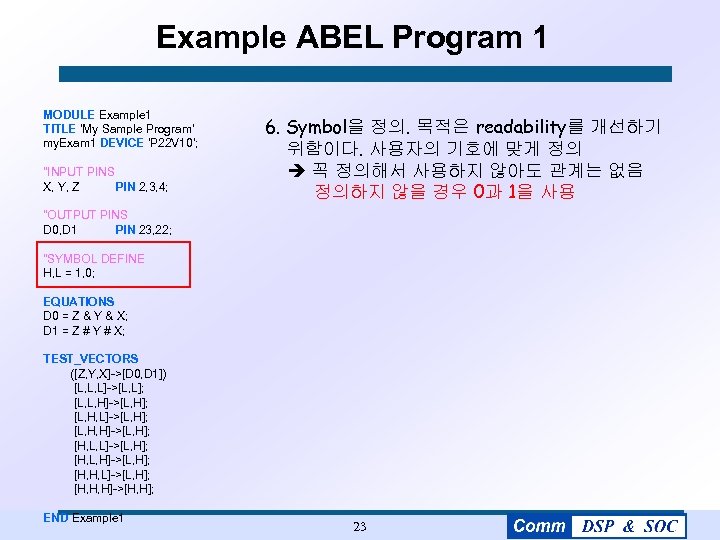

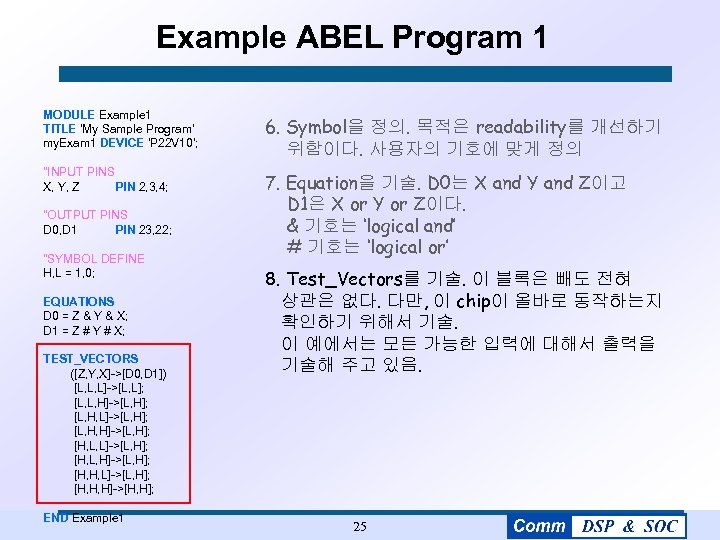

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; "INPUT PINS X, Y, Z PIN 2, 3, 4; 6. Symbol을 정의. 목적은 readability를 개선하기 위함이다. 사용자의 기호에 맞게 정의 꼭 정의해서 사용하지 않아도 관계는 없음 정의하지 않을 경우 0과 1을 사용 "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 23

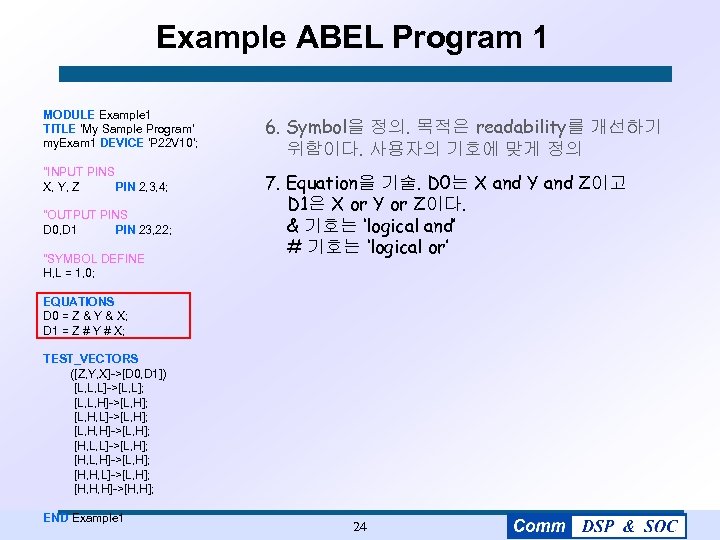

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; 6. Symbol을 정의. 목적은 readability를 개선하기 위함이다. 사용자의 기호에 맞게 정의 "INPUT PINS X, Y, Z PIN 2, 3, 4; 7. Equation을 기술. D 0는 X and Y and Z이고 D 1은 X or Y or Z이다. & 기호는 ‘logical and’ # 기호는 ‘logical or’ "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 24

Example ABEL Program 1 MODULE Example 1 TITLE 'My Sample Program' my. Exam 1 DEVICE 'P 22 V 10'; 6. Symbol을 정의. 목적은 readability를 개선하기 위함이다. 사용자의 기호에 맞게 정의 "INPUT PINS X, Y, Z PIN 2, 3, 4; 7. Equation을 기술. D 0는 X and Y and Z이고 D 1은 X or Y or Z이다. & 기호는 ‘logical and’ # 기호는 ‘logical or’ "OUTPUT PINS D 0, D 1 PIN 23, 22; "SYMBOL DEFINE H, L = 1, 0; EQUATIONS D 0 = Z & Y & X; D 1 = Z # Y # X; TEST_VECTORS ([Z, Y, X]->[D 0, D 1]) [L, L, L]->[L, L]; [L, L, H]->[L, H]; [L, H, L]->[L, H]; [L, H, H]->[L, H]; [H, L, L]->[L, H]; [H, L, H]->[L, H]; [H, H, L]->[L, H]; [H, H, H]->[H, H]; END Example 1 8. Test_Vectors를 기술. 이 블록은 빼도 전혀 상관은 없다. 다만, 이 chip이 올바로 동작하는지 확인하기 위해서 기술. 이 예에서는 모든 가능한 입력에 대해서 출력을 기술해 주고 있음. 25

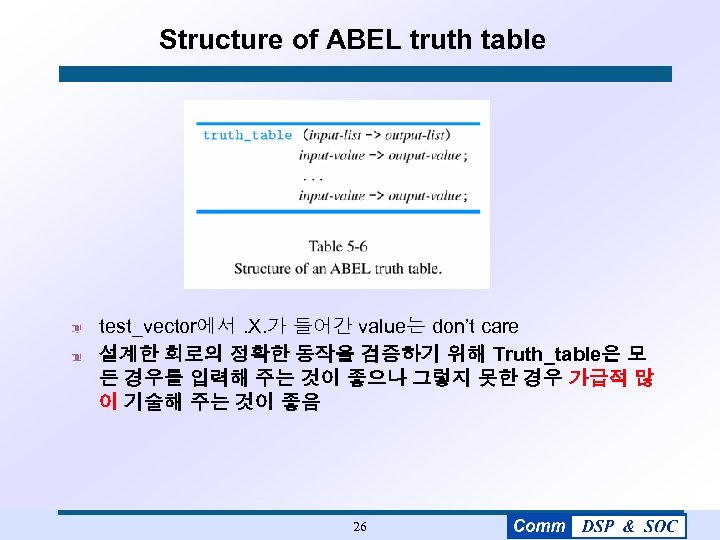

Structure of ABEL truth table test_vector에서. X. 가 들어간 value는 don’t care 설계한 회로의 정확한 동작을 검증하기 위해 Truth_table은 모 든 경우를 입력해 주는 것이 좋으나 그렇지 못한 경우 가급적 많 이 기술해 주는 것이 좋음 26

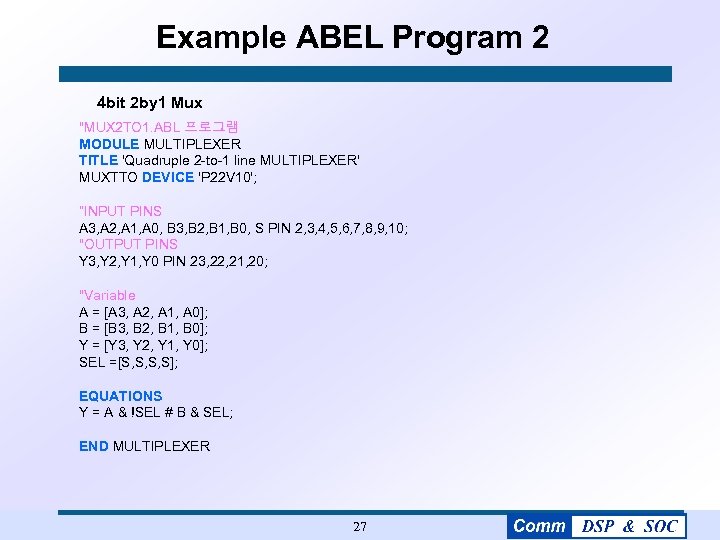

Example ABEL Program 2 4 bit 2 by 1 Mux "MUX 2 TO 1. ABL 프로그램 MODULE MULTIPLEXER TITLE 'Quadruple 2 -to-1 line MULTIPLEXER' MUXTTO DEVICE 'P 22 V 10'; “INPUT PINS A 3, A 2, A 1, A 0, B 3, B 2, B 1, B 0, S PIN 2, 3, 4, 5, 6, 7, 8, 9, 10; "OUTPUT PINS Y 3, Y 2, Y 1, Y 0 PIN 23, 22, 21, 20; "Variable A = [A 3, A 2, A 1, A 0]; B = [B 3, B 2, B 1, B 0]; Y = [Y 3, Y 2, Y 1, Y 0]; SEL =[S, S, S, S]; EQUATIONS Y = A & !SEL # B & SEL; END MULTIPLEXER 27

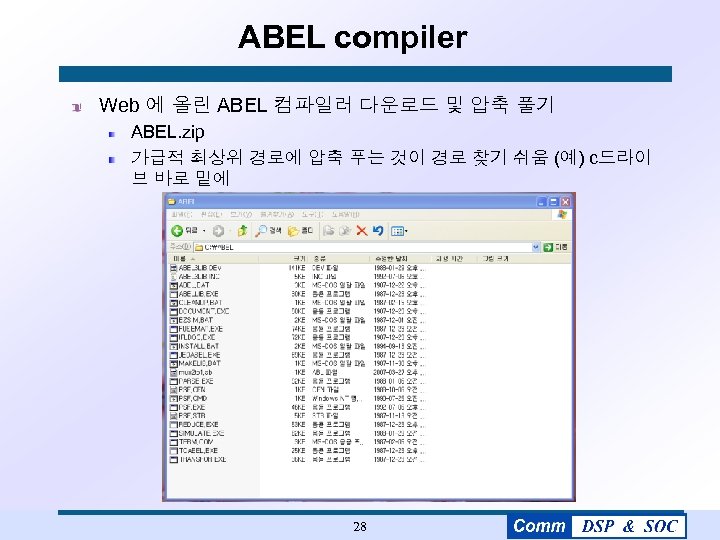

ABEL compiler Web 에 올린 ABEL 컴파일러 다운로드 및 압축 풀기 ABEL. zip 가급적 최상위 경로에 압축 푸는 것이 경로 찾기 쉬움 (예) c드라이 브 바로 밑에 28

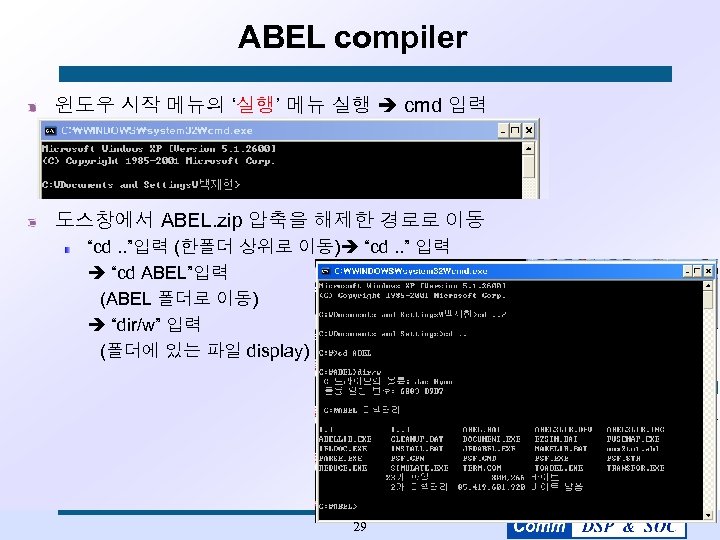

ABEL compiler 윈도우 시작 메뉴의 ‘실행’ 메뉴 실행 cmd 입력 도스창에서 ABEL. zip 압축을 해제한 경로로 이동 “cd. . ”입력 (한폴더 상위로 이동) “cd. . ” 입력 “cd ABEL”입력 (ABEL 폴더로 이동) “dir/w” 입력 (폴더에 있는 파일 display) 29

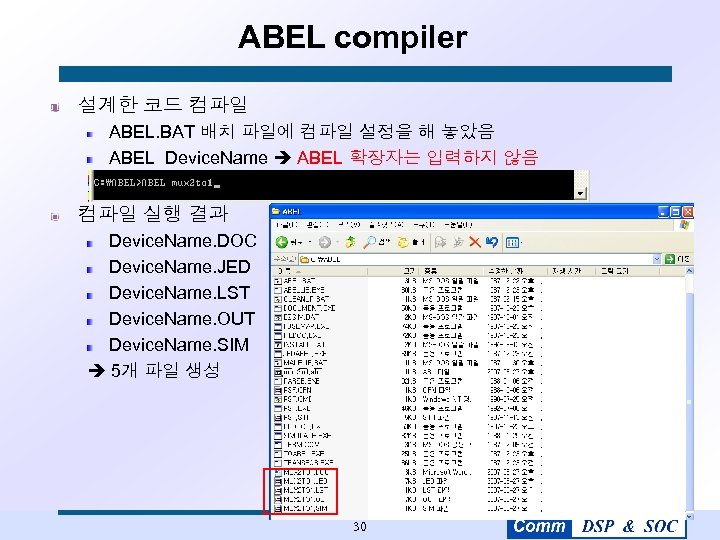

ABEL compiler 설계한 코드 컴파일 ABEL. BAT 배치 파일에 컴파일 설정을 해 놓았음 ABEL Device. Name ABEL 확장자는 입력하지 않음 컴파일 실행 결과 Device. Name. DOC Device. Name. JED Device. Name. LST Device. Name. OUT Device. Name. SIM 5개 파일 생성 30

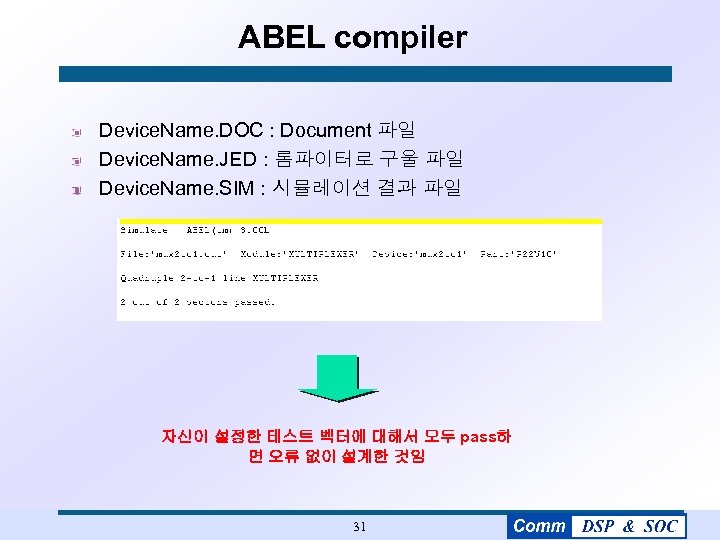

ABEL compiler Device. Name. DOC : Document 파일 Device. Name. JED : 롬파이터로 구울 파일 Device. Name. SIM : 시뮬레이션 결과 파일 자신이 설정한 테스트 벡터에 대해서 모두 pass하 면 오류 없이 설계한 것임 31

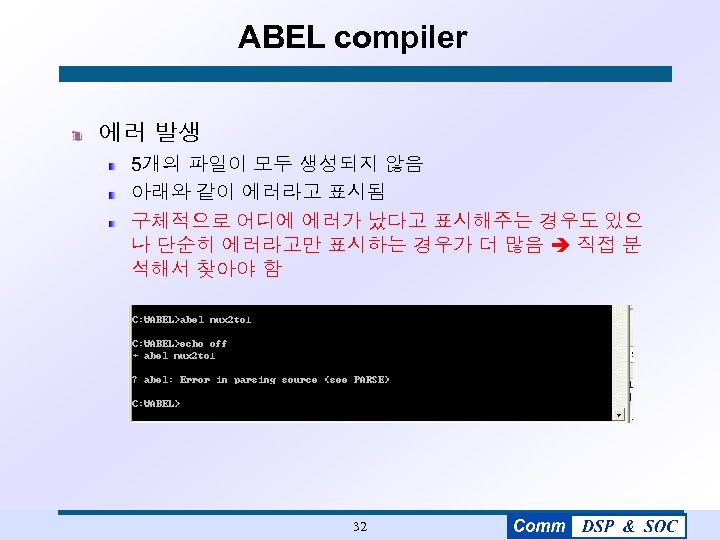

ABEL compiler 에러 발생 5개의 파일이 모두 생성되지 않음 아래와 같이 에러라고 표시됨 구체적으로 어디에 에러가 났다고 표시해주는 경우도 있으 나 단순히 에러라고만 표시하는 경우가 더 많음 직접 분 석해서 찾아야 함 32

0e4aea4a469372af7ce7d47786abcf47.ppt