7783d950534ec861295e3f5eca1950ba.ppt

- Количество слайдов: 26

A Hadron Calorimeter with Resistive Plate Chambers José Repond Argonne National Laboratory LCWS, Vancouver, Canada, July 19 – 22, 2006

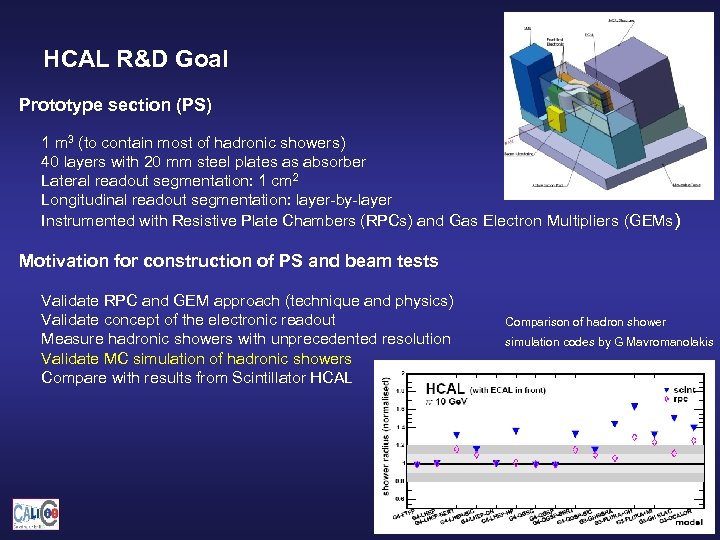

HCAL R&D Goal Prototype section (PS) 1 m 3 (to contain most of hadronic showers) 40 layers with 20 mm steel plates as absorber Lateral readout segmentation: 1 cm 2 Longitudinal readout segmentation: layer-by-layer Instrumented with Resistive Plate Chambers (RPCs) and Gas Electron Multipliers (GEMs) Motivation for construction of PS and beam tests Validate RPC and GEM approach (technique and physics) Validate concept of the electronic readout Measure hadronic showers with unprecedented resolution Validate MC simulation of hadronic showers Compare with results from Scintillator HCAL Comparison of hadron shower simulation codes by G Mavromanolakis

Collaboration Argonne National Laboratory Boston University of Chicago Fermi National Accelerator Laboratory Iowa University ITEP Protvino As part of Mechanical structure Possibly back-end readout system Test beam coordination Analysis framework…

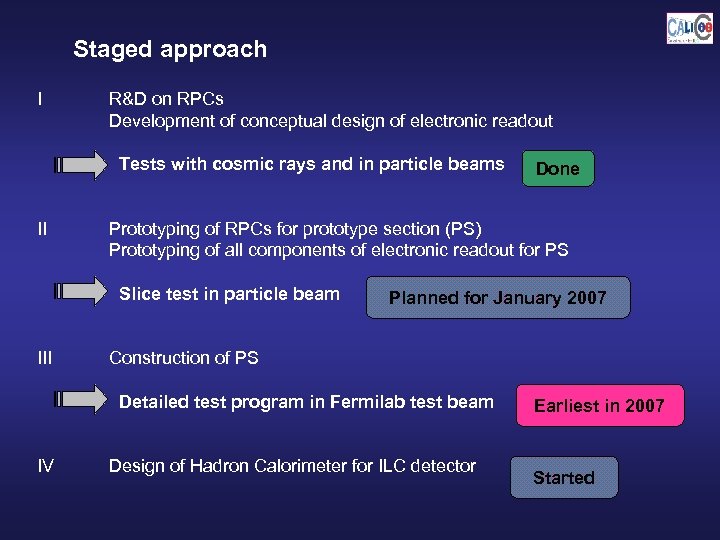

Staged approach I R&D on RPCs Development of conceptual design of electronic readout Tests with cosmic rays and in particle beams II Prototyping of RPCs for prototype section (PS) Prototyping of all components of electronic readout for PS Slice test in particle beam III Planned for January 2007 Construction of PS Detailed test program in Fermilab test beam IV Done Design of Hadron Calorimeter for ILC detector Earliest in 2007 Started

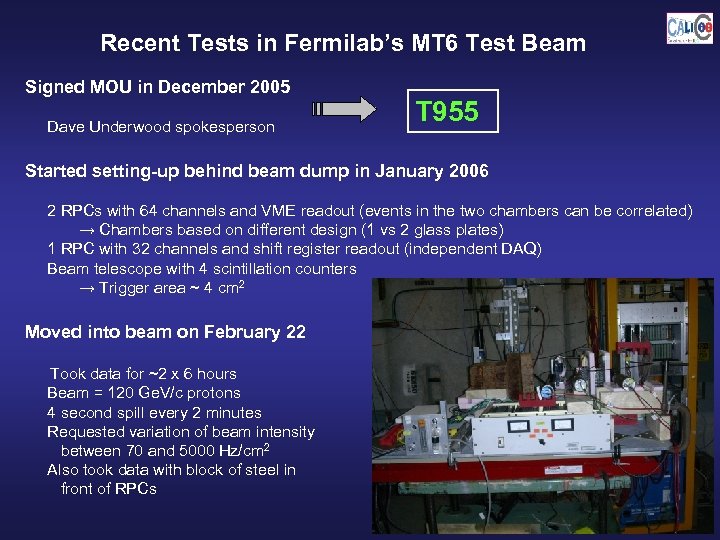

Recent Tests in Fermilab’s MT 6 Test Beam Signed MOU in December 2005 Dave Underwood spokesperson T 955 Started setting-up behind beam dump in January 2006 2 RPCs with 64 channels and VME readout (events in the two chambers can be correlated) → Chambers based on different design (1 vs 2 glass plates) 1 RPC with 32 channels and shift register readout (independent DAQ) Beam telescope with 4 scintillation counters → Trigger area ~ 4 cm 2 Moved into beam on February 22 Took data for ~2 x 6 hours Beam = 120 Ge. V/c protons 4 second spill every 2 minutes Requested variation of beam intensity between 70 and 5000 Hz/cm 2 Also took data with block of steel in front of RPCs

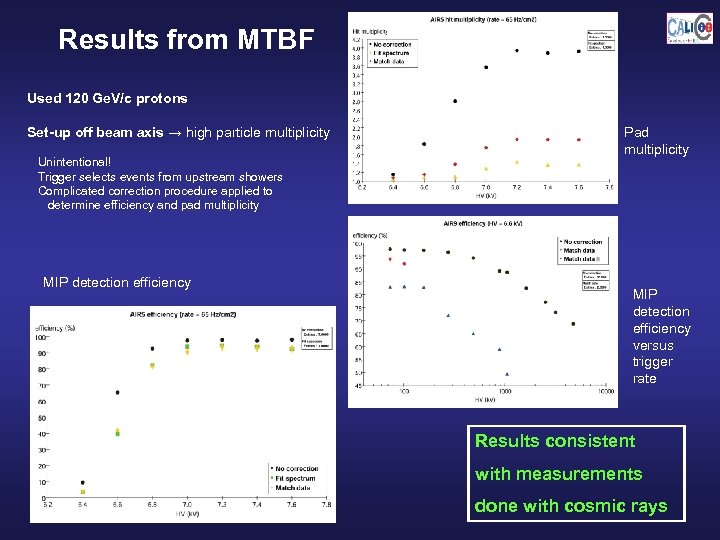

Results from MTBF Used 120 Ge. V/c protons Set-up off beam axis → high particle multiplicity Unintentional! Trigger selects events from upstream showers Complicated correction procedure applied to determine efficiency and pad multiplicity MIP detection efficiency Pad multiplicity MIP detection efficiency versus trigger rate Results consistent with measurements done with cosmic rays

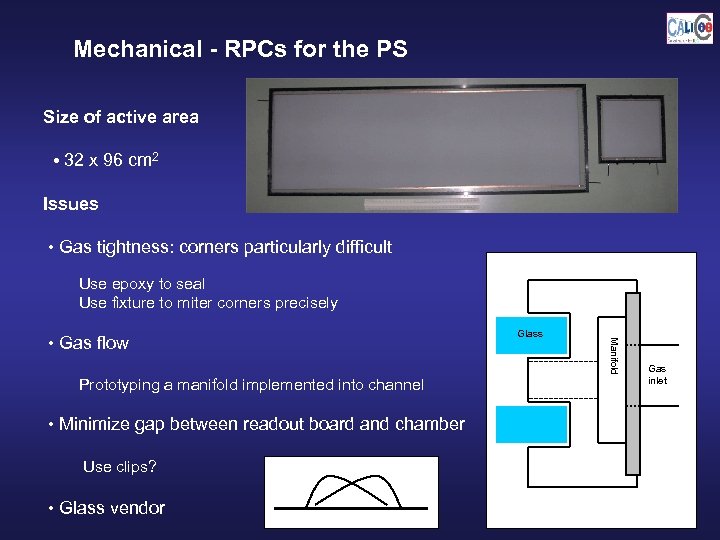

Mechanical - RPCs for the PS Size of active area • 32 x 96 cm 2 Issues • Gas tightness: corners particularly difficult Use epoxy to seal Use fixture to miter corners precisely Prototyping a manifold implemented into channel • Minimize gap between readout board and chamber Use clips? • Glass vendor Glass Manifold • Gas flow Gas inlet

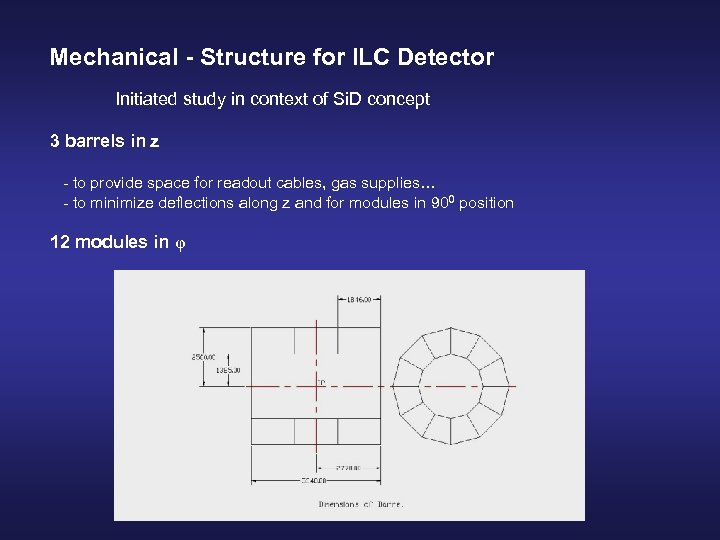

Mechanical - Structure for ILC Detector Initiated study in context of Si. D concept 3 barrels in z - to provide space for readout cables, gas supplies… - to minimize deflections along z and for modules in 900 position 12 modules in φ

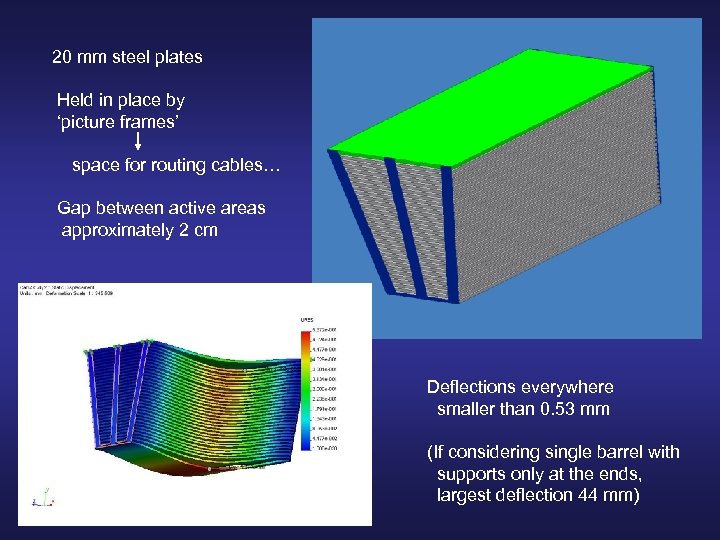

20 mm steel plates Held in place by ‘picture frames’ space for routing cables… Gap between active areas approximately 2 cm Deflections everywhere smaller than 0. 53 mm (If considering single barrel with supports only at the ends, largest deflection 44 mm)

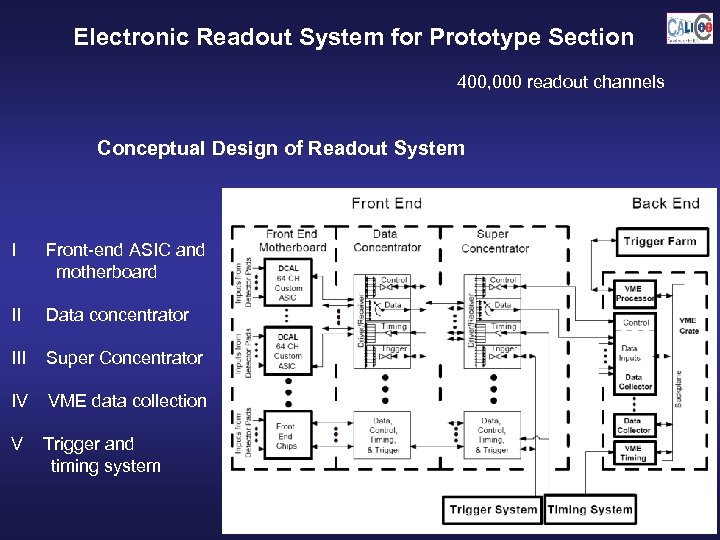

Electronic Readout System for Prototype Section 400, 000 readout channels Conceptual Design of Readout System I Front-end ASIC and motherboard II Data concentrator III Super Concentrator IV VME data collection V Trigger and timing system

Specification of system completed Document Written by Gary Drake (ANL) Released in September 2005 Contains all details of system Basis for design work of subsystems Counts 57 pages

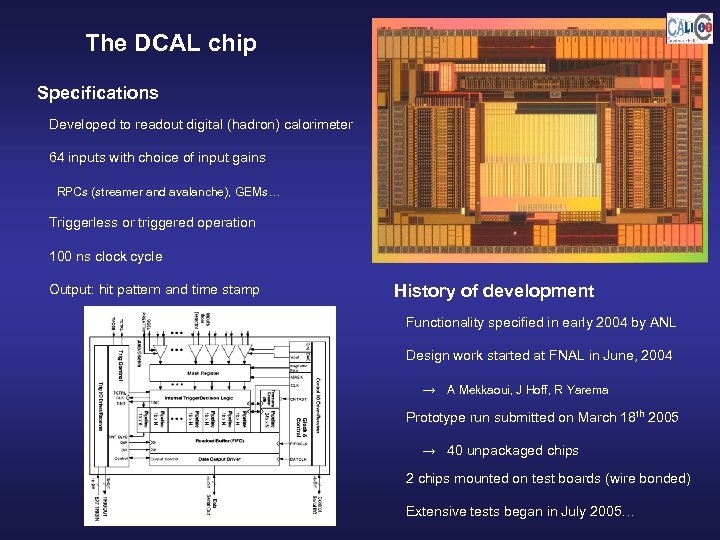

The DCAL chip Specifications Developed to readout digital (hadron) calorimeter 64 inputs with choice of input gains RPCs (streamer and avalanche), GEMs… Triggerless or triggered operation 100 ns clock cycle Output: hit pattern and time stamp History of development Functionality specified in early 2004 by ANL Design work started at FNAL in June, 2004 → A Mekkaoui, J Hoff, R Yarema Prototype run submitted on March 18 th 2005 → 40 unpackaged chips 2 chips mounted on test boards (wire bonded) Extensive tests began in July 2005…

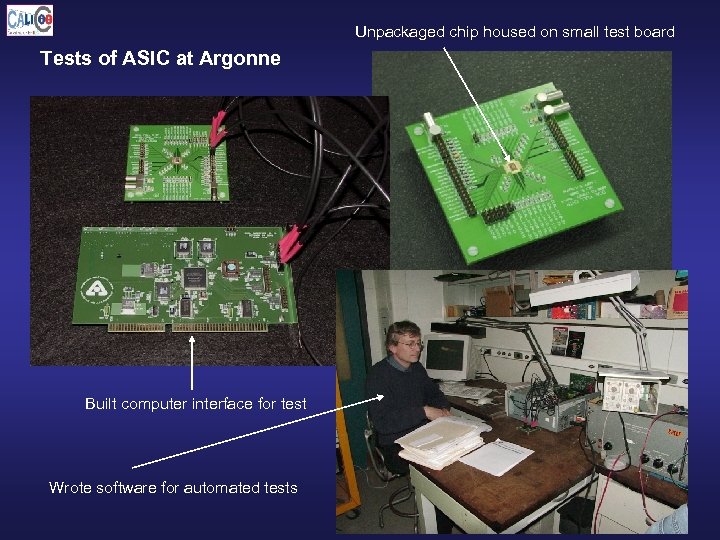

Unpackaged chip housed on small test board Tests of ASIC at Argonne Built computer interface for test Wrote software for automated tests

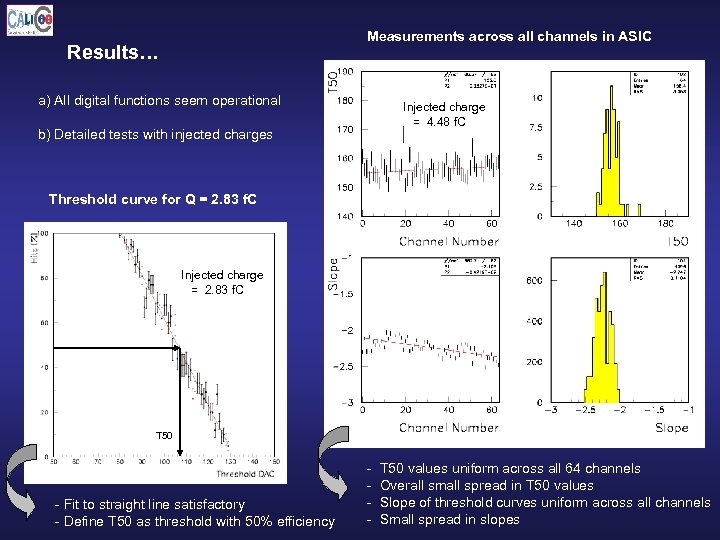

Measurements across all channels in ASIC Results… a) All digital functions seem operational Injected charge = 4. 48 f. C b) Detailed tests with injected charges Threshold curve for Q = 2. 83 f. C Injected charge = 2. 83 f. C T 50 - Fit to straight line satisfactory - Define T 50 as threshold with 50% efficiency - T 50 values uniform across all 64 channels Overall small spread in T 50 values Slope of threshold curves uniform across all channels Small spread in slopes

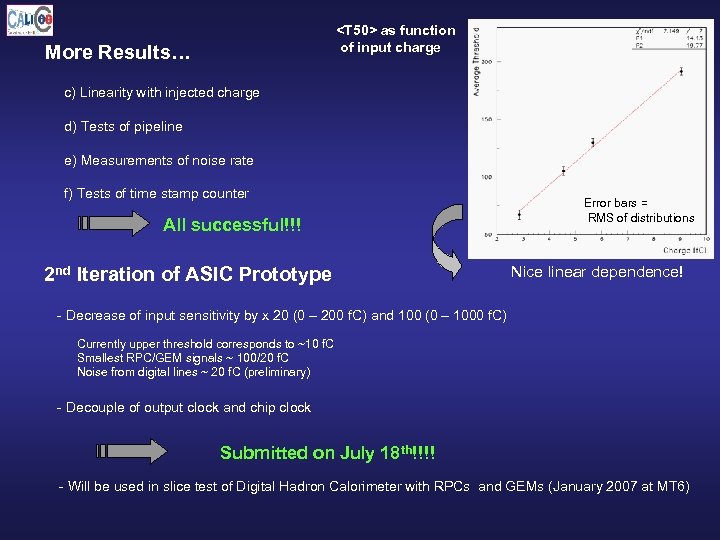

<T 50> as function of input charge More Results… c) Linearity with injected charge d) Tests of pipeline e) Measurements of noise rate f) Tests of time stamp counter All successful!!! 2 nd Iteration of ASIC Prototype Error bars = RMS of distributions Nice linear dependence! - Decrease of input sensitivity by x 20 (0 – 200 f. C) and 100 (0 – 1000 f. C) Currently upper threshold corresponds to ~10 f. C Smallest RPC/GEM signals ~ 100/20 f. C Noise from digital lines ~ 20 f. C (preliminary) - Decouple of output clock and chip clock Submitted on July 18 th!!!! - Will be used in slice test of Digital Hadron Calorimeter with RPCs and GEMs (January 2007 at MT 6)

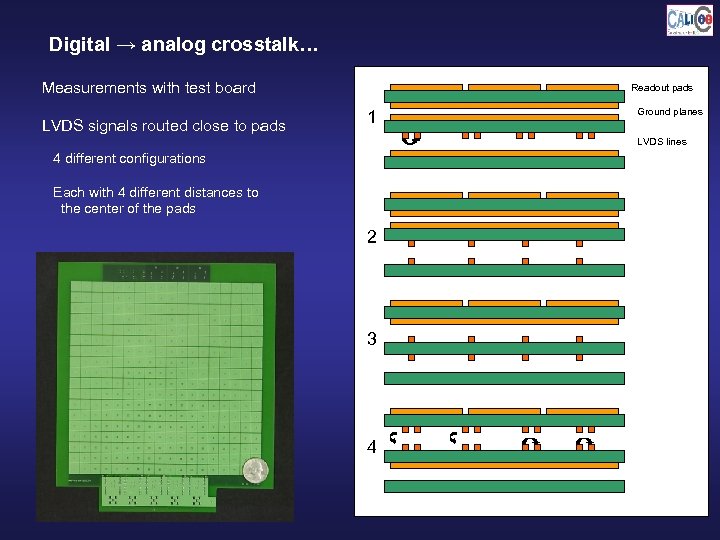

Digital → analog crosstalk… Measurements with test board LVDS signals routed close to pads Readout pads 1 Ground planes LVDS lines 4 different configurations Each with 4 different distances to the center of the pads 2 3 4

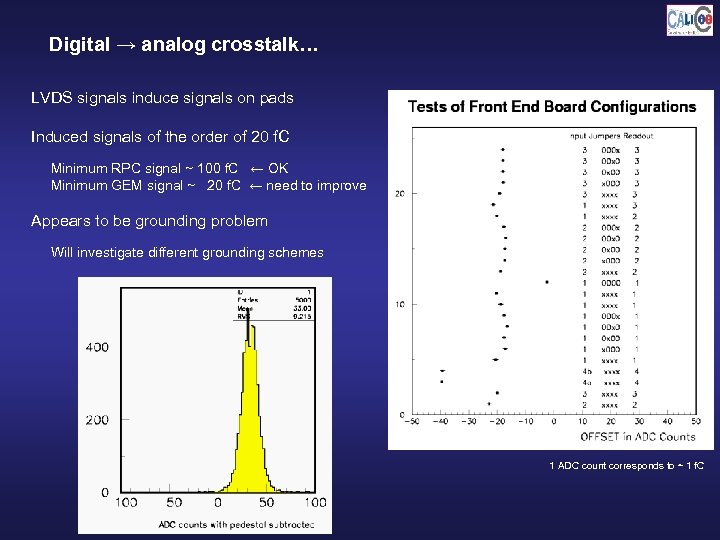

Digital → analog crosstalk… LVDS signals induce signals on pads Induced signals of the order of 20 f. C Minimum RPC signal ~ 100 f. C ← OK Minimum GEM signal ~ 20 f. C ← need to improve Appears to be grounding problem Will investigate different grounding schemes 1 ADC count corresponds to ~ 1 f. C

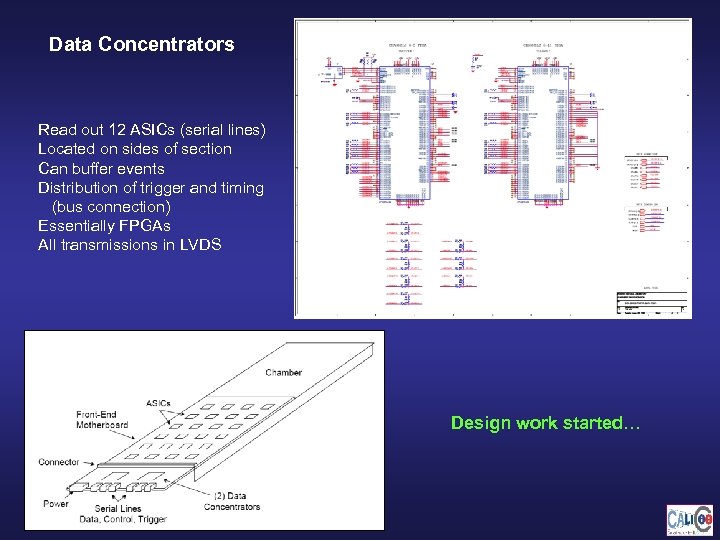

Data Concentrators Read out 12 ASICs (serial lines) Located on sides of section Can buffer events Distribution of trigger and timing (bus connection) Essentially FPGAs All transmissions in LVDS Design work started…

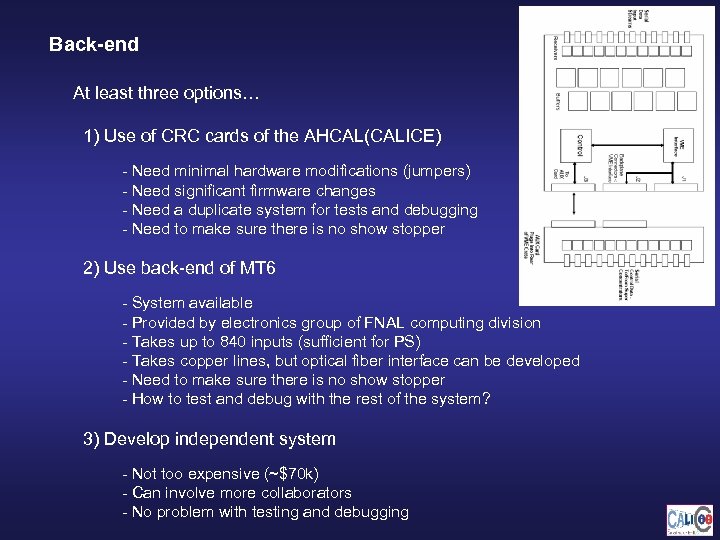

Back-end At least three options… 1) Use of CRC cards of the AHCAL(CALICE) - Need minimal hardware modifications (jumpers) - Need significant firmware changes - Need a duplicate system for tests and debugging - Need to make sure there is no show stopper 2) Use back-end of MT 6 - System available - Provided by electronics group of FNAL computing division - Takes up to 840 inputs (sufficient for PS) - Takes copper lines, but optical fiber interface can be developed - Need to make sure there is no show stopper - How to test and debug with the rest of the system? 3) Develop independent system - Not too expensive (~$70 k) - Can involve more collaborators - No problem with testing and debugging

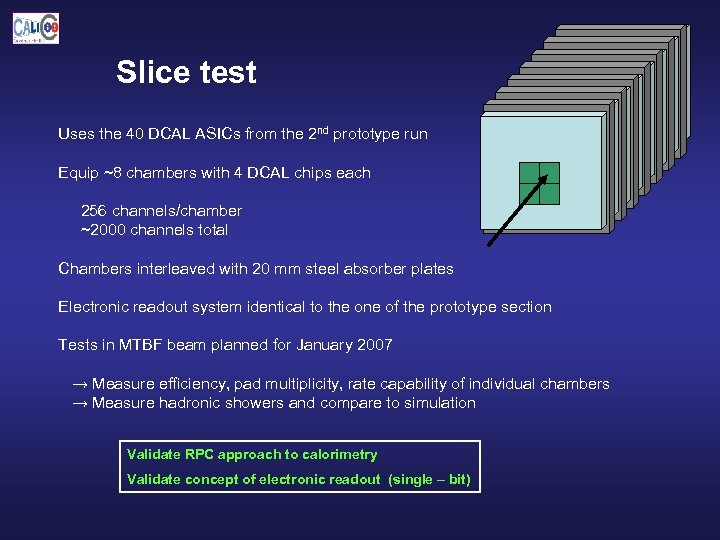

Slice test Uses the 40 DCAL ASICs from the 2 nd prototype run Equip ~8 chambers with 4 DCAL chips each 256 channels/chamber ~2000 channels total Chambers interleaved with 20 mm steel absorber plates Electronic readout system identical to the one of the prototype section Tests in MTBF beam planned for January 2007 → Measure efficiency, pad multiplicity, rate capability of individual chambers → Measure hadronic showers and compare to simulation Validate RPC approach to calorimetry Validate concept of electronic readout (single – bit)

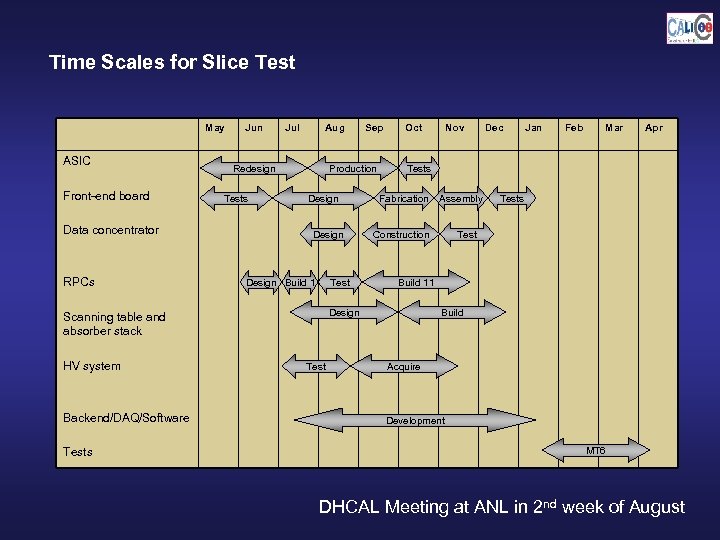

Time Scales for Slice Test May ASIC Front-end board Data concentrator RPCs Jun Jul Aug Redesign Tests Production Design Build 1 Test Backend/DAQ/Software Tests Oct Test Nov Dec Jan Feb Mar Apr Tests Fabrication Assembly Construction Tests Test Build 11 Design Scanning table and absorber stack HV system Sep Build Acquire Development MT 6 DHCAL Meeting at ANL in 2 nd week of August

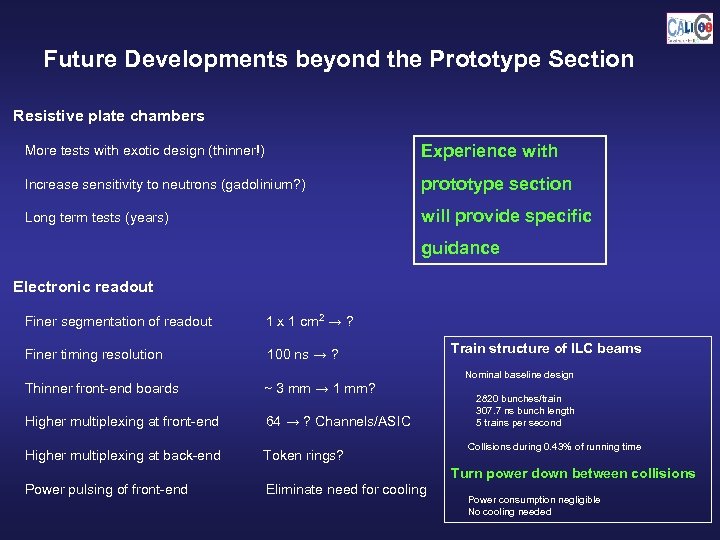

Future Developments beyond the Prototype Section Resistive plate chambers More tests with exotic design (thinner!) Experience with Increase sensitivity to neutrons (gadolinium? ) prototype section Long term tests (years) will provide specific guidance Electronic readout Finer segmentation of readout 1 x 1 cm 2 → ? Finer timing resolution 100 ns → ? Thinner front-end boards ~ 3 mm → 1 mm? Higher multiplexing at front-end 64 → ? Channels/ASIC Higher multiplexing at back-end Token rings? Power pulsing of front-end Eliminate need for cooling Train structure of ILC beams Nominal baseline design 2820 bunches/train 307. 7 ns bunch length 5 trains per second Collisions during 0. 43% of running time Turn power down between collisions Power consumption negligible No cooling needed

Funding for the Prototype Section Presidents budget request for 2007 ILC: $30 M (2006) → $60 M (2007) p. 339 LCRD funding looks good Received $98 k for RPC-DHCAL development → will pay for slice test Will submit proposal for supplemental funds → will pay for prototype section construction

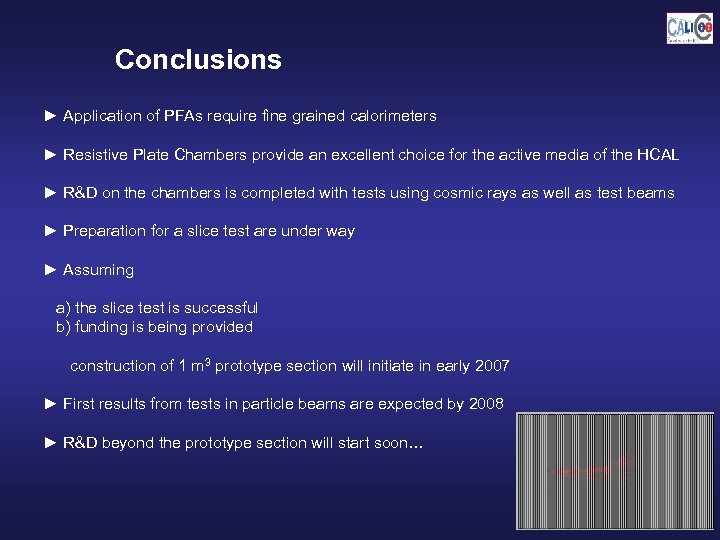

Conclusions ► Application of PFAs require fine grained calorimeters ► Resistive Plate Chambers provide an excellent choice for the active media of the HCAL ► R&D on the chambers is completed with tests using cosmic rays as well as test beams ► Preparation for a slice test are under way ► Assuming a) the slice test is successful b) funding is being provided construction of 1 m 3 prototype section will initiate in early 2007 ► First results from tests in particle beams are expected by 2008 ► R&D beyond the prototype section will start soon…

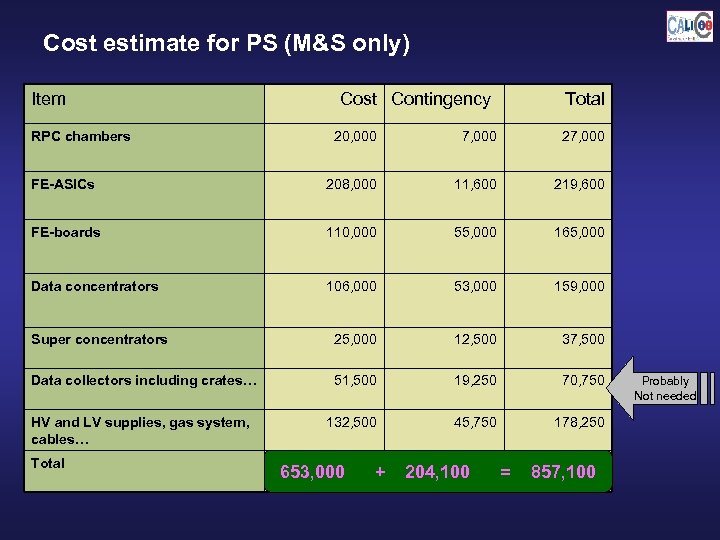

Cost estimate for PS (M&S only) Item RPC chambers Cost Contingency Total 20, 000 7, 000 27, 000 FE-ASICs 208, 000 11, 600 219, 600 FE-boards 110, 000 55, 000 165, 000 Data concentrators 106, 000 53, 000 159, 000 Super concentrators 25, 000 12, 500 37, 500 Data collectors including crates… 51, 500 19, 250 70, 750 HV and LV supplies, gas system, cables… 132, 500 45, 750 178, 250 Total 653, 000 + 204, 100 = 857, 100 Probably Not needed

7783d950534ec861295e3f5eca1950ba.ppt