db7cb922b934423d88ad2185318a415c.ppt

- Количество слайдов: 1

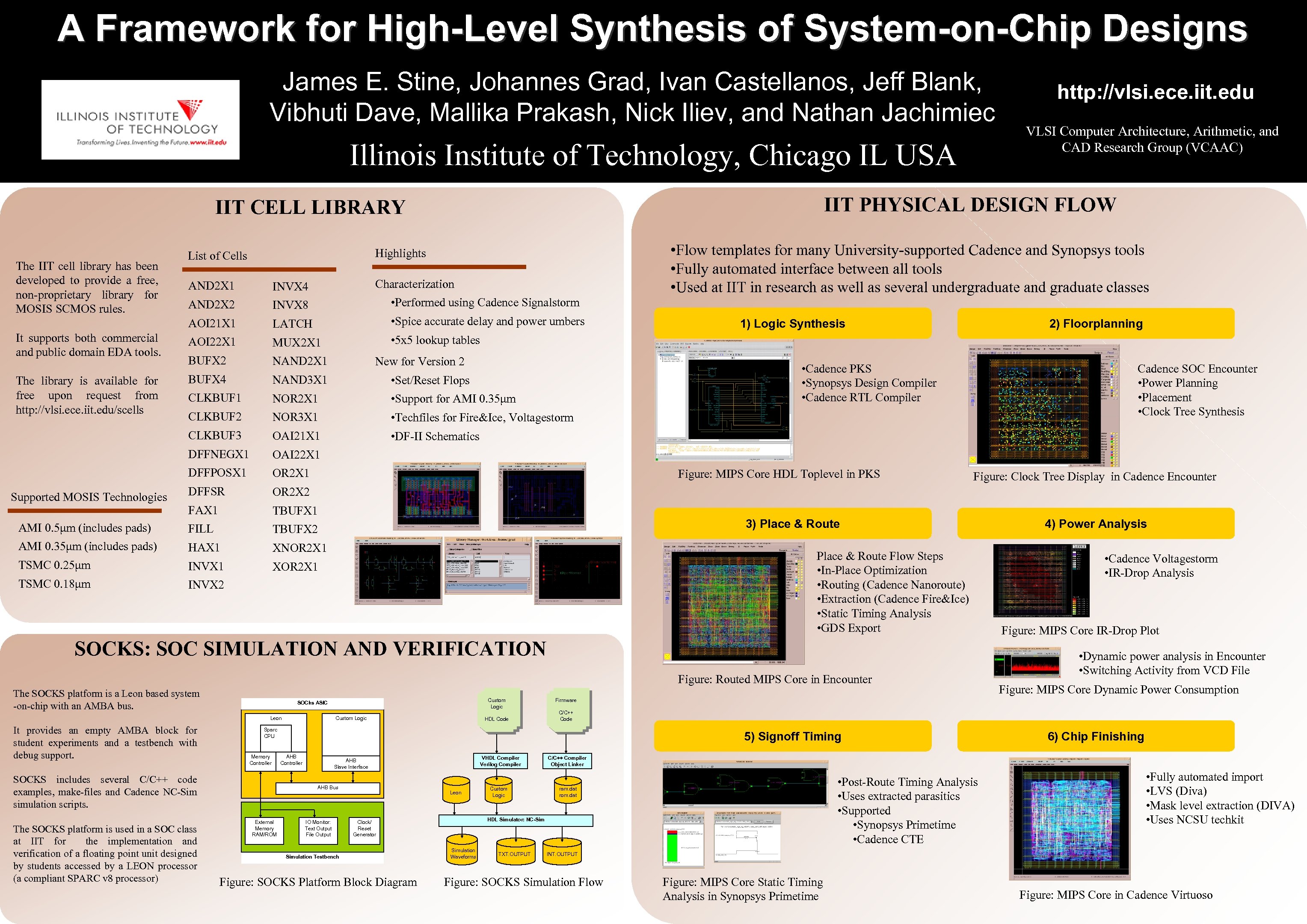

A Framework for High-Level Synthesis of System-on-Chip Designs James E. Stine, Johannes Grad, Ivan Castellanos, Jeff Blank, Vibhuti Dave, Mallika Prakash, Nick Iliev, and Nathan Jachimiec ` Illinois Institute of Technology, Chicago IL USA The IIT cell library has been developed to provide a free, non-proprietary library for MOSIS SCMOS rules. VLSI Computer Architecture, Arithmetic, and CAD Research Group (VCAAC) IIT PHYSICAL DESIGN FLOW IIT CELL LIBRARY • Flow templates for many University-supported Cadence and Synopsys tools • Fully automated interface between all tools • Used at IIT in research as well as several undergraduate and graduate classes Highlights List of Cells http: //vlsi. ece. iit. edu Characterization AND 2 X 1 INVX 4 AND 2 X 2 INVX 8 • Performed using Cadence Signalstorm AOI 21 X 1 LATCH • Spice accurate delay and power umbers AOI 22 X 1 MUX 2 X 1 • 5 x 5 lookup tables BUFX 2 NAND 2 X 1 BUFX 4 NAND 3 X 1 • Set/Reset Flops CLKBUF 1 NOR 2 X 1 • Support for AMI 0. 35μm CLKBUF 2 NOR 3 X 1 • Techfiles for Fire&Ice, Voltagestorm CLKBUF 3 OAI 21 X 1 • DF-II Schematics DFFNEGX 1 OAI 22 X 1 DFFPOSX 1 OR 2 X 1 DFFSR OR 2 X 2 FAX 1 TBUFX 1 AMI 0. 5μm (includes pads) FILL TBUFX 2 AMI 0. 35μm (includes pads) HAX 1 XNOR 2 X 1 TSMC 0. 25μm INVX 1 XOR 2 X 1 TSMC 0. 18μm INVX 2 It supports both commercial and public domain EDA tools. The library is available for free upon request from http: //vlsi. ece. iit. edu/scells Supported MOSIS Technologies New for Version 2 1) Logic Synthesis 2) Floorplanning • Cadence PKS • Synopsys Design Compiler • Cadence RTL Compiler Figure: MIPS Core HDL Toplevel in PKS Cadence SOC Encounter • Power Planning • Placement • Clock Tree Synthesis Figure: Clock Tree Display in Cadence Encounter 3) Place & Route Flow Steps • In-Place Optimization • Routing (Cadence Nanoroute) • Extraction (Cadence Fire&Ice) • Static Timing Analysis • GDS Export SOCKS: SOC SIMULATION AND VERIFICATION Figure: Routed MIPS Core in Encounter The SOCKS platform is a Leon based system -on-chip with an AMBA bus. Leon It provides an empty AMBA block for student experiments and a testbench with debug support. Custom Logic HDL Code Memory Controller AHB Bus External Memory RAM/ROM VHDL Compiler Verilog Compiler AHB Slave Interface IO Monitor: Text Output File Output Leon Figure: SOCKS Platform Block Diagram Simulation Waveforms TXT. OUTPUT • Dynamic power analysis in Encounter • Switching Activity from VCD File Figure: MIPS Core Dynamic Power Consumption 6) Chip Finishing C/C++ Compiler Object Linker • Post-Route Timing Analysis • Uses extracted parasitics • Supported • Synopsys Primetime • Cadence CTE ram. dat rom. dat HDL Simulator: NC-Sim Clock/ Reset Generator Simulation Testbench Custom Logic Figure: MIPS Core IR-Drop Plot C/C++ Code 5) Signoff Timing AHB Controller • Cadence Voltagestorm • IR-Drop Analysis Firmware Sparc CPU SOCKS includes several C/C++ code examples, make-files and Cadence NC-Sim simulation scripts. The SOCKS platform is used in a SOC class at IIT for the implementation and verification of a floating point unit designed by students accessed by a LEON processor (a compliant SPARC v 8 processor) Custom Logic SOCks ASIC 4) Power Analysis • Fully automated import • LVS (Diva) • Mask level extraction (DIVA) • Uses NCSU techkit INT. OUTPUT Figure: SOCKS Simulation Flow Figure: MIPS Core Static Timing Analysis in Synopsys Primetime Figure: MIPS Core in Cadence Virtuoso

A Framework for High-Level Synthesis of System-on-Chip Designs James E. Stine, Johannes Grad, Ivan Castellanos, Jeff Blank, Vibhuti Dave, Mallika Prakash, Nick Iliev, and Nathan Jachimiec ` Illinois Institute of Technology, Chicago IL USA The IIT cell library has been developed to provide a free, non-proprietary library for MOSIS SCMOS rules. VLSI Computer Architecture, Arithmetic, and CAD Research Group (VCAAC) IIT PHYSICAL DESIGN FLOW IIT CELL LIBRARY • Flow templates for many University-supported Cadence and Synopsys tools • Fully automated interface between all tools • Used at IIT in research as well as several undergraduate and graduate classes Highlights List of Cells http: //vlsi. ece. iit. edu Characterization AND 2 X 1 INVX 4 AND 2 X 2 INVX 8 • Performed using Cadence Signalstorm AOI 21 X 1 LATCH • Spice accurate delay and power umbers AOI 22 X 1 MUX 2 X 1 • 5 x 5 lookup tables BUFX 2 NAND 2 X 1 BUFX 4 NAND 3 X 1 • Set/Reset Flops CLKBUF 1 NOR 2 X 1 • Support for AMI 0. 35μm CLKBUF 2 NOR 3 X 1 • Techfiles for Fire&Ice, Voltagestorm CLKBUF 3 OAI 21 X 1 • DF-II Schematics DFFNEGX 1 OAI 22 X 1 DFFPOSX 1 OR 2 X 1 DFFSR OR 2 X 2 FAX 1 TBUFX 1 AMI 0. 5μm (includes pads) FILL TBUFX 2 AMI 0. 35μm (includes pads) HAX 1 XNOR 2 X 1 TSMC 0. 25μm INVX 1 XOR 2 X 1 TSMC 0. 18μm INVX 2 It supports both commercial and public domain EDA tools. The library is available for free upon request from http: //vlsi. ece. iit. edu/scells Supported MOSIS Technologies New for Version 2 1) Logic Synthesis 2) Floorplanning • Cadence PKS • Synopsys Design Compiler • Cadence RTL Compiler Figure: MIPS Core HDL Toplevel in PKS Cadence SOC Encounter • Power Planning • Placement • Clock Tree Synthesis Figure: Clock Tree Display in Cadence Encounter 3) Place & Route Flow Steps • In-Place Optimization • Routing (Cadence Nanoroute) • Extraction (Cadence Fire&Ice) • Static Timing Analysis • GDS Export SOCKS: SOC SIMULATION AND VERIFICATION Figure: Routed MIPS Core in Encounter The SOCKS platform is a Leon based system -on-chip with an AMBA bus. Leon It provides an empty AMBA block for student experiments and a testbench with debug support. Custom Logic HDL Code Memory Controller AHB Bus External Memory RAM/ROM VHDL Compiler Verilog Compiler AHB Slave Interface IO Monitor: Text Output File Output Leon Figure: SOCKS Platform Block Diagram Simulation Waveforms TXT. OUTPUT • Dynamic power analysis in Encounter • Switching Activity from VCD File Figure: MIPS Core Dynamic Power Consumption 6) Chip Finishing C/C++ Compiler Object Linker • Post-Route Timing Analysis • Uses extracted parasitics • Supported • Synopsys Primetime • Cadence CTE ram. dat rom. dat HDL Simulator: NC-Sim Clock/ Reset Generator Simulation Testbench Custom Logic Figure: MIPS Core IR-Drop Plot C/C++ Code 5) Signoff Timing AHB Controller • Cadence Voltagestorm • IR-Drop Analysis Firmware Sparc CPU SOCKS includes several C/C++ code examples, make-files and Cadence NC-Sim simulation scripts. The SOCKS platform is used in a SOC class at IIT for the implementation and verification of a floating point unit designed by students accessed by a LEON processor (a compliant SPARC v 8 processor) Custom Logic SOCks ASIC 4) Power Analysis • Fully automated import • LVS (Diva) • Mask level extraction (DIVA) • Uses NCSU techkit INT. OUTPUT Figure: SOCKS Simulation Flow Figure: MIPS Core Static Timing Analysis in Synopsys Primetime Figure: MIPS Core in Cadence Virtuoso