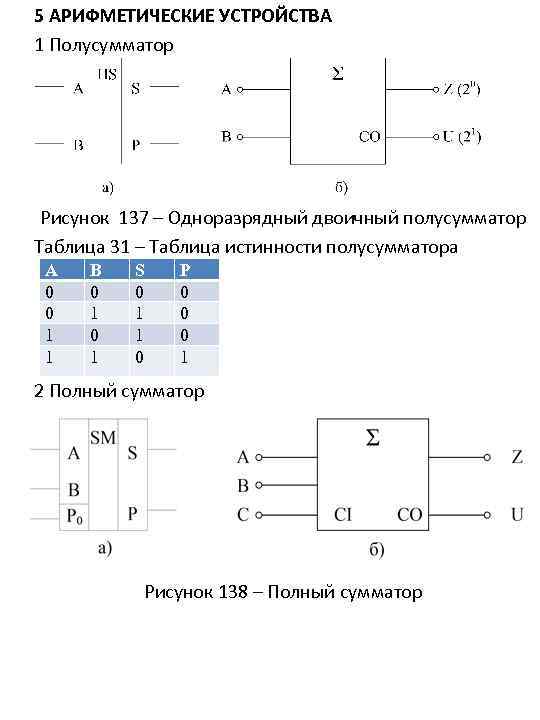

5 АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА 1 Полусумматор Рисунок 137 – Одноразрядный двоичный полусумматор Таблица 31 – Таблица истинности полусумматора А 0 0 1 1 В 0 1 S 0 1 1 0 Р 0 0 0 1 2 Полный сумматор Рисунок 138 – Полный сумматор

5 АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА 1 Полусумматор Рисунок 137 – Одноразрядный двоичный полусумматор Таблица 31 – Таблица истинности полусумматора А 0 0 1 1 В 0 1 S 0 1 1 0 Р 0 0 0 1 2 Полный сумматор Рисунок 138 – Полный сумматор

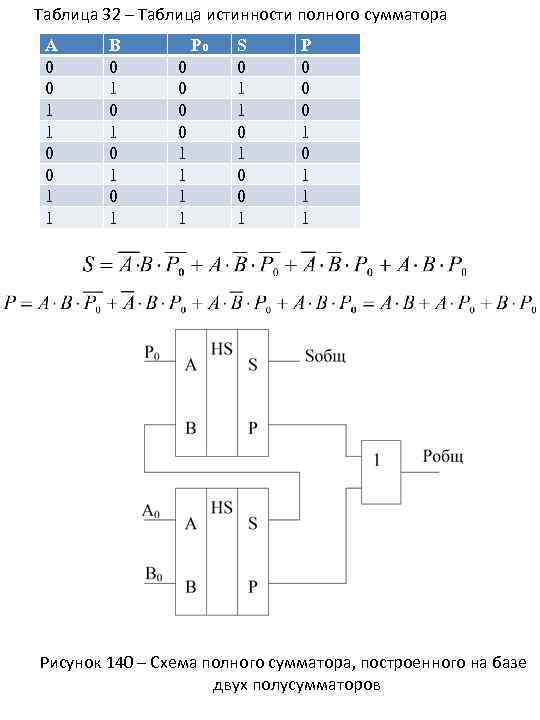

Таблица 32 – Таблица истинности полного сумматора А 0 0 1 1 В 0 1 0 1 Po 0 0 1 1 S 0 1 1 0 0 1 Р 0 0 0 1 1 1 Рисунок 140 – Схема полного сумматора, построенного на базе двух полусумматоров

Таблица 32 – Таблица истинности полного сумматора А 0 0 1 1 В 0 1 0 1 Po 0 0 1 1 S 0 1 1 0 0 1 Р 0 0 0 1 1 1 Рисунок 140 – Схема полного сумматора, построенного на базе двух полусумматоров

3 Сумматор с последовательным переносом Рисунок 141 – Сумматор с последовательным переносом 4 Последовательный сумматор Рисунок 142 – Последовательный сумматор

3 Сумматор с последовательным переносом Рисунок 141 – Сумматор с последовательным переносом 4 Последовательный сумматор Рисунок 142 – Последовательный сумматор

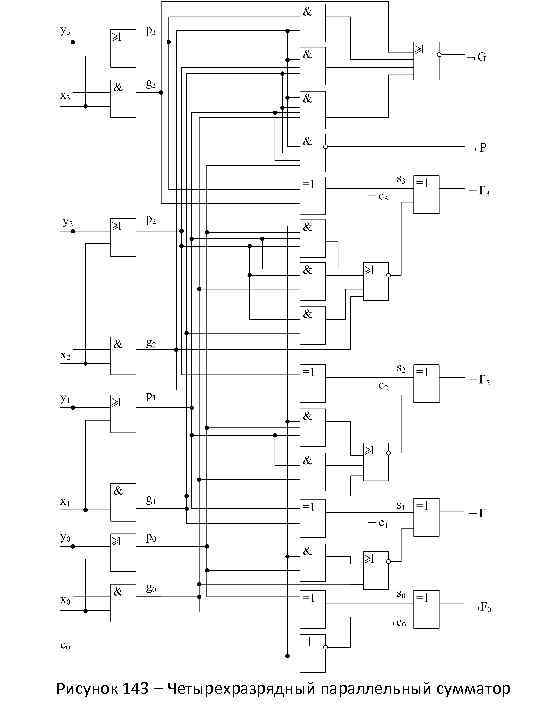

Рисунок 143 – Четырехразрядный параллельный сумматор

Рисунок 143 – Четырехразрядный параллельный сумматор

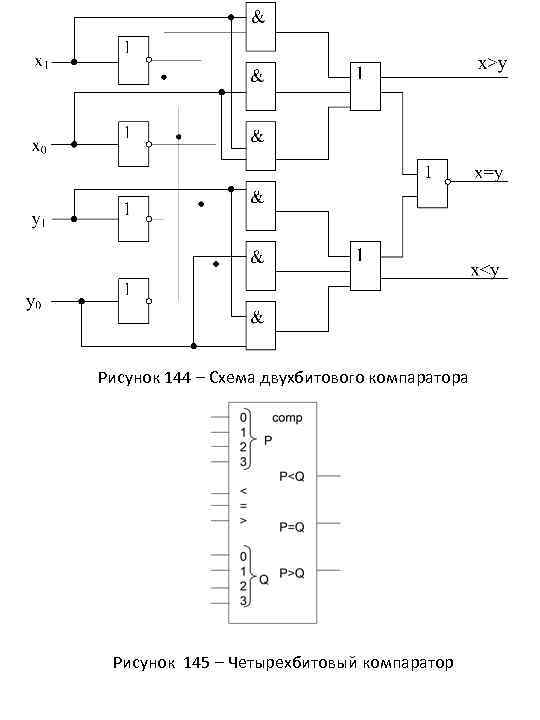

5 Цифровые компараторы Таблица 34 – Таблица истинности двухбитового компаратора у1 0 0 0 0 1 1 1 1 у0 0 0 1 1 х1 0 0 1 1 х0 0 1 0 1 х=у 1 0 0 0 0 1 х<у 0 0 1 0 0 0 1 1 1 0 х>у 0 1 1 1 0 0 0 1 0 0 DECy 0 0 1 1 2 2 3 3 DECx 0 1 2 3

5 Цифровые компараторы Таблица 34 – Таблица истинности двухбитового компаратора у1 0 0 0 0 1 1 1 1 у0 0 0 1 1 х1 0 0 1 1 х0 0 1 0 1 х=у 1 0 0 0 0 1 х<у 0 0 1 0 0 0 1 1 1 0 х>у 0 1 1 1 0 0 0 1 0 0 DECy 0 0 1 1 2 2 3 3 DECx 0 1 2 3

Условимся, что х=у – это =; х<у – это <; х>у – это >. Карта Карно будет иметь вид:

Условимся, что х=у – это =; х<у – это <; х>у – это >. Карта Карно будет иметь вид:

Рисунок 144 – Схема двухбитового компаратора Рисунок 145 – Четырехбитовый компаратор

Рисунок 144 – Схема двухбитового компаратора Рисунок 145 – Четырехбитовый компаратор

Рисунок 146 – Схема каскадируемого компаратора

Рисунок 146 – Схема каскадируемого компаратора

1 Схема контроля четности для трехразрядной передающей шины. Таблица 35 – Таблица истинности для схемы контроля четности х2 0 0 1 1 х1 0 0 1 1 х0 0 1 0 1 Четн. 1 0 0 1 1 0 Нечетн. 0 1 1 0 0 1

1 Схема контроля четности для трехразрядной передающей шины. Таблица 35 – Таблица истинности для схемы контроля четности х2 0 0 1 1 х1 0 0 1 1 х0 0 1 0 1 Четн. 1 0 0 1 1 0 Нечетн. 0 1 1 0 0 1

Рисунок 147 – Схема контроля четности на элементах равнозначности

Рисунок 147 – Схема контроля четности на элементах равнозначности