b88579ada3c0896a364cbb1349382d39.ppt

- Количество слайдов: 47

41 st DAC Tuesday Keynote

41 st DAC Tuesday Keynote

Giga-scale Integration for Tera-Ops Performance Opportunities and New Frontiers Pat Gelsinger Senior Vice President & CTO Intel Corporation June 8, 2004

Giga-scale Integration for Tera-Ops Performance Opportunities and New Frontiers Pat Gelsinger Senior Vice President & CTO Intel Corporation June 8, 2004

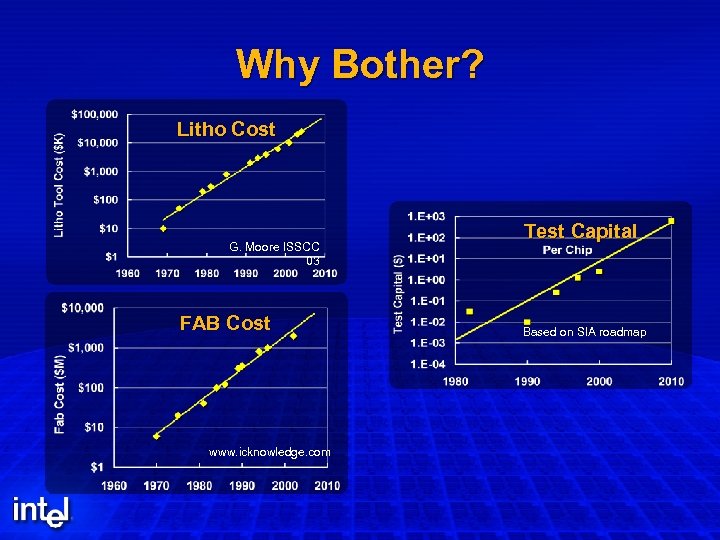

Why Bother? Litho Cost G. Moore ISSCC 03 FAB Cost www. icknowledge. com Test Capital Based on SIA roadmap

Why Bother? Litho Cost G. Moore ISSCC 03 FAB Cost www. icknowledge. com Test Capital Based on SIA roadmap

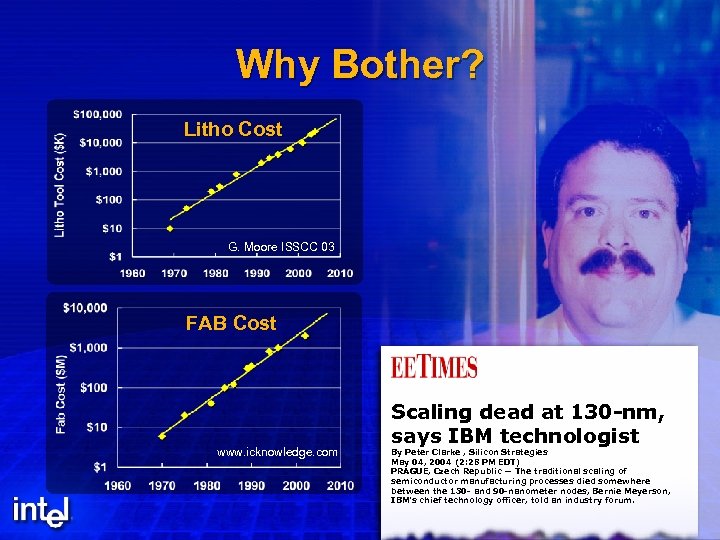

Why Bother? Litho Cost G. Moore ISSCC 03 FAB Cost www. icknowledge. com Scaling dead at 130 -nm, says IBM technologist By Peter Clarke , Silicon Strategies May 04, 2004 (2: 28 PM EDT) PRAGUE, Czech Republic — The traditional scaling of semiconductor manufacturing processes died somewhere between the 130 - and 90 -nanometer nodes, Bernie Meyerson, IBM's chief technology officer, told an industry forum.

Why Bother? Litho Cost G. Moore ISSCC 03 FAB Cost www. icknowledge. com Scaling dead at 130 -nm, says IBM technologist By Peter Clarke , Silicon Strategies May 04, 2004 (2: 28 PM EDT) PRAGUE, Czech Republic — The traditional scaling of semiconductor manufacturing processes died somewhere between the 130 - and 90 -nanometer nodes, Bernie Meyerson, IBM's chief technology officer, told an industry forum.

Believe in the Law $ per MIPS $ per Transistor No exponential is forever, but you can delay forever… –Gordon Moore

Believe in the Law $ per MIPS $ per Transistor No exponential is forever, but you can delay forever… –Gordon Moore

Direction For The Future

Direction For The Future

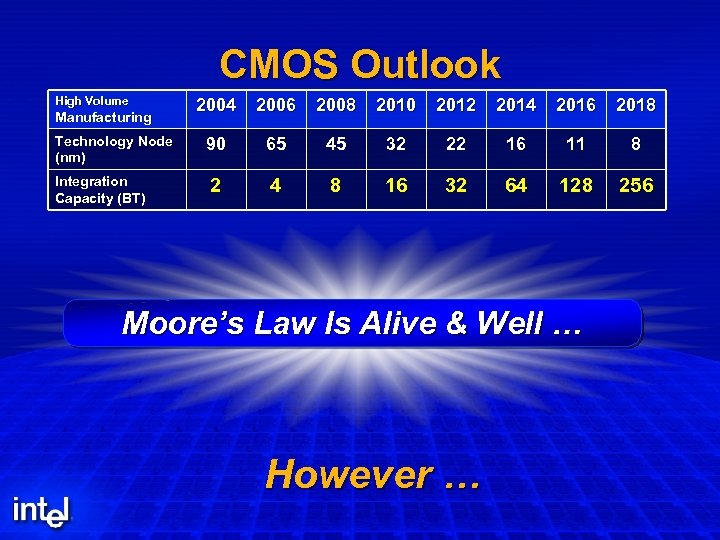

CMOS Outlook High Volume Manufacturing Technology Node (nm) Integration Capacity (BT) 2004 2006 2008 2010 2012 2014 2016 2018 90 65 45 32 22 16 11 8 2 4 8 16 32 64 128 256 Moore’s Law Is Alive & Well … However …

CMOS Outlook High Volume Manufacturing Technology Node (nm) Integration Capacity (BT) 2004 2006 2008 2010 2012 2014 2016 2018 90 65 45 32 22 16 11 8 2 4 8 16 32 64 128 256 Moore’s Law Is Alive & Well … However …

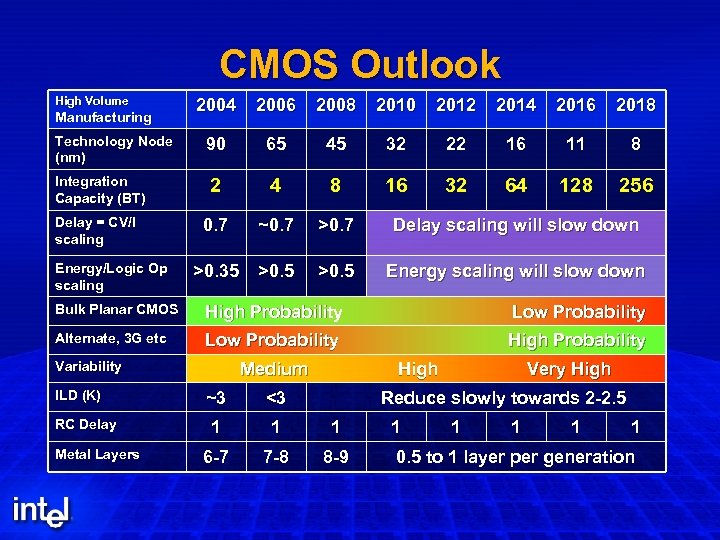

CMOS Outlook High Volume Manufacturing Technology Node (nm) Integration Capacity (BT) Delay = CV/I scaling Energy/Logic Op scaling 2004 2006 2008 2010 2012 2014 2016 2018 90 65 45 32 22 16 11 8 2 4 8 16 32 64 128 256 0. 7 ~0. 7 >0. 7 Delay scaling will slow down >0. 35 >0. 5 Energy scaling will slow down Bulk Planar CMOS High Probability Low Probability Alternate, 3 G etc Low Probability High Probability Variability ILD (K) RC Delay Metal Layers Medium High ~3 <3 1 1 1 6 -7 7 -8 8 -9 Very High Reduce slowly towards 2 -2. 5 1 1 1 0. 5 to 1 layer per generation

CMOS Outlook High Volume Manufacturing Technology Node (nm) Integration Capacity (BT) Delay = CV/I scaling Energy/Logic Op scaling 2004 2006 2008 2010 2012 2014 2016 2018 90 65 45 32 22 16 11 8 2 4 8 16 32 64 128 256 0. 7 ~0. 7 >0. 7 Delay scaling will slow down >0. 35 >0. 5 Energy scaling will slow down Bulk Planar CMOS High Probability Low Probability Alternate, 3 G etc Low Probability High Probability Variability ILD (K) RC Delay Metal Layers Medium High ~3 <3 1 1 1 6 -7 7 -8 8 -9 Very High Reduce slowly towards 2 -2. 5 1 1 1 0. 5 to 1 layer per generation

Guiding Observations Transistors (and silicon) are free Power is the only real limiter Optimizing for frequency AND/OR area may achieve neither

Guiding Observations Transistors (and silicon) are free Power is the only real limiter Optimizing for frequency AND/OR area may achieve neither

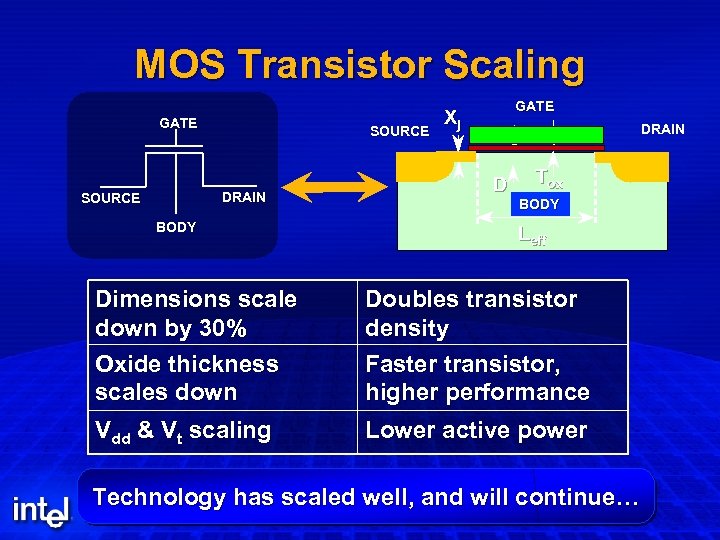

MOS Transistor Scaling GATE SOURCE DRAIN SOURCE BODY GATE Xj DRAIN D Tox BODY Leff Dimensions scale down by 30% Oxide thickness scales down Doubles transistor density Faster transistor, higher performance Vdd & Vt scaling Lower active power Technology has scaled well, and will continue…

MOS Transistor Scaling GATE SOURCE DRAIN SOURCE BODY GATE Xj DRAIN D Tox BODY Leff Dimensions scale down by 30% Oxide thickness scales down Doubles transistor density Faster transistor, higher performance Vdd & Vt scaling Lower active power Technology has scaled well, and will continue…

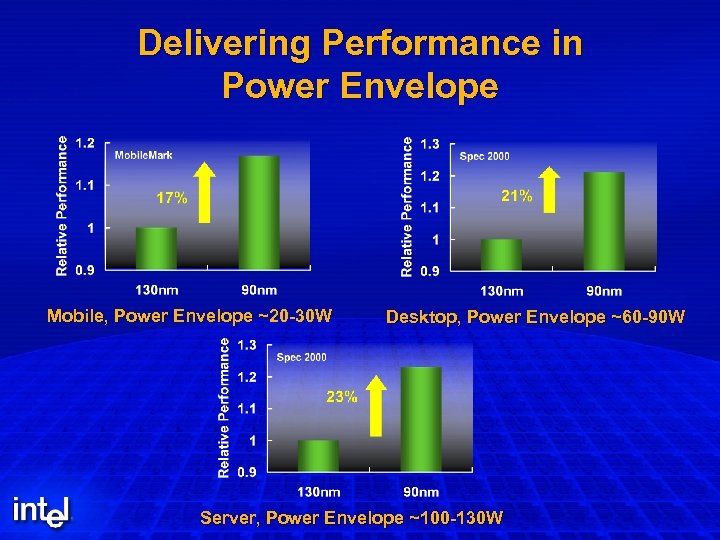

Delivering Performance in Power Envelope Mobile, Power Envelope ~20 -30 W Desktop, Power Envelope ~60 -90 W Server, Power Envelope ~100 -130 W

Delivering Performance in Power Envelope Mobile, Power Envelope ~20 -30 W Desktop, Power Envelope ~60 -90 W Server, Power Envelope ~100 -130 W

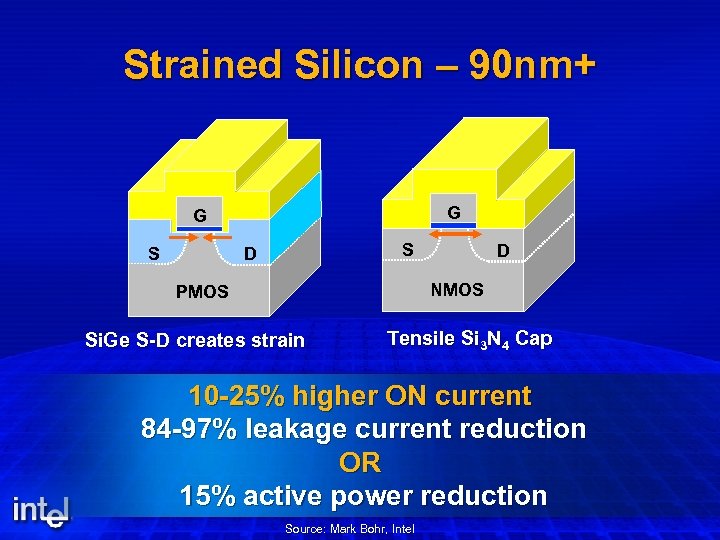

Strained Silicon – 90 nm+ G G S S D D NMOS PMOS Si. Ge S-D creates strain Tensile Si 3 N 4 Cap 10 -25% higher ON current 84 -97% leakage current reduction OR 15% active power reduction Source: Mark Bohr, Intel

Strained Silicon – 90 nm+ G G S S D D NMOS PMOS Si. Ge S-D creates strain Tensile Si 3 N 4 Cap 10 -25% higher ON current 84 -97% leakage current reduction OR 15% active power reduction Source: Mark Bohr, Intel

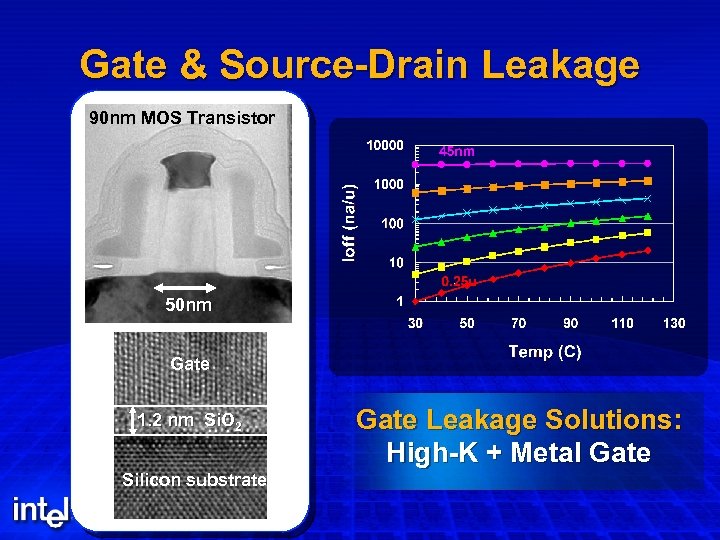

Gate & Source-Drain Leakage 90 nm MOS Transistor 50 nm Gate 1. 2 nm Si. O 2 Silicon substrate Gate Leakage Solutions: High-K + Metal Gate

Gate & Source-Drain Leakage 90 nm MOS Transistor 50 nm Gate 1. 2 nm Si. O 2 Silicon substrate Gate Leakage Solutions: High-K + Metal Gate

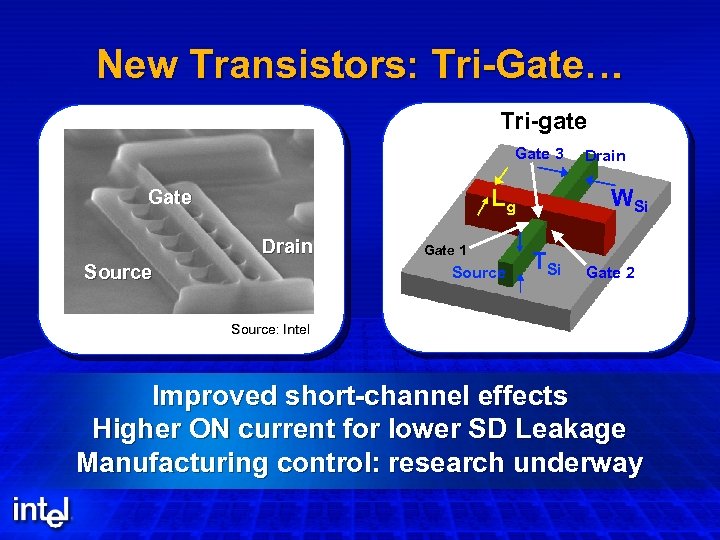

New Transistors: Tri-Gate… Tri-gate Gate 3 Lg Gate Drain Source Gate 1 Source Drain WSi TSi Gate 2 Source: Intel Improved short-channel effects Higher ON current for lower SD Leakage Manufacturing control: research underway

New Transistors: Tri-Gate… Tri-gate Gate 3 Lg Gate Drain Source Gate 1 Source Drain WSi TSi Gate 2 Source: Intel Improved short-channel effects Higher ON current for lower SD Leakage Manufacturing control: research underway

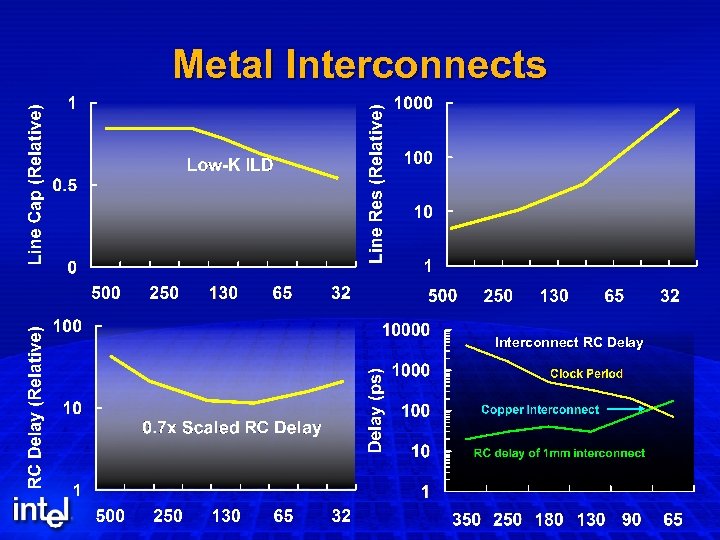

Metal Interconnects Interconnect RC Delay

Metal Interconnects Interconnect RC Delay

New Challenge: Variations Static & Dynamic

New Challenge: Variations Static & Dynamic

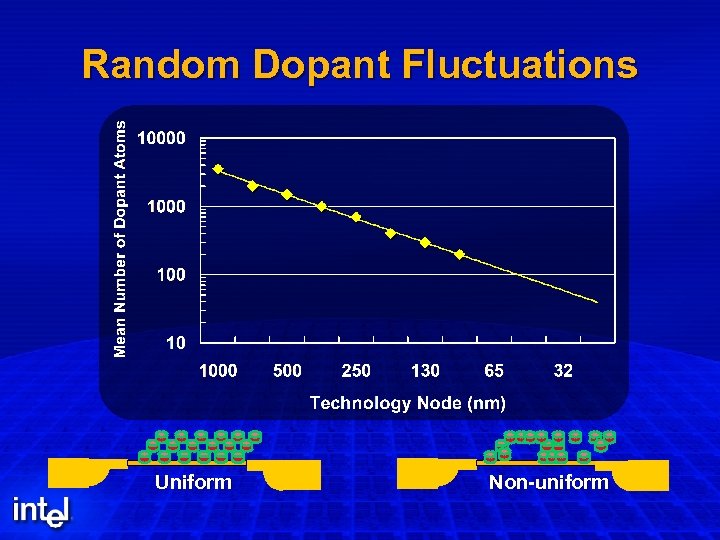

Random Dopant Fluctuations Uniform Non-uniform

Random Dopant Fluctuations Uniform Non-uniform

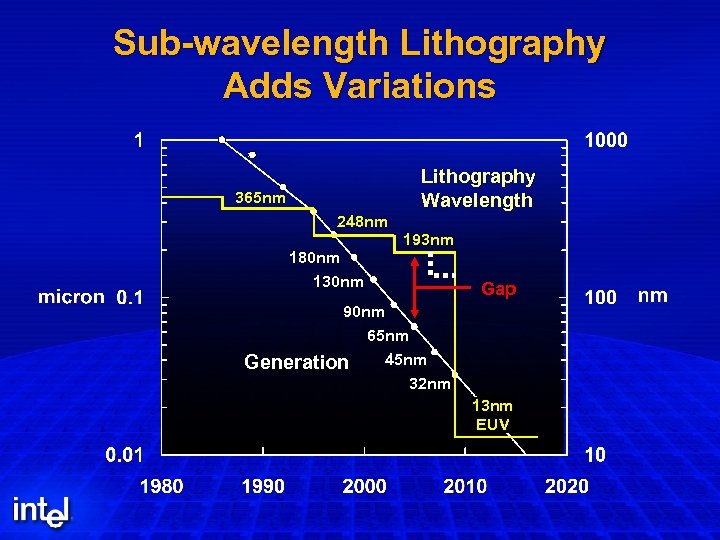

Sub-wavelength Lithography Adds Variations Lithography Wavelength 365 nm 248 nm 180 nm 130 nm 193 nm Gap 90 nm 65 nm 45 nm Generation 32 nm 13 nm EUV

Sub-wavelength Lithography Adds Variations Lithography Wavelength 365 nm 248 nm 180 nm 130 nm 193 nm Gap 90 nm 65 nm 45 nm Generation 32 nm 13 nm EUV

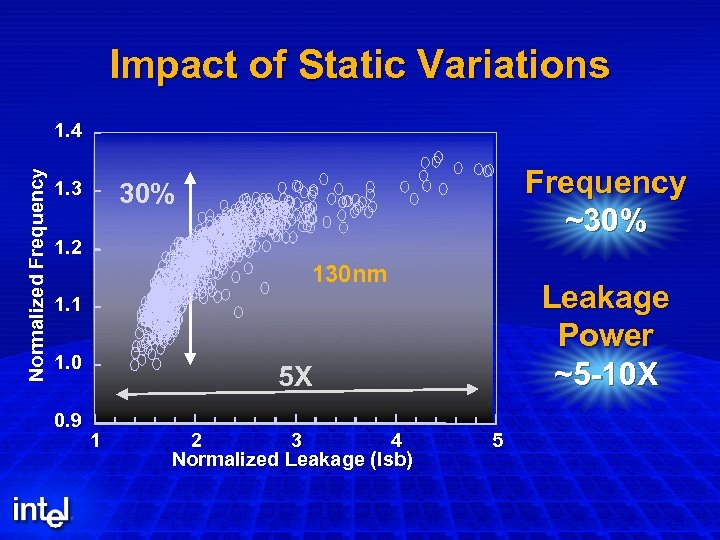

Impact of Static Variations Normalized Frequency 1. 4 1. 3 Frequency ~30% 1. 2 130 nm Leakage Power ~5 -10 X 1. 1 1. 0 0. 9 5 X 1 2 3 4 Normalized Leakage (Isb) 5

Impact of Static Variations Normalized Frequency 1. 4 1. 3 Frequency ~30% 1. 2 130 nm Leakage Power ~5 -10 X 1. 1 1. 0 0. 9 5 X 1 2 3 4 Normalized Leakage (Isb) 5

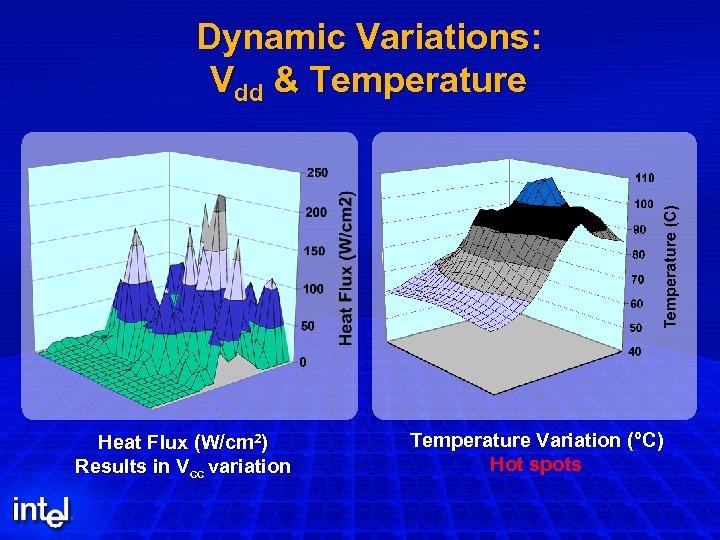

Dynamic Variations: Vdd & Temperature Heat Flux (W/cm 2) Results in Vcc variation Temperature Variation (°C) Hot spots

Dynamic Variations: Vdd & Temperature Heat Flux (W/cm 2) Results in Vcc variation Temperature Variation (°C) Hot spots

Technology Challenges Power: Active + Leakage Interconnects (RC Delay) Variations

Technology Challenges Power: Active + Leakage Interconnects (RC Delay) Variations

Design Methodology Is Changing…

Design Methodology Is Changing…

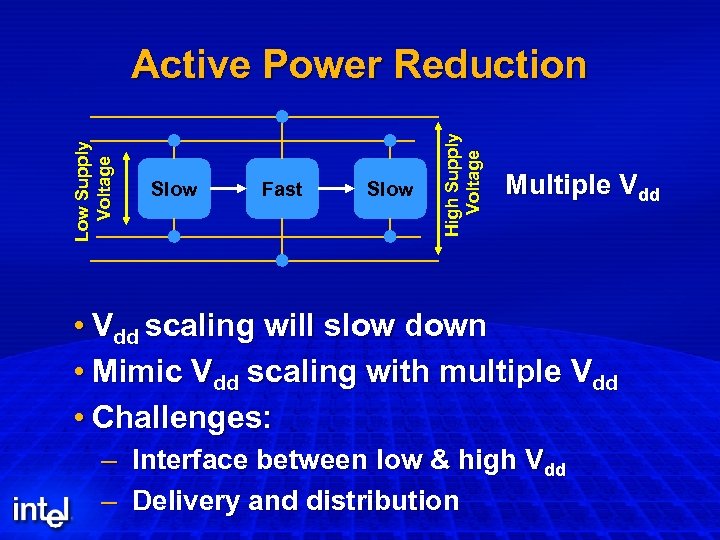

Slow Fast Slow High Supply Voltage Low Supply Voltage Active Power Reduction Multiple Vdd • Vdd scaling will slow down • Mimic Vdd scaling with multiple Vdd • Challenges: – Interface between low & high Vdd – Delivery and distribution

Slow Fast Slow High Supply Voltage Low Supply Voltage Active Power Reduction Multiple Vdd • Vdd scaling will slow down • Mimic Vdd scaling with multiple Vdd • Challenges: – Interface between low & high Vdd – Delivery and distribution

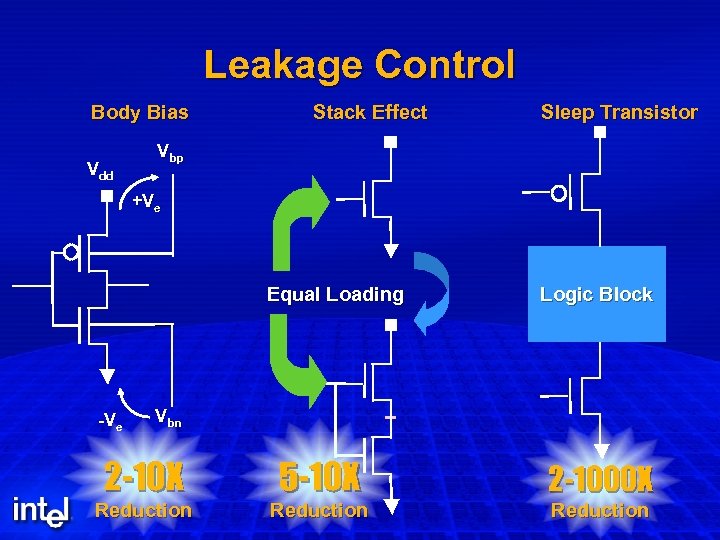

Leakage Control Body Bias Vdd Stack Effect Sleep Transistor Vbp +Ve Equal Loading -Ve Logic Block Vbn 2 -10 X Reduction 5 -10 X Reduction 2 -1000 X Reduction

Leakage Control Body Bias Vdd Stack Effect Sleep Transistor Vbp +Ve Equal Loading -Ve Logic Block Vbn 2 -10 X Reduction 5 -10 X Reduction 2 -1000 X Reduction

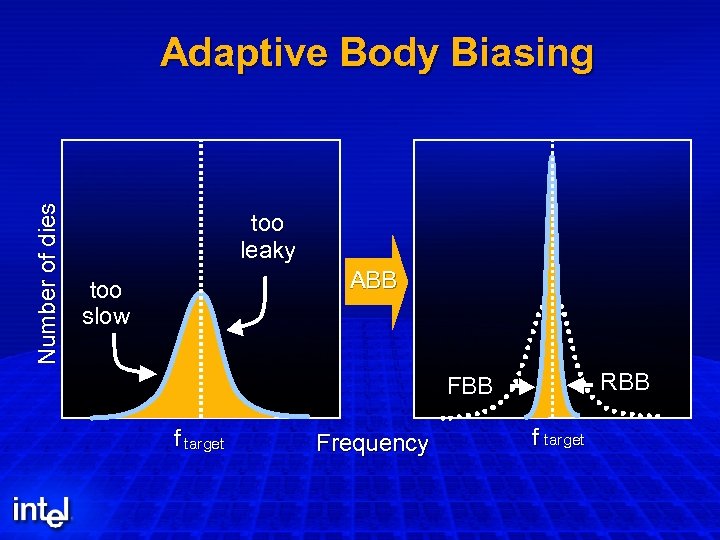

Number of dies Adaptive Body Biasing too leaky ABB too slow RBB FBB f target Frequency f target

Number of dies Adaptive Body Biasing too leaky ABB too slow RBB FBB f target Frequency f target

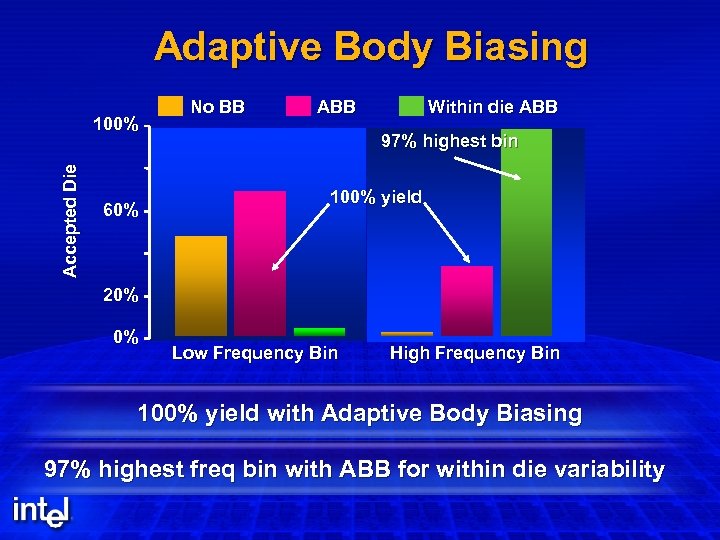

Adaptive Body Biasing Accepted Die 100% 60% No BB ABB Within die ABB 97% highest bin 100% yield 20% 0% Low Frequency Bin High Frequency Bin 100% yield with Adaptive Body Biasing 97% highest freq bin with ABB for within die variability

Adaptive Body Biasing Accepted Die 100% 60% No BB ABB Within die ABB 97% highest bin 100% yield 20% 0% Low Frequency Bin High Frequency Bin 100% yield with Adaptive Body Biasing 97% highest freq bin with ABB for within die variability

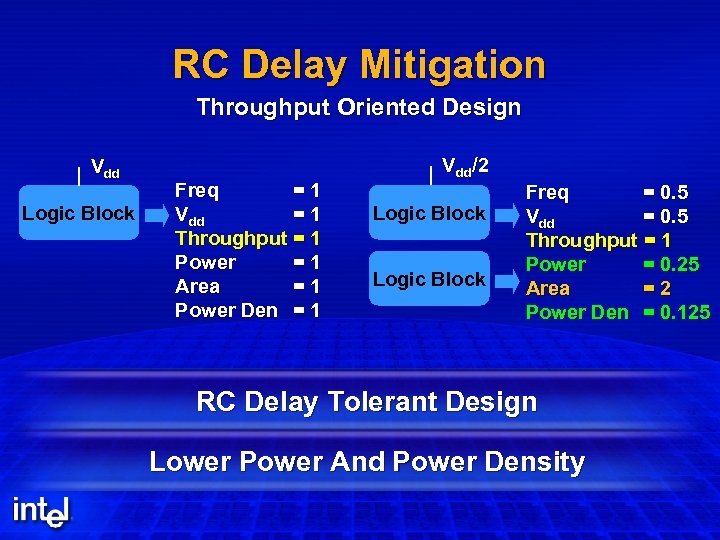

RC Delay Mitigation Throughput Oriented Design Vdd Logic Block Freq =1 Vdd =1 Throughput = 1 Power =1 Area =1 Power Den = 1 Vdd/2 Logic Block Freq = 0. 5 Vdd = 0. 5 Throughput = 1 Power = 0. 25 Area =2 Power Den = 0. 125 RC Delay Tolerant Design Lower Power And Power Density

RC Delay Mitigation Throughput Oriented Design Vdd Logic Block Freq =1 Vdd =1 Throughput = 1 Power =1 Area =1 Power Den = 1 Vdd/2 Logic Block Freq = 0. 5 Vdd = 0. 5 Throughput = 1 Power = 0. 25 Area =2 Power Den = 0. 125 RC Delay Tolerant Design Lower Power And Power Density

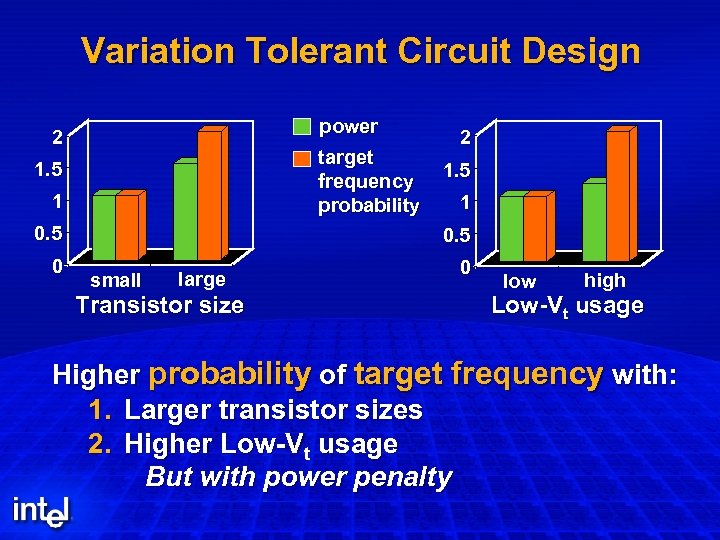

Variation Tolerant Circuit Design power 2 target frequency probability 1. 5 1 0. 5 0 2 1. 5 1 0. 5 small large Transistor size 0 low high Low-Vt usage Higher probability of target frequency with: 1. Larger transistor sizes 2. Higher Low-Vt usage But with power penalty

Variation Tolerant Circuit Design power 2 target frequency probability 1. 5 1 0. 5 0 2 1. 5 1 0. 5 small large Transistor size 0 low high Low-Vt usage Higher probability of target frequency with: 1. Larger transistor sizes 2. Higher Low-Vt usage But with power penalty

µ-architecture Is Also Changing…

µ-architecture Is Also Changing…

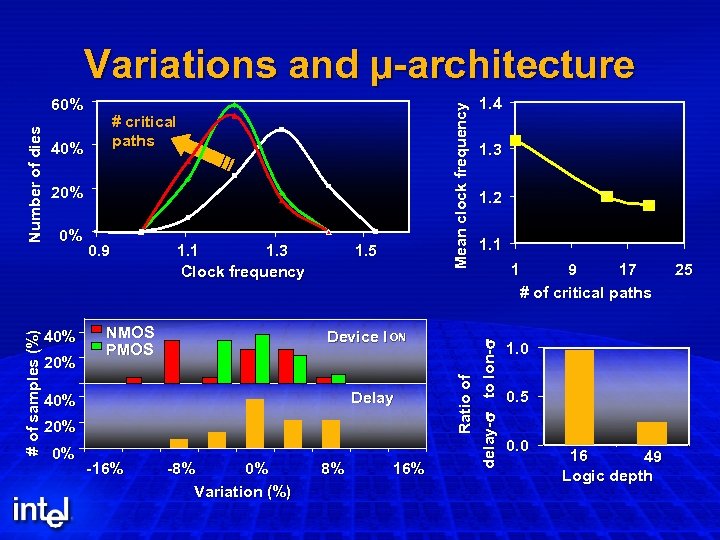

# critical paths 40% 20% 0% 40% 20% 0. 9 1. 1 1. 3 Clock frequency NMOS PMOS 1. 5 Device I ON Delay 40% 20% 0% -16% -8% 0% Variation (%) 8% 16% 1. 4 1. 3 1. 2 1. 1 Ratio of delay-s to Ion-s # of samples (%) Number of dies 60% Mean clock frequency Variations and µ-architecture 1 9 17 # of critical paths 1. 0 0. 5 0. 0 16 49 Logic depth 25

# critical paths 40% 20% 0% 40% 20% 0. 9 1. 1 1. 3 Clock frequency NMOS PMOS 1. 5 Device I ON Delay 40% 20% 0% -16% -8% 0% Variation (%) 8% 16% 1. 4 1. 3 1. 2 1. 1 Ratio of delay-s to Ion-s # of samples (%) Number of dies 60% Mean clock frequency Variations and µ-architecture 1 9 17 # of critical paths 1. 0 0. 5 0. 0 16 49 Logic depth 25

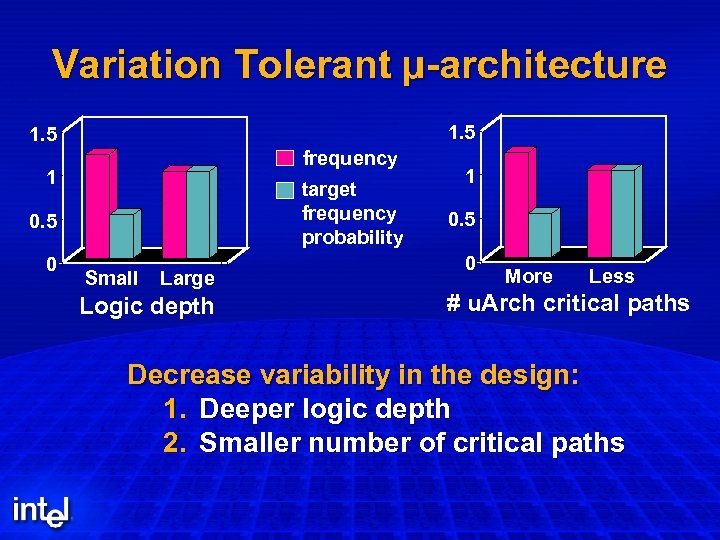

Variation Tolerant µ-architecture 1. 5 frequency 1 target frequency probability 0. 5 0 Small Large Logic depth 1 0. 5 0 More Less # u. Arch critical paths Decrease variability in the design: 1. Deeper logic depth 2. Smaller number of critical paths

Variation Tolerant µ-architecture 1. 5 frequency 1 target frequency probability 0. 5 0 Small Large Logic depth 1 0. 5 0 More Less # u. Arch critical paths Decrease variability in the design: 1. Deeper logic depth 2. Smaller number of critical paths

Implications For CAD Logic & Circuits Layout Test

Implications For CAD Logic & Circuits Layout Test

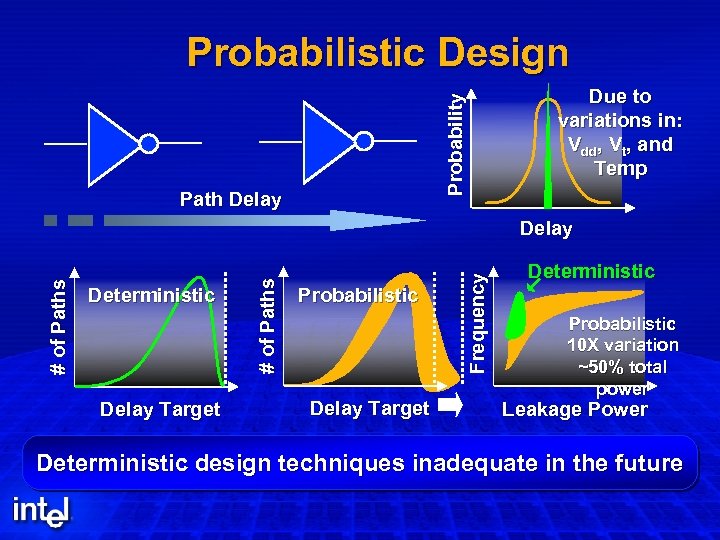

Probability Probabilistic Design Path Delay Due to variations in: Vdd, Vt, and Temp Delay Target Probabilistic Delay Target Frequency Deterministic # of Paths Delay Deterministic Probabilistic 10 X variation ~50% total power Leakage Power Deterministic design techniques inadequate in the future

Probability Probabilistic Design Path Delay Due to variations in: Vdd, Vt, and Temp Delay Target Probabilistic Delay Target Frequency Deterministic # of Paths Delay Deterministic Probabilistic 10 X variation ~50% total power Leakage Power Deterministic design techniques inadequate in the future

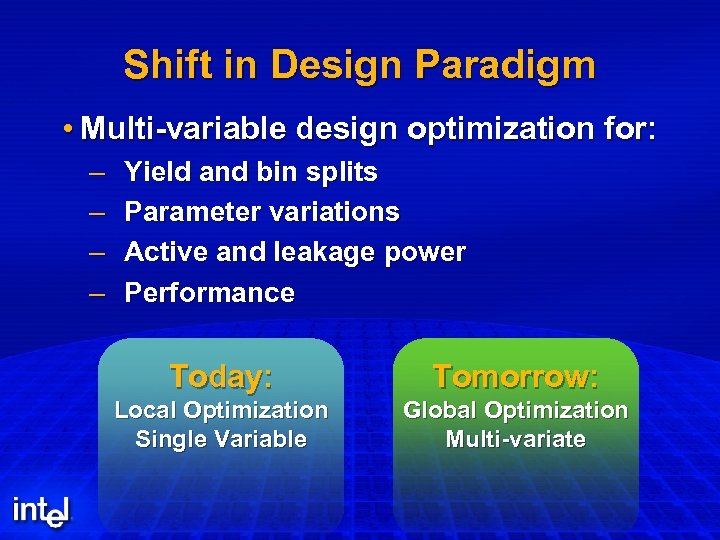

Shift in Design Paradigm • Multi-variable design optimization for: – – Yield and bin splits Parameter variations Active and leakage power Performance Today: Tomorrow: Local Optimization Single Variable Global Optimization Multi-variate

Shift in Design Paradigm • Multi-variable design optimization for: – – Yield and bin splits Parameter variations Active and leakage power Performance Today: Tomorrow: Local Optimization Single Variable Global Optimization Multi-variate

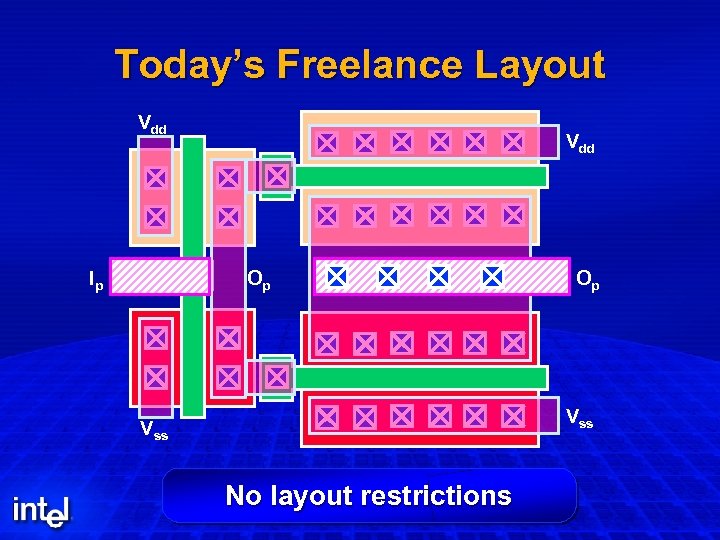

Today’s Freelance Layout Vdd Ip Vdd Op Op Vss No layout restrictions

Today’s Freelance Layout Vdd Ip Vdd Op Op Vss No layout restrictions

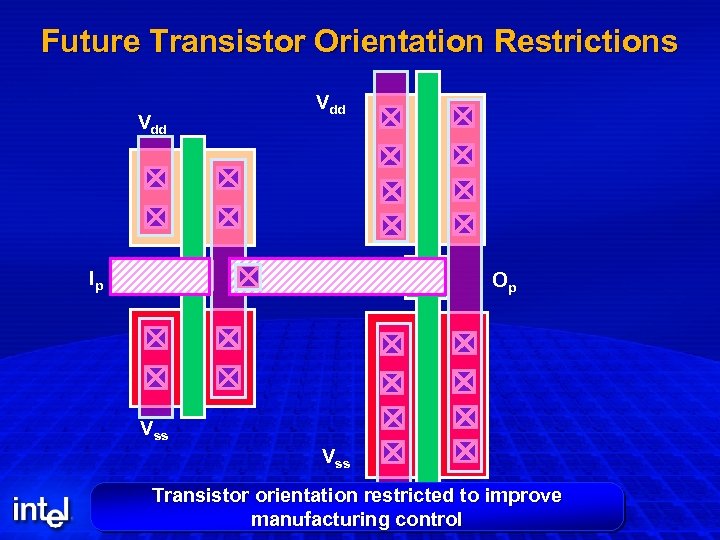

Future Transistor Orientation Restrictions Vdd Ip Op Op Vss Transistor orientation restricted to improve manufacturing control

Future Transistor Orientation Restrictions Vdd Ip Op Op Vss Transistor orientation restricted to improve manufacturing control

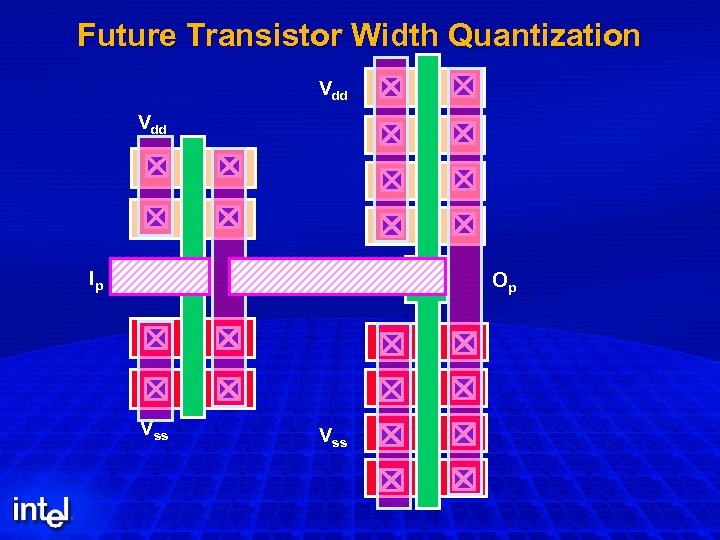

Future Transistor Width Quantization Vdd Op Ip Vss Op Vss

Future Transistor Width Quantization Vdd Op Ip Vss Op Vss

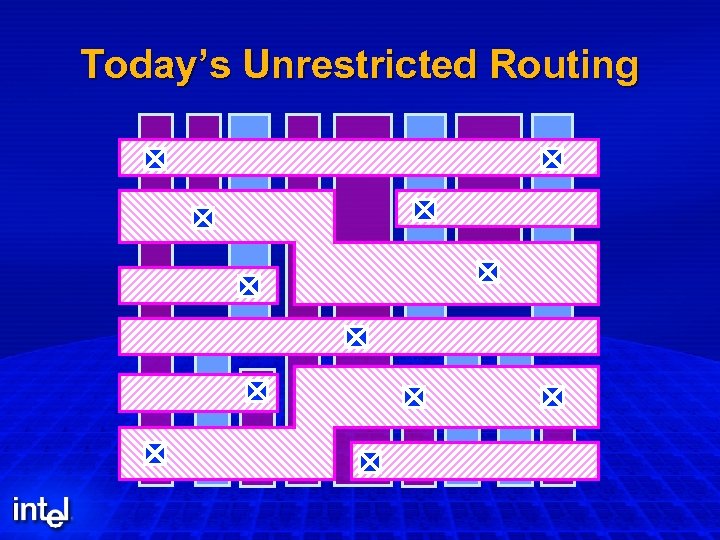

Today’s Unrestricted Routing

Today’s Unrestricted Routing

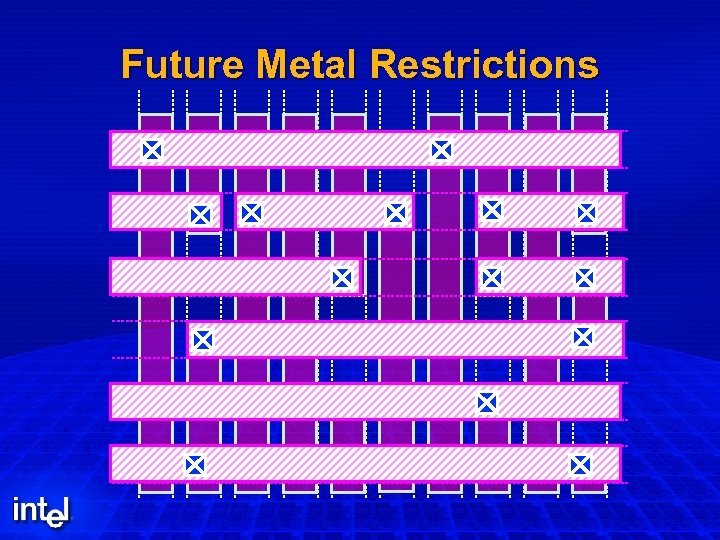

Future Metal Restrictions

Future Metal Restrictions

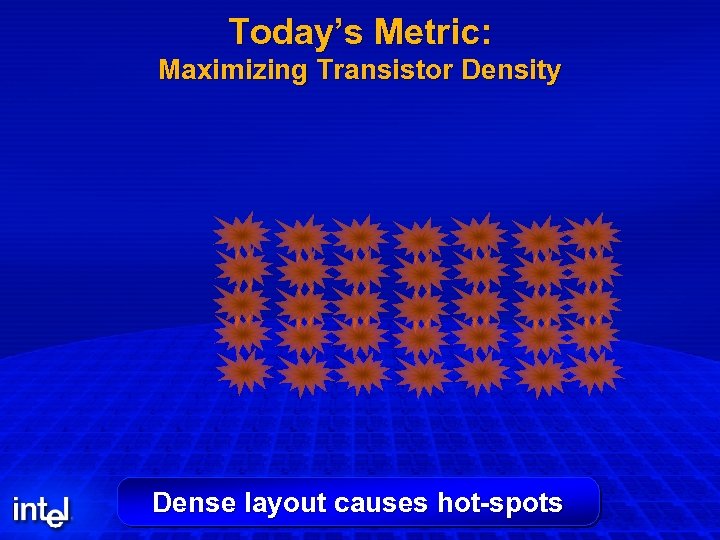

Today’s Metric: Maximizing Transistor Density Dense layout causes hot-spots

Today’s Metric: Maximizing Transistor Density Dense layout causes hot-spots

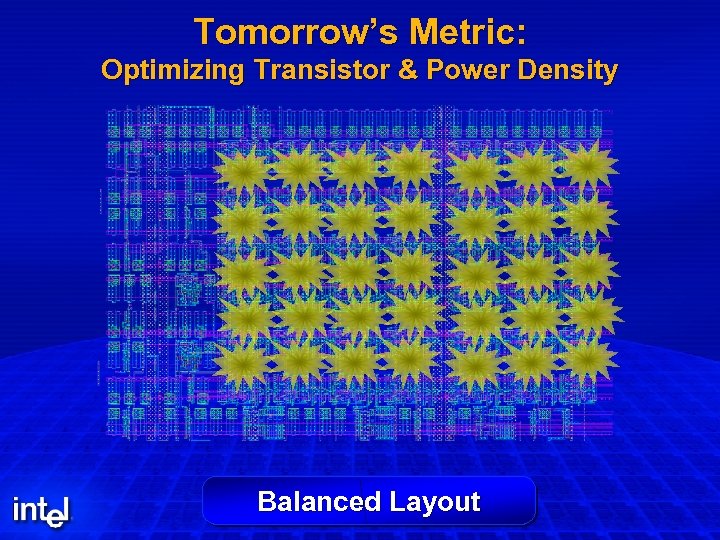

Tomorrow’s Metric: Optimizing Transistor & Power Density Balanced Layout

Tomorrow’s Metric: Optimizing Transistor & Power Density Balanced Layout

Other Challenges … Test & Debug

Other Challenges … Test & Debug

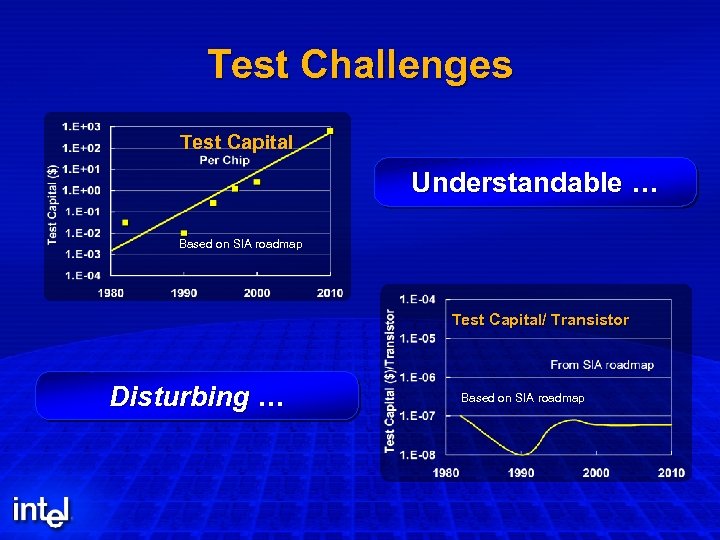

Test Challenges Test Capital Understandable … Based on SIA roadmap Test Capital/ Transistor Disturbing … Based on SIA roadmap

Test Challenges Test Capital Understandable … Based on SIA roadmap Test Capital/ Transistor Disturbing … Based on SIA roadmap

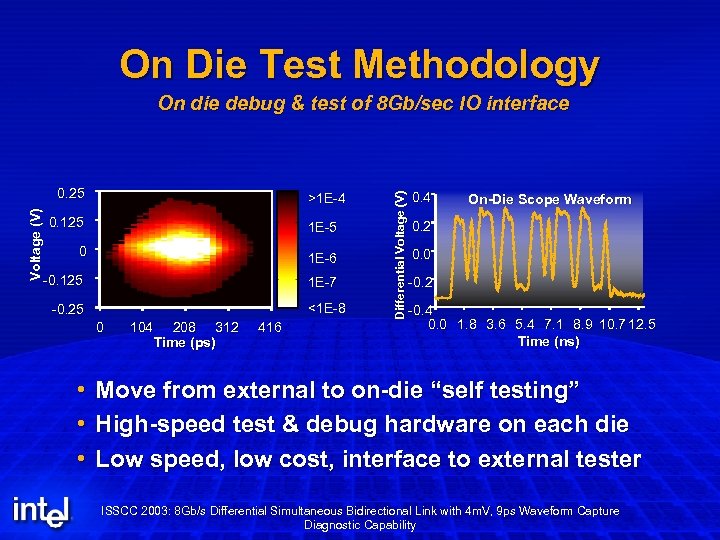

On Die Test Methodology Voltage (V) 0. 25 >1 E-4 0. 125 1 E-5 0 1 E-6 -0. 125 1 E-7 <1 E-8 -0. 25 0 104 208 312 Time (ps) 416 Differential Voltage (V) On die debug & test of 8 Gb/sec IO interface 0. 4 On-Die Scope Waveform 0. 2 0. 0 -0. 2 -0. 4 0. 0 1. 8 3. 6 5. 4 7. 1 8. 9 10. 7 12. 5 Time (ns) • Move from external to on-die “self testing” • High-speed test & debug hardware on each die • Low speed, low cost, interface to external tester ISSCC 2003: 8 Gb/s Differential Simultaneous Bidirectional Link with 4 m. V, 9 ps Waveform Capture Diagnostic Capability

On Die Test Methodology Voltage (V) 0. 25 >1 E-4 0. 125 1 E-5 0 1 E-6 -0. 125 1 E-7 <1 E-8 -0. 25 0 104 208 312 Time (ps) 416 Differential Voltage (V) On die debug & test of 8 Gb/sec IO interface 0. 4 On-Die Scope Waveform 0. 2 0. 0 -0. 2 -0. 4 0. 0 1. 8 3. 6 5. 4 7. 1 8. 9 10. 7 12. 5 Time (ns) • Move from external to on-die “self testing” • High-speed test & debug hardware on each die • Low speed, low cost, interface to external tester ISSCC 2003: 8 Gb/s Differential Simultaneous Bidirectional Link with 4 m. V, 9 ps Waveform Capture Diagnostic Capability

Other Challenges … Mixed-signal Design System-level Design Correctness Multi-clock domains Resiliency

Other Challenges … Mixed-signal Design System-level Design Correctness Multi-clock domains Resiliency

Business As Usual Is NOT An Option For CAD…

Business As Usual Is NOT An Option For CAD…

Summary BELIEVE CMOS scaling will continue, transistors become free SHIFT Deterministic Probabilistic, Single Multi EMBRACE local to global optimization: power, …

Summary BELIEVE CMOS scaling will continue, transistors become free SHIFT Deterministic Probabilistic, Single Multi EMBRACE local to global optimization: power, …