32-разрядные микроконтроллеры.ppt

- Количество слайдов: 31

32 -разрядные микроконтроллеры

32 -разрядные микроконтроллеры

Микроконтроллерное ядро ARM • Advanced RISC Machines • Разработки используются в продукции Altera, Analog Devices, Atmel, Cirrus Logic, Fujitsu, Magna. Chip (Hynix), Intel, Motorola, National Semiconductor, Philips, ST Microelectronics и Texas Instruments.

Микроконтроллерное ядро ARM • Advanced RISC Machines • Разработки используются в продукции Altera, Analog Devices, Atmel, Cirrus Logic, Fujitsu, Magna. Chip (Hynix), Intel, Motorola, National Semiconductor, Philips, ST Microelectronics и Texas Instruments.

Микроконтроллерное ядро ARM • ARM 2 -1986 - 32 -шина данных, 26 -бит (64 Mбайт) адресное пространство и 16 регистров 32 бит. Программный счетчик -26 бит, старшие 6 бит –статусные флаги. Ядро почти не изменилось. • RISC особенности: – Простая архитектура загрузки/выгрузки – Нет поддержки неупорядоченного доступа к памяти (сделана в ядре ARMv 6) – Универсальный файл регистров 16 × 32 -бит – Фиксированные инструкции по 32 бит – В основном на исполнение один цикл

Микроконтроллерное ядро ARM • ARM 2 -1986 - 32 -шина данных, 26 -бит (64 Mбайт) адресное пространство и 16 регистров 32 бит. Программный счетчик -26 бит, старшие 6 бит –статусные флаги. Ядро почти не изменилось. • RISC особенности: – Простая архитектура загрузки/выгрузки – Нет поддержки неупорядоченного доступа к памяти (сделана в ядре ARMv 6) – Универсальный файл регистров 16 × 32 -бит – Фиксированные инструкции по 32 бит – В основном на исполнение один цикл

Микроконтроллерное ядро ARM Для компенсации простого дизайна были использованы некоторые уникальные особенности: • Условное исполнение большинства команд, снижающее ошибки ветвлений и компенсирующие отсутствие предсказаний ветвлений –использование 4 битного кода условий • Арифметические инструкции изменяют код условий при необходимости • 32 -бит многорегистровое циклическое сдвиговое устройство без задержек может быть использовано для почти всех арифметических команд и адресных вычислений • Режимы индексной адресации • Регистр связи для быстрых вызовов в сети. • Простая, быстрая 2 уровневая подсистема прерываний с переключением файловых регистров

Микроконтроллерное ядро ARM Для компенсации простого дизайна были использованы некоторые уникальные особенности: • Условное исполнение большинства команд, снижающее ошибки ветвлений и компенсирующие отсутствие предсказаний ветвлений –использование 4 битного кода условий • Арифметические инструкции изменяют код условий при необходимости • 32 -бит многорегистровое циклическое сдвиговое устройство без задержек может быть использовано для почти всех арифметических команд и адресных вычислений • Режимы индексной адресации • Регистр связи для быстрых вызовов в сети. • Простая, быстрая 2 уровневая подсистема прерываний с переключением файловых регистров

Блок-схема ядра ARM 7

Блок-схема ядра ARM 7

Основные характеристики ядра ARM 7 • 32 -разрядный RISC процессор (32 -разрядные шины данных и адреса) с производительностью 17 MIPS при тактовой частоте 25 МГц (пиковая производительность 25 MIPS) • 32 -разрядная адресация - линейное адресное пространство в 4 Гбайта - исключает потребность в сегментированной, разделенной на банки или оверлейной памяти • Тридцать один 32 -разрядный регистр общего назначения и шесть регистров состояния • Регистры адресов, записи и конвейера • Циклическое сдвиговое устройство и перемножитель • Трехуровневый конвейер (выборка команды, ее декодирование и выполнение)

Основные характеристики ядра ARM 7 • 32 -разрядный RISC процессор (32 -разрядные шины данных и адреса) с производительностью 17 MIPS при тактовой частоте 25 МГц (пиковая производительность 25 MIPS) • 32 -разрядная адресация - линейное адресное пространство в 4 Гбайта - исключает потребность в сегментированной, разделенной на банки или оверлейной памяти • Тридцать один 32 -разрядный регистр общего назначения и шесть регистров состояния • Регистры адресов, записи и конвейера • Циклическое сдвиговое устройство и перемножитель • Трехуровневый конвейер (выборка команды, ее декодирование и выполнение)

ARM 7 • Рабочие режимы Big Endian и Little Endian • Напряжение питания 3, 3 и 5 В • Малое потребление 0, 6 м. А/МГц, при изготовлении по CMOS технологии с топологическими нормами 0, 8 мкм. • Полностью статическая работа, позволяющая дополнительно снижать потребление за счет уменьшения тактовой частоты, что идеально для критичных к потреблению применений • Быстрый отклик на прерывания применений реального масштаба времени • Поддержка систем виртуальной памяти • Простая но мощная система команд

ARM 7 • Рабочие режимы Big Endian и Little Endian • Напряжение питания 3, 3 и 5 В • Малое потребление 0, 6 м. А/МГц, при изготовлении по CMOS технологии с топологическими нормами 0, 8 мкм. • Полностью статическая работа, позволяющая дополнительно снижать потребление за счет уменьшения тактовой частоты, что идеально для критичных к потреблению применений • Быстрый отклик на прерывания применений реального масштаба времени • Поддержка систем виртуальной памяти • Простая но мощная система команд

32 -разрядная система команд ядра ARM 7 содержит одиннадцать базовых типов команд: • Два типа используют встроенное арифметикологическое устройство, циклическое сдвиговое устройство и умножитель при операциях над данными в банке из 31 регистра, форматом по 32 разряда каждый; • Три класса команд управления перемещением данных между памятью и регистрами, один оптимизированный на обеспечение гибкости адресации, другой под быстрое контекстное переключение и третий подкачку данных; • Три команды управляют потоком и уровнем привилегии выполнения; • Три типа предназначены для управления внешними сопроцессорами, что позволяет расширить функциональные возможности системы команд за пределами ядра.

32 -разрядная система команд ядра ARM 7 содержит одиннадцать базовых типов команд: • Два типа используют встроенное арифметикологическое устройство, циклическое сдвиговое устройство и умножитель при операциях над данными в банке из 31 регистра, форматом по 32 разряда каждый; • Три класса команд управления перемещением данных между памятью и регистрами, один оптимизированный на обеспечение гибкости адресации, другой под быстрое контекстное переключение и третий подкачку данных; • Три команды управляют потоком и уровнем привилегии выполнения; • Три типа предназначены для управления внешними сопроцессорами, что позволяет расширить функциональные возможности системы команд за пределами ядра.

Микроконтроллерное ядро ARM • В настоящее время разработано шесть основных семейств ARM 7™, ARM 9 E™, ARM 10™, ARM 11™ и Secur. Core™. Также совместно с компанией Intel разработаны семейства XScale™ и Strong. ARM®. Как дополнение к ARM-архитектуре могут интегрироваться несколько расширений: • Thumb® - 16 -разр. набор инструкций, улучшающий эффективность использования памяти программ; • DSP - набор арифметических инструкций для цифровой обработки сигналов; • Jazelle™ - расширение для аппаратного непосредственного исполнения Java-инструкций; • Media - расширение для 2 -4 -кратного увеличения скорости обработки аудио и видео сигналов.

Микроконтроллерное ядро ARM • В настоящее время разработано шесть основных семейств ARM 7™, ARM 9 E™, ARM 10™, ARM 11™ и Secur. Core™. Также совместно с компанией Intel разработаны семейства XScale™ и Strong. ARM®. Как дополнение к ARM-архитектуре могут интегрироваться несколько расширений: • Thumb® - 16 -разр. набор инструкций, улучшающий эффективность использования памяти программ; • DSP - набор арифметических инструкций для цифровой обработки сигналов; • Jazelle™ - расширение для аппаратного непосредственного исполнения Java-инструкций; • Media - расширение для 2 -4 -кратного увеличения скорости обработки аудио и видео сигналов.

В зависимости от назначения ARMпроцессоры разделяются на три группы • Процессоры для операционных систем с открытой платформой в приложениях беспроводной связи, обработки изображений и пользовательской электронике. • Процессоры для встраиваемых операционных систем реального времени для запоминающих устройств, промышленных, авто-мобильных и сетевых приложений. • Система защиты данных для смарт-карт и SIM-карт.

В зависимости от назначения ARMпроцессоры разделяются на три группы • Процессоры для операционных систем с открытой платформой в приложениях беспроводной связи, обработки изображений и пользовательской электронике. • Процессоры для встраиваемых операционных систем реального времени для запоминающих устройств, промышленных, авто-мобильных и сетевых приложений. • Система защиты данных для смарт-карт и SIM-карт.

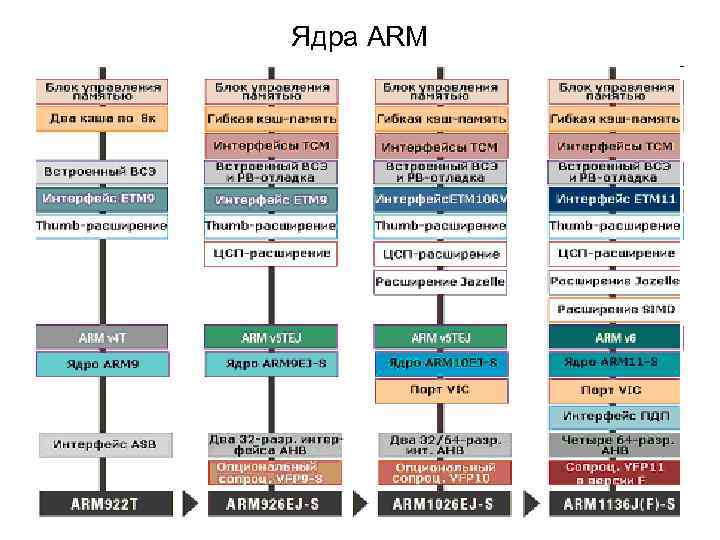

Ядра ARM

Ядра ARM

Ядра для ОС реального времени

Ядра для ОС реального времени

• ВСЭ - внутрисхемный эмулятор, РВ - реальное время, ЦСП- цифровой сигнальный процессор, SIMD - несколько данных в одной инструкции, ТСМ - плотно-связанная память (кэш), ETM - встроенные трассировочные макроячейки, VIC - векторизованный контроллер прерываний, ASB, AHB разновидности внутренних шин

• ВСЭ - внутрисхемный эмулятор, РВ - реальное время, ЦСП- цифровой сигнальный процессор, SIMD - несколько данных в одной инструкции, ТСМ - плотно-связанная память (кэш), ETM - встроенные трассировочные макроячейки, VIC - векторизованный контроллер прерываний, ASB, AHB разновидности внутренних шин

Микроконтроллерное ядро 68000 (CPU 32) • Motorola 68000 представляет 16/32 -бит CISC семейство микропроцессов, сконструированных и производимых Freescale Semiconductor (бывшее подразделение Motorola Semiconductor). Впервые этот процессор был опубликован в 1979 как первый процессор 32 -бит семейства m 68 k. • Адресная шина 24 бит – 16 Мбайт физической памяти. Используется 32 бит адресация, однако верхний байт игнорируется из-за физического отсутствия контактов. Программное обеспечение работает внутри 32 битного линейного адресного пространства

Микроконтроллерное ядро 68000 (CPU 32) • Motorola 68000 представляет 16/32 -бит CISC семейство микропроцессов, сконструированных и производимых Freescale Semiconductor (бывшее подразделение Motorola Semiconductor). Впервые этот процессор был опубликован в 1979 как первый процессор 32 -бит семейства m 68 k. • Адресная шина 24 бит – 16 Мбайт физической памяти. Используется 32 бит адресация, однако верхний байт игнорируется из-за физического отсутствия контактов. Программное обеспечение работает внутри 32 битного линейного адресного пространства

Микроконтроллерное ядро 68000 Внутренние регистры • Процессор имеет восемь 32 разрядных регистров общего назначения (D 0 -D 7), и восемь адресных регистров (A 0 -A 7). Последний адресный регистр является указателем стека. • Статусный регистр. Арифметические и логические операции устанавливают битовый флаг в статусном регистре для записи их результатов для последующих условных переходов. Имеются следующие флаги "нуля" (Z), "переноса" (C), "переполнения" (V), "расширения" (X), и "отрицания" (N).

Микроконтроллерное ядро 68000 Внутренние регистры • Процессор имеет восемь 32 разрядных регистров общего назначения (D 0 -D 7), и восемь адресных регистров (A 0 -A 7). Последний адресный регистр является указателем стека. • Статусный регистр. Арифметические и логические операции устанавливают битовый флаг в статусном регистре для записи их результатов для последующих условных переходов. Имеются следующие флаги "нуля" (Z), "переноса" (C), "переполнения" (V), "расширения" (X), и "отрицания" (N).

Микроконтроллерное ядро 68000 • Имеется 2 уровня привилегий: режим пользователя и режим супервизора. • Процессор использует 7 уровней прерываний по приоритету. Наивысший уровень у аппаратных прерываний. Таблица векторов прерываний содержит 256 32 -битных векторов.

Микроконтроллерное ядро 68000 • Имеется 2 уровня привилегий: режим пользователя и режим супервизора. • Процессор использует 7 уровней прерываний по приоритету. Наивысший уровень у аппаратных прерываний. Таблица векторов прерываний содержит 256 32 -битных векторов.

Микроконтроллерное ядро 68000 Процессор CPU 32 выполняет набор из 139 команд, которые реализуют следующие группы операций: • операции пересылки, • арифметические операции, • логические операции, • операции сдвига, • операции сравнения и тестирования, • битовые операции, • операции управления; • операции условной установки байтов.

Микроконтроллерное ядро 68000 Процессор CPU 32 выполняет набор из 139 команд, которые реализуют следующие группы операций: • операции пересылки, • арифметические операции, • логические операции, • операции сдвига, • операции сравнения и тестирования, • битовые операции, • операции управления; • операции условной установки байтов.

Микроконтроллерное ядро 68000 Cпособы адресации и формат команд Процессор выполняет обработку битов, байтов, 16 -разрядных слов, 32 -разрядных длинных слов и двоично-десятичных чисел (1 байт = 2 десятичных разряда). Обрабатываемые данные - операнды могут располагаться в регистрах (данных или адреса) или оперативной памяти.

Микроконтроллерное ядро 68000 Cпособы адресации и формат команд Процессор выполняет обработку битов, байтов, 16 -разрядных слов, 32 -разрядных длинных слов и двоично-десятичных чисел (1 байт = 2 десятичных разряда). Обрабатываемые данные - операнды могут располагаться в регистрах (данных или адреса) или оперативной памяти.

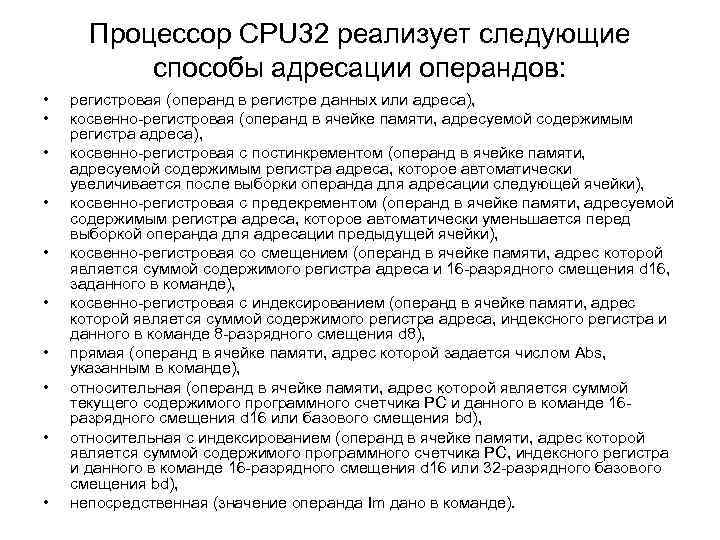

Процессор CPU 32 реализует следующие способы адресации операндов: • • • регистровая (операнд в регистре данных или адреса), косвенно-регистровая (операнд в ячейке памяти, адресуемой содержимым регистра адреса), косвенно-регистровая с постинкрементом (операнд в ячейке памяти, адресуемой содержимым регистра адреса, которое автоматически увеличивается после выборки операнда для адресации следующей ячейки), косвенно-регистровая с предекрементом (операнд в ячейке памяти, адресуемой содержимым регистра адреса, которое автоматически уменьшается перед выборкой операнда для адресации предыдущей ячейки), косвенно-регистровая со смещением (операнд в ячейке памяти, адрес которой является суммой содержимого регистра адреса и 16 -разрядного смещения d 16, заданного в команде), косвенно-регистровая с индексированием (операнд в ячейке памяти, адрес которой является суммой содержимого регистра адреса, индексного регистра и данного в команде 8 -разрядного смещения d 8), прямая (операнд в ячейке памяти, адрес которой задается числом Abs, указанным в команде), относительная (операнд в ячейке памяти, адрес которой является суммой текущего содержимого программного счетчика PC и данного в команде 16 разрядного смещения d 16 или базового смещения bd), относительная с индексированием (операнд в ячейке памяти, адрес которой является суммой содержимого программного счетчика PC, индексного регистра и данного в команде 16 -разрядного смещения d 16 или 32 -разрядного базового смещения bd), непосредственная (значение операнда Im дано в команде).

Процессор CPU 32 реализует следующие способы адресации операндов: • • • регистровая (операнд в регистре данных или адреса), косвенно-регистровая (операнд в ячейке памяти, адресуемой содержимым регистра адреса), косвенно-регистровая с постинкрементом (операнд в ячейке памяти, адресуемой содержимым регистра адреса, которое автоматически увеличивается после выборки операнда для адресации следующей ячейки), косвенно-регистровая с предекрементом (операнд в ячейке памяти, адресуемой содержимым регистра адреса, которое автоматически уменьшается перед выборкой операнда для адресации предыдущей ячейки), косвенно-регистровая со смещением (операнд в ячейке памяти, адрес которой является суммой содержимого регистра адреса и 16 -разрядного смещения d 16, заданного в команде), косвенно-регистровая с индексированием (операнд в ячейке памяти, адрес которой является суммой содержимого регистра адреса, индексного регистра и данного в команде 8 -разрядного смещения d 8), прямая (операнд в ячейке памяти, адрес которой задается числом Abs, указанным в команде), относительная (операнд в ячейке памяти, адрес которой является суммой текущего содержимого программного счетчика PC и данного в команде 16 разрядного смещения d 16 или базового смещения bd), относительная с индексированием (операнд в ячейке памяти, адрес которой является суммой содержимого программного счетчика PC, индексного регистра и данного в команде 16 -разрядного смещения d 16 или 32 -разрядного базового смещения bd), непосредственная (значение операнда Im дано в команде).

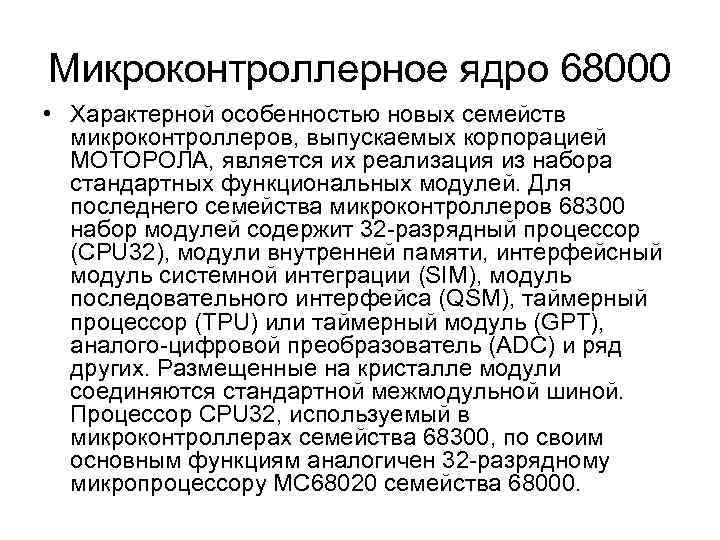

Микроконтроллерное ядро 68000 • Характерной особенностью новых семейств микроконтроллеров, выпускаемых корпорацией МОТОРОЛА, является их реализация из набора стандартных функциональных модулей. Для последнего семейства микроконтроллеров 68300 набор модулей содержит 32 -разрядный процессор (CPU 32), модули внутренней памяти, интерфейсный модуль системной интеграции (SIM), модуль последовательного интерфейса (QSM), таймерный процессор (TPU) или таймерный модуль (GPT), аналого-цифровой преобразователь (ADC) и ряд других. Размещенные на кристалле модули соединяются стандартной межмодульной шиной. Процессор CPU 32, используемый в микроконтроллерах семейства 68300, по своим основным функциям аналогичен 32 -разрядному микропроцессору MC 68020 семейства 68000.

Микроконтроллерное ядро 68000 • Характерной особенностью новых семейств микроконтроллеров, выпускаемых корпорацией МОТОРОЛА, является их реализация из набора стандартных функциональных модулей. Для последнего семейства микроконтроллеров 68300 набор модулей содержит 32 -разрядный процессор (CPU 32), модули внутренней памяти, интерфейсный модуль системной интеграции (SIM), модуль последовательного интерфейса (QSM), таймерный процессор (TPU) или таймерный модуль (GPT), аналого-цифровой преобразователь (ADC) и ряд других. Размещенные на кристалле модули соединяются стандартной межмодульной шиной. Процессор CPU 32, используемый в микроконтроллерах семейства 68300, по своим основным функциям аналогичен 32 -разрядному микропроцессору MC 68020 семейства 68000.

• Староверов К. С. , Сравнительный анализ микроконтроллеров с ядром ARM 08. 09. 2005

• Староверов К. С. , Сравнительный анализ микроконтроллеров с ядром ARM 08. 09. 2005