3.1 Архитектура 16-разрядных микропроцессоров.pptx

- Количество слайдов: 14

3. 1 Архитектура 16 -разрядных микропроцессоров Микропроцессор 8086 был представлен в 1978 и нашел применение как основа построения процессора микро ЭВМ. Сегодня в мире имеются буквально миллионы систем основанных на этом микропроцессоре. С количеством программного обеспечения, написанного для 8086, не конкурирует никакая другая архитектура. Однако в начале 80 х годов стало ясно, что замена для 8086 была необходима. Система на основе микропроцессора 8086 требовала множество дополнительных схем, чтобы выполнить даже несложную разработку. Фирма Intel почувствовала потребность интегрировать обычно используемые внешние устройства системы на тот же самый кремниевый кристалл, что и центральный процессор. В 1982 Intel удовлетворила эту потребность, представляя семейство микропроцессо ров 80186. Первоначальный 80186 объединил расширенный централь ный процессор 8086 с шестью обычно используемыми внешними устройствами системы. Параллельно Intel прикладывала усилия по разработке микропроцессора 80286. Этот микропроцессор начал путь к самой высокоэффективной архитектуре Intel, которая сегодня включает Intel 386, Intel 486 и Pentium микропроцессоры. 1

3. 1 Архитектура 16 -разрядных микропроцессоров Микропроцессор 8086 был представлен в 1978 и нашел применение как основа построения процессора микро ЭВМ. Сегодня в мире имеются буквально миллионы систем основанных на этом микропроцессоре. С количеством программного обеспечения, написанного для 8086, не конкурирует никакая другая архитектура. Однако в начале 80 х годов стало ясно, что замена для 8086 была необходима. Система на основе микропроцессора 8086 требовала множество дополнительных схем, чтобы выполнить даже несложную разработку. Фирма Intel почувствовала потребность интегрировать обычно используемые внешние устройства системы на тот же самый кремниевый кристалл, что и центральный процессор. В 1982 Intel удовлетворила эту потребность, представляя семейство микропроцессо ров 80186. Первоначальный 80186 объединил расширенный централь ный процессор 8086 с шестью обычно используемыми внешними устройствами системы. Параллельно Intel прикладывала усилия по разработке микропроцессора 80286. Этот микропроцессор начал путь к самой высокоэффективной архитектуре Intel, которая сегодня включает Intel 386, Intel 486 и Pentium микропроцессоры. 1

В 1987 Intel объявила второе поколение семейства микропроцес соров 80186: 80 C 186/C 188. Семейство 80 C 186 совместимо с семейством 80186 и имеет расширенный набор элементов. Высокоэффективный процесс производства позволил вдвое повысить тактовую частоту и вчетверо снизить потребляемую мощность. Следующий важный шаг произошел в 1990 с введением в семейство 80 C 186 EB. Центральный процессор 8086 был повторно разработан как статический модуль, внешние устройства семейства были также повторно разработаны как статические модули со стандартными сопряжениями. В 1991 г. семейство 80 C 186 было снова расширено введением трех новых изделий: 80 C 186 XL, 80 C 186 EA и 80 C 186 EC. Они отличаются сниженным энергопотреблением и повышенным быстродействием. 2

В 1987 Intel объявила второе поколение семейства микропроцес соров 80186: 80 C 186/C 188. Семейство 80 C 186 совместимо с семейством 80186 и имеет расширенный набор элементов. Высокоэффективный процесс производства позволил вдвое повысить тактовую частоту и вчетверо снизить потребляемую мощность. Следующий важный шаг произошел в 1990 с введением в семейство 80 C 186 EB. Центральный процессор 8086 был повторно разработан как статический модуль, внешние устройства семейства были также повторно разработаны как статические модули со стандартными сопряжениями. В 1991 г. семейство 80 C 186 было снова расширено введением трех новых изделий: 80 C 186 XL, 80 C 186 EA и 80 C 186 EC. Они отличаются сниженным энергопотреблением и повышенным быстродействием. 2

Микросхема 8086 представляет собой однокристальный высоко производительный 16 разрядный микропроцессор с фиксиро ваннойсистемой команд. Микропроцессор предназначен для использования в качестве центрального процессорного устройства при построении средств вычислительной техники – от простейших одно платных микро ЭВМ до высокопроизводительных мультипроцессорных систем. Микропроцессор обладает высоким быстродействием, обеспечивает возможность прямой адресации памяти объемом до 1 М байта (ША=20 бит), 65536 устройств ввода и 65536 устройств вывода (ШД=16 бит). Для вычисления адресов операндов, размещенных в памяти, используется 24 режима адресации. Микропроцессор имеет векторную структуру прерываний и обеспечивает обработку до 256 запросов прерываний трех типов: внешних, внутренних и программных. Архитектурной особенностью микропроцессора 8086 является наличие аппаратно программных средств, позволяющих упростить построение мультипроцессорных систем на его основе. Эти средства обеспечивают синхронизацию работы нескольких независимых (выполняющих собственные потоки команд) процессоров, имеющих общие ресурсы, а также синхронизацию параллельной работы микропроцессора и сопроцессоров (специализированных процессоров, аппаратно реализующих команды сложных процедур). Микропроцессор 8086 характеризуется двумя режимами работы – минимальным и максимальным, которые отличаются способом формирования сигналов обмена и соответственно 3 возможностями реализуемых систем.

Микросхема 8086 представляет собой однокристальный высоко производительный 16 разрядный микропроцессор с фиксиро ваннойсистемой команд. Микропроцессор предназначен для использования в качестве центрального процессорного устройства при построении средств вычислительной техники – от простейших одно платных микро ЭВМ до высокопроизводительных мультипроцессорных систем. Микропроцессор обладает высоким быстродействием, обеспечивает возможность прямой адресации памяти объемом до 1 М байта (ША=20 бит), 65536 устройств ввода и 65536 устройств вывода (ШД=16 бит). Для вычисления адресов операндов, размещенных в памяти, используется 24 режима адресации. Микропроцессор имеет векторную структуру прерываний и обеспечивает обработку до 256 запросов прерываний трех типов: внешних, внутренних и программных. Архитектурной особенностью микропроцессора 8086 является наличие аппаратно программных средств, позволяющих упростить построение мультипроцессорных систем на его основе. Эти средства обеспечивают синхронизацию работы нескольких независимых (выполняющих собственные потоки команд) процессоров, имеющих общие ресурсы, а также синхронизацию параллельной работы микропроцессора и сопроцессоров (специализированных процессоров, аппаратно реализующих команды сложных процедур). Микропроцессор 8086 характеризуется двумя режимами работы – минимальным и максимальным, которые отличаются способом формирования сигналов обмена и соответственно 3 возможностями реализуемых систем.

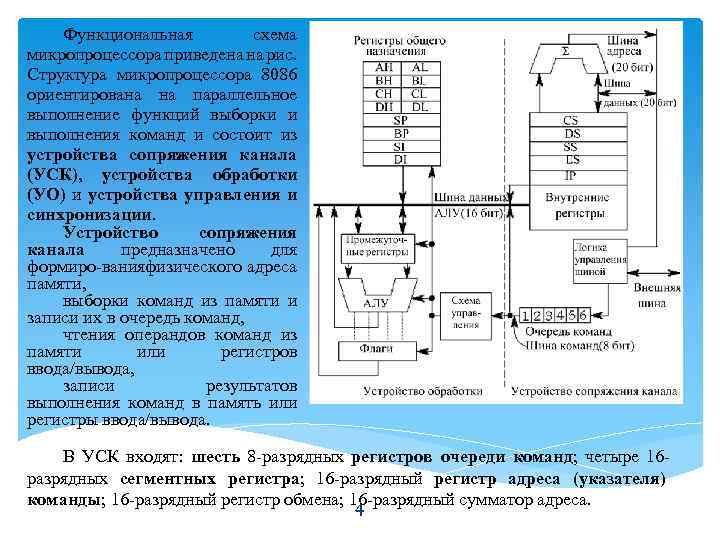

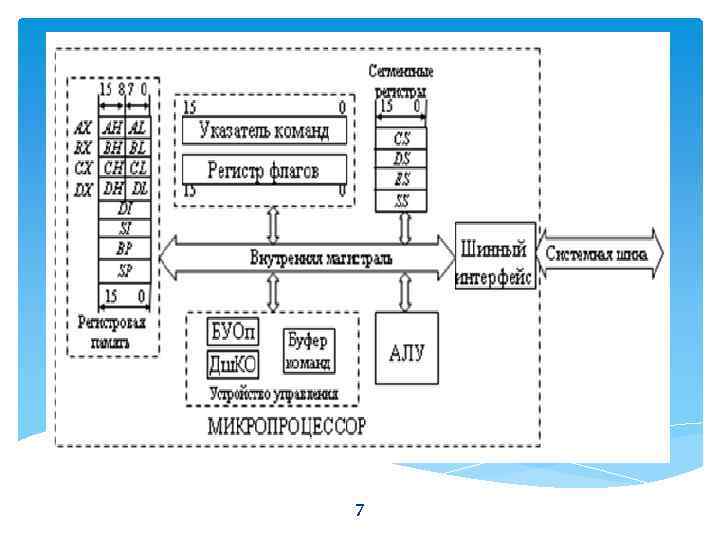

Функциональная схема микропроцессора приведена на рис. Структура микропроцессора 8086 ориентирована на параллельное выполнение функций выборки и выполнения команд и состоит из устройства сопряжения канала (УСК), устройства обработки (УО) и устройства управления и синхронизации. Устройство сопряжения канала предназначено для формиро ванияфизического адреса памяти, выборки команд из памяти и записи их в очередь команд, чтения операндов команд из памяти или регистров ввода/вывода, записи результатов выполнения команд в память или регистры ввода/вывода. В УСК входят: шесть 8 разрядных регистров очереди команд; четыре 16 разрядных сегментных регистра; 16 разрядный регистр адреса (указателя) команды; 16 разрядный регистр обмена; 16 разрядный сумматор адреса. 4

Функциональная схема микропроцессора приведена на рис. Структура микропроцессора 8086 ориентирована на параллельное выполнение функций выборки и выполнения команд и состоит из устройства сопряжения канала (УСК), устройства обработки (УО) и устройства управления и синхронизации. Устройство сопряжения канала предназначено для формиро ванияфизического адреса памяти, выборки команд из памяти и записи их в очередь команд, чтения операндов команд из памяти или регистров ввода/вывода, записи результатов выполнения команд в память или регистры ввода/вывода. В УСК входят: шесть 8 разрядных регистров очереди команд; четыре 16 разрядных сегментных регистра; 16 разрядный регистр адреса (указателя) команды; 16 разрядный регистр обмена; 16 разрядный сумматор адреса. 4

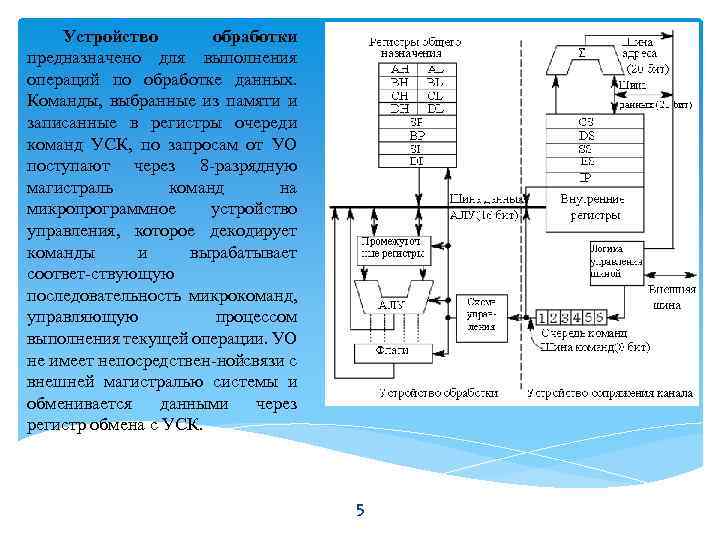

Устройство обработки предназначено для выполнения операций по обработке данных. Команды, выбранные из памяти и записанные в регистры очереди команд УСК, по запросам от УО поступают через 8 разрядную магистраль команд на микропрограммное устройство управления, которое декодирует команды и вырабатывает соответ ствующую последовательность микрокоманд, управляющую процессом выполнения текущей операции. УО не имеет непосредствен нойсвязи с внешней магистралью системы и обменивается данными через регистр обмена с УСК. 5

Устройство обработки предназначено для выполнения операций по обработке данных. Команды, выбранные из памяти и записанные в регистры очереди команд УСК, по запросам от УО поступают через 8 разрядную магистраль команд на микропрограммное устройство управления, которое декодирует команды и вырабатывает соответ ствующую последовательность микрокоманд, управляющую процессом выполнения текущей операции. УО не имеет непосредствен нойсвязи с внешней магистралью системы и обменивается данными через регистр обмена с УСК. 5

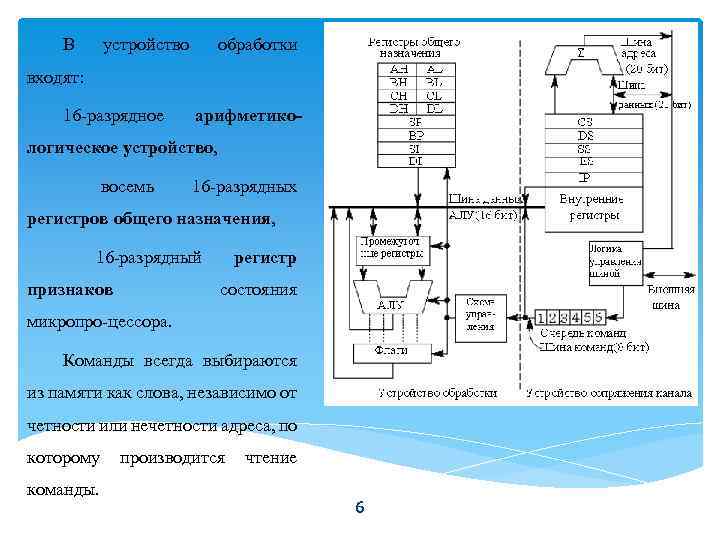

В устройство обработки входят: 16 разрядное арифметико- логическое устройство, восемь 16 разрядных регистров общего назначения, 16 разрядный признаков регистр состояния микропро цессора. Команды всегда выбираются из памяти как слова, независимо от четности или нечетности адреса, по которому команды. производится чтение 6

В устройство обработки входят: 16 разрядное арифметико- логическое устройство, восемь 16 разрядных регистров общего назначения, 16 разрядный признаков регистр состояния микропро цессора. Команды всегда выбираются из памяти как слова, независимо от четности или нечетности адреса, по которому команды. производится чтение 6

7

7

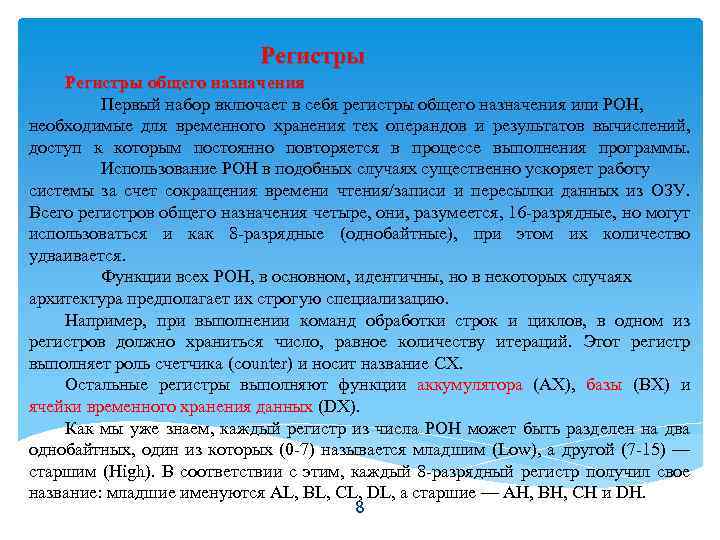

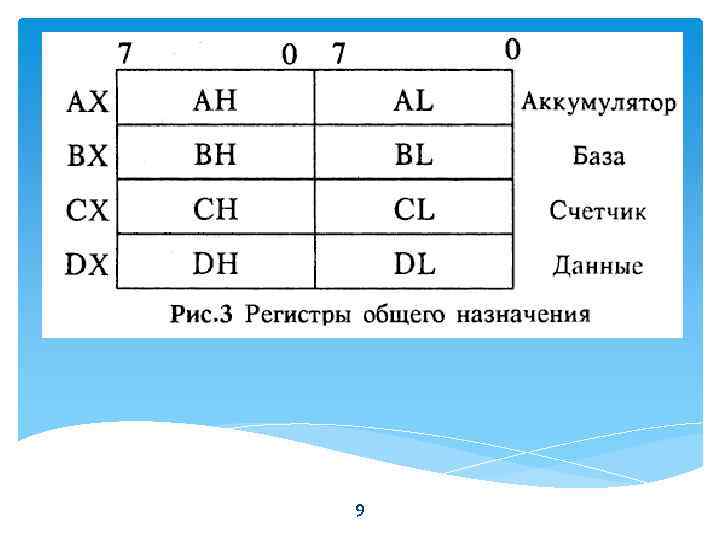

Регистры общего назначения Первый набор включает в себя регистры общего назначения или РОН, необходимые для временного хранения тех операндов и результатов вычислений, доступ к которым постоянно повторяется в процессе выполнения программы. Использование РОН в подобных случаях существенно ускоряет работу системы за счет сокращения времени чтения/записи и пересылки данных из ОЗУ. Всего регистров общего назначения четыре, они, разумеется, 16 разрядные, но могут использоваться и как 8 разрядные (однобайтные), при этом их количество удваивается. Функции всех РОН, в основном, идентичны, но в некоторых случаях архитектура предполагает их строгую специализацию. Например, при выполнении команд обработки строк и циклов, в одном из регистров должно храниться число, равное количеству итераций. Этот регистр выполняет роль счетчика (counter) и носит название CX. Остальные регистры выполняют функции аккумулятора (AX), базы (BX) и ячейки временного хранения данных (DX). Как мы уже знаем, каждый регистр из числа РОН может быть разделен на два однобайтных, один из которых (0 7) называется младшим (Low), а другой (7 15) — старшим (High). В соответствии с этим, каждый 8 разрядный регистр получил свое название: младшие именуются AL, BL, CL, DL, а старшие — AН, BН, CН и DH. 8

Регистры общего назначения Первый набор включает в себя регистры общего назначения или РОН, необходимые для временного хранения тех операндов и результатов вычислений, доступ к которым постоянно повторяется в процессе выполнения программы. Использование РОН в подобных случаях существенно ускоряет работу системы за счет сокращения времени чтения/записи и пересылки данных из ОЗУ. Всего регистров общего назначения четыре, они, разумеется, 16 разрядные, но могут использоваться и как 8 разрядные (однобайтные), при этом их количество удваивается. Функции всех РОН, в основном, идентичны, но в некоторых случаях архитектура предполагает их строгую специализацию. Например, при выполнении команд обработки строк и циклов, в одном из регистров должно храниться число, равное количеству итераций. Этот регистр выполняет роль счетчика (counter) и носит название CX. Остальные регистры выполняют функции аккумулятора (AX), базы (BX) и ячейки временного хранения данных (DX). Как мы уже знаем, каждый регистр из числа РОН может быть разделен на два однобайтных, один из которых (0 7) называется младшим (Low), а другой (7 15) — старшим (High). В соответствии с этим, каждый 8 разрядный регистр получил свое название: младшие именуются AL, BL, CL, DL, а старшие — AН, BН, CН и DH. 8

9

9

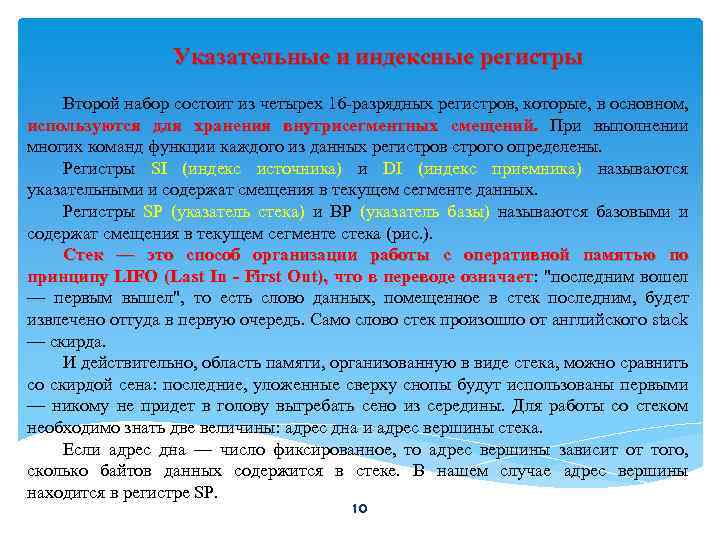

Указательные и индексные регистры Второй набор состоит из четырех 16 разрядных регистров, которые, в основном, используются для хранения внутрисегментных смещений. При выполнении многих команд функции каждого из данных регистров строго определены. Регистры SI (индекс источника) и DI (индекс приемника) называются указательными и содержат смещения в текущем сегменте данных. Регистры SP (указатель стека) и ВР (указатель базы) называются базовыми и содержат смещения в текущем сегменте стека (рис. ). Стек — это способ организации работы с оперативной памятью по принципу LIFO (Last In - First Out), что в переводе означает: "последним вошел означает — первым вышел", то есть слово данных, помещенное в стек последним, будет извлечено оттуда в первую очередь. Само слово стек произошло от английского stack — скирда. И действительно, область памяти, организованную в виде стека, можно сравнить со скирдой сена: последние, уложенные сверху снопы будут использованы первыми — никому не придет в голову выгребать сено из середины. Для работы со стеком необходимо знать две величины: адрес дна и адрес вершины стека. Если адрес дна — число фиксированное, то адрес вершины зависит от того, сколько байтов данных содержится в стеке. В нашем случае адрес вершины находится в регистре SP. 10

Указательные и индексные регистры Второй набор состоит из четырех 16 разрядных регистров, которые, в основном, используются для хранения внутрисегментных смещений. При выполнении многих команд функции каждого из данных регистров строго определены. Регистры SI (индекс источника) и DI (индекс приемника) называются указательными и содержат смещения в текущем сегменте данных. Регистры SP (указатель стека) и ВР (указатель базы) называются базовыми и содержат смещения в текущем сегменте стека (рис. ). Стек — это способ организации работы с оперативной памятью по принципу LIFO (Last In - First Out), что в переводе означает: "последним вошел означает — первым вышел", то есть слово данных, помещенное в стек последним, будет извлечено оттуда в первую очередь. Само слово стек произошло от английского stack — скирда. И действительно, область памяти, организованную в виде стека, можно сравнить со скирдой сена: последние, уложенные сверху снопы будут использованы первыми — никому не придет в голову выгребать сено из середины. Для работы со стеком необходимо знать две величины: адрес дна и адрес вершины стека. Если адрес дна — число фиксированное, то адрес вершины зависит от того, сколько байтов данных содержится в стеке. В нашем случае адрес вершины находится в регистре SP. 10

Использование общих регистров Регистр AX AL AH BX CX CL DX SP SI DI Операция Умножение и деление слов, ввод/вывод слов Умножение и деление байтов, ввод/вывод байтов, десятичная арифметика, перекодирование Умножение и деление байтов Перекодирование Строковые операции, циклы Сдвиги переменных Умножение и деление слов, косвенная адресация портов ввода/вывода Стековые операции Операции со строками 11

Использование общих регистров Регистр AX AL AH BX CX CL DX SP SI DI Операция Умножение и деление слов, ввод/вывод слов Умножение и деление байтов, ввод/вывод байтов, десятичная арифметика, перекодирование Умножение и деление байтов Перекодирование Строковые операции, циклы Сдвиги переменных Умножение и деление слов, косвенная адресация портов ввода/вывода Стековые операции Операции со строками 11

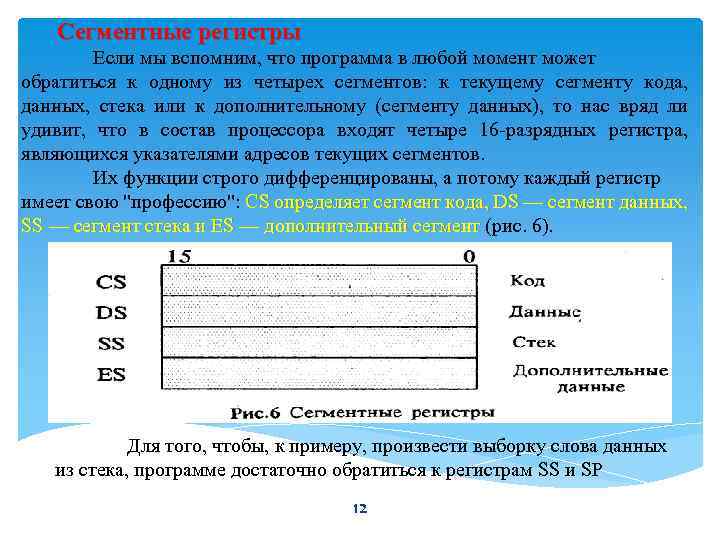

Сегментные регистры Если мы вспомним, что программа в любой момент может обратиться к одному из четырех сегментов: к текущему сегменту кода, данных, стека или к дополнительному (сегменту данных), то нас вряд ли удивит, что в состав процессора входят четыре 16 разрядных регистра, являющихся указателями адресов текущих сегментов. Их функции строго дифференцированы, а потому каждый регистр имеет свою "профессию": CS определяет сегмент кода, DS — сегмент данных, SS — сегмент стека и ES — дополнительный сегмент (рис. 6). Для того, чтобы, к примеру, произвести выборку слова данных из стека, программе достаточно обратиться к регистрам SS и SP 12

Сегментные регистры Если мы вспомним, что программа в любой момент может обратиться к одному из четырех сегментов: к текущему сегменту кода, данных, стека или к дополнительному (сегменту данных), то нас вряд ли удивит, что в состав процессора входят четыре 16 разрядных регистра, являющихся указателями адресов текущих сегментов. Их функции строго дифференцированы, а потому каждый регистр имеет свою "профессию": CS определяет сегмент кода, DS — сегмент данных, SS — сегмент стека и ES — дополнительный сегмент (рис. 6). Для того, чтобы, к примеру, произвести выборку слова данных из стека, программе достаточно обратиться к регистрам SS и SP 12

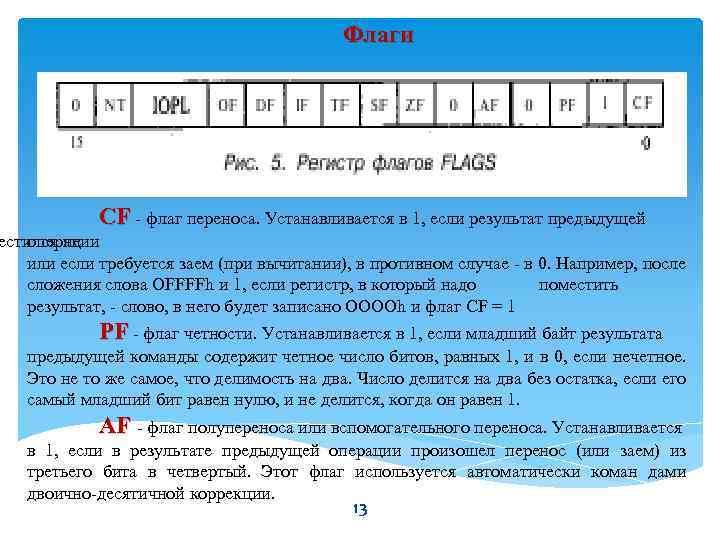

Флаги CF флаг переноса. Устанавливается в 1, если результат предыдущей естился не операции или если требуется заем (при вычитании), в противном случае в 0. Например, после сложения слова OFFFFh и 1, если регистр, в который надо поместить результат, слово, в него будет записано OOOOh и флаг CF = 1 PF флаг четности. Устанавливается в 1, если младший байт результата предыдущей команды содержит четное число битов, равных 1, и в 0, если нечетное. Это не то же самое, что делимость на два. Число делится на два без остатка, если его самый младший бит равен нулю, и не делится, когда он равен 1. AF флаг полупереноса или вспомогательного переноса. Устанавливается в 1, если в результате предыдущей операции произошел перенос (или заем) из третьего бита в четвертый. Этот флаг используется автоматически коман дами двоично десятичной коррекции. 13

Флаги CF флаг переноса. Устанавливается в 1, если результат предыдущей естился не операции или если требуется заем (при вычитании), в противном случае в 0. Например, после сложения слова OFFFFh и 1, если регистр, в который надо поместить результат, слово, в него будет записано OOOOh и флаг CF = 1 PF флаг четности. Устанавливается в 1, если младший байт результата предыдущей команды содержит четное число битов, равных 1, и в 0, если нечетное. Это не то же самое, что делимость на два. Число делится на два без остатка, если его самый младший бит равен нулю, и не делится, когда он равен 1. AF флаг полупереноса или вспомогательного переноса. Устанавливается в 1, если в результате предыдущей операции произошел перенос (или заем) из третьего бита в четвертый. Этот флаг используется автоматически коман дами двоично десятичной коррекции. 13

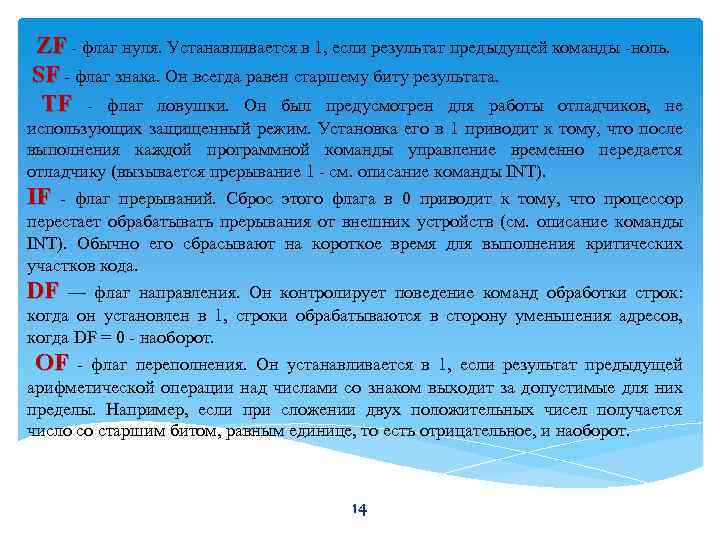

ZF флаг нуля. Устанавливается в 1, если результат предыдущей команды ноль. SF флаг знака. Он всегда равен старшему биту результата. TF флаг ловушки. Он был предусмотрен для работы отладчиков, не использующих защищенный режим. Установка его в 1 приводит к тому, что после выполнения каждой программной команды управление временно передается отладчику (вызывается прерывание 1 см. описание команды INT). IF флаг прерываний. Сброс этого флага в 0 приводит к тому, что процессор перестает обрабатывать прерывания от внешних устройств (см. описание команды INT). Обычно его сбрасывают на короткое время для выполнения критических участков кода. DF — флаг направления. Он контролирует поведение команд обработки строк: когда он установлен в 1, строки обрабатываются в сторону уменьшения адресов, когда DF = 0 наоборот. OF флаг переполнения. Он устанавливается в 1, если результат предыдущей арифметической операции над числами со знаком выходит за допустимые для них пределы. Например, если при сложении двух положительных чисел получается число со старшим битом, равным единице, то есть отрицательное, и наоборот. 14

ZF флаг нуля. Устанавливается в 1, если результат предыдущей команды ноль. SF флаг знака. Он всегда равен старшему биту результата. TF флаг ловушки. Он был предусмотрен для работы отладчиков, не использующих защищенный режим. Установка его в 1 приводит к тому, что после выполнения каждой программной команды управление временно передается отладчику (вызывается прерывание 1 см. описание команды INT). IF флаг прерываний. Сброс этого флага в 0 приводит к тому, что процессор перестает обрабатывать прерывания от внешних устройств (см. описание команды INT). Обычно его сбрасывают на короткое время для выполнения критических участков кода. DF — флаг направления. Он контролирует поведение команд обработки строк: когда он установлен в 1, строки обрабатываются в сторону уменьшения адресов, когда DF = 0 наоборот. OF флаг переполнения. Он устанавливается в 1, если результат предыдущей арифметической операции над числами со знаком выходит за допустимые для них пределы. Например, если при сложении двух положительных чисел получается число со старшим битом, равным единице, то есть отрицательное, и наоборот. 14