ca97ed36422da04735ab4177be8ff9ca.ppt

- Количество слайдов: 35

234262 © Dima Elenbogen 2010, Technion 234262 Solving MIPS Exam Problems 12: 27 1

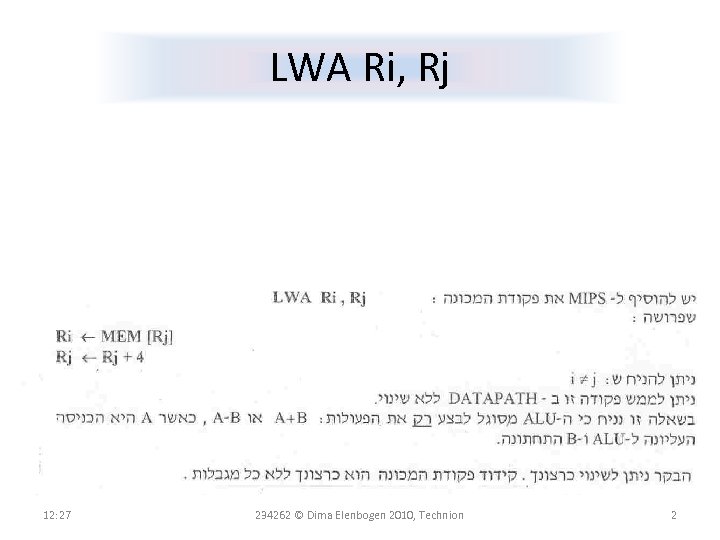

LWA Ri, Rj 12: 27 234262 © Dima Elenbogen 2010, Technion 2

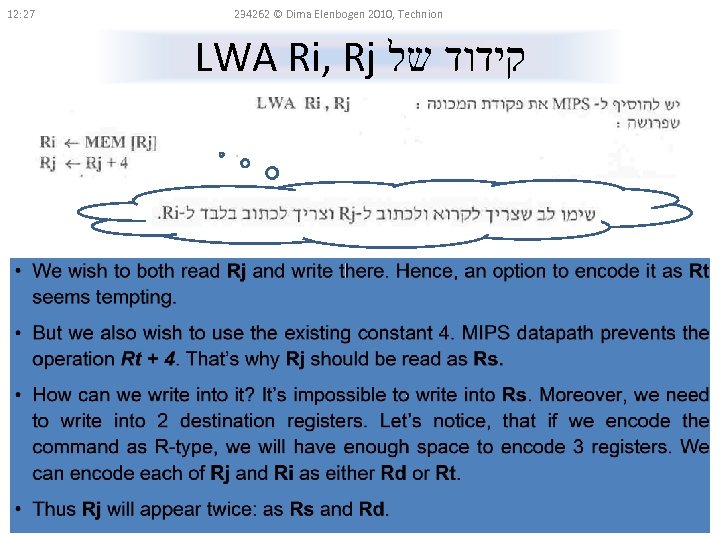

12: 27 234262 © Dima Elenbogen 2010, Technion LWA Ri, Rj קידוד של 3

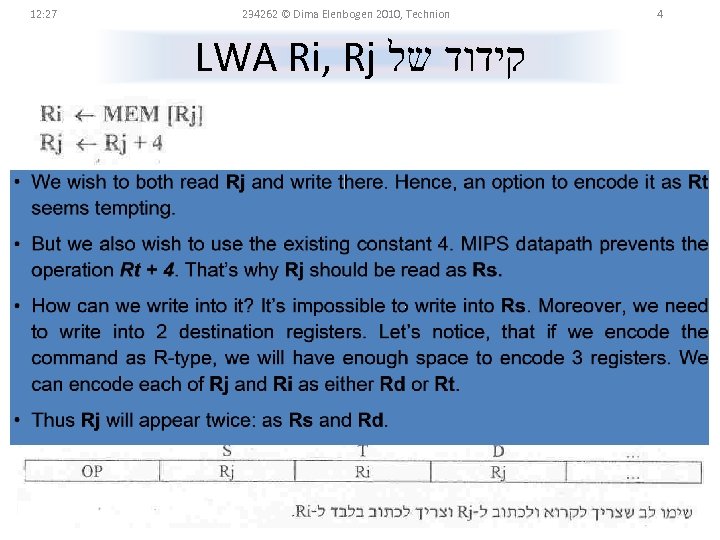

12: 27 234262 © Dima Elenbogen 2010, Technion LWA Ri, Rj קידוד של 4

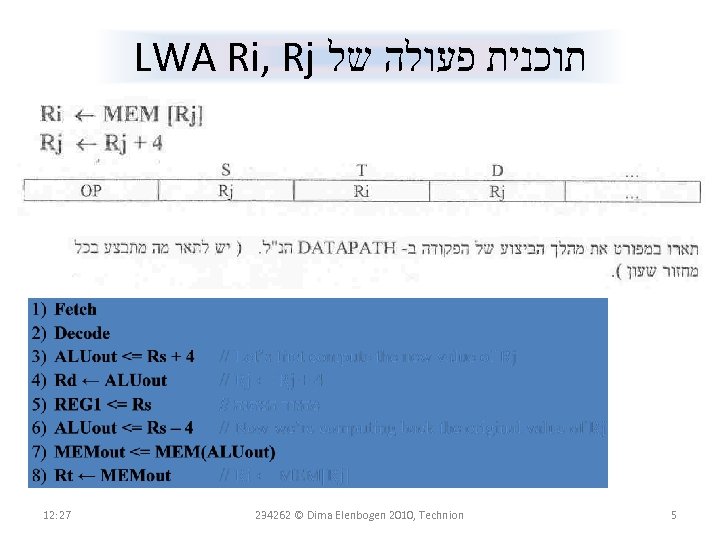

LWA Ri, Rj תוכנית פעולה של 12: 27 234262 © Dima Elenbogen 2010, Technion 5

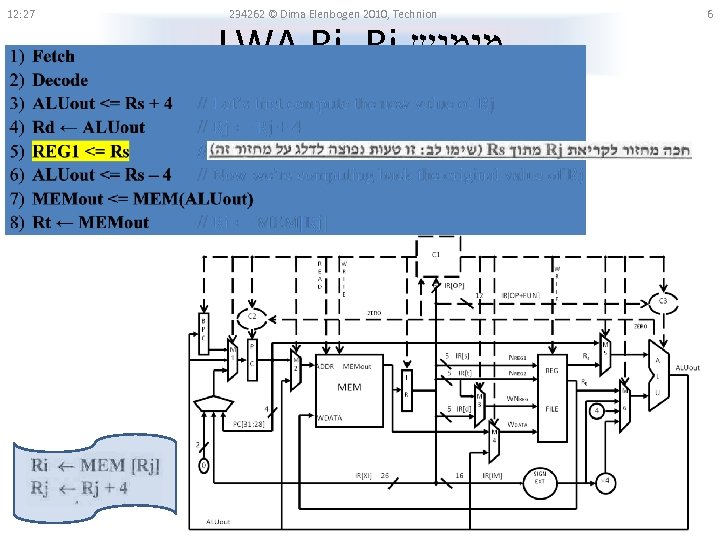

12: 27 234262 © Dima Elenbogen 2010, Technion LWA Ri, Rj מימוש 6

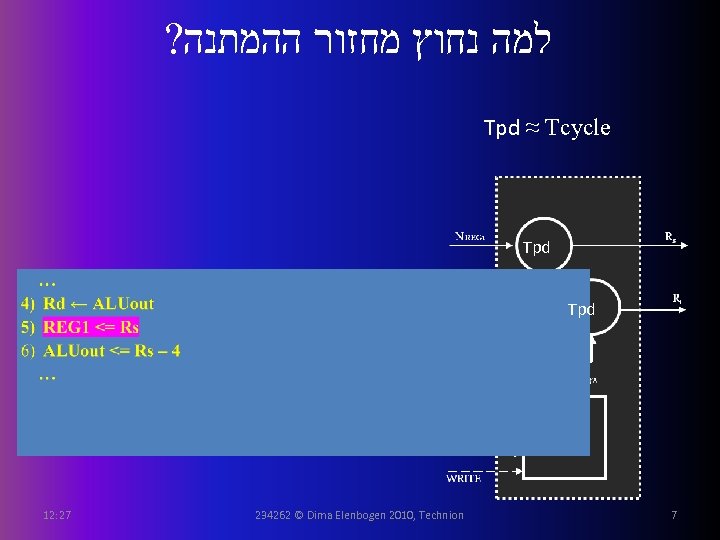

? למה נחוץ מחזור ההמתנה Tpd ≈ Tcycle Tpd 12: 27 234262 © Dima Elenbogen 2010, Technion 7

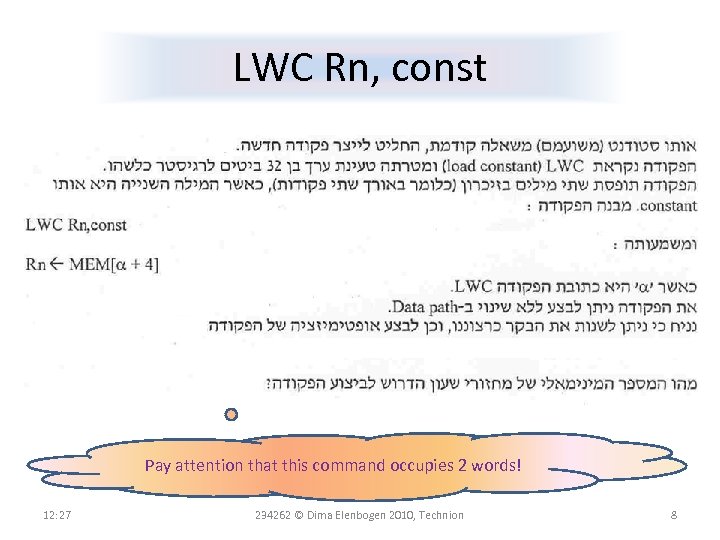

LWC Rn, const Pay attention that this command occupies 2 words! 12: 27 234262 © Dima Elenbogen 2010, Technion 8

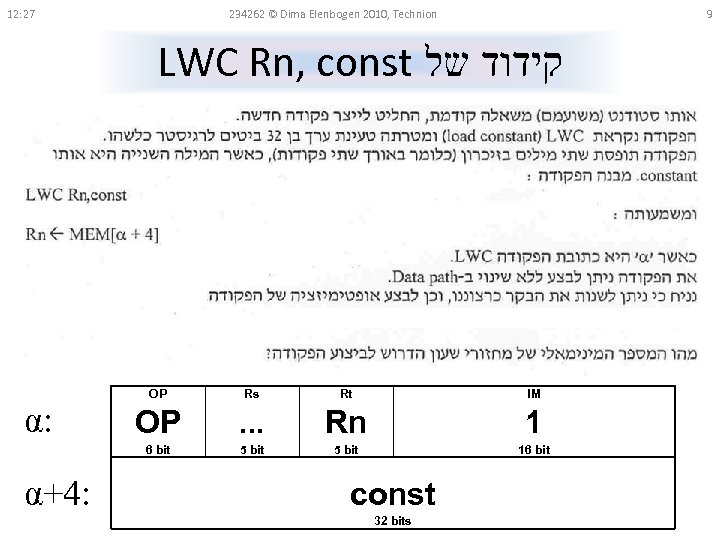

12: 27 234262 © Dima Elenbogen 2010, Technion 9 LWC Rn, const קידוד של α+4: Rs Rt IM OP . . . Rn 1 6 bit α: OP 5 bit 16 bit const 32 bits

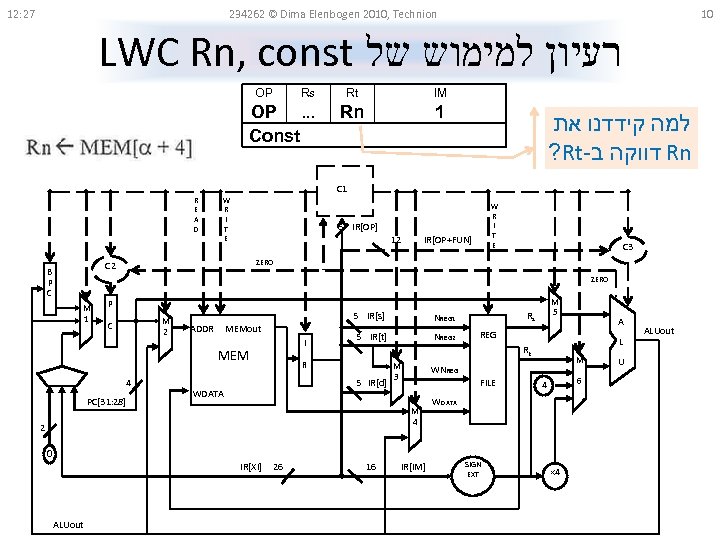

12: 27 234262 © Dima Elenbogen 2010, Technion 10 LWC Rn, const רעיון למימוש של OP Rs OP. . . Const Rt IM Rn 1 למה קידדנו את ? Rt- דווקה ב Rn C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P M 2 C 5 IR[s] ADDR MEMout I MEM 4 PC[31: 28] NREG 2 5 IR[d] M 3 L 2 M WNREG FILE M 4 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A REG Rt R WDATA NREG 1 5 IR[t] M 5 Rs SIGN EXT 4 U ALUout

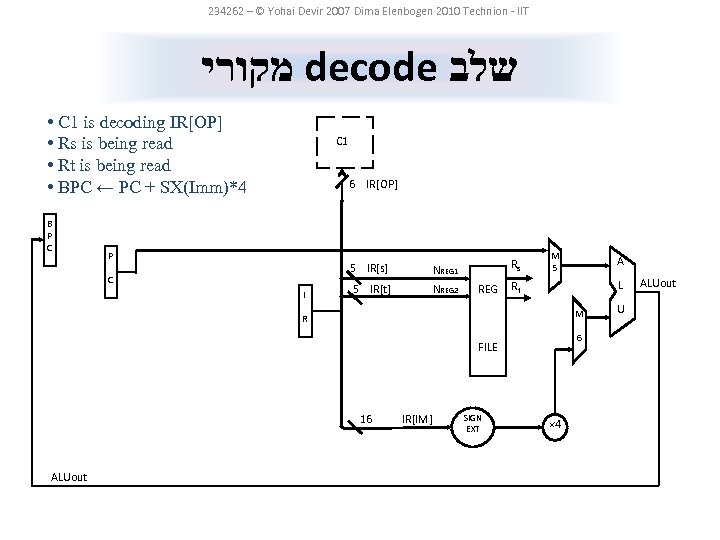

234262 – © Yohai Devir 2007 Dima Elenbogen 2010 Technion - IIT מקורי decode שלב • C 1 is decoding IR[OP] • Rs is being read • Rt is being read • BPC ← PC + SX(Imm)*4 B P C C 1 6 IR[OP] P 5 IR[s] C I NREG 1 5 IR[t] NREG 2 Rs REG M 5 L Rt M R 6 FILE 16 ALUout A IR[IM] SIGN EXT 4 U ALUout

234262 – © Yohai Devir 2007 Dima Elenbogen 2010 Technion - IIT decode תוספת בשלב OP Rt IM OP • C 1 is decoding IR[OP] • . . . • BPC ← PC + SX(Imm)*4 • MEMout <= MEM(PC) Rs . . . Rn 1 // BPC ← α + 8 // Read the const value from the memory C 1 השינוי לא פוגע ! בפקודות אחרות B P C M 1 6 IR[OP] M 5 P C M 2 ADDR MEMout MEM L I M R 6 WDATA 16 ALUout A IR[IM] SIGN EXT 4 U ALUout

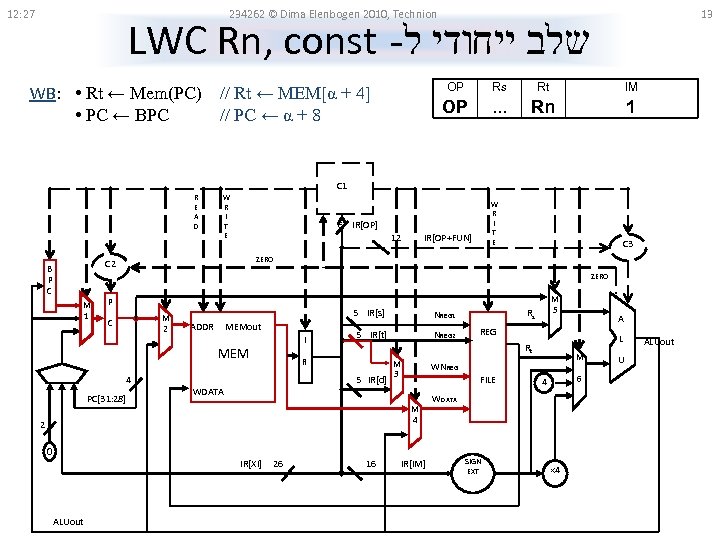

12: 27 234262 © Dima Elenbogen 2010, Technion 13 LWC Rn, const - שלב ייחודי ל WB: • Rt ← Mem(PC) • PC ← BPC OP Rs Rt IM OP // Rt ← MEM[α + 4] // PC ← α + 8 . . . Rn 1 C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P M 2 C 5 IR[s] ADDR MEMout I MEM 4 PC[31: 28] NREG 2 5 IR[d] M 3 L 2 M WNREG FILE M 4 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A REG Rt R WDATA Rs NREG 1 5 IR[t] M 5 SIGN EXT 4 U ALUout

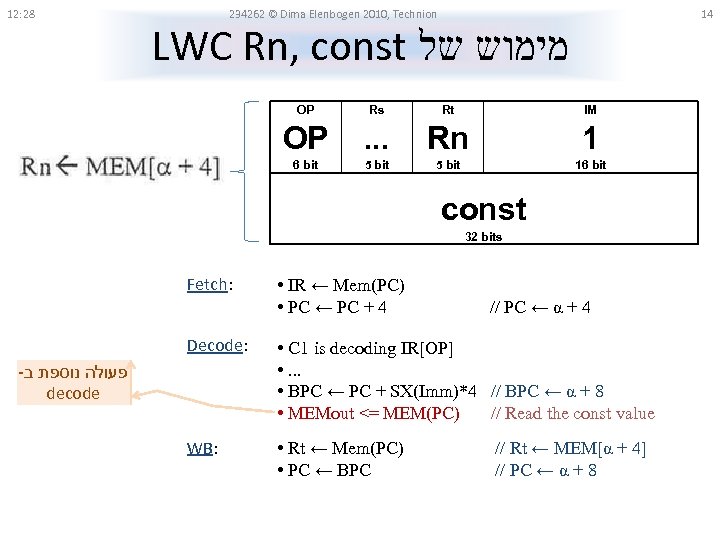

12: 28 234262 © Dima Elenbogen 2010, Technion 14 LWC Rn, const מימוש של OP Rs Rt IM OP . . . Rn 1 6 bit 5 bit 16 bit const 32 bits Fetch: • IR ← Mem(PC) • PC ← PC + 4 // PC ← α + 4 Decode: • C 1 is decoding IR[OP] • . . . • BPC ← PC + SX(Imm)*4 // BPC ← α + 8 • MEMout <= MEM(PC) // Read the const value WB: • Rt ← Mem(PC) • PC ← BPC - פעולה נוספת ב decode // Rt ← MEM[α + 4] // PC ← α + 8

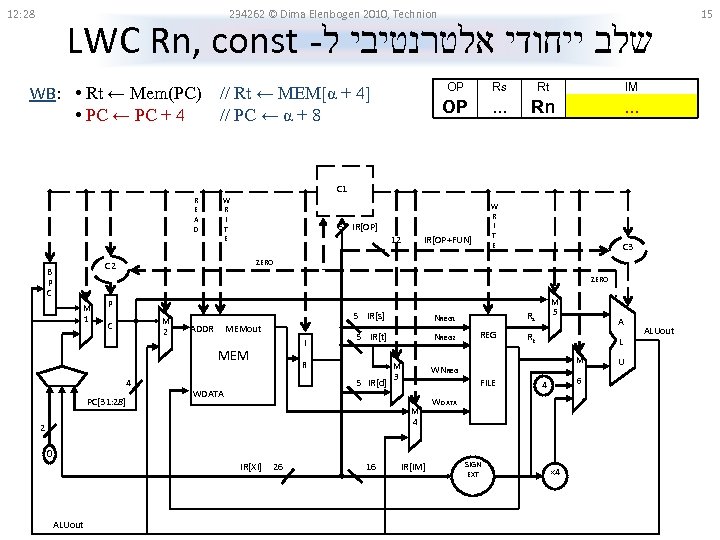

12: 28 234262 © Dima Elenbogen 2010, Technion LWC Rn, const - שלב ייחודי אלטרנטיבי ל WB: • Rt ← Mem(PC) • PC ← PC + 4 OP Rs Rt IM OP // Rt ← MEM[α + 4] // PC ← α + 8 . . . Rn . . . C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P M 2 C 5 IR[s] ADDR MEMout I MEM 4 PC[31: 28] R 5 IR[d] WDATA NREG 1 5 IR[t] NREG 2 M 3 REG L M FILE 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A Rt WNREG M 4 2 M 5 Rs SIGN EXT 4 U ALUout 15

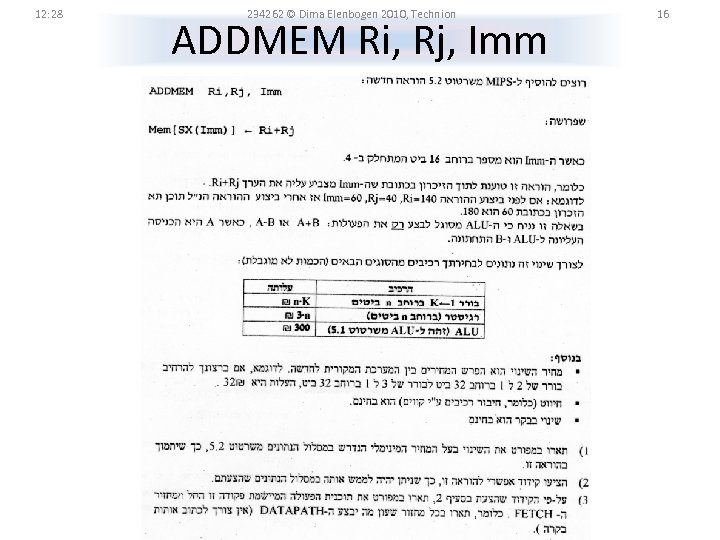

12: 28 234262 © Dima Elenbogen 2010, Technion ADDMEM Ri, Rj, Imm 16

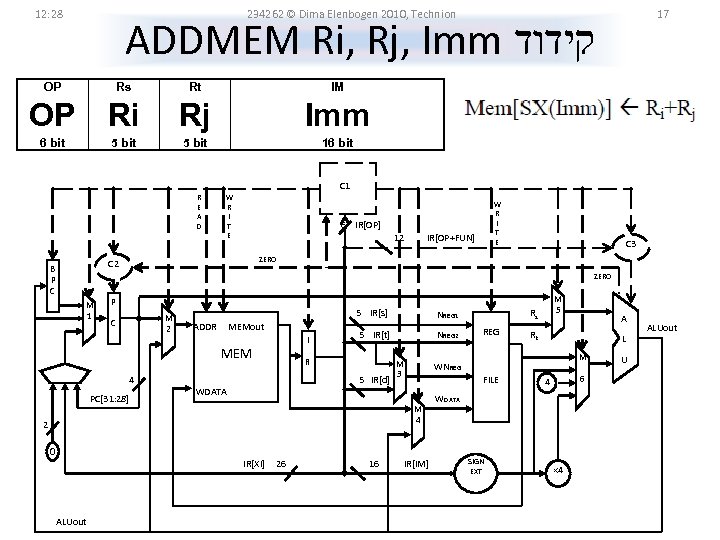

12: 28 234262 © Dima Elenbogen 2010, Technion 17 ADDMEM Ri, Rj, Imm קידוד OP Rs Rt IM OP Ri Rj Imm 6 bit 5 bit 16 bit C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P M 2 C 5 IR[s] ADDR MEMout I MEM 4 PC[31: 28] R 5 IR[d] WDATA NREG 2 M 3 REG L M FILE 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A Rt WNREG M 4 2 Rs NREG 1 5 IR[t] M 5 SIGN EXT 4 U ALUout

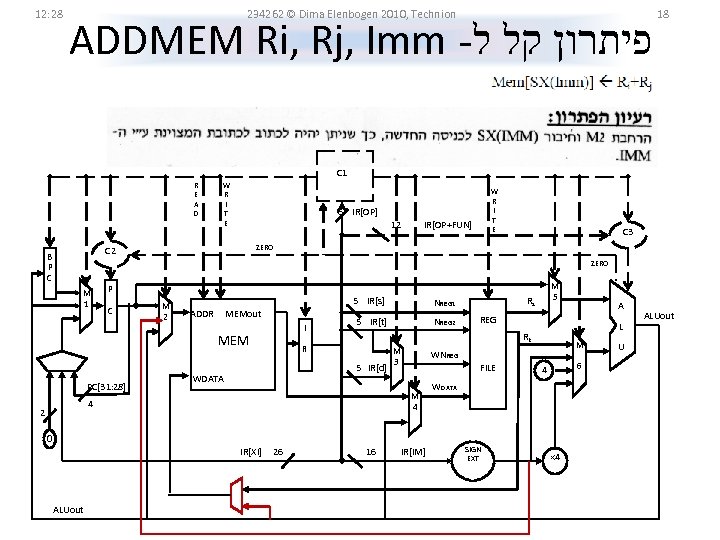

12: 28 234262 © Dima Elenbogen 2010, Technion ADDMEM Ri, Rj, Imm - פיתרון קל ל 18 C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P C M 2 5 IR[s] ADDR MEMout I MEM PC[31: 28] 5 IR[d] M 3 L M WNREG FILE M 4 4 2 NREG 2 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A REG Rt R WDATA NREG 1 5 IR[t] M 5 Rs SIGN EXT 4 U ALUout

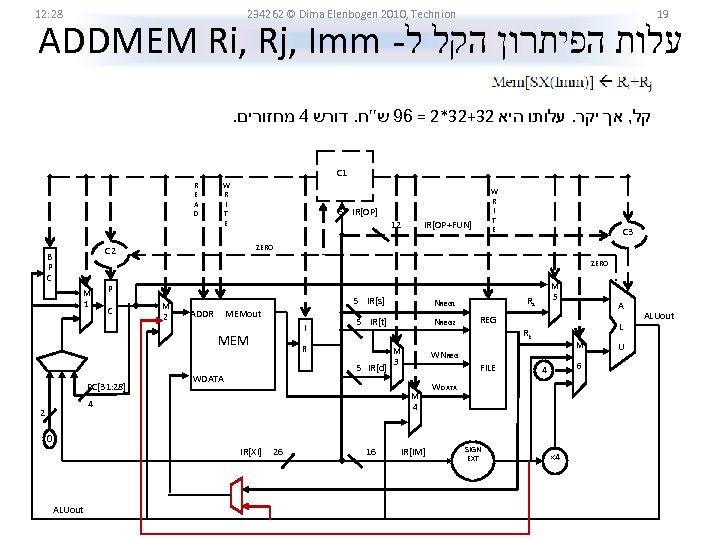

12: 28 234262 © Dima Elenbogen 2010, Technion 19 ADDMEM Ri, Rj, Imm - עלות הפיתרון הקל ל . קל, אך יקר. עלותו היא 23+23*2 = 69 ש''ח. דורש 4 מחזורים C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P C M 2 5 IR[s] ADDR MEMout I MEM PC[31: 28] R 5 IR[d] WDATA NREG 2 M 3 L Rt M FILE 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A REG WNREG M 4 4 2 NREG 1 5 IR[t] M 5 Rs SIGN EXT 4 U ALUout

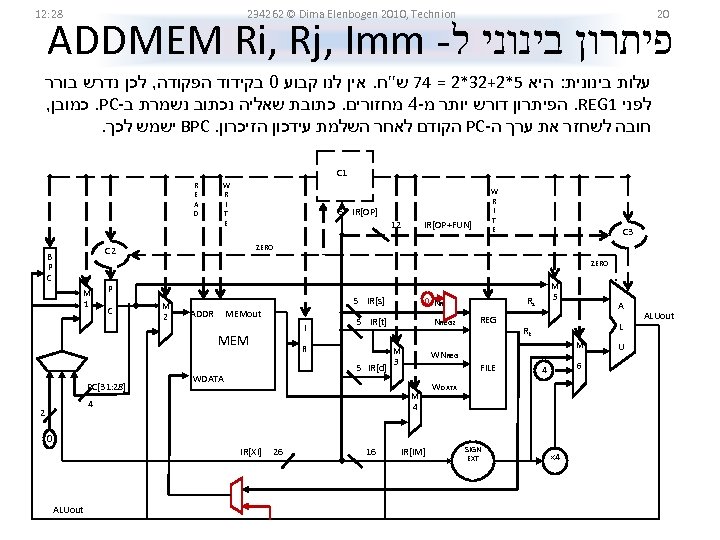

12: 28 234262 © Dima Elenbogen 2010, Technion 20 ADDMEM Ri, Rj, Imm - פיתרון בינוני ל עלות בינונית: היא 5*2+23*2 = 47 ש''ח. אין לנו קבוע 0 בקידוד הפקודה, לכן נדרש בורר , . כמובן PC-. הפיתרון דורש יותר מ-4 מחזורים. כתובת שאליה נכתוב נשמרת ב REG 1 לפני . ישמש לכך BPC. הקודם לאחר השלמת עידכון הזיכרון PC- חובה לשחזר את ערך ה C 1 R E A D W R I T E 6 IR[OP] 12 IR[OP+FUN] C 3 ZERO C 2 B P C W R I T E ZERO M 1 P C M 2 5 IR[s] ADDR MEMout I MEM PC[31: 28] 5 IR[t] R 5 IR[d] WDATA M 3 M 5 Rs NREG 1 NREG 2 REG Rt M FILE 6 4 WDATA 0 IR[XI] ALUout 26 16 IR[IM] A L WNREG M 4 4 2 0 SIGN EXT 4 U ALUout

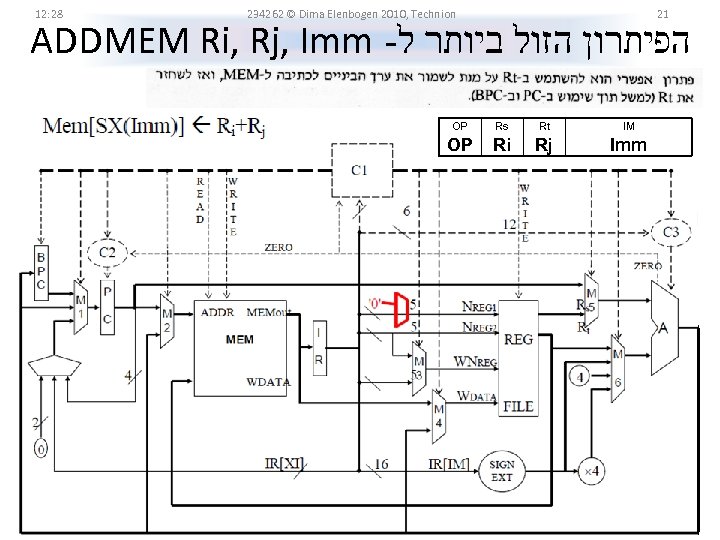

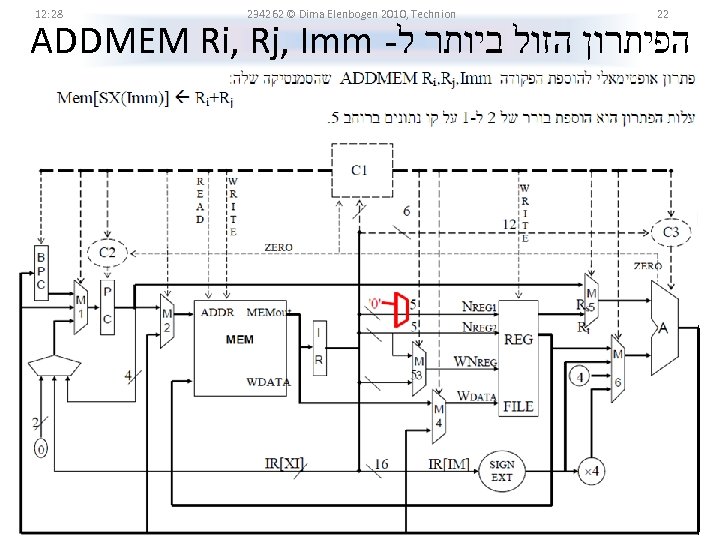

12: 28 234262 © Dima Elenbogen 2010, Technion 21 ADDMEM Ri, Rj, Imm - הפיתרון הזול ביותר ל OP Rs Rt IM OP Ri Rj Imm

12: 28 234262 © Dima Elenbogen 2010, Technion 22 ADDMEM Ri, Rj, Imm - הפיתרון הזול ביותר ל

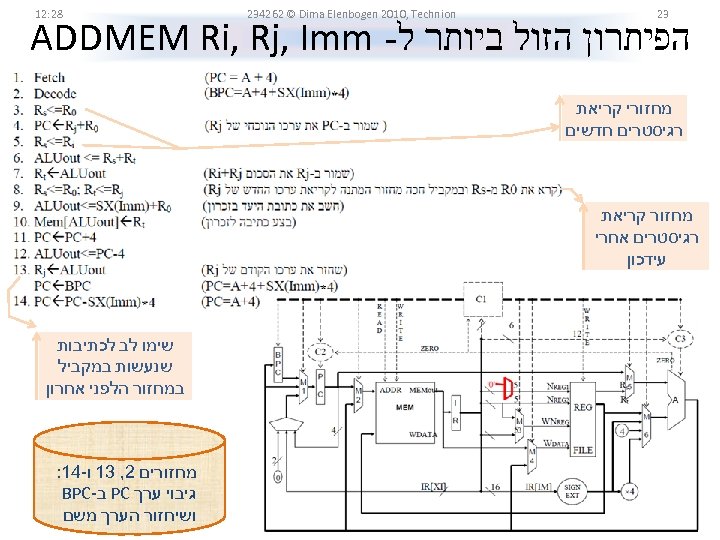

32 234262 © Dima Elenbogen 2010, Technion 82: 21 הפיתרון הזול ביותר ל- ADDMEM Ri, Rj, Imm מחזורי קריאת רגיסטרים חדשים מחזור קריאת רגיסטרים אחרי עידכון שימו לב לכתיבות שנעשות במקביל במחזור הלפני אחרון מחזורים 2, 31 ו-41: גיבוי ערך PC ב- BPC ושיחזור הערך משם

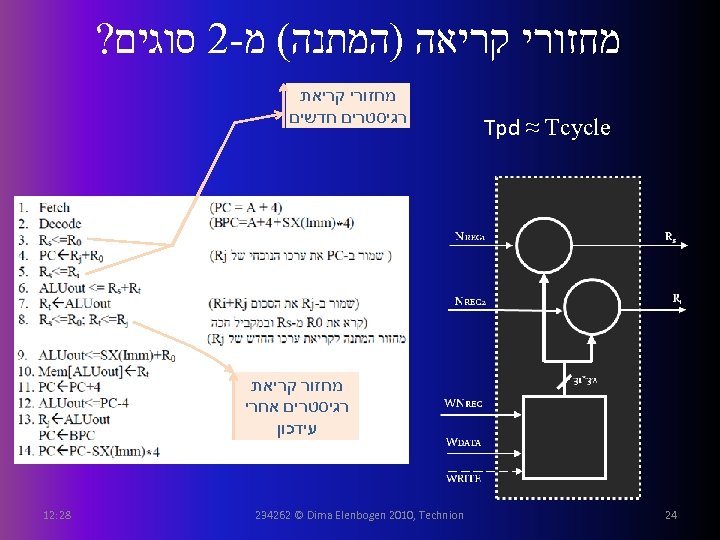

מחזורי קריאה )המתנה( מ-2 סוגים? Tpd ≈ Tcycle מחזורי קריאת רגיסטרים חדשים Tpd מחזור קריאת רגיסטרים אחרי עידכון 42 234262 © Dima Elenbogen 2010, Technion 82: 21

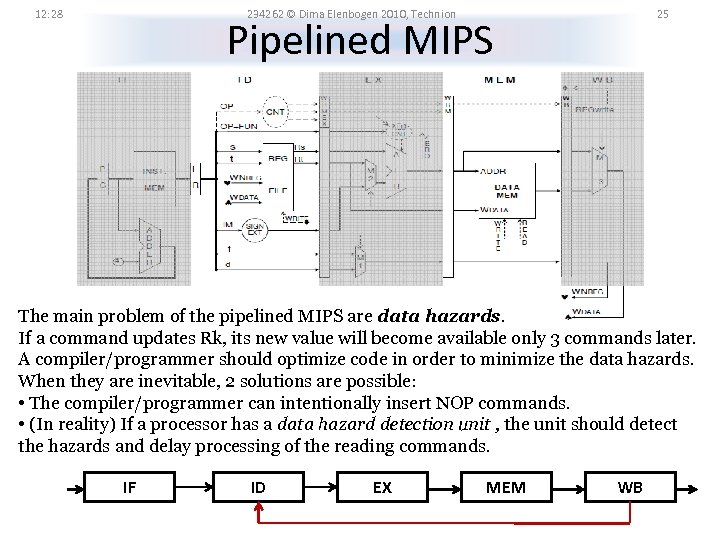

12: 28 234262 © Dima Elenbogen 2010, Technion 25 Pipelined MIPS The main problem of the pipelined MIPS are data hazards. If a command updates Rk, its new value will become available only 3 commands later. A compiler/programmer should optimize code in order to minimize the data hazards. When they are inevitable, 2 solutions are possible: • The compiler/programmer can intentionally insert NOP commands. • (In reality) If a processor has a data hazard detection unit , the unit should detect the hazards and delay processing of the reading commands. IF ID EX MEM WB

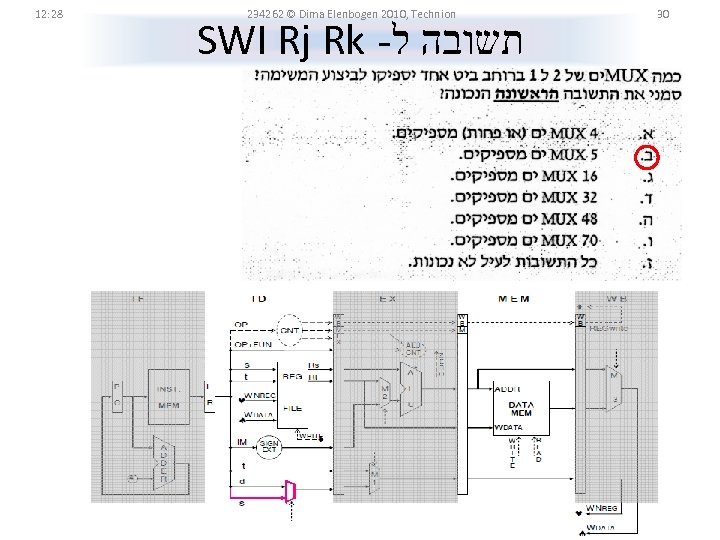

12: 28 234262 © Dima Elenbogen 2010, Technion SWI Rj Rk 26

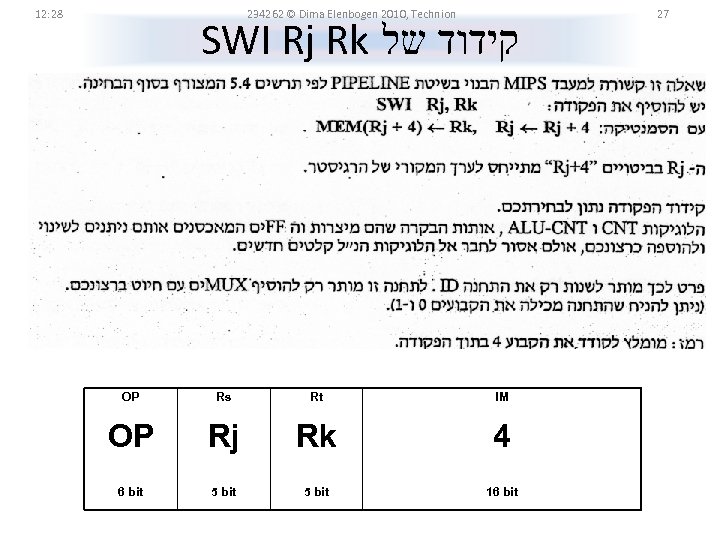

12: 28 234262 © Dima Elenbogen 2010, Technion SWI Rj Rk קידוד של OP Rs Rt IM OP Rj Rk 4 6 bit 5 bit 16 bit 27

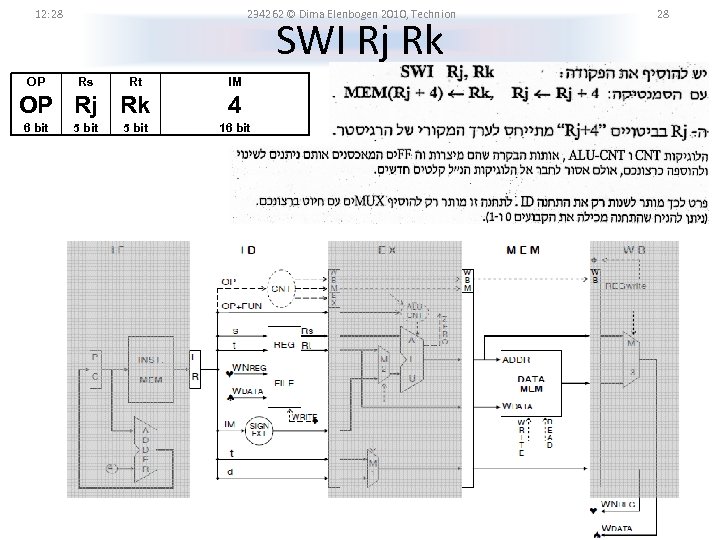

12: 28 OP 234262 © Dima Elenbogen 2010, Technion SWI Rj Rk Rs Rt OP Rj Rk 6 bit 5 bit IM 4 16 bit 28

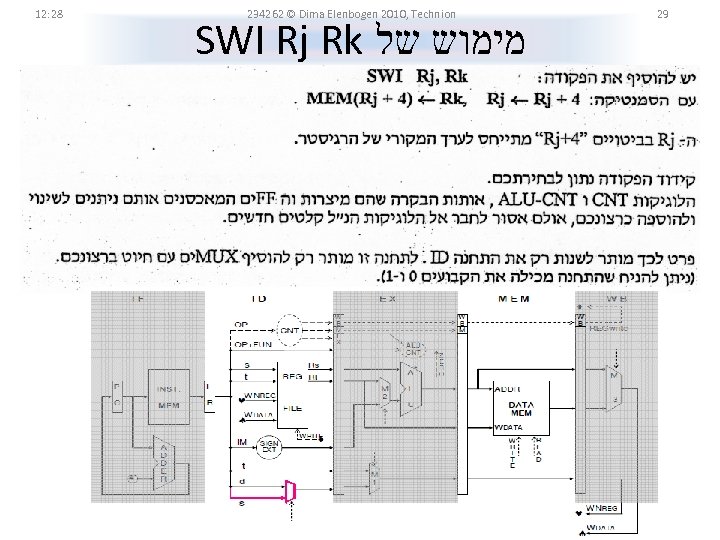

12: 28 234262 © Dima Elenbogen 2010, Technion SWI Rj Rk מימוש של 29

12: 28 234262 © Dima Elenbogen 2010, Technion SWI Rj Rk - תשובה ל 30

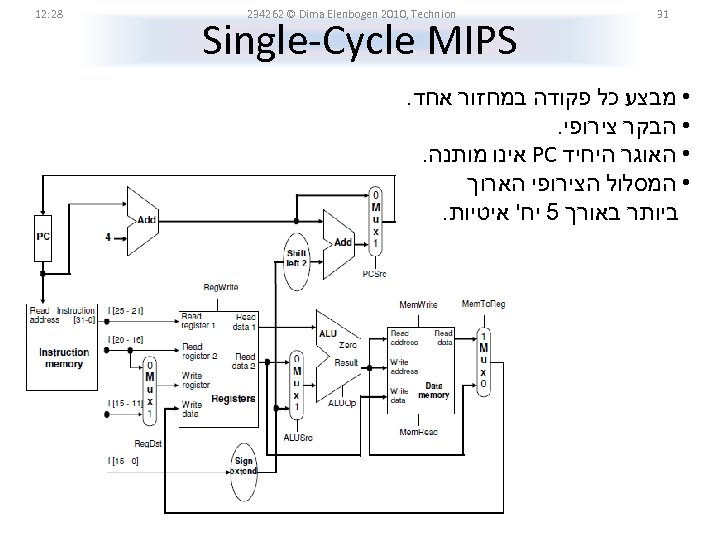

13 234262 © Dima Elenbogen 2010, Technion Single-Cycle MIPS • מבצע כל פקודה במחזור אחד. • הבקר צירופי. • האוגר היחיד PC אינו מותנה. • המסלול הצירופי הארוך ביותר באורך 5 יח' איטיות. 82: 21

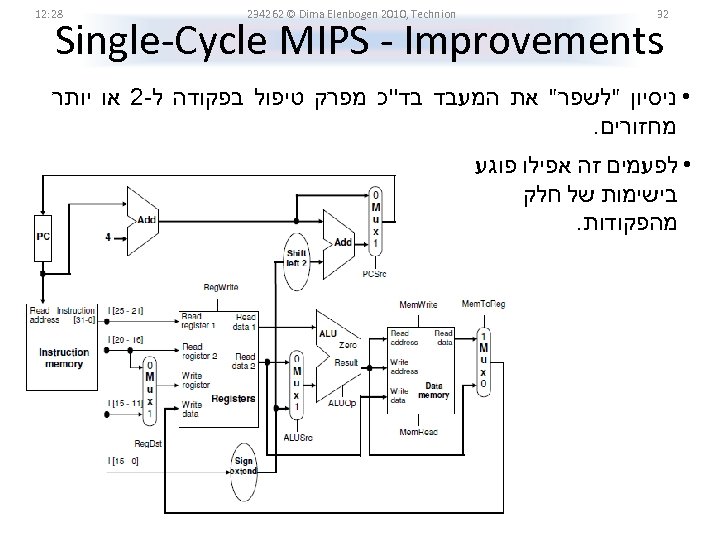

23 234262 © Dima Elenbogen 2010, Technion 82: 21 Single-Cycle MIPS - Improvements • ניסיון "לשפר" את המעבד בד''כ מפרק טיפול בפקודה ל-2 או יותר מחזורים. • לפעמים זה אפילו פוגע בישימות של חלק מהפקודות.

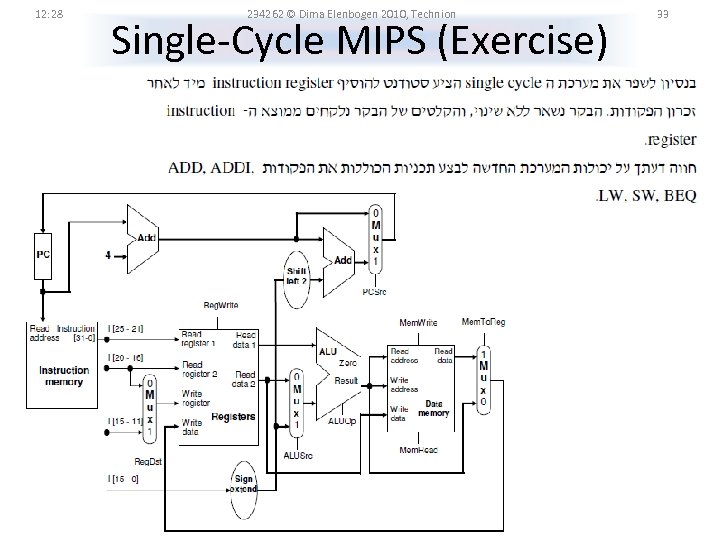

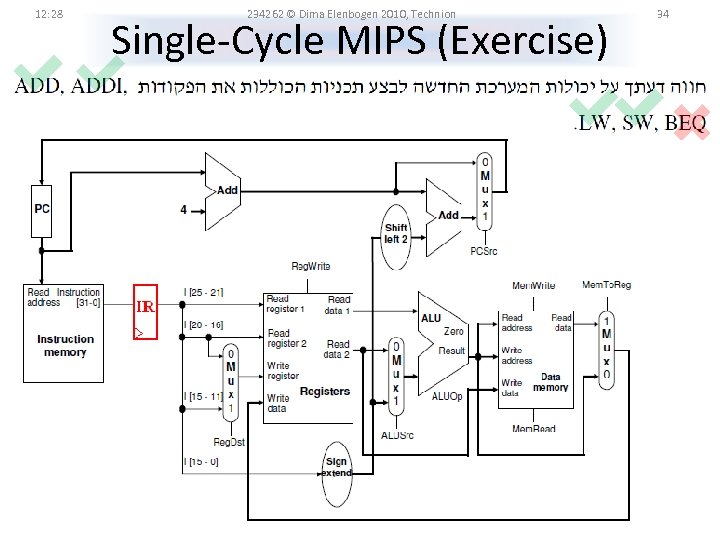

12: 28 234262 © Dima Elenbogen 2010, Technion Single-Cycle MIPS (Exercise) 33

12: 28 234262 © Dima Elenbogen 2010, Technion Single-Cycle MIPS (Exercise) 34

! בהצלחה בבחינות ! ואל תעשו בהן טעויות מטופשות © Dima Elenbogen 2010, Technion – Israel Institute of Technology

ca97ed36422da04735ab4177be8ff9ca.ppt