a9f8240c8326b8529865d1c1192f2adc.ppt

- Количество слайдов: 40

2002 International Conference on Electronics Packaging (ICEP) JIEP/ IMAPS Japan, IEEE CPMT Japan Chapter Dai-ichi Hotel Seafort, Tokyo, Japan April 17 -19, 2002 Techniques and Tools for Product-Specific Analysis Templates Towards Enhanced CAD-CAE Interoperability for Simulation-Based Design and Related Topics http: //eislab. gatech. edu/pubs/conferences/2002 -jiep-icep-peak/ Russell Peak Senior Researcher Manufacturing Research Center Georgia Tech

2002 International Conference on Electronics Packaging (ICEP) JIEP/ IMAPS Japan, IEEE CPMT Japan Chapter Dai-ichi Hotel Seafort, Tokyo, Japan April 17 -19, 2002 Techniques and Tools for Product-Specific Analysis Templates Towards Enhanced CAD-CAE Interoperability for Simulation-Based Design and Related Topics http: //eislab. gatech. edu/pubs/conferences/2002 -jiep-icep-peak/ Russell Peak Senior Researcher Manufacturing Research Center Georgia Tech

Abstract http: //eislab. gatech. edu/pubs/conferences/2002 -jiep-icep-peak/ Techniques and Tools for Product-Specific Analysis Templates Towards Enhanced CAD-CAE Interoperability for Simulation-Based Design and Related Topics Design engineers are becoming increasingly aware of “analysis template” pockets that exist in their product domain. For example, thermal resistance and interconnect reliability analysis are common templates for electronic chip packages, while tire-roadway templates exist to verify handling, durability, and slip requirements. Such templates may be captured as paper-based notes and design standards, as well as loosely structured spreadsheets and electronic workbooks. Often, however, they are not articulated in any persistent form. Some CAD/E software vendors are offering pre-packaged analysis template catalogs like the above; however, they are typically dependent on a specific toolset and do not present design-analysis idealization associativity to the user. Thus, it is difficult to adapt, extend, or transfer analysis template knowledge. As noted in places like the 2001 International Technology Roadmap for Semiconductors (ITRS), domain- and tool-independent techniques and related standards are necessary. This paper overviews infrastructure needs and emerging analysis template theory and methodology that addresses such issues. Patterns that naturally exist in between traditional CAD and CAE models are summarized, along with their embodiment in a knowledge representation known as constrained objects. Industrial applications for airframe structural analysis, circuit board thermomechanical analysis, and chip package thermal resistance analysis are noted. This approach enhances knowledge capture, modularity, and reusability, as well as improves automation (e. g. , decreasing total simulation cycle time by 75%). The object patterns also identify where best to apply information technologies like STEP, XML, CORBA/SOAP, and web services. We believe further benefits are possible if these patterns are combined with other efforts to enable ubiquitous analysis template technology. Trends and needs towards this end are discussed, including analogies with electronics like JEDEC package standards and mechanical subsystems. 2

Abstract http: //eislab. gatech. edu/pubs/conferences/2002 -jiep-icep-peak/ Techniques and Tools for Product-Specific Analysis Templates Towards Enhanced CAD-CAE Interoperability for Simulation-Based Design and Related Topics Design engineers are becoming increasingly aware of “analysis template” pockets that exist in their product domain. For example, thermal resistance and interconnect reliability analysis are common templates for electronic chip packages, while tire-roadway templates exist to verify handling, durability, and slip requirements. Such templates may be captured as paper-based notes and design standards, as well as loosely structured spreadsheets and electronic workbooks. Often, however, they are not articulated in any persistent form. Some CAD/E software vendors are offering pre-packaged analysis template catalogs like the above; however, they are typically dependent on a specific toolset and do not present design-analysis idealization associativity to the user. Thus, it is difficult to adapt, extend, or transfer analysis template knowledge. As noted in places like the 2001 International Technology Roadmap for Semiconductors (ITRS), domain- and tool-independent techniques and related standards are necessary. This paper overviews infrastructure needs and emerging analysis template theory and methodology that addresses such issues. Patterns that naturally exist in between traditional CAD and CAE models are summarized, along with their embodiment in a knowledge representation known as constrained objects. Industrial applications for airframe structural analysis, circuit board thermomechanical analysis, and chip package thermal resistance analysis are noted. This approach enhances knowledge capture, modularity, and reusability, as well as improves automation (e. g. , decreasing total simulation cycle time by 75%). The object patterns also identify where best to apply information technologies like STEP, XML, CORBA/SOAP, and web services. We believe further benefits are possible if these patterns are combined with other efforts to enable ubiquitous analysis template technology. Trends and needs towards this end are discussed, including analogies with electronics like JEDEC package standards and mechanical subsystems. 2

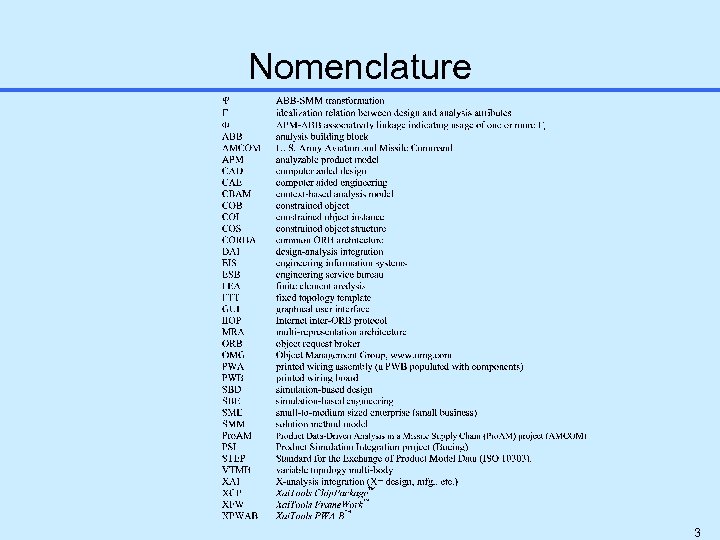

Nomenclature 3

Nomenclature 3

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 4

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 4

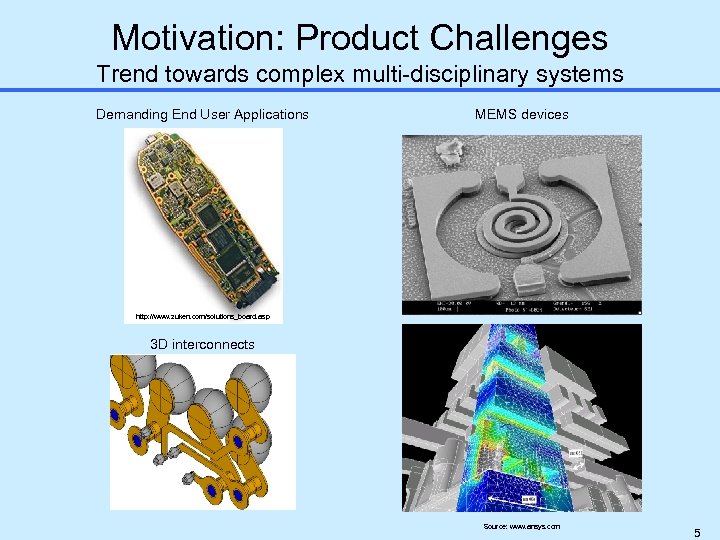

Motivation: Product Challenges Trend towards complex multi-disciplinary systems Demanding End User Applications MEMS devices http: //www. zuken. com/solutions_board. asp 3 D interconnects Source: www. ansys. com 5

Motivation: Product Challenges Trend towards complex multi-disciplinary systems Demanding End User Applications MEMS devices http: //www. zuken. com/solutions_board. asp 3 D interconnects Source: www. ansys. com 5

Motivation: Engineering Tool Challenges 2001 International Technology Roadmap for Semiconductors (ITRS) http: //public. itrs. net/Files/2001 ITRS/Home. htm u Design Sharing and Reuse – Tool interoperability – Standard IC information model – Integration of multi-vendor and internal design technology – Reduction of integration cost u Simulation module integration – Seamless integration of simulation modules – Interplay of modules to enhance design effectiveness 6

Motivation: Engineering Tool Challenges 2001 International Technology Roadmap for Semiconductors (ITRS) http: //public. itrs. net/Files/2001 ITRS/Home. htm u Design Sharing and Reuse – Tool interoperability – Standard IC information model – Integration of multi-vendor and internal design technology – Reduction of integration cost u Simulation module integration – Seamless integration of simulation modules – Interplay of modules to enhance design effectiveness 6

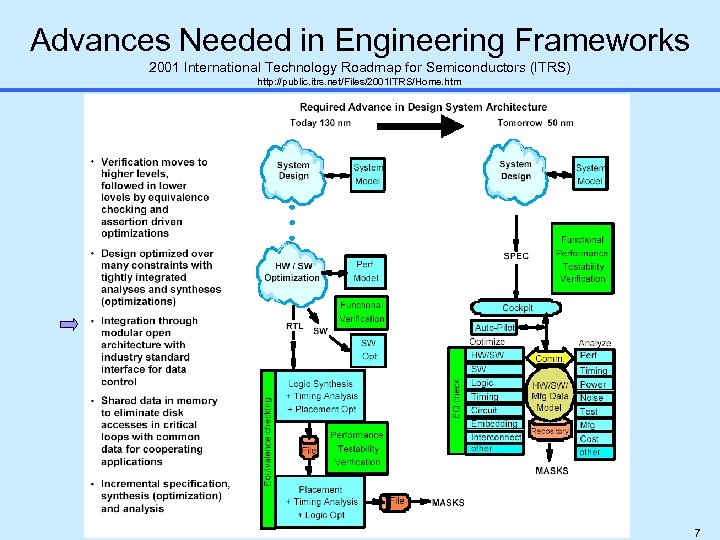

Advances Needed in Engineering Frameworks 2001 International Technology Roadmap for Semiconductors (ITRS) http: //public. itrs. net/Files/2001 ITRS/Home. htm 7

Advances Needed in Engineering Frameworks 2001 International Technology Roadmap for Semiconductors (ITRS) http: //public. itrs. net/Files/2001 ITRS/Home. htm 7

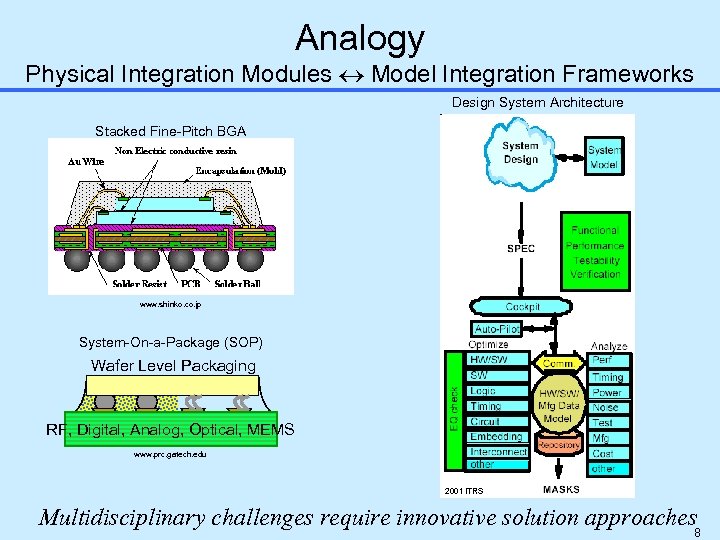

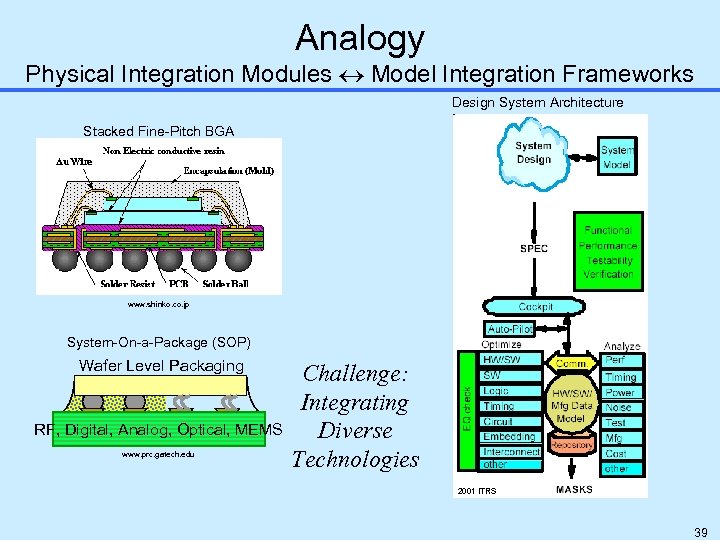

Analogy Physical Integration Modules Model Integration Frameworks Design System Architecture Stacked Fine-Pitch BGA www. shinko. co. jp System-On-a-Package (SOP) Wafer Level Packaging RF, Digital, Analog, Optical, MEMS www. prc. gatech. edu 2001 ITRS Multidisciplinary challenges require innovative solution approaches 8

Analogy Physical Integration Modules Model Integration Frameworks Design System Architecture Stacked Fine-Pitch BGA www. shinko. co. jp System-On-a-Package (SOP) Wafer Level Packaging RF, Digital, Analog, Optical, MEMS www. prc. gatech. edu 2001 ITRS Multidisciplinary challenges require innovative solution approaches 8

Interoperability Seamless communication between people, their models, and their tools. u Requires techniques beyond traditional engineering – Information models » Abstract data types » Object-oriented languages (UML, STEP Express, …) – Knowledge representation » Constraint graphs, rules, … – Web/Internet computing » Middleware, agents, mobility, … u Emerging field: engineering information methods – Analogous to CAD and FEA methods 9

Interoperability Seamless communication between people, their models, and their tools. u Requires techniques beyond traditional engineering – Information models » Abstract data types » Object-oriented languages (UML, STEP Express, …) – Knowledge representation » Constraint graphs, rules, … – Web/Internet computing » Middleware, agents, mobility, … u Emerging field: engineering information methods – Analogous to CAD and FEA methods 9

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 10

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 10

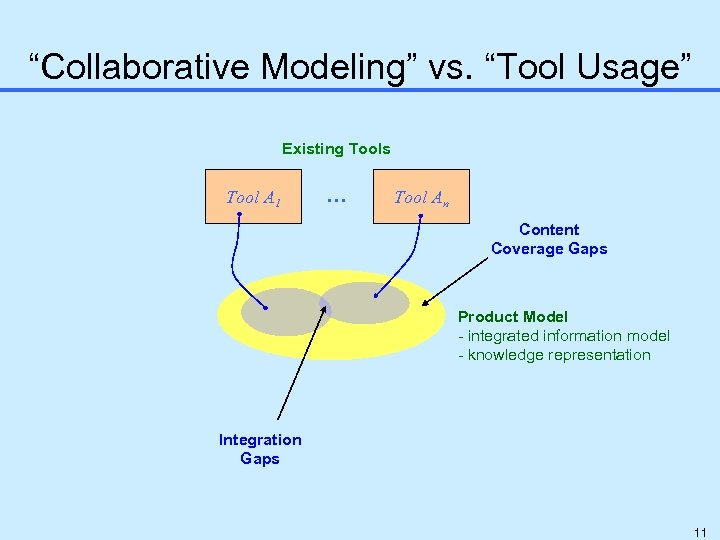

“Collaborative Modeling” vs. “Tool Usage” Existing Tools Tool A 1 . . . Tool An Content Coverage Gaps Product Model - integrated information model - knowledge representation Integration Gaps 11

“Collaborative Modeling” vs. “Tool Usage” Existing Tools Tool A 1 . . . Tool An Content Coverage Gaps Product Model - integrated information model - knowledge representation Integration Gaps 11

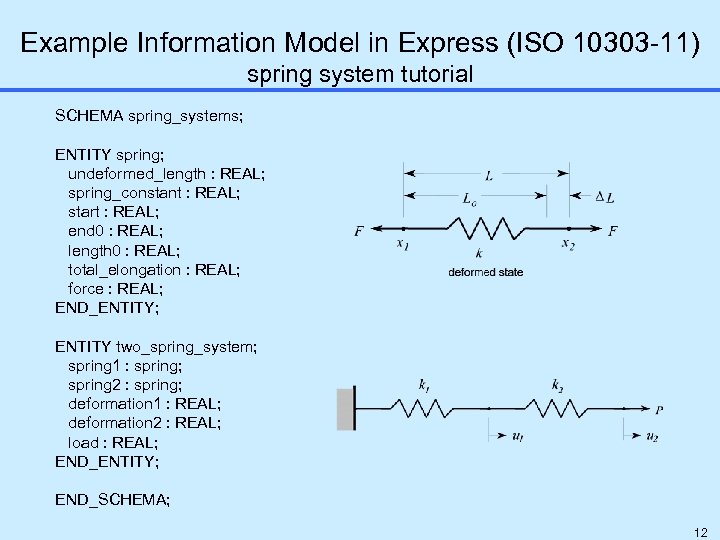

Example Information Model in Express (ISO 10303 -11) spring system tutorial SCHEMA spring_systems; ENTITY spring; undeformed_length : REAL; spring_constant : REAL; start : REAL; end 0 : REAL; length 0 : REAL; total_elongation : REAL; force : REAL; END_ENTITY; ENTITY two_spring_system; spring 1 : spring; spring 2 : spring; deformation 1 : REAL; deformation 2 : REAL; load : REAL; END_ENTITY; END_SCHEMA; 12

Example Information Model in Express (ISO 10303 -11) spring system tutorial SCHEMA spring_systems; ENTITY spring; undeformed_length : REAL; spring_constant : REAL; start : REAL; end 0 : REAL; length 0 : REAL; total_elongation : REAL; force : REAL; END_ENTITY; ENTITY two_spring_system; spring 1 : spring; spring 2 : spring; deformation 1 : REAL; deformation 2 : REAL; load : REAL; END_ENTITY; END_SCHEMA; 12

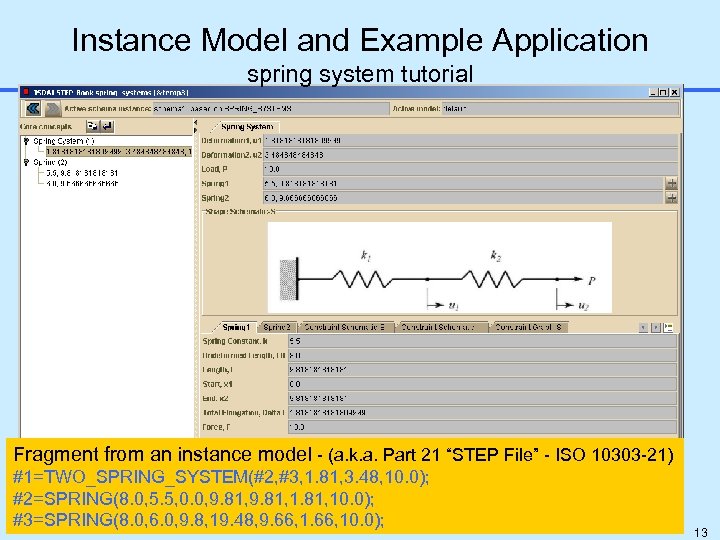

Instance Model and Example Application spring system tutorial Fragment from an instance model - (a. k. a. Part 21 “STEP File” - ISO 10303 -21) #1=TWO_SPRING_SYSTEM(#2, #3, 1. 81, 3. 48, 10. 0); #2=SPRING(8. 0, 5. 5, 0. 0, 9. 81, 10. 0); #3=SPRING(8. 0, 6. 0, 9. 8, 19. 48, 9. 66, 10. 0); 13

Instance Model and Example Application spring system tutorial Fragment from an instance model - (a. k. a. Part 21 “STEP File” - ISO 10303 -21) #1=TWO_SPRING_SYSTEM(#2, #3, 1. 81, 3. 48, 10. 0); #2=SPRING(8. 0, 5. 5, 0. 0, 9. 81, 10. 0); #3=SPRING(8. 0, 6. 0, 9. 8, 19. 48, 9. 66, 10. 0); 13

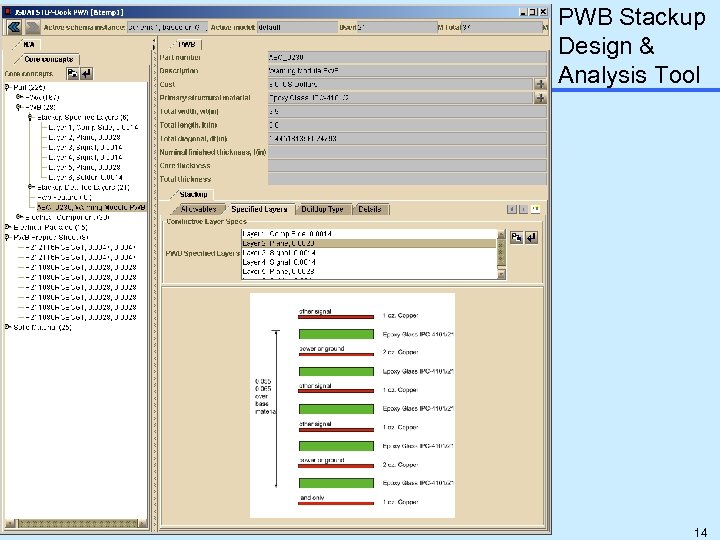

PWB Stackup Design & Analysis Tool 14

PWB Stackup Design & Analysis Tool 14

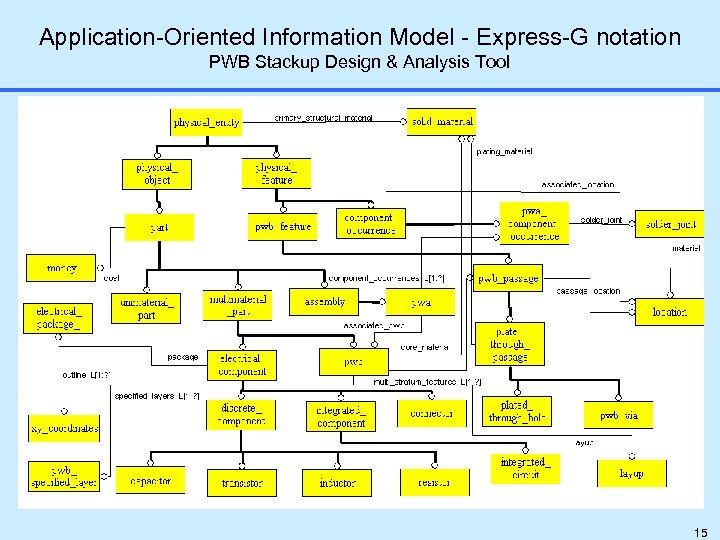

Application-Oriented Information Model - Express-G notation PWB Stackup Design & Analysis Tool 15

Application-Oriented Information Model - Express-G notation PWB Stackup Design & Analysis Tool 15

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 16

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 16

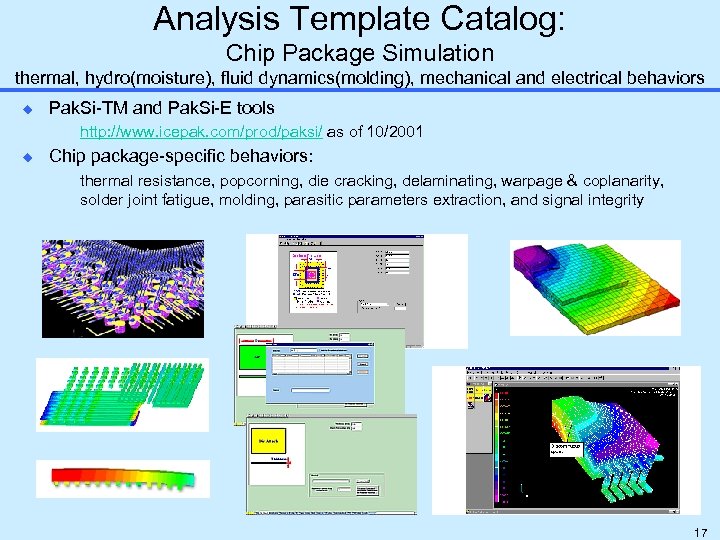

Analysis Template Catalog: Chip Package Simulation thermal, hydro(moisture), fluid dynamics(molding), mechanical and electrical behaviors u Pak. Si-TM and Pak. Si-E tools http: //www. icepak. com/prod/paksi/ as of 10/2001 u Chip package-specific behaviors: thermal resistance, popcorning, die cracking, delaminating, warpage & coplanarity, solder joint fatigue, molding, parasitic parameters extraction, and signal integrity 17

Analysis Template Catalog: Chip Package Simulation thermal, hydro(moisture), fluid dynamics(molding), mechanical and electrical behaviors u Pak. Si-TM and Pak. Si-E tools http: //www. icepak. com/prod/paksi/ as of 10/2001 u Chip package-specific behaviors: thermal resistance, popcorning, die cracking, delaminating, warpage & coplanarity, solder joint fatigue, molding, parasitic parameters extraction, and signal integrity 17

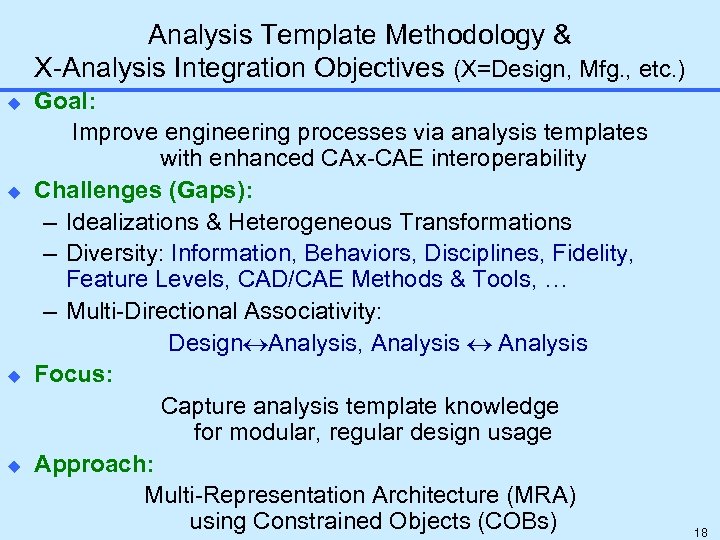

Analysis Template Methodology & X-Analysis Integration Objectives (X=Design, Mfg. , etc. ) u u Goal: Improve engineering processes via analysis templates with enhanced CAx-CAE interoperability Challenges (Gaps): – Idealizations & Heterogeneous Transformations – Diversity: Information, Behaviors, Disciplines, Fidelity, Feature Levels, CAD/CAE Methods & Tools, … – Multi-Directional Associativity: Design Analysis, Analysis Focus: Capture analysis template knowledge for modular, regular design usage Approach: Multi-Representation Architecture (MRA) using Constrained Objects (COBs) 18

Analysis Template Methodology & X-Analysis Integration Objectives (X=Design, Mfg. , etc. ) u u Goal: Improve engineering processes via analysis templates with enhanced CAx-CAE interoperability Challenges (Gaps): – Idealizations & Heterogeneous Transformations – Diversity: Information, Behaviors, Disciplines, Fidelity, Feature Levels, CAD/CAE Methods & Tools, … – Multi-Directional Associativity: Design Analysis, Analysis Focus: Capture analysis template knowledge for modular, regular design usage Approach: Multi-Representation Architecture (MRA) using Constrained Objects (COBs) 18

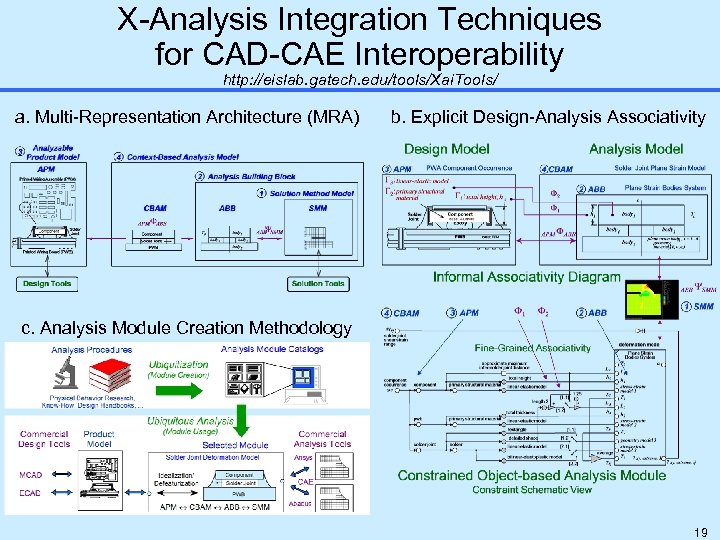

X-Analysis Integration Techniques for CAD-CAE Interoperability http: //eislab. gatech. edu/tools/Xai. Tools/ a. Multi-Representation Architecture (MRA) b. Explicit Design-Analysis Associativity c. Analysis Module Creation Methodology 19

X-Analysis Integration Techniques for CAD-CAE Interoperability http: //eislab. gatech. edu/tools/Xai. Tools/ a. Multi-Representation Architecture (MRA) b. Explicit Design-Analysis Associativity c. Analysis Module Creation Methodology 19

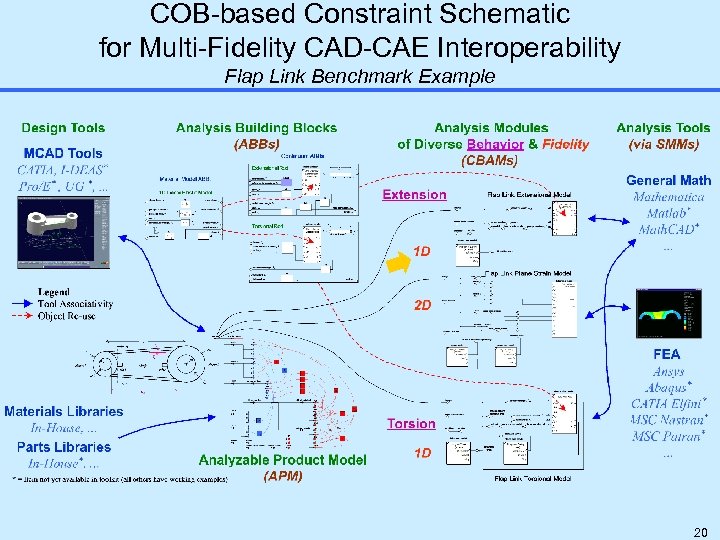

COB-based Constraint Schematic for Multi-Fidelity CAD-CAE Interoperability Flap Link Benchmark Example 20

COB-based Constraint Schematic for Multi-Fidelity CAD-CAE Interoperability Flap Link Benchmark Example 20

An Introduction to X-Analysis Integration (XAI) Short Course Outline Part 1: Constrained Objects (COBs) Primer – Nomenclature Part 2: Multi-Representation Architecture (MRA) Primer – Analysis Integration Challenges – Overview of COB-based XAI Part 3: Example Applications » Airframe Structural Analysis (Boeing) » Circuit Board Thermomechanical Analysis (Do. D, JPL/NASA) » Chip Package Thermal Analysis (Shinko) – Summary Part 4: Advanced Topics & Current Research 21

An Introduction to X-Analysis Integration (XAI) Short Course Outline Part 1: Constrained Objects (COBs) Primer – Nomenclature Part 2: Multi-Representation Architecture (MRA) Primer – Analysis Integration Challenges – Overview of COB-based XAI Part 3: Example Applications » Airframe Structural Analysis (Boeing) » Circuit Board Thermomechanical Analysis (Do. D, JPL/NASA) » Chip Package Thermal Analysis (Shinko) – Summary Part 4: Advanced Topics & Current Research 21

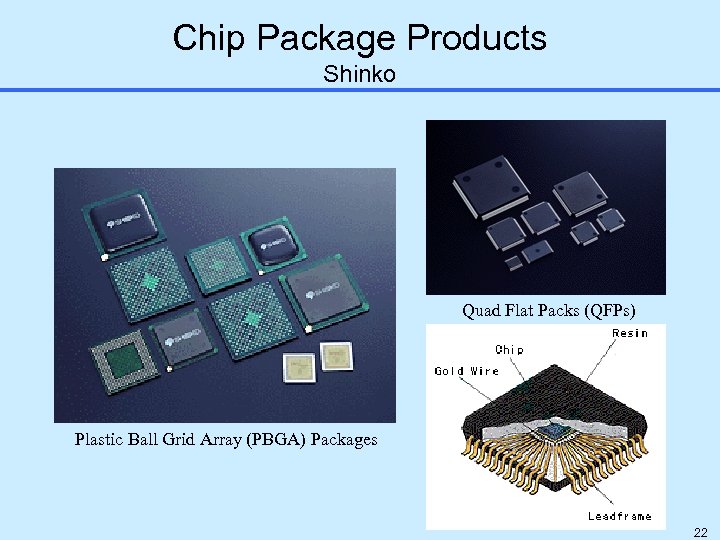

Chip Package Products Shinko Quad Flat Packs (QFPs) Plastic Ball Grid Array (PBGA) Packages 22

Chip Package Products Shinko Quad Flat Packs (QFPs) Plastic Ball Grid Array (PBGA) Packages 22

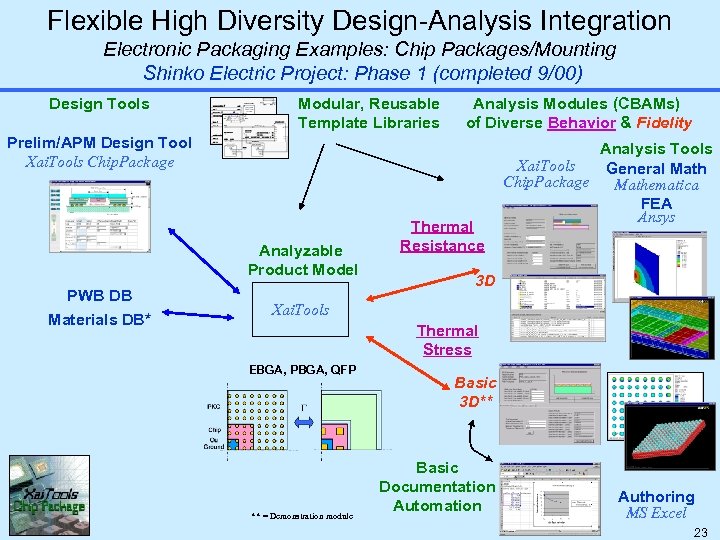

Flexible High Diversity Design-Analysis Integration Electronic Packaging Examples: Chip Packages/Mounting Shinko Electric Project: Phase 1 (completed 9/00) Design Tools Modular, Reusable Template Libraries Analysis Modules (CBAMs) of Diverse Behavior & Fidelity Prelim/APM Design Tool Xai. Tools Chip. Package Analyzable Product Model PWB DB Materials DB* Thermal Resistance Analysis Tools Xai. Tools General Math Chip. Package Mathematica FEA Ansys 3 D Xai. Tools Thermal Stress EBGA, PBGA, QFP ** = Demonstration module Basic 3 D** Basic Documentation Automation Authoring MS Excel 23

Flexible High Diversity Design-Analysis Integration Electronic Packaging Examples: Chip Packages/Mounting Shinko Electric Project: Phase 1 (completed 9/00) Design Tools Modular, Reusable Template Libraries Analysis Modules (CBAMs) of Diverse Behavior & Fidelity Prelim/APM Design Tool Xai. Tools Chip. Package Analyzable Product Model PWB DB Materials DB* Thermal Resistance Analysis Tools Xai. Tools General Math Chip. Package Mathematica FEA Ansys 3 D Xai. Tools Thermal Stress EBGA, PBGA, QFP ** = Demonstration module Basic 3 D** Basic Documentation Automation Authoring MS Excel 23

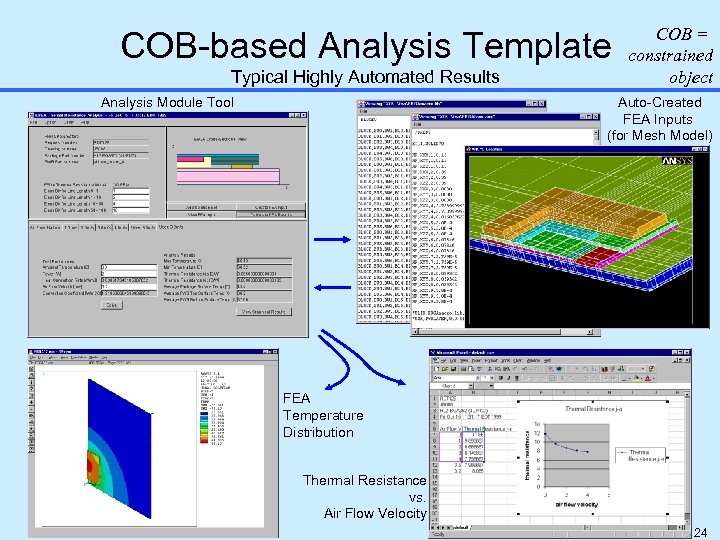

COB-based Analysis Template Typical Highly Automated Results Analysis Module Tool COB = constrained object Auto-Created FEA Inputs (for Mesh Model) FEA Temperature Distribution Thermal Resistance vs. Air Flow Velocity 24

COB-based Analysis Template Typical Highly Automated Results Analysis Module Tool COB = constrained object Auto-Created FEA Inputs (for Mesh Model) FEA Temperature Distribution Thermal Resistance vs. Air Flow Velocity 24

![VTMB = variable topology multi-body technique [Koo, 2000] Pilot & Initial Production Usage Results VTMB = variable topology multi-body technique [Koo, 2000] Pilot & Initial Production Usage Results](https://present5.com/presentation/a9f8240c8326b8529865d1c1192f2adc/image-25.jpg) VTMB = variable topology multi-body technique [Koo, 2000] Pilot & Initial Production Usage Results Product Model-Driven Analysis u u Reduced FEA modeling time > 10: 1 (days/hours minutes) References [1] Shinko 5/00 (in Koo, 2000) Reduced simulation cycle > 75% [2] Shinko evaluation 10/12/00 Enables greater analysis intensity Better designs Leverages XAI / CAD-CAE interoperability techniques – Objects, Internet/web services, ubiquitization methodology, … 25

VTMB = variable topology multi-body technique [Koo, 2000] Pilot & Initial Production Usage Results Product Model-Driven Analysis u u Reduced FEA modeling time > 10: 1 (days/hours minutes) References [1] Shinko 5/00 (in Koo, 2000) Reduced simulation cycle > 75% [2] Shinko evaluation 10/12/00 Enables greater analysis intensity Better designs Leverages XAI / CAD-CAE interoperability techniques – Objects, Internet/web services, ubiquitization methodology, … 25

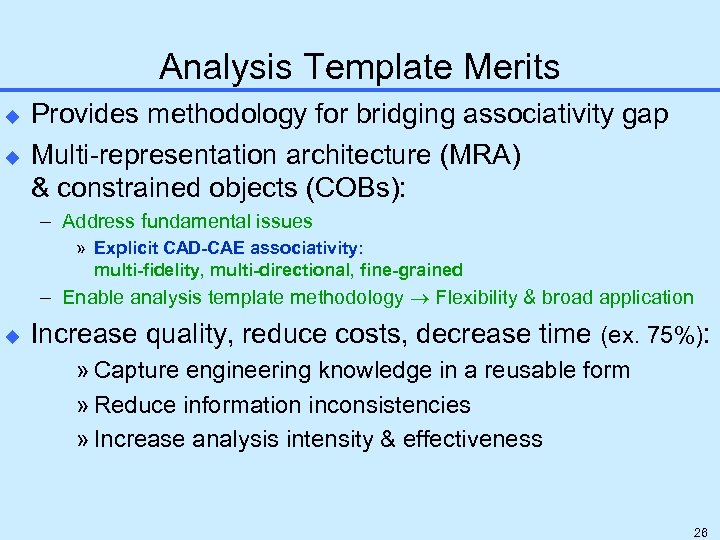

Analysis Template Merits u u Provides methodology for bridging associativity gap Multi-representation architecture (MRA) & constrained objects (COBs): – Address fundamental issues » Explicit CAD-CAE associativity: multi-fidelity, multi-directional, fine-grained – Enable analysis template methodology Flexibility & broad application u Increase quality, reduce costs, decrease time (ex. 75%): » Capture engineering knowledge in a reusable form » Reduce information inconsistencies » Increase analysis intensity & effectiveness 26

Analysis Template Merits u u Provides methodology for bridging associativity gap Multi-representation architecture (MRA) & constrained objects (COBs): – Address fundamental issues » Explicit CAD-CAE associativity: multi-fidelity, multi-directional, fine-grained – Enable analysis template methodology Flexibility & broad application u Increase quality, reduce costs, decrease time (ex. 75%): » Capture engineering knowledge in a reusable form » Reduce information inconsistencies » Increase analysis intensity & effectiveness 26

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 27

Contents u u u Motivation Introduction to Information Modeling and Knowledge Representation Analysis Template Applications International Collaboration on Engineering Frameworks Recommended Solution Approach 27

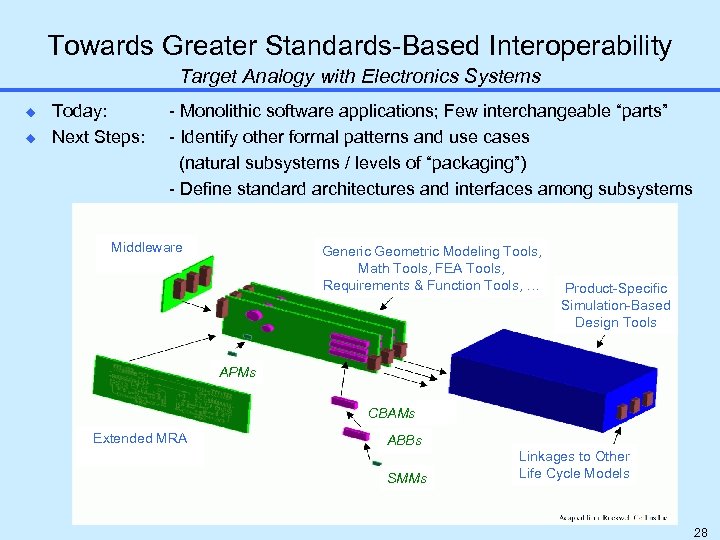

Towards Greater Standards-Based Interoperability Target Analogy with Electronics Systems u u Today: Next Steps: - Monolithic software applications; Few interchangeable “parts” - Identify other formal patterns and use cases (natural subsystems / levels of “packaging”) - Define standard architectures and interfaces among subsystems Middleware Generic Geometric Modeling Tools, Math Tools, FEA Tools, Requirements & Function Tools, … Product-Specific Simulation-Based Design Tools APMs CBAMs Extended MRA ABBs SMMs Linkages to Other Life Cycle Models 28

Towards Greater Standards-Based Interoperability Target Analogy with Electronics Systems u u Today: Next Steps: - Monolithic software applications; Few interchangeable “parts” - Identify other formal patterns and use cases (natural subsystems / levels of “packaging”) - Define standard architectures and interfaces among subsystems Middleware Generic Geometric Modeling Tools, Math Tools, FEA Tools, Requirements & Function Tools, … Product-Specific Simulation-Based Design Tools APMs CBAMs Extended MRA ABBs SMMs Linkages to Other Life Cycle Models 28

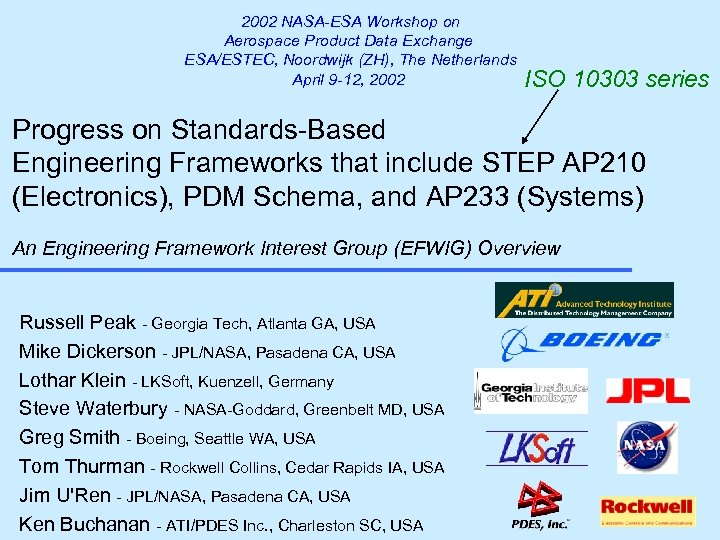

2002 NASA-ESA Workshop on Aerospace Product Data Exchange ESA/ESTEC, Noordwijk (ZH), The Netherlands April 9 -12, 2002 ISO 10303 series Progress on Standards-Based Engineering Frameworks that include STEP AP 210 (Electronics), PDM Schema, and AP 233 (Systems) An Engineering Framework Interest Group (EFWIG) Overview Russell Peak - Georgia Tech, Atlanta GA, USA Mike Dickerson - JPL/NASA, Pasadena CA, USA Lothar Klein - LKSoft, Kuenzell, Germany Steve Waterbury - NASA-Goddard, Greenbelt MD, USA Greg Smith - Boeing, Seattle WA, USA Tom Thurman - Rockwell Collins, Cedar Rapids IA, USA Jim U'Ren - JPL/NASA, Pasadena CA, USA Ken Buchanan - ATI/PDES Inc. , Charleston SC, USA

2002 NASA-ESA Workshop on Aerospace Product Data Exchange ESA/ESTEC, Noordwijk (ZH), The Netherlands April 9 -12, 2002 ISO 10303 series Progress on Standards-Based Engineering Frameworks that include STEP AP 210 (Electronics), PDM Schema, and AP 233 (Systems) An Engineering Framework Interest Group (EFWIG) Overview Russell Peak - Georgia Tech, Atlanta GA, USA Mike Dickerson - JPL/NASA, Pasadena CA, USA Lothar Klein - LKSoft, Kuenzell, Germany Steve Waterbury - NASA-Goddard, Greenbelt MD, USA Greg Smith - Boeing, Seattle WA, USA Tom Thurman - Rockwell Collins, Cedar Rapids IA, USA Jim U'Ren - JPL/NASA, Pasadena CA, USA Ken Buchanan - ATI/PDES Inc. , Charleston SC, USA

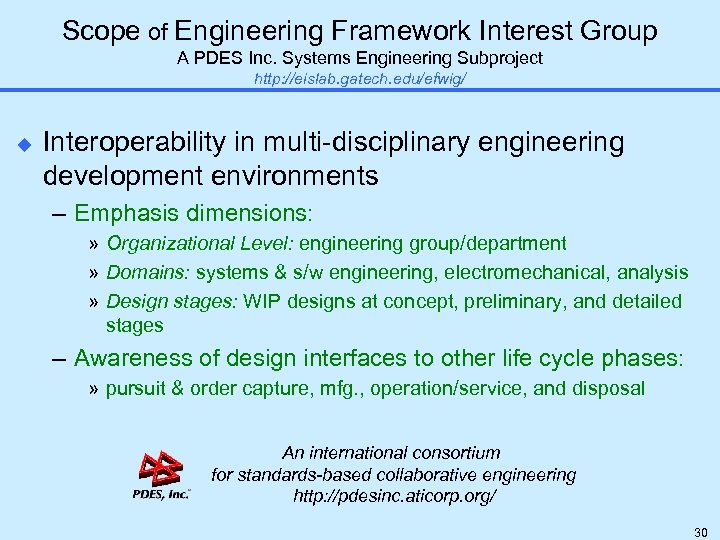

Scope of Engineering Framework Interest Group A PDES Inc. Systems Engineering Subproject http: //eislab. gatech. edu/efwig/ u Interoperability in multi-disciplinary engineering development environments – Emphasis dimensions: » Organizational Level: engineering group/department » Domains: systems & s/w engineering, electromechanical, analysis » Design stages: WIP designs at concept, preliminary, and detailed stages – Awareness of design interfaces to other life cycle phases: » pursuit & order capture, mfg. , operation/service, and disposal An international consortium for standards-based collaborative engineering http: //pdesinc. aticorp. org/ 30

Scope of Engineering Framework Interest Group A PDES Inc. Systems Engineering Subproject http: //eislab. gatech. edu/efwig/ u Interoperability in multi-disciplinary engineering development environments – Emphasis dimensions: » Organizational Level: engineering group/department » Domains: systems & s/w engineering, electromechanical, analysis » Design stages: WIP designs at concept, preliminary, and detailed stages – Awareness of design interfaces to other life cycle phases: » pursuit & order capture, mfg. , operation/service, and disposal An international consortium for standards-based collaborative engineering http: //pdesinc. aticorp. org/ 30

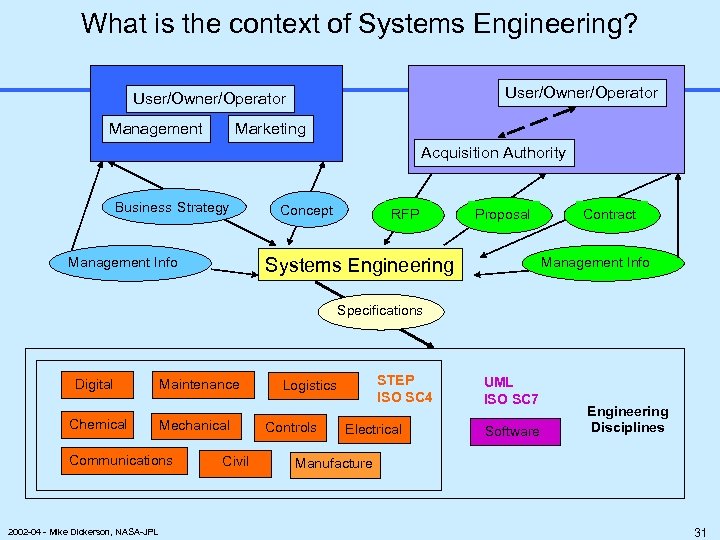

What is the context of Systems Engineering? User/Owner/Operator Management Marketing Acquisition Authority Business Strategy Concept RFP Proposal Systems Engineering Management Info Contract Management Info Specifications Digital Chemical Maintenance Mechanical Communications 2002 -04 - Mike Dickerson, NASA-JPL Civil STEP ISO SC 4 Logistics Controls Electrical UML ISO SC 7 Software Engineering Disciplines Manufacture 31

What is the context of Systems Engineering? User/Owner/Operator Management Marketing Acquisition Authority Business Strategy Concept RFP Proposal Systems Engineering Management Info Contract Management Info Specifications Digital Chemical Maintenance Mechanical Communications 2002 -04 - Mike Dickerson, NASA-JPL Civil STEP ISO SC 4 Logistics Controls Electrical UML ISO SC 7 Software Engineering Disciplines Manufacture 31

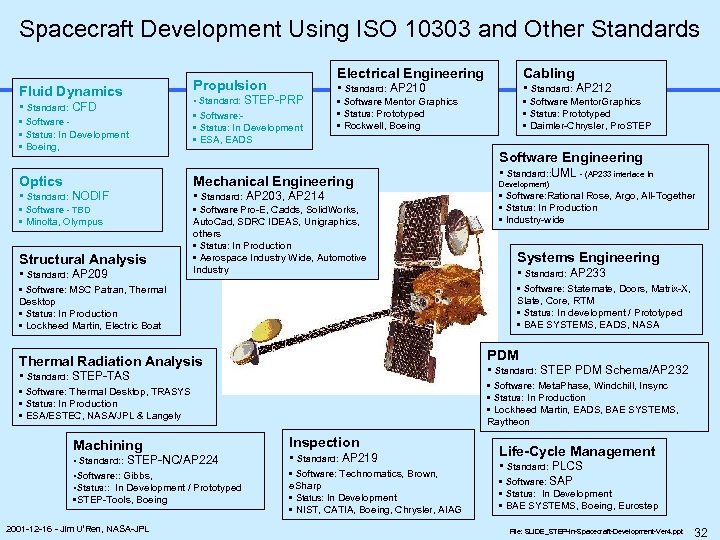

Spacecraft Development Using ISO 10303 and Other Standards Fluid Dynamics • Standard: CFD • Software - • Status: In Development • Boeing, Electrical Engineering Propulsion • Standard: STEP-PRP • Software: - • Status: In Development • ESA, EADS Cabling • Standard: AP 210 • Standard: AP 212 • Software Mentor Graphics • Status: Prototyped • Rockwell, Boeing • Software Mentor. Graphics • Status: Prototyped • Daimler-Chrysler, Pro. STEP Software Engineering Optics Mechanical Engineering • Standard: NODIF • Standard: AP 203, AP 214 • Software - TBD • Minolta, Olympus • Software Pro-E, Cadds, Solid. Works, Auto. Cad, SDRC IDEAS, Unigraphics, others • Status: In Production • Aerospace Industry Wide, Automotive Industry Structural Analysis • Standard: AP 209 • Software: MSC Patran, Thermal 2001 -12 -16 - Jim U’Ren, NASA-JPL • Standard: AP 233 • Software: Statemate, Doors, Matrix-X, • Status: In Production • Lockheed Martin, EADS, BAE SYSTEMS, Raytheon • Status: In Production • ESA/ESTEC, NASA/JPL & Langely • STEP-Tools, Boeing Systems Engineering • Standard: STEP PDM Schema/AP 232 • Software: Meta. Phase, Windchill, Insync • Standard: STEP-TAS • Software: Thermal Desktop, TRASYS • Software: : Gibbs, • Status: : In Development / Prototyped • Software: Rational Rose, Argo, All-Together • Status: In Production • Industry-wide PDM Thermal Radiation Analysis • Standard: : STEP-NC/AP 224 Development) Slate, Core, RTM • Status: In development / Prototyped • BAE SYSTEMS, EADS, NASA Desktop • Status: In Production • Lockheed Martin, Electric Boat Machining • Standard: : UML - (AP 233 interface In Inspection • Standard: AP 219 • Software: Technomatics, Brown, e. Sharp • Status: In Development • NIST, CATIA, Boeing, Chrysler, AIAG Life-Cycle Management • Standard: PLCS • Software: SAP • Status: In Development • BAE SYSTEMS, Boeing, Eurostep File: SLIDE_STEP-in-Spacecraft-Development-Ver 4. ppt 32

Spacecraft Development Using ISO 10303 and Other Standards Fluid Dynamics • Standard: CFD • Software - • Status: In Development • Boeing, Electrical Engineering Propulsion • Standard: STEP-PRP • Software: - • Status: In Development • ESA, EADS Cabling • Standard: AP 210 • Standard: AP 212 • Software Mentor Graphics • Status: Prototyped • Rockwell, Boeing • Software Mentor. Graphics • Status: Prototyped • Daimler-Chrysler, Pro. STEP Software Engineering Optics Mechanical Engineering • Standard: NODIF • Standard: AP 203, AP 214 • Software - TBD • Minolta, Olympus • Software Pro-E, Cadds, Solid. Works, Auto. Cad, SDRC IDEAS, Unigraphics, others • Status: In Production • Aerospace Industry Wide, Automotive Industry Structural Analysis • Standard: AP 209 • Software: MSC Patran, Thermal 2001 -12 -16 - Jim U’Ren, NASA-JPL • Standard: AP 233 • Software: Statemate, Doors, Matrix-X, • Status: In Production • Lockheed Martin, EADS, BAE SYSTEMS, Raytheon • Status: In Production • ESA/ESTEC, NASA/JPL & Langely • STEP-Tools, Boeing Systems Engineering • Standard: STEP PDM Schema/AP 232 • Software: Meta. Phase, Windchill, Insync • Standard: STEP-TAS • Software: Thermal Desktop, TRASYS • Software: : Gibbs, • Status: : In Development / Prototyped • Software: Rational Rose, Argo, All-Together • Status: In Production • Industry-wide PDM Thermal Radiation Analysis • Standard: : STEP-NC/AP 224 Development) Slate, Core, RTM • Status: In development / Prototyped • BAE SYSTEMS, EADS, NASA Desktop • Status: In Production • Lockheed Martin, Electric Boat Machining • Standard: : UML - (AP 233 interface In Inspection • Standard: AP 219 • Software: Technomatics, Brown, e. Sharp • Status: In Development • NIST, CATIA, Boeing, Chrysler, AIAG Life-Cycle Management • Standard: PLCS • Software: SAP • Status: In Development • BAE SYSTEMS, Boeing, Eurostep File: SLIDE_STEP-in-Spacecraft-Development-Ver 4. ppt 32

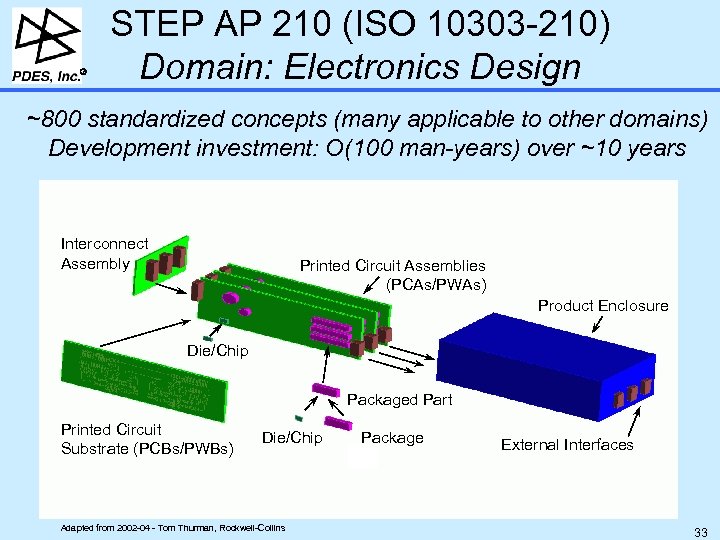

R STEP AP 210 (ISO 10303 -210) Domain: Electronics Design ~800 standardized concepts (many applicable to other domains) Development investment: O(100 man-years) over ~10 years Interconnect Assembly Printed Circuit Assemblies (PCAs/PWAs) Product Enclosure Die/Chip Packaged Part Printed Circuit Substrate (PCBs/PWBs) Die/Chip Adapted from 2002 -04 - Tom Thurman, Rockwell-Collins Package External Interfaces 33

R STEP AP 210 (ISO 10303 -210) Domain: Electronics Design ~800 standardized concepts (many applicable to other domains) Development investment: O(100 man-years) over ~10 years Interconnect Assembly Printed Circuit Assemblies (PCAs/PWAs) Product Enclosure Die/Chip Packaged Part Printed Circuit Substrate (PCBs/PWBs) Die/Chip Adapted from 2002 -04 - Tom Thurman, Rockwell-Collins Package External Interfaces 33

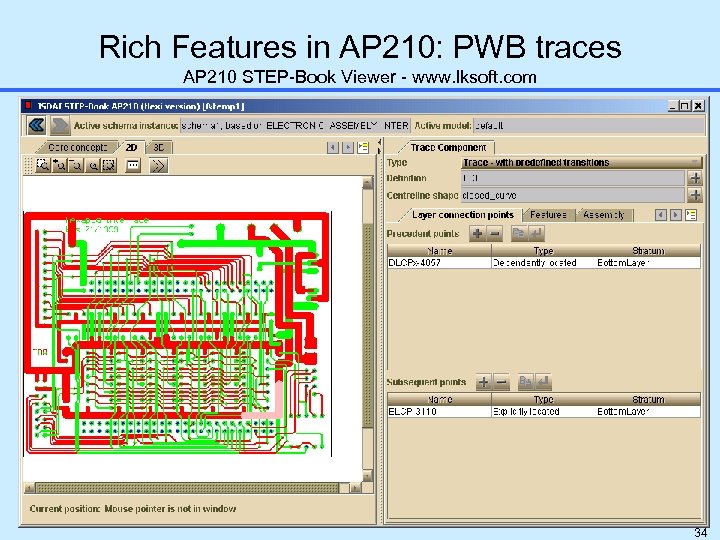

Rich Features in AP 210: PWB traces AP 210 STEP-Book Viewer - www. lksoft. com 34

Rich Features in AP 210: PWB traces AP 210 STEP-Book Viewer - www. lksoft. com 34

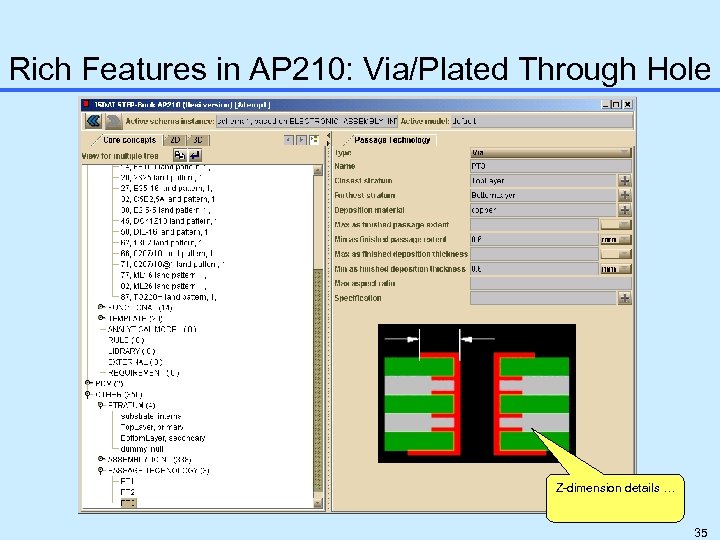

Rich Features in AP 210: Via/Plated Through Hole Z-dimension details … 35

Rich Features in AP 210: Via/Plated Through Hole Z-dimension details … 35

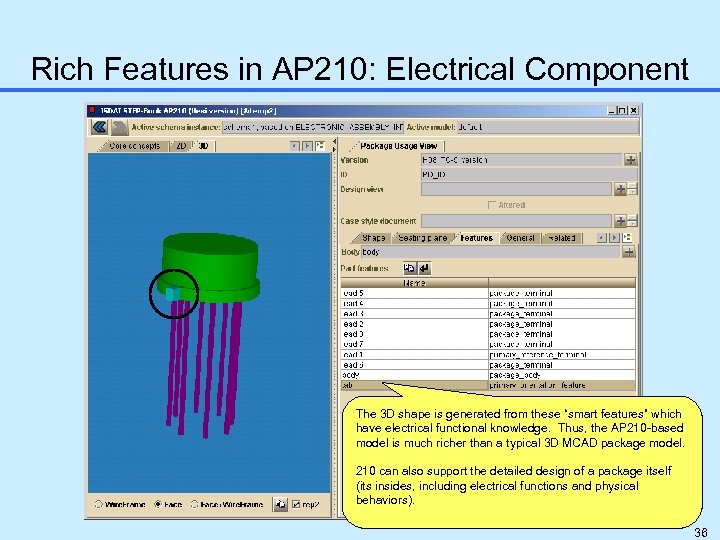

Rich Features in AP 210: Electrical Component The 3 D shape is generated from these “smart features” which have electrical functional knowledge. Thus, the AP 210 -based model is much richer than a typical 3 D MCAD package model. 210 can also support the detailed design of a package itself (its insides, including electrical functions and physical behaviors). 36

Rich Features in AP 210: Electrical Component The 3 D shape is generated from these “smart features” which have electrical functional knowledge. Thus, the AP 210 -based model is much richer than a typical 3 D MCAD package model. 210 can also support the detailed design of a package itself (its insides, including electrical functions and physical behaviors). 36

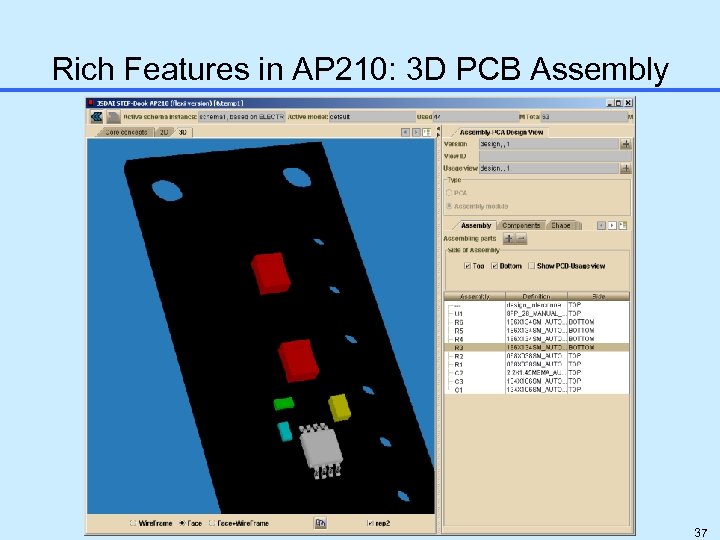

Rich Features in AP 210: 3 D PCB Assembly 37

Rich Features in AP 210: 3 D PCB Assembly 37

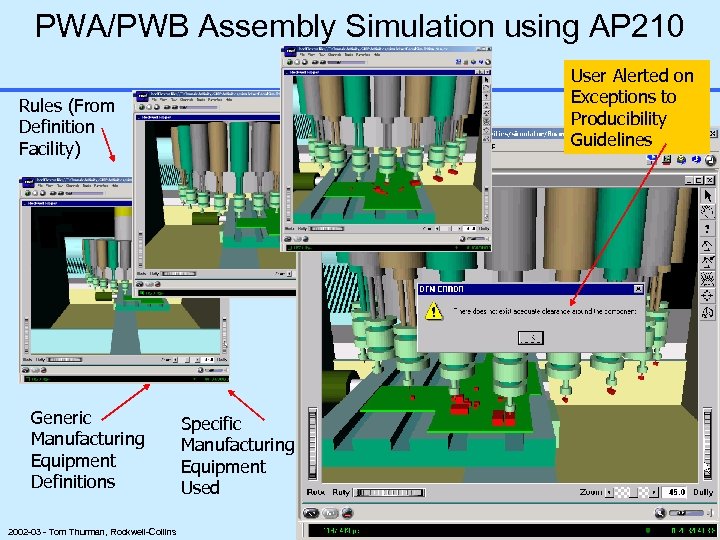

PWA/PWB Assembly Simulation using AP 210 User Alerted on Exceptions to Producibility Guidelines Rules (From Definition Facility) Generic Manufacturing Equipment Definitions 2002 -03 - Tom Thurman, Rockwell-Collins Specific Manufacturing Equipment Used 38

PWA/PWB Assembly Simulation using AP 210 User Alerted on Exceptions to Producibility Guidelines Rules (From Definition Facility) Generic Manufacturing Equipment Definitions 2002 -03 - Tom Thurman, Rockwell-Collins Specific Manufacturing Equipment Used 38

Analogy Physical Integration Modules Model Integration Frameworks Design System Architecture Stacked Fine-Pitch BGA www. shinko. co. jp System-On-a-Package (SOP) Wafer Level Packaging RF, Digital, Analog, Optical, MEMS www. prc. gatech. edu Challenge: Integrating Diverse Technologies 2001 ITRS 39

Analogy Physical Integration Modules Model Integration Frameworks Design System Architecture Stacked Fine-Pitch BGA www. shinko. co. jp System-On-a-Package (SOP) Wafer Level Packaging RF, Digital, Analog, Optical, MEMS www. prc. gatech. edu Challenge: Integrating Diverse Technologies 2001 ITRS 39

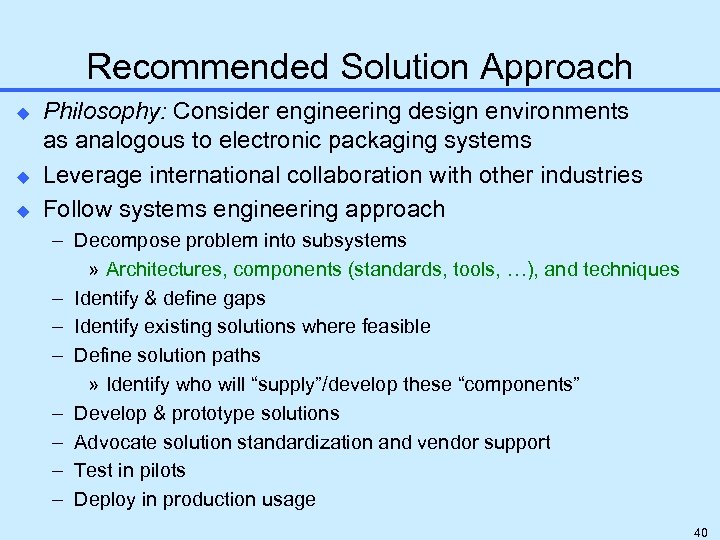

Recommended Solution Approach u u u Philosophy: Consider engineering design environments as analogous to electronic packaging systems Leverage international collaboration with other industries Follow systems engineering approach – Decompose problem into subsystems » Architectures, components (standards, tools, …), and techniques – Identify & define gaps – Identify existing solutions where feasible – Define solution paths » Identify who will “supply”/develop these “components” – Develop & prototype solutions – Advocate solution standardization and vendor support – Test in pilots – Deploy in production usage 40

Recommended Solution Approach u u u Philosophy: Consider engineering design environments as analogous to electronic packaging systems Leverage international collaboration with other industries Follow systems engineering approach – Decompose problem into subsystems » Architectures, components (standards, tools, …), and techniques – Identify & define gaps – Identify existing solutions where feasible – Define solution paths » Identify who will “supply”/develop these “components” – Develop & prototype solutions – Advocate solution standardization and vendor support – Test in pilots – Deploy in production usage 40