2 ФУНКЦИОНАЛЬНАЯ ОРГАНИЗАЦИЯ ЭВМ.ppt

- Количество слайдов: 40

2 ФУНКЦИОНАЛЬНАЯ ОРГАНИЗАЦИЯ ЭВМ 2. 3 Командный цикл процессора 1

2 ФУНКЦИОНАЛЬНАЯ ОРГАНИЗАЦИЯ ЭВМ 2. 3 Командный цикл процессора 1

Процессор v. Центральный процессор (ЦП; англ. central processing unit, CPU, дословно — центральное вычислительное устройство) — исполнитель машинных инструкций, часть аппаратного обеспечения компьютера или программируемого логического контроллера, отвечающий за выполнение операций, заданных программами. v. Современные ЦП, выполняемые в виде отдельных микросхем (чипов), реализующих все особенности, присущие данного рода устройствам, называют микропроцессорами. 2

Процессор v. Центральный процессор (ЦП; англ. central processing unit, CPU, дословно — центральное вычислительное устройство) — исполнитель машинных инструкций, часть аппаратного обеспечения компьютера или программируемого логического контроллера, отвечающий за выполнение операций, заданных программами. v. Современные ЦП, выполняемые в виде отдельных микросхем (чипов), реализующих все особенности, присущие данного рода устройствам, называют микропроцессорами. 2

Командный цикл процессора Командой называется элементарное действие, которое может выполнить процессор без дальнейшей детализации. Последовательность команд, выполнение которых приводит к достижению определённой цели, называется программой. Команды программы кодируются двоичными словами и размещаются в памяти ЭВМ. Вся работа ЭВМ состоит в последовательном выполнении команд программы. Действия по выбору из памяти и выполнению одной команды называется командным циклом. 3

Командный цикл процессора Командой называется элементарное действие, которое может выполнить процессор без дальнейшей детализации. Последовательность команд, выполнение которых приводит к достижению определённой цели, называется программой. Команды программы кодируются двоичными словами и размещаются в памяти ЭВМ. Вся работа ЭВМ состоит в последовательном выполнении команд программы. Действия по выбору из памяти и выполнению одной команды называется командным циклом. 3

Командный цикл процессора В составе любого процессора имеется специальная ячейка, которая хранит адрес выполняемой команды – счетчик команд или программный счетчик. После выполнения очередной команды его значение увеличивается на единицу (если код одной команды занимает несколько ячеек памяти, то содержимое счетчика команд увеличивается на длину команды). Таким образом осуществляется выполнение последовательности команд. Существуют специальные команды (передачи управления), которые в процессе своего выполнения модифицируют содержимое программного счетчика, обеспечивая переходы по программе. Сама выполняемая программа помещается в регистр команд – специальную ячейку процессора. 4

Командный цикл процессора В составе любого процессора имеется специальная ячейка, которая хранит адрес выполняемой команды – счетчик команд или программный счетчик. После выполнения очередной команды его значение увеличивается на единицу (если код одной команды занимает несколько ячеек памяти, то содержимое счетчика команд увеличивается на длину команды). Таким образом осуществляется выполнение последовательности команд. Существуют специальные команды (передачи управления), которые в процессе своего выполнения модифицируют содержимое программного счетчика, обеспечивая переходы по программе. Сама выполняемая программа помещается в регистр команд – специальную ячейку процессора. 4

Командный цикл процессора q. Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом. q. Важнейшие этапы этого процесса приведены ниже. В различных архитектурах и для различных команд могут потребоваться дополнительные этапы. Например, для арифметических команд могут потребоваться дополнительные обращения к памяти, во время которых производится считывание операндов и запись результатов. Отличительной особенностью архитектуры фон Неймана является то, что инструкции и данные хранятся в одной и той же памяти. 5

Командный цикл процессора q. Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом. q. Важнейшие этапы этого процесса приведены ниже. В различных архитектурах и для различных команд могут потребоваться дополнительные этапы. Например, для арифметических команд могут потребоваться дополнительные обращения к памяти, во время которых производится считывание операндов и запись результатов. Отличительной особенностью архитектуры фон Неймана является то, что инструкции и данные хранятся в одной и той же памяти. 5

Командный цикл процессора Этапы цикла выполнения: 1. Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения; 2. Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности; 3. Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её; 4. Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды; 5. Снова выполняется п. 1. Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства). 6

Командный цикл процессора Этапы цикла выполнения: 1. Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения; 2. Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности; 3. Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её; 4. Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды; 5. Снова выполняется п. 1. Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства). 6

Командный цикл процессора Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода — тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки прерывания. 7

Командный цикл процессора Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода — тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки прерывания. 7

Командный цикл процессора Команды центрального процессора являются самым нижним уровнем управления компьютером, поэтому выполнение каждой команды неизбежно и безусловно. Не производится никакой проверки на допустимость выполняемых действий, в частности, не проверяется возможная потеря ценных данных. Чтобы компьютер выполнял только допустимые действия, команды должны быть соответствующим образом организованы в виде необходимой программы. 8

Командный цикл процессора Команды центрального процессора являются самым нижним уровнем управления компьютером, поэтому выполнение каждой команды неизбежно и безусловно. Не производится никакой проверки на допустимость выполняемых действий, в частности, не проверяется возможная потеря ценных данных. Чтобы компьютер выполнял только допустимые действия, команды должны быть соответствующим образом организованы в виде необходимой программы. 8

Командный цикл процессора Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора. Частота тактовых импульсов называется тактовой частотой. 9

Командный цикл процессора Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора. Частота тактовых импульсов называется тактовой частотой. 9

Командный цикл процессора Фактически вся работа процессора заключается в циклическом выполнении пунктов 1 – 5 командного цикла. При запуске машины в счётчик команд аппаратно помещается фиксированное значение – начальный адрес программы (часто 0 или последний адрес памяти; встречаются и более экзотические способы загрузки начального адреса). В дальнейшем содержимое программного счетчика модифицируется в командном цикле. Прекращение выполнения командных циклов может произойти только при выполнении специальной команды «СТОП» . 10

Командный цикл процессора Фактически вся работа процессора заключается в циклическом выполнении пунктов 1 – 5 командного цикла. При запуске машины в счётчик команд аппаратно помещается фиксированное значение – начальный адрес программы (часто 0 или последний адрес памяти; встречаются и более экзотические способы загрузки начального адреса). В дальнейшем содержимое программного счетчика модифицируется в командном цикле. Прекращение выполнения командных циклов может произойти только при выполнении специальной команды «СТОП» . 10

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. 11

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. 11

Конвейерная архитектура Конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии: lполучение и декодирование инструкции (Fetch) lадресация и выборка операнда из ОЗУ (Memory access) lвыполнение арифметических операций (Arithmetic Operation) lсохранение результата операции (Store) 12

Конвейерная архитектура Конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии: lполучение и декодирование инструкции (Fetch) lадресация и выборка операнда из ОЗУ (Memory access) lвыполнение арифметических операций (Arithmetic Operation) lсохранение результата операции (Store) 12

Конвейерная архитектура При отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по прежнему необходимо выполнять выборку, дешифрацию и т. д. ), и для исполнения m команд понадобится n*m единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени. 13

Конвейерная архитектура При отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по прежнему необходимо выполнять выборку, дешифрацию и т. д. ), и для исполнения m команд понадобится n*m единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени. 13

Конвейерная архитектура Факторы, снижающие эффективность конвейера: §простой конвейера, когда некоторые ступени не используются (напр. , адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами); §ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд, out-of-order execution); §очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов). Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода. ) 14

Конвейерная архитектура Факторы, снижающие эффективность конвейера: §простой конвейера, когда некоторые ступени не используются (напр. , адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами); §ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд, out-of-order execution); §очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов). Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода. ) 14

Параллельная архитектура Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных ни требовалось обработать, каждый его байт должен будет пройти через центральный процессор, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана. Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах. Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна): ØSISD — один поток команд, один поток данных; ØSIMD — один поток команд, много потоков данных; ØMISD — много потоков команд, один поток данных; ØMIMD — много потоков команд, много потоков данных. 15

Параллельная архитектура Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных ни требовалось обработать, каждый его байт должен будет пройти через центральный процессор, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана. Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах. Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна): ØSISD — один поток команд, один поток данных; ØSIMD — один поток команд, много потоков данных; ØMISD — много потоков команд, один поток данных; ØMIMD — много потоков команд, много потоков данных. 15

2. 3. 1 Система команд процессора Разнообразие типов данных, форм их представления и действий, которые необходимы для обработки информации и управления ходом вычислений, порождает необходимость использования различных команд – набора команд. Каждый процессор имеет собственный вполне определенный набор команд, называемый системой команд процессора. Система команд должна обладать двумя свойствами – функциональной полнотой и эффективностью. 16

2. 3. 1 Система команд процессора Разнообразие типов данных, форм их представления и действий, которые необходимы для обработки информации и управления ходом вычислений, порождает необходимость использования различных команд – набора команд. Каждый процессор имеет собственный вполне определенный набор команд, называемый системой команд процессора. Система команд должна обладать двумя свойствами – функциональной полнотой и эффективностью. 16

Система команд процессора Функциональная полнота – это достаточность системы команд для описания любого алгоритма. Требование функциональной полноты не является слишком жестким. Доказано, что свойством функциональной полноты обладает система, включающая всего три команды (система Поста): присвоение 0, присвоение 1, проверка на 0. Однако составление программ в такой системе команд крайне не эффективно. 17

Система команд процессора Функциональная полнота – это достаточность системы команд для описания любого алгоритма. Требование функциональной полноты не является слишком жестким. Доказано, что свойством функциональной полноты обладает система, включающая всего три команды (система Поста): присвоение 0, присвоение 1, проверка на 0. Однако составление программ в такой системе команд крайне не эффективно. 17

Система команд процессора Эффективность системы команд – степень соответствия системы команд назначению ЭВМ, т. е. классу алгоритмов, для выполнения которых предназначается ЭВМ, а также требованиям к производительности ЭВМ. Очевидно, что реализация развитой системы команд связана с большими затратами оборудования и, следовательно, с высокой стоимостью процессора. В тоже время ограниченный набор команд приводит к снижению производительности и повышенным требованиям к памяти для размещения программы. Даже простые и дешевые современные микропроцессоры поддерживают систему команд, содержащую несколько сотен команд. 18

Система команд процессора Эффективность системы команд – степень соответствия системы команд назначению ЭВМ, т. е. классу алгоритмов, для выполнения которых предназначается ЭВМ, а также требованиям к производительности ЭВМ. Очевидно, что реализация развитой системы команд связана с большими затратами оборудования и, следовательно, с высокой стоимостью процессора. В тоже время ограниченный набор команд приводит к снижению производительности и повышенным требованиям к памяти для размещения программы. Даже простые и дешевые современные микропроцессоры поддерживают систему команд, содержащую несколько сотен команд. 18

2. 3. 2 Форматы команд Под форматом команды следует понимать длину команды, количество, размер, положение, назначение и способ кодировки ее полей. 19

2. 3. 2 Форматы команд Под форматом команды следует понимать длину команды, количество, размер, положение, назначение и способ кодировки ее полей. 19

Форматы команд Машинная команда представляет собой закодированное по определенным правилам указание микропроцессору на выполнение некоторой операции или действия. Каждая команда содержит элементы, определяющие: Ø что делать? (ответ на этот вопрос дает элемент команды, называемый кодом операции (КОП)); Ø объекты, над которыми нужно что-то делать (эти элементы называются операндами); Ø как делать? (эти элементы называются типами операндов – обычно задаются неявно). 20

Форматы команд Машинная команда представляет собой закодированное по определенным правилам указание микропроцессору на выполнение некоторой операции или действия. Каждая команда содержит элементы, определяющие: Ø что делать? (ответ на этот вопрос дает элемент команды, называемый кодом операции (КОП)); Ø объекты, над которыми нужно что-то делать (эти элементы называются операндами); Ø как делать? (эти элементы называются типами операндов – обычно задаются неявно). 20

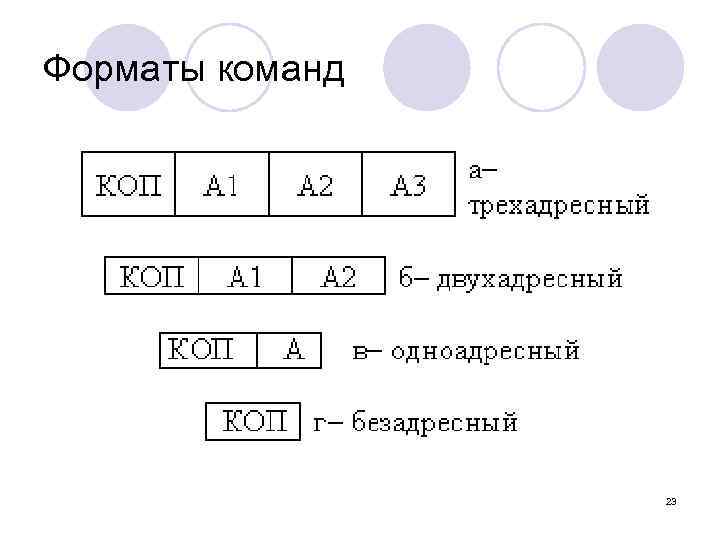

Форматы команд Команды, как и любая информация в ЭВМ, кодируются двоичными словами, которые должны содержать в себе следующие виды информации: q тип операции, которую следует реализовать в данной команде (КОП); q место в памяти, откуда следует взять первый операнд (А 1); q место в памяти, откуда следует взять второй операнд (А 2); q место в памяти, куда следует поместить результат (А 3). 21

Форматы команд Команды, как и любая информация в ЭВМ, кодируются двоичными словами, которые должны содержать в себе следующие виды информации: q тип операции, которую следует реализовать в данной команде (КОП); q место в памяти, откуда следует взять первый операнд (А 1); q место в памяти, откуда следует взять второй операнд (А 2); q место в памяти, куда следует поместить результат (А 3). 21

Форматы команд Каждому из этих видов информации соответствует своя часть двоичного слова – поле, а совокупность полей (их длины, расположение в командном слове, способ кодирования информации) называется форматом команды. В свою очередь, некоторые поля команды могут делиться на подполя. 22

Форматы команд Каждому из этих видов информации соответствует своя часть двоичного слова – поле, а совокупность полей (их длины, расположение в командном слове, способ кодирования информации) называется форматом команды. В свою очередь, некоторые поля команды могут делиться на подполя. 22

Форматы команд 23

Форматы команд 23

Форматы команд Команды трехадресного формата занимают много места в памяти, в то же время далеко не всегда поля адресов используются в командах эффективно. Действительно, наряду с двухместными операциями (сложение, деление, конъюнкция и др. )встречаются и одноместные (инверсия, сдвиг, инкремент и др. ), для которых третий адрес не нужен. 24

Форматы команд Команды трехадресного формата занимают много места в памяти, в то же время далеко не всегда поля адресов используются в командах эффективно. Действительно, наряду с двухместными операциями (сложение, деление, конъюнкция и др. )встречаются и одноместные (инверсия, сдвиг, инкремент и др. ), для которых третий адрес не нужен. 24

Форматы команд При выполнении цепочки вычислений часто результат предыдущей операции используется в качестве операнда для следующей. Более того, нередко встречаются команды, для которых операнды не определены (СТОП) или подразумеваются самим кодом операции (DAA, десятичная коррекция аккумулятора). Поэтому чаще используются двухадресные команды, в этом случае в бинарных операциях результат помещается на место одного из операндов. 25

Форматы команд При выполнении цепочки вычислений часто результат предыдущей операции используется в качестве операнда для следующей. Более того, нередко встречаются команды, для которых операнды не определены (СТОП) или подразумеваются самим кодом операции (DAA, десятичная коррекция аккумулятора). Поэтому чаще используются двухадресные команды, в этом случае в бинарных операциях результат помещается на место одного из операндов. 25

Форматы команд Для реализации одноадресных форматов в процессоре предусматривают специальную ячейку – аккумулятор. Первый операнд и результат всегда размещаются в аккумуляторе, а второй операнд адресуется полем А. 26

Форматы команд Для реализации одноадресных форматов в процессоре предусматривают специальную ячейку – аккумулятор. Первый операнд и результат всегда размещаются в аккумуляторе, а второй операнд адресуется полем А. 26

2. 3. 3 Способы адресации Существует пять основных способов адресации операндов в командах. ØПрямая – в этом случае в адресном поле располагается адрес операнда. Разновидность – прямая регистровая адресация, адресующая не ячейку памяти, а РОН (регистр общего назначения). Поле адреса регистра имеет в команде значительно меньшую длину, чем поле адреса памяти. 27

2. 3. 3 Способы адресации Существует пять основных способов адресации операндов в командах. ØПрямая – в этом случае в адресном поле располагается адрес операнда. Разновидность – прямая регистровая адресация, адресующая не ячейку памяти, а РОН (регистр общего назначения). Поле адреса регистра имеет в команде значительно меньшую длину, чем поле адреса памяти. 27

Способы адресации ØНепосредственная – в поле адреса команды располагается не адрес операнда, а сам операнд. Такой способ удобно использовать в командах с константами. 28

Способы адресации ØНепосредственная – в поле адреса команды располагается не адрес операнда, а сам операнд. Такой способ удобно использовать в командах с константами. 28

Способы адресации Ø Косвенная – в поле адреса команды располагается адрес ячейки памяти, в которой хранится адрес операнда ( «адреса» ). Такой способ позволяет оперировать адресами как данными, что облегчает организацию циклов, обработку массивов данных и др. Его основной недостаток – потеря времени на двойное обращение к памяти – сначала за адресом, потом – за операндом. Разновидность – косвенно-регистровая адресация, при которой в поле команды размещается адрес РОН, хранящего адрес операнда. Этот способ, помимо преимущества обычной косвенной адресации, позволяет обращаться к большой памяти с помощью коротких команд и не требует двойного обращения к памяти (обращение к регистру занимает гораздо меньше времени, чем к памяти). 29

Способы адресации Ø Косвенная – в поле адреса команды располагается адрес ячейки памяти, в которой хранится адрес операнда ( «адреса» ). Такой способ позволяет оперировать адресами как данными, что облегчает организацию циклов, обработку массивов данных и др. Его основной недостаток – потеря времени на двойное обращение к памяти – сначала за адресом, потом – за операндом. Разновидность – косвенно-регистровая адресация, при которой в поле команды размещается адрес РОН, хранящего адрес операнда. Этот способ, помимо преимущества обычной косвенной адресации, позволяет обращаться к большой памяти с помощью коротких команд и не требует двойного обращения к памяти (обращение к регистру занимает гораздо меньше времени, чем к памяти). 29

Способы адресации Ø Относительная – адрес формируется как сумма двух слагаемых: базы, хранящейся в специальном регистре или в одном из РОН, и смещения, извлекаемого из поля адреса команды. Этот способ позволяет сократить длину команды (смещение может быть укороченным, правда в этом случае не вся память доступна в команде) и/или перемещать адресуемые массивы информации по памяти (изменяя базу). Разновидности – индексная и базовоиндексная адресации. Индексная адресация предполагает наличие индексного регистра вместо базового. При каждом обращении содержимое индексного регистра автоматически модифицируется (обычно увеличивается или уменьшается на 1). Базово-индексная адресация формирует адрес операнда как сумму трех слагаемых: базы, индекса и смещения. 30

Способы адресации Ø Относительная – адрес формируется как сумма двух слагаемых: базы, хранящейся в специальном регистре или в одном из РОН, и смещения, извлекаемого из поля адреса команды. Этот способ позволяет сократить длину команды (смещение может быть укороченным, правда в этом случае не вся память доступна в команде) и/или перемещать адресуемые массивы информации по памяти (изменяя базу). Разновидности – индексная и базовоиндексная адресации. Индексная адресация предполагает наличие индексного регистра вместо базового. При каждом обращении содержимое индексного регистра автоматически модифицируется (обычно увеличивается или уменьшается на 1). Базово-индексная адресация формирует адрес операнда как сумму трех слагаемых: базы, индекса и смещения. 30

Способы адресации Ø Безадресная – поле адреса в команде отсутствует, а адрес операнда или не имеет смысла для данной команды, или подразумевается по умолчанию. Часто безадресные команды подразумевают действия над содержимым аккумулятора. Характерно, что безадресные команды нельзя применить к другим регистрам или ячейкам памяти. Одной из разновидностей безадресного обращения является использование т. н. магазинной памяти или стека. 31

Способы адресации Ø Безадресная – поле адреса в команде отсутствует, а адрес операнда или не имеет смысла для данной команды, или подразумевается по умолчанию. Часто безадресные команды подразумевают действия над содержимым аккумулятора. Характерно, что безадресные команды нельзя применить к другим регистрам или ячейкам памяти. Одной из разновидностей безадресного обращения является использование т. н. магазинной памяти или стека. 31

Безадресная адресация Обращение к такой памяти напоминает обращение с магазином стрелкового оружия. Имеется фиксированная ячейка, называемая верхушкой стека. При чтении слово извлекается из верхушки, а все остальное содержимое «поднимается вверх» подобно патронам в магазине, так что в верхушке оказывается следующее по порядку слово. Одно слово нельзя прочитать из стека дважды. При записи новое слово помещается в верхушку стека, а все остальное содержимое «опускается вниз» на одну позицию. Таким образом, слово помещенное в стек первым, будет прочитано последним. Говорят, что стек поддерживает дисциплину LIFO – Last In First Out (последний пришел – первый ушел). Реже используется безадресная память типа очередь с дисциплиной FIFO – First In First Out (первый пришел – первый ушел). 32

Безадресная адресация Обращение к такой памяти напоминает обращение с магазином стрелкового оружия. Имеется фиксированная ячейка, называемая верхушкой стека. При чтении слово извлекается из верхушки, а все остальное содержимое «поднимается вверх» подобно патронам в магазине, так что в верхушке оказывается следующее по порядку слово. Одно слово нельзя прочитать из стека дважды. При записи новое слово помещается в верхушку стека, а все остальное содержимое «опускается вниз» на одну позицию. Таким образом, слово помещенное в стек первым, будет прочитано последним. Говорят, что стек поддерживает дисциплину LIFO – Last In First Out (последний пришел – первый ушел). Реже используется безадресная память типа очередь с дисциплиной FIFO – First In First Out (первый пришел – первый ушел). 32

2. 3. 4 Обработка прерываний По определению прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, называемых работой аппаратуры или программы. Эти действия могут носить сервисный характер, быть запросами со стороны программы пользователя на выполнение обслуживания со стороны операционной системы либо быть реакцией на нештатные ситуации. Механизм прерываний поддерживается на аппаратном уровне и позволяет реализовать как эффективное взаимодействие программ с операционной системой так и эффективное управление программой аппаратной частью компьютера. 33

2. 3. 4 Обработка прерываний По определению прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, называемых работой аппаратуры или программы. Эти действия могут носить сервисный характер, быть запросами со стороны программы пользователя на выполнение обслуживания со стороны операционной системы либо быть реакцией на нештатные ситуации. Механизм прерываний поддерживается на аппаратном уровне и позволяет реализовать как эффективное взаимодействие программ с операционной системой так и эффективное управление программой аппаратной частью компьютера. 33

Обработка прерываний В зависимости от источника, прерывания классифицируются так: Ø аппаратные, возникающие как реакция микропроцессора на физический сигнал от некоторого устройства компьютера (клавиатура, системный таймер, жесткий диск и т. д. ). По времени возникновения эти прерывания асинхронны, то есть происходят в случайные моменты времени; Ø программные, которые вызываются искусственно с помощью соответствующей команды из программы (команда int). Они предназначены для выполнения некоторых действий операционной системы. Эти прерывания являются синхронными; Ø исключения – разновидность программных прерываний, являющихся реакцией микропроцессора на нестандартную ситуацию, возникшую внутри микропроцессора во время выполнения некоторой команды программы. 34

Обработка прерываний В зависимости от источника, прерывания классифицируются так: Ø аппаратные, возникающие как реакция микропроцессора на физический сигнал от некоторого устройства компьютера (клавиатура, системный таймер, жесткий диск и т. д. ). По времени возникновения эти прерывания асинхронны, то есть происходят в случайные моменты времени; Ø программные, которые вызываются искусственно с помощью соответствующей команды из программы (команда int). Они предназначены для выполнения некоторых действий операционной системы. Эти прерывания являются синхронными; Ø исключения – разновидность программных прерываний, являющихся реакцией микропроцессора на нестандартную ситуацию, возникшую внутри микропроцессора во время выполнения некоторой команды программы. 34

3 Организация памяти в ЭВМ, реализованная по классической фоннеймановской архитектуре, включает в себя: o процессор, содержащий арифметико-логическое устройство (АЛУ) и центральное устройство управления (ЦУУ); o память, которая в современных ЭВМ подразделяется на оперативную (ОП или ОЗУ) и сверхоперативную (СОЗУ); o внешние устройства, к которым относят внешнюю память (ВЗУ) и устройства ввода/вывода (УВВ) 35

3 Организация памяти в ЭВМ, реализованная по классической фоннеймановской архитектуре, включает в себя: o процессор, содержащий арифметико-логическое устройство (АЛУ) и центральное устройство управления (ЦУУ); o память, которая в современных ЭВМ подразделяется на оперативную (ОП или ОЗУ) и сверхоперативную (СОЗУ); o внешние устройства, к которым относят внешнюю память (ВЗУ) и устройства ввода/вывода (УВВ) 35

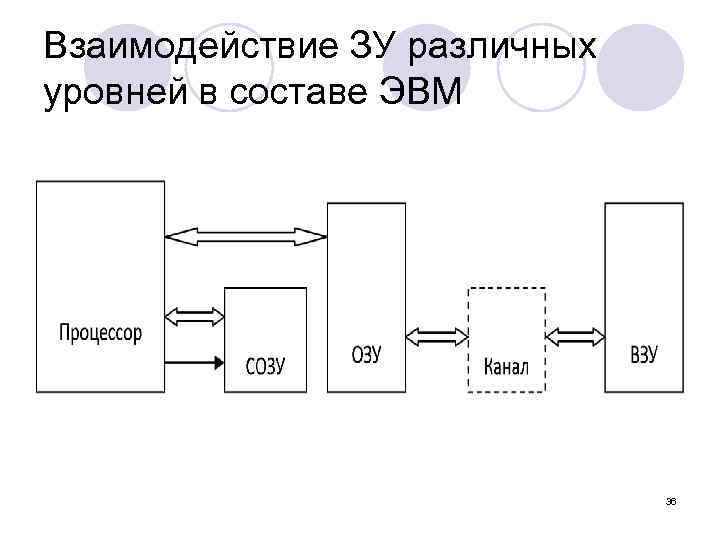

Взаимодействие ЗУ различных уровней в составе ЭВМ 36

Взаимодействие ЗУ различных уровней в составе ЭВМ 36

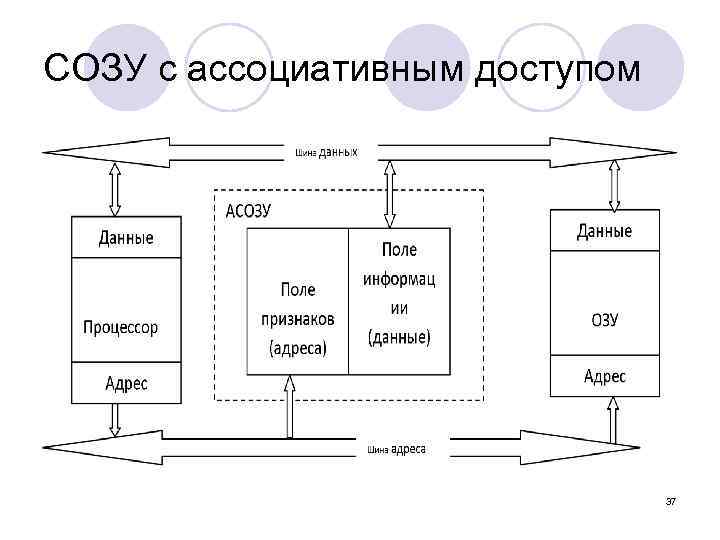

СОЗУ с ассоциативным доступом 37

СОЗУ с ассоциативным доступом 37

Виртуальная память В современных ЭВМ реализовано динамическое распределение памяти между несколькими задачами, существующими в ЭВМ в процессе решения. Данное распределение памяти, называется страничной организацией виртуальной памяти. 38

Виртуальная память В современных ЭВМ реализовано динамическое распределение памяти между несколькими задачами, существующими в ЭВМ в процессе решения. Данное распределение памяти, называется страничной организацией виртуальной памяти. 38

Виртуальная память Суть концепции виртуальной памяти заключается в том, что виртуальные адреса к которым обращается выполняющийся процесс отделяются от адресов реально существующих в первичной памяти (реальные, физические или абсолютные адреса). Диапазон виртуальных адресов к которым может обращаться выполняющийся процесс называется виртуальным адресным пространством этого процесса. Диапазон реальных адресов, существующих в конкретной ЭВМ (2 n, где n– разрядность регистра физического адреса), называется пространством реальных адресов R этой машины. Предполагают, что объем V значительно больше R. 39

Виртуальная память Суть концепции виртуальной памяти заключается в том, что виртуальные адреса к которым обращается выполняющийся процесс отделяются от адресов реально существующих в первичной памяти (реальные, физические или абсолютные адреса). Диапазон виртуальных адресов к которым может обращаться выполняющийся процесс называется виртуальным адресным пространством этого процесса. Диапазон реальных адресов, существующих в конкретной ЭВМ (2 n, где n– разрядность регистра физического адреса), называется пространством реальных адресов R этой машины. Предполагают, что объем V значительно больше R. 39

Виртуальная память Перевод виртуальных адресов в реальные во время выполнения процесса, называется динамическим преобразованием адресов (DAT). Это преобразование адресов выполняет сама система, причем это делается прозрачно (невидимо) для пользователя. Существует два наиболее распространенных способа реализации виртуальной памяти – это страничная и сегментная организация. Блоки фиксированного размера, называются страницами, блоки переменного размера называются сегментами. В современной ВС оба вида блоков комбинируются, причем как правило применяются сегменты длина которых выражается целым числом страниц (странично-сегментная организация памяти). 40

Виртуальная память Перевод виртуальных адресов в реальные во время выполнения процесса, называется динамическим преобразованием адресов (DAT). Это преобразование адресов выполняет сама система, причем это делается прозрачно (невидимо) для пользователя. Существует два наиболее распространенных способа реализации виртуальной памяти – это страничная и сегментная организация. Блоки фиксированного размера, называются страницами, блоки переменного размера называются сегментами. В современной ВС оба вида блоков комбинируются, причем как правило применяются сегменты длина которых выражается целым числом страниц (странично-сегментная организация памяти). 40