b07bf511b7726906ecbece24be3352a3.ppt

- Количество слайдов: 54

2. CMOS Op-amp설계 (1)

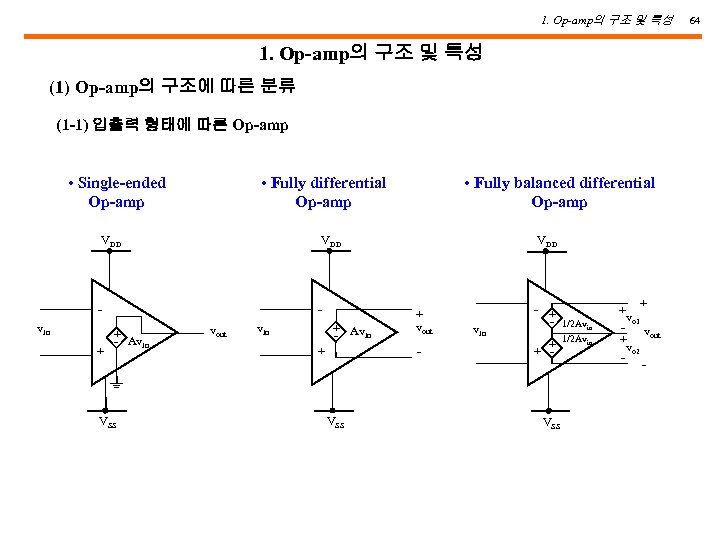

1. Op-amp의 구조 및 특성 (1) Op-amp의 구조에 따른 분류 (1 -1) 입출력 형태에 따른 Op-amp • Single-ended Op-amp • Fully differential Op-amp VDD - vin + + - Avin VSS • Fully balanced differential Op-amp vout + Av in - vin + VDD + vout - VSS vin - + - 1/2 Avin + + - VSS 1/2 Avin + + vo 1 vout + vo 2 - 64

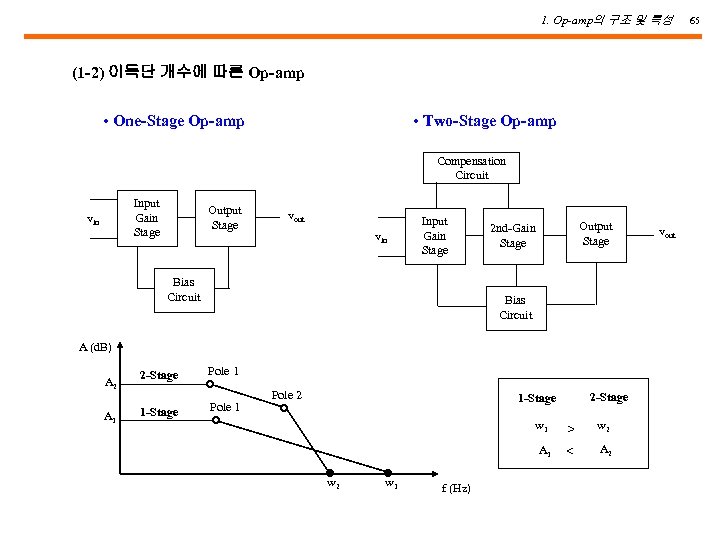

1. Op-amp의 구조 및 특성 (1 -2) 이득단 개수에 따른 Op-amp • One-Stage Op-amp • Two-Stage Op-amp Compensation Circuit Input Gain Stage vin Output Stage vout vin Input Gain Stage Bias Circuit Output Stage 2 nd-Gain Stage Bias Circuit A (d. B) A 2 A 1 2 -Stage Pole 1 1 -Stage Pole 1 Pole 2 2 -Stage 1 -Stage w 1 f (Hz) w 2 A 1 w 2 > < A 2 vout 65

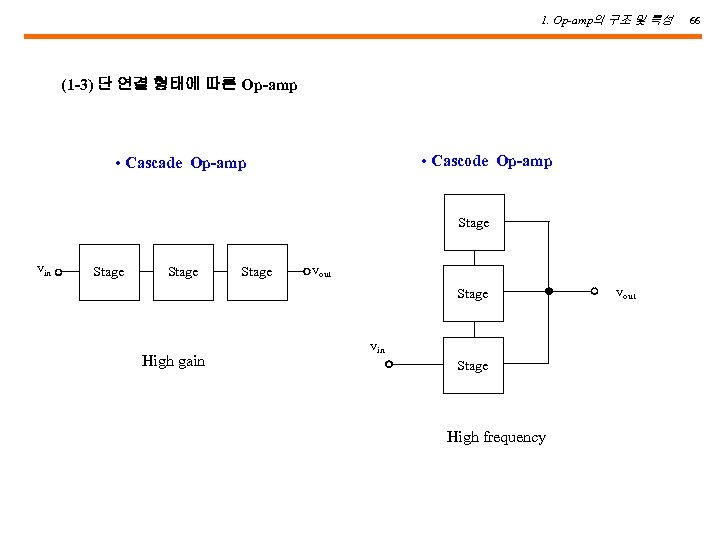

1. Op-amp의 구조 및 특성 (1 -3) 단 연결 형태에 따른 Op-amp • Cascode Op-amp • Cascade Op-amp Stage vin Stage vout Stage High gain vin Stage High frequency vout 66

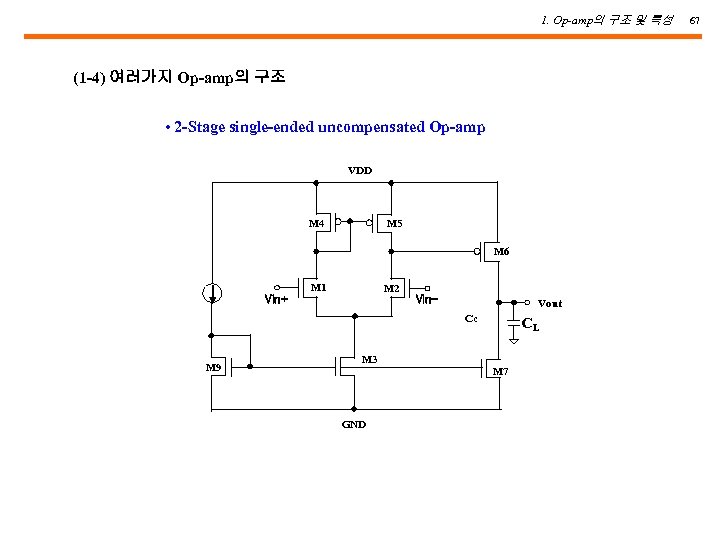

1. Op-amp의 구조 및 특성 (1 -4) 여러가지 Op-amp의 구조 • 2 -Stage single-ended uncompensated Op-amp VDD M 4 M 5 M 6 M 1 M 2 Vin+ Vin- Vout Cc M 9 CL M 3 M 7 GND 67

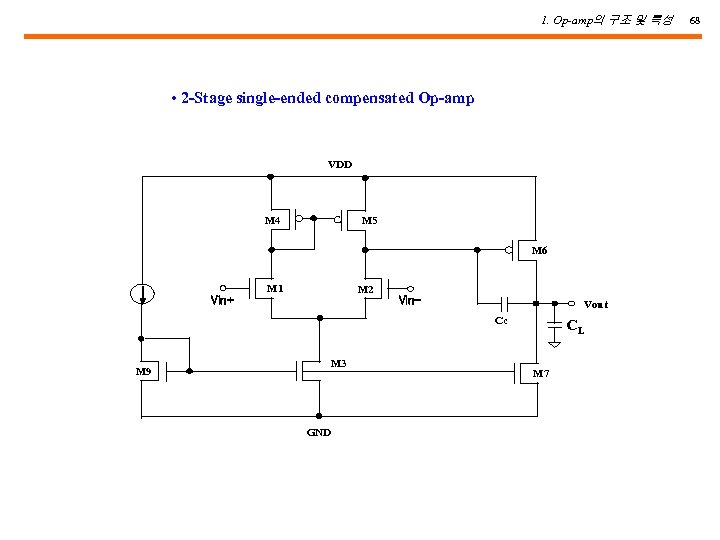

1. Op-amp의 구조 및 특성 • 2 -Stage single-ended compensated Op-amp VDD M 4 M 5 M 6 M 1 M 2 Vin+ Vin- Vout Cc M 9 M 3 GND CL M 7 68

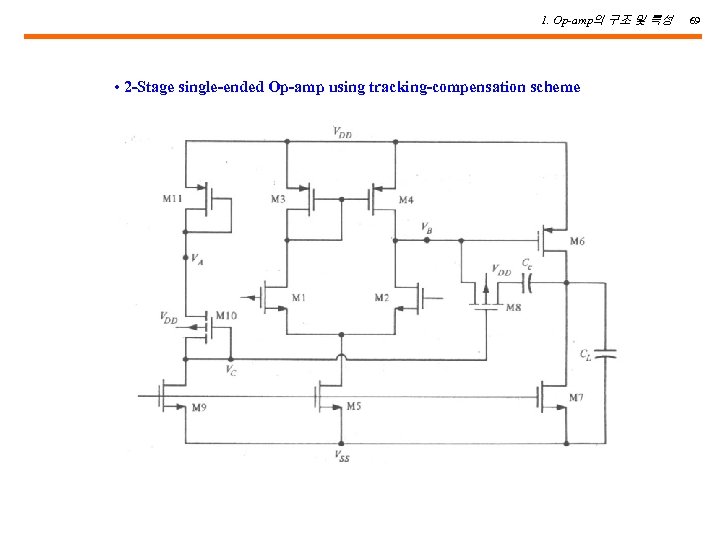

1. Op-amp의 구조 및 특성 • 2 -Stage single-ended Op-amp using tracking-compensation scheme 69

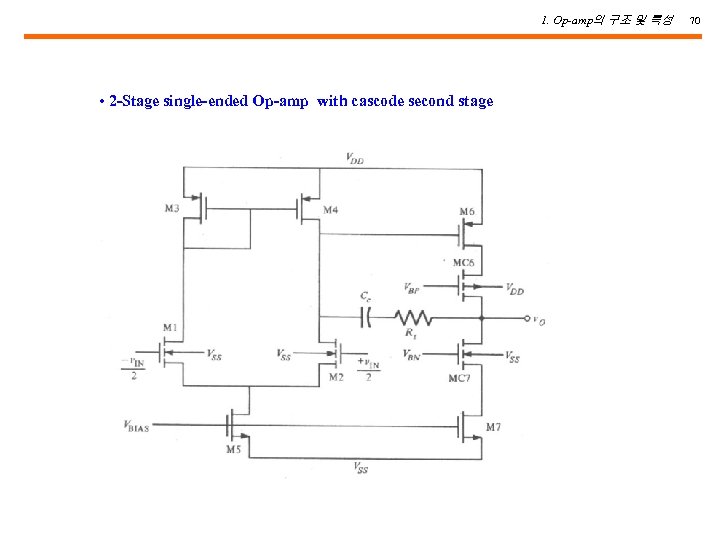

1. Op-amp의 구조 및 특성 • 2 -Stage single-ended Op-amp with cascode second stage 70

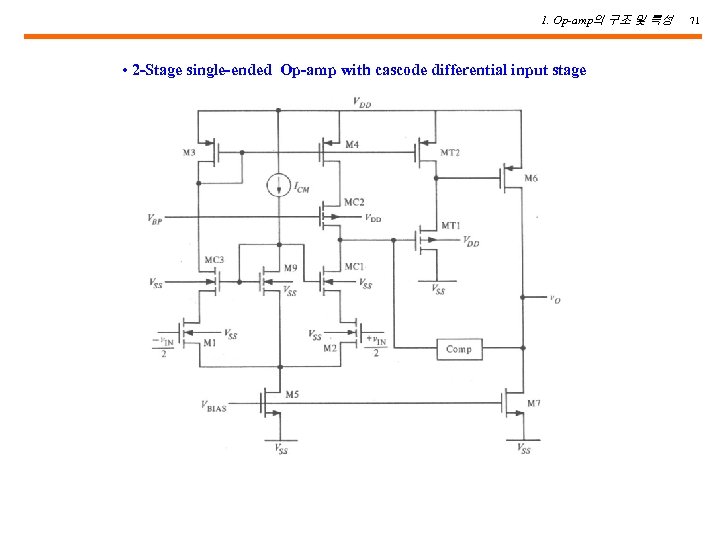

1. Op-amp의 구조 및 특성 • 2 -Stage single-ended Op-amp with cascode differential input stage 71

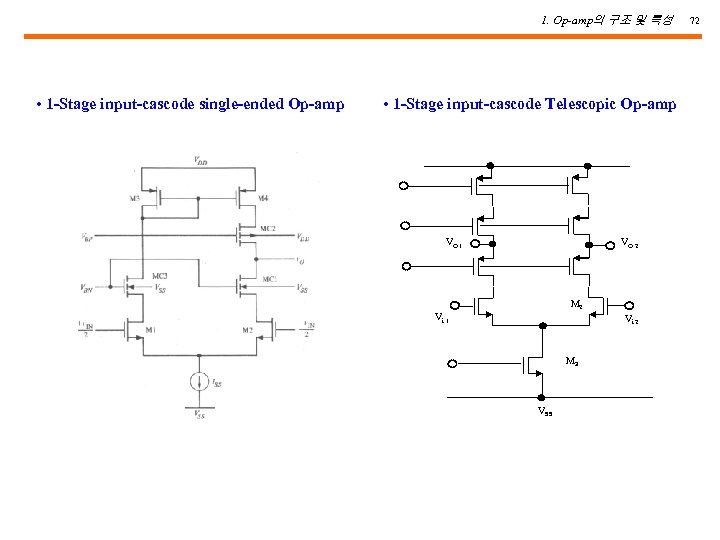

1. Op-amp의 구조 및 특성 • 1 -Stage input-cascode single-ended Op-amp • 1 -Stage input-cascode Telescopic Op-amp VO 1 VO 2 M 2 Vi 1 Vi 2 M 3 VSS 72

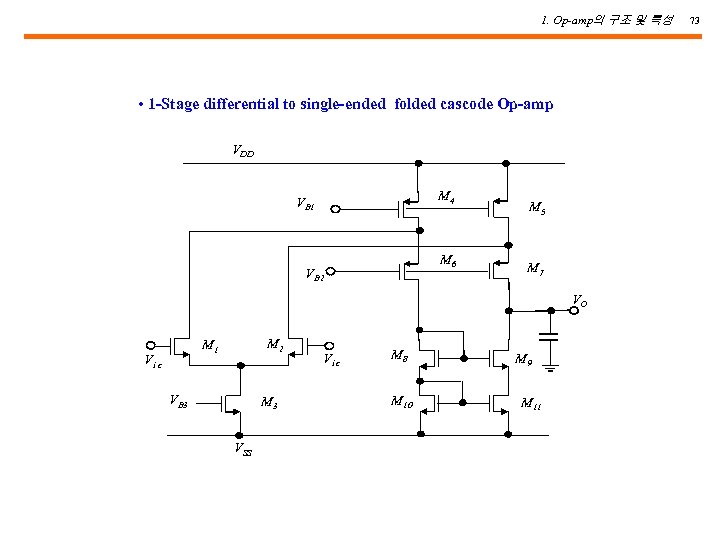

1. Op-amp의 구조 및 특성 • 1 -Stage differential to single-ended folded cascode Op-amp VDD M 4 VB 1 M 6 VB 2 M 5 M 7 VO M 2 M 1 Vi c VB 3 M 3 VSS Vi c M 8 M 10 M 9 M 11 73

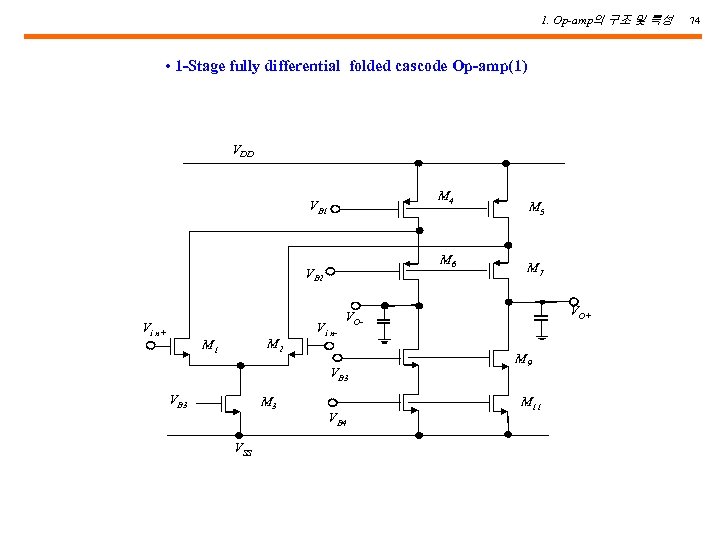

1. Op-amp의 구조 및 특성 • 1 -Stage fully differential folded cascode Op-amp(1) VDD M 4 VB 1 M 6 VB 2 Vi n+ M 2 M 1 Vi n- M 3 VSS M 7 VO+ VO- VB 3 M 5 VB 4 M 9 M 11 74

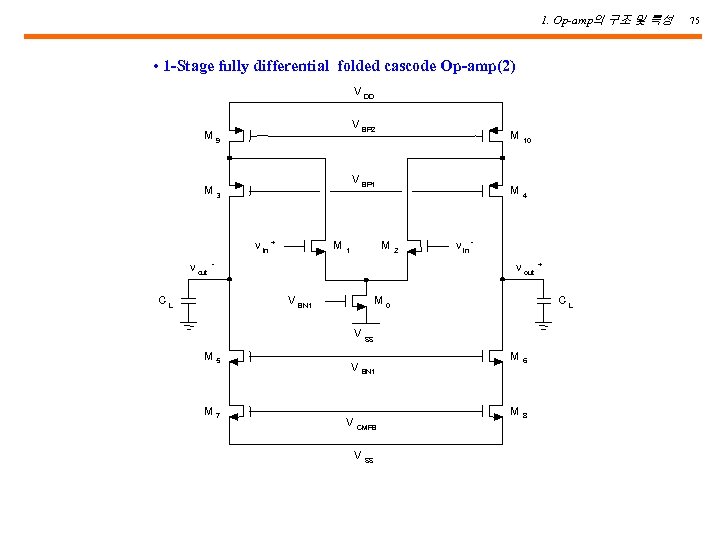

1. Op-amp의 구조 및 특성 • 1 -Stage fully differential folded cascode Op-amp(2) V DD M M V BP 2 3 M M 1 - 2 10 M V BP 1 v in + v out M 9 4 v in v out CL V BN 1 M CL 0 V SS M 5 M 7 V BN 1 V CMFB V SS + M 6 M 8 75

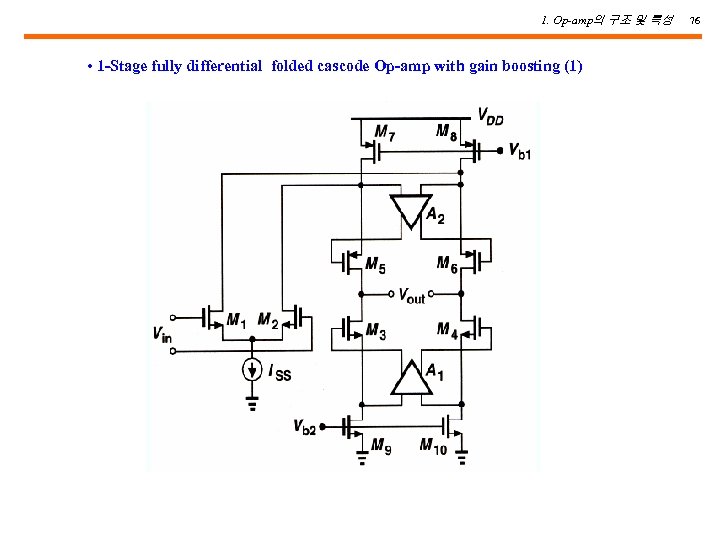

1. Op-amp의 구조 및 특성 • 1 -Stage fully differential folded cascode Op-amp with gain boosting (1) 76

1. Op-amp의 구조 및 특성 • 1 -Stage fully differential folded cascode Op-amp with gain boosting (2) 77

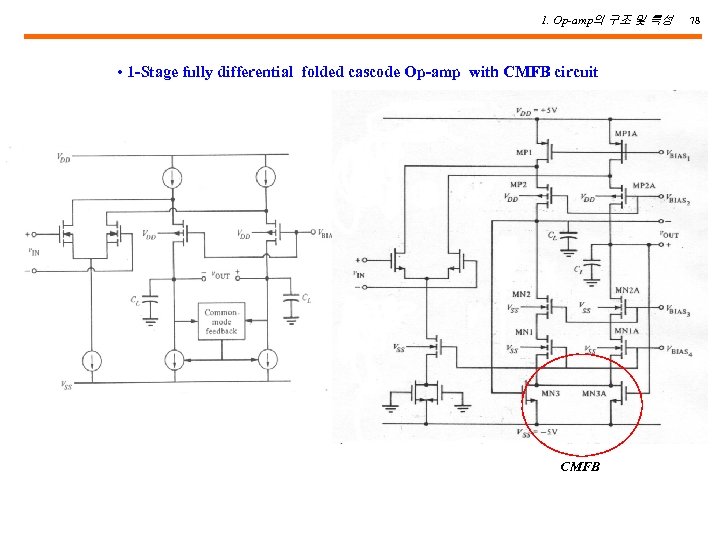

1. Op-amp의 구조 및 특성 • 1 -Stage fully differential folded cascode Op-amp with CMFB circuit CMFB 78

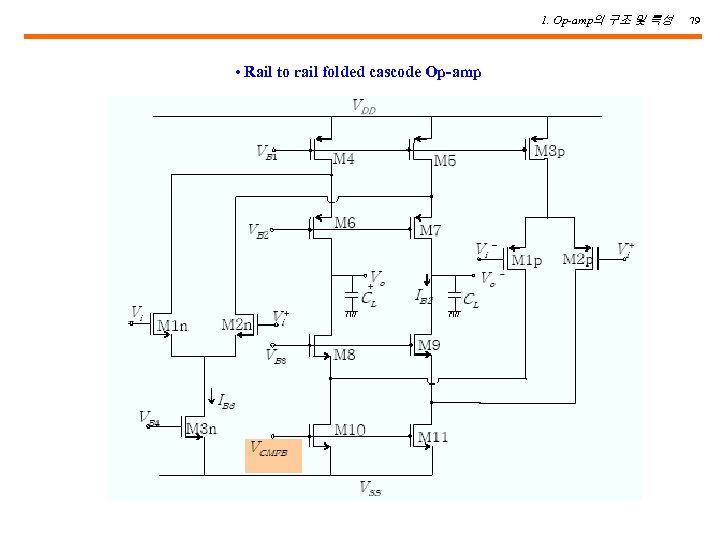

1. Op-amp의 구조 및 특성 • Rail to rail folded cascode Op-amp 79

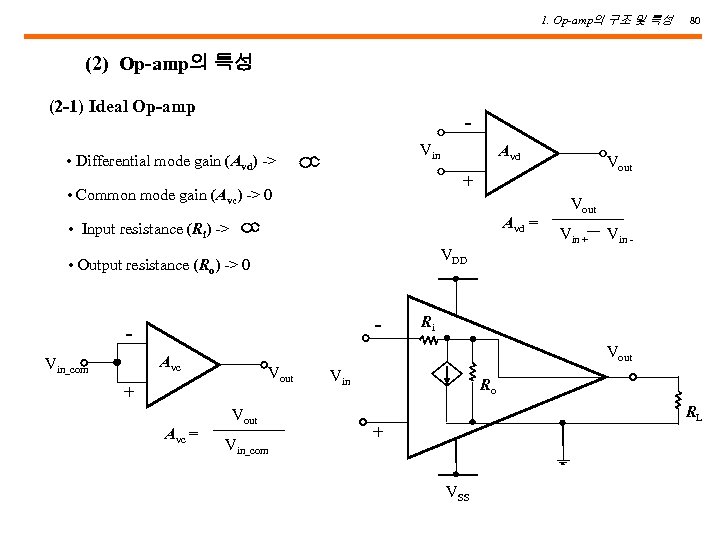

1. Op-amp의 구조 및 특성 80 (2) Op-amp의 특성 (2 -1) Ideal Op-amp Vin • Differential mode gain (Avd) -> Avd + • Common mode gain (Avc) -> 0 Avd = • Input resistance (Ri) -> - - Vin + Vin - Ri Vout Avc Vout + Avc = Vout VDD • Output resistance (Ro) -> 0 Vin_com Vout Vin_com Vin Ro RL + VSS

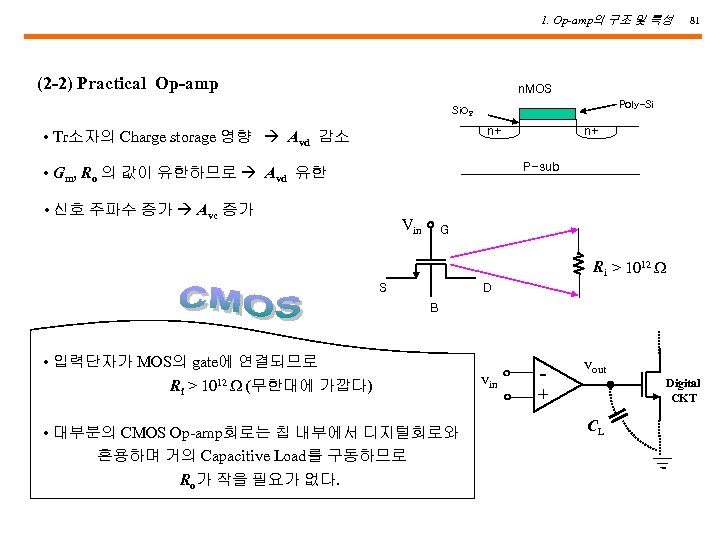

1. Op-amp의 구조 및 특성 (2 -2) Practical Op-amp 81 n. MOS Poly-Si Si. O 2 n+ n+ • Tr소자의 Charge storage 영향 Avd 감소 P-sub • Gm, Ro 의 값이 유한하므로 Avd 유한 • 신호 주파수 증가 Avc 증가 Vin G Ri > 1012 W S D B • 입력단자가 MOS의 gate에 연결되므로 Ri > 1012 W (무한대에 가깝다) • 대부분의 CMOS Op-amp회로는 칩 내부에서 디지털회로와 혼용하며 거의 Capacitive Load를 구동하므로 Ro가 작을 필요가 없다. vin + vout Digital CKT CL

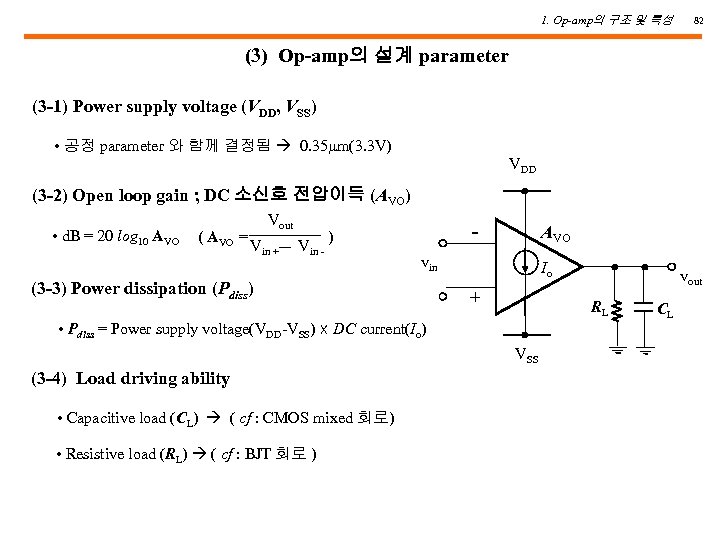

1. Op-amp의 구조 및 특성 82 (3) Op-amp의 설계 parameter (3 -1) Power supply voltage (VDD, VSS) • 공정 parameter 와 함께 결정됨 0. 35 mm(3. 3 V) VDD (3 -2) Open loop gain ; DC 소신호 전압이득 (AVO) • d. B = 20 log 10 AVO ( AVO = Vout Vin + Vin - - ) AVO vin (3 -3) Power dissipation (Pdiss) Io + RL • Pdiss = Power supply voltage(VDD-VSS) x DC current(Io) VSS (3 -4) Load driving ability • Capacitive load (CL) ( cf : CMOS mixed 회로) • Resistive load (RL) ( cf : BJT 회로 ) vout CL

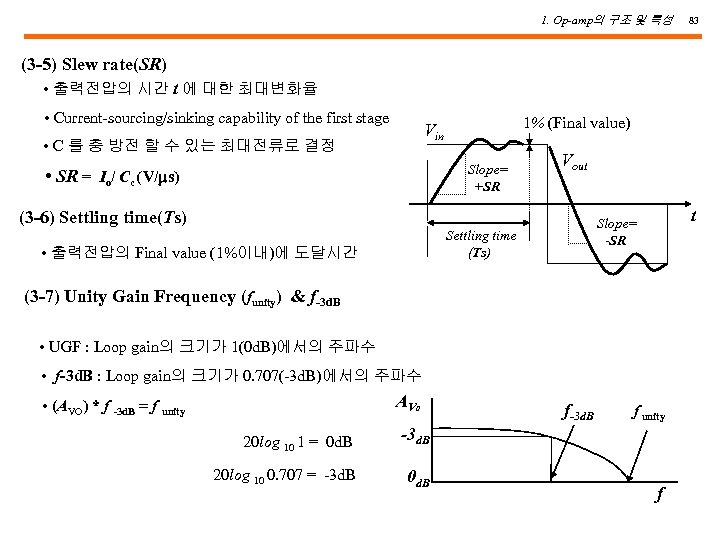

1. Op-amp의 구조 및 특성 83 (3 -5) Slew rate(SR) • 출력전압의 시간 t 에 대한 최대변화율 • Current-sourcing/sinking capability of the first stage 1% (Final value) Vin • C 를 충 방전 할 수 있는 최대전류로 결정 Slope= +SR • SR = Io/ Cc (V/ms) Vout (3 -6) Settling time(Ts) Settling time (Ts) • 출력전압의 Final value (1%이내)에 도달시간 t Slope= -SR (3 -7) Unity Gain Frequency (funity) & f-3 d. B • UGF : Loop gain의 크기가 1(0 d. B)에서의 주파수 • f-3 d. B : Loop gain의 크기가 0. 707(-3 d. B)에서의 주파수 AVo • (AVO) * f -3 d. B = f unity 20 log 10 1 = 0 d. B f unity -3 d. B 20 log 10 0. 707 = -3 d. B f

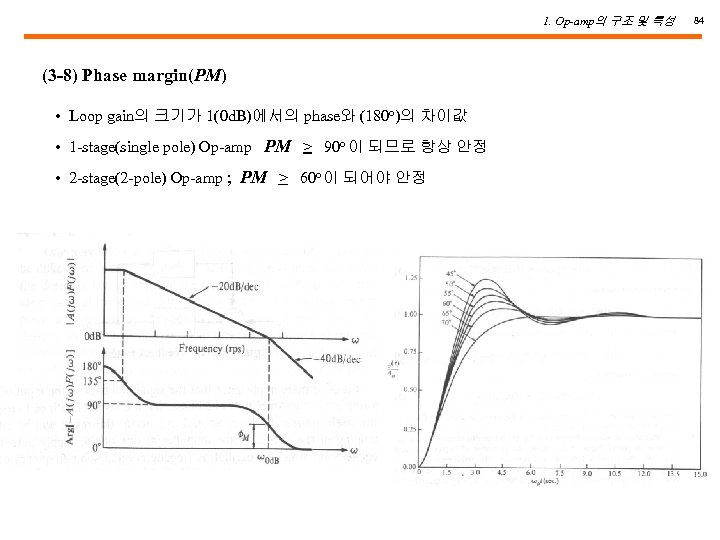

1. Op-amp의 구조 및 특성 (3 -8) Phase margin(PM) • Loop gain의 크기가 1(0 d. B)에서의 phase와 (180 o)의 차이값 • 1 -stage(single pole) Op-amp PM > 90 o 이 되므로 항상 안정 • 2 -stage(2 -pole) Op-amp ; PM > 60 o 이 되어야 안정 84

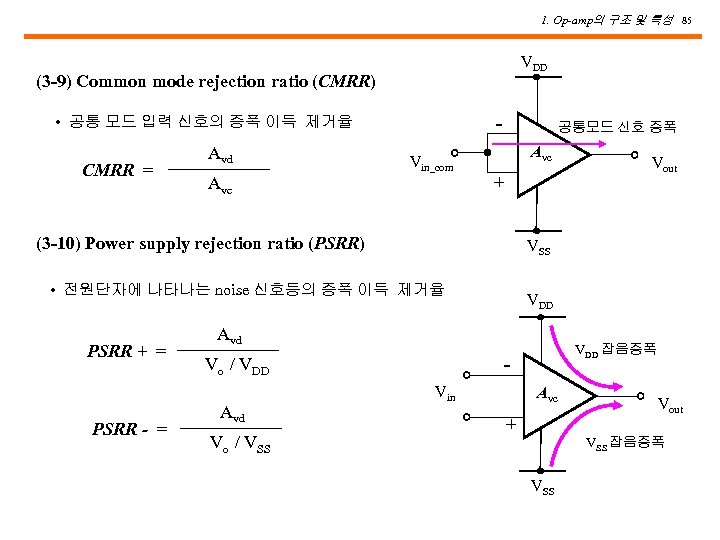

1. Op-amp의 구조 및 특성 85 VDD (3 -9) Common mode rejection ratio (CMRR) • 공통 모드 입력 신호의 증폭 이득 제거율 CMRR = Avd Vin_com Avc 공통모드 신호 증폭 Avc + (3 -10) Power supply rejection ratio (PSRR) VSS • 전원단자에 나타나는 noise 신호등의 증폭 이득 제거율 PSRR + = PSRR - = VDD Avd Vo / VSS Vout VDD 잡음증폭 Vin Avc + Vout VSS 잡음증폭 VSS

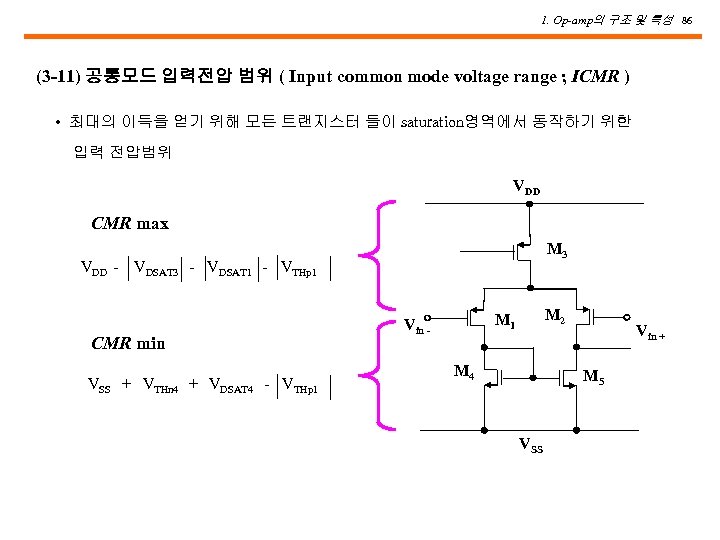

1. Op-amp의 구조 및 특성 86 (3 -11) 공통모드 입력전압 범위 ( Input common mode voltage range ; ICMR ) • 최대의 이득을 얻기 위해 모든 트랜지스터 들이 saturation영역에서 동작하기 위한 입력 전압범위 VDD CMR max VDD - M 3 VDSAT 3 - VDSAT 1 - VTHp 1 CMR min VSS + VTHn 4 + VDSAT 4 - VTHp 1 M 2 M 1 Vin M 4 Vin + M 5 VSS

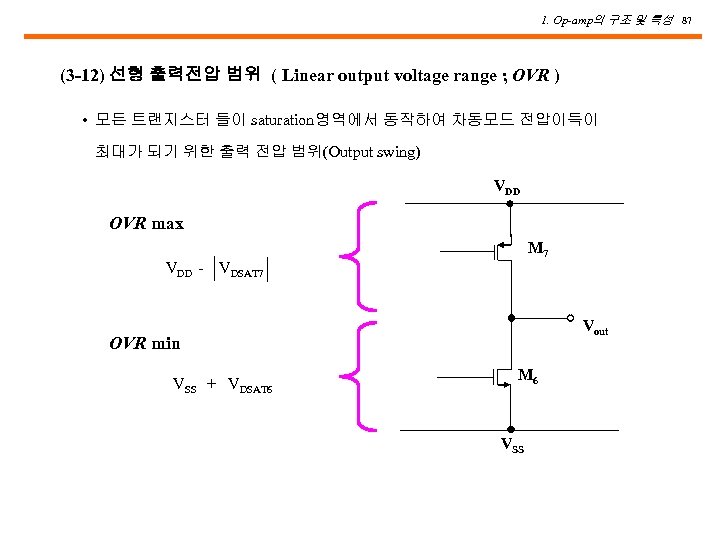

1. Op-amp의 구조 및 특성 87 (3 -12) 선형 출력전압 범위 ( Linear output voltage range ; OVR ) • 모든 트랜지스터 들이 saturation영역에서 동작하여 차동모드 전압이득이 최대가 되기 위한 출력 전압 범위(Output swing) VDD OVR max VDD - M 7 VDSAT 7 Vout OVR min VSS + VDSAT 6 M 6 VSS

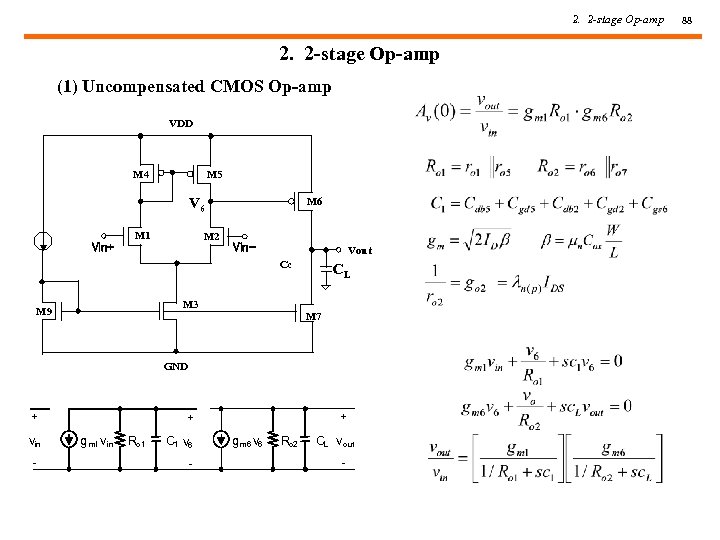

2. 2 -stage Op-amp (1) Uncompensated CMOS Op-amp VDD M 4 M 5 V 6 M 1 M 2 Vin+ M 6 Vin- Vout Cc M 3 M 9 CL M 7 GND + vin - + + g m. I v in Ro 1 C 1 v 6 - g m 6 v 6 Ro 2 CL v out - 88

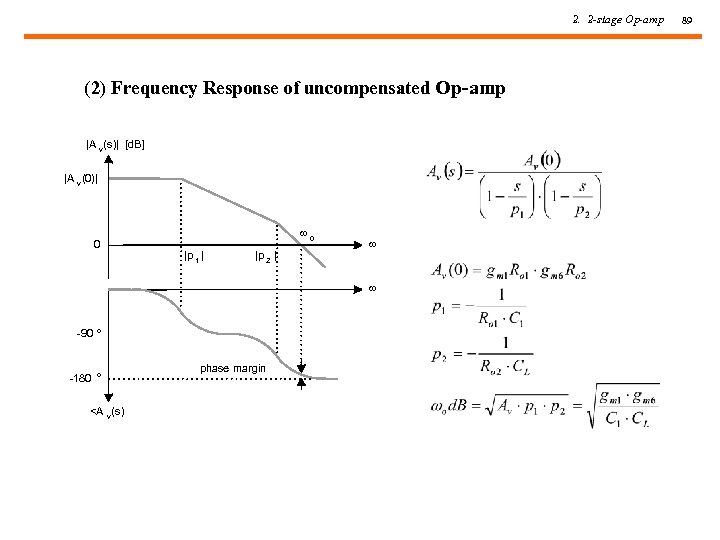

2. 2 -stage Op-amp (2) Frequency Response of uncompensated Op-amp |A v (s)| [d. B] |A v (0)| 0 0 |p 1 | |p 2 | -90 o -180 o <A v (s) phase margin 89

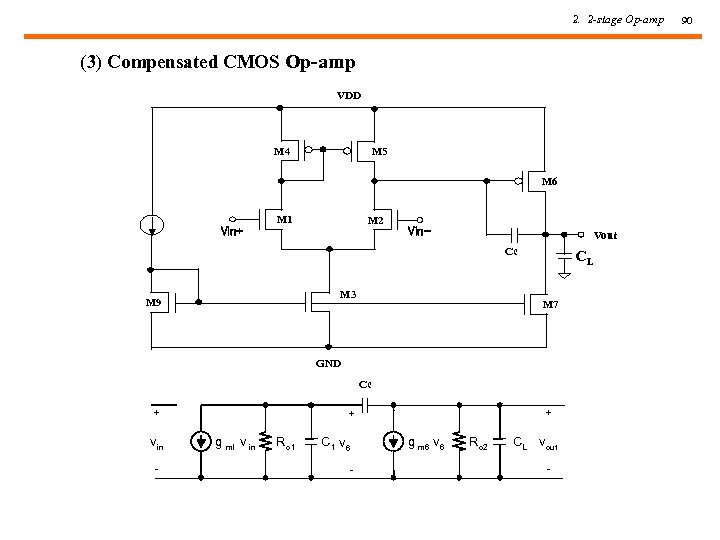

2. 2 -stage Op-amp (3) Compensated CMOS Op-amp VDD M 4 M 5 M 6 M 1 M 2 Vin+ Vin- Vout Cc M 3 M 9 CL M 7 GND Cc + v in - + + g m. I v in R o 1 C 1 v 6 - g m 6 v 6 R o 2 C L vout - 90

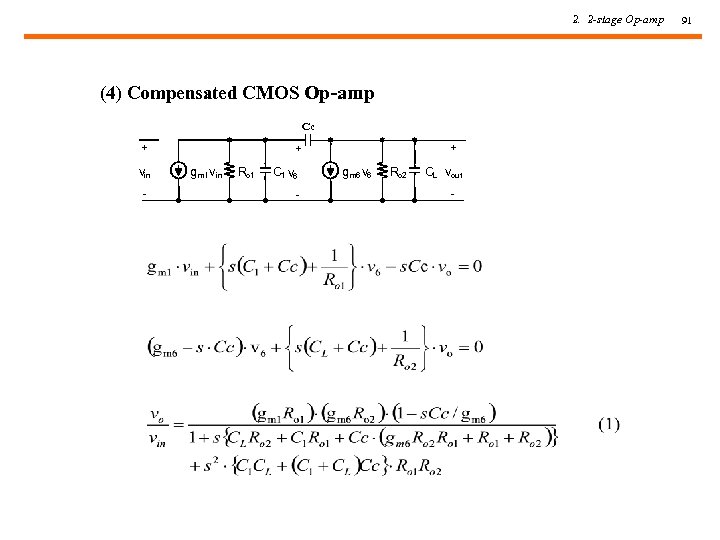

2. 2 -stage Op-amp (4) Compensated CMOS Op-amp Cc + vin - + + g m. I v in Ro 1 C 1 v 6 - g m 6 v 6 Ro 2 CL vout - 91

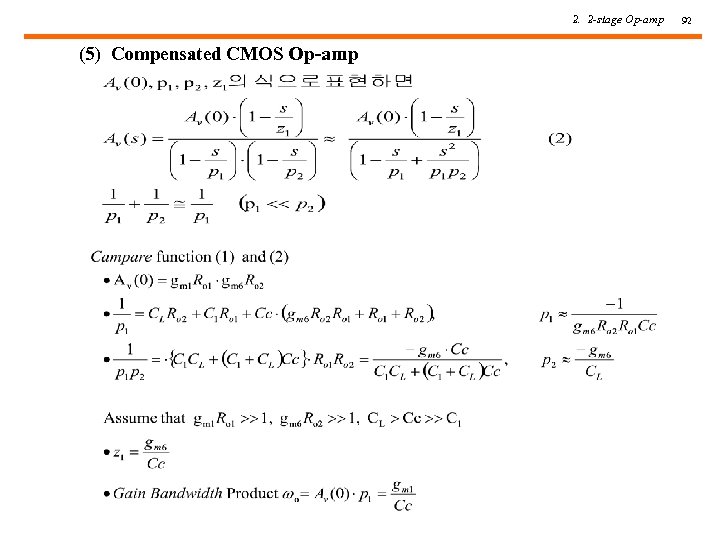

2. 2 -stage Op-amp (5) Compensated CMOS Op-amp 92

![2. 2 -stage Op-amp (6) Frequency Response of CMOS Op-amp |Av(s)| [d. B] |Av(0)| 2. 2 -stage Op-amp (6) Frequency Response of CMOS Op-amp |Av(s)| [d. B] |Av(0)|](https://present5.com/presentation/b07bf511b7726906ecbece24be3352a3/image-31.jpg)

2. 2 -stage Op-amp (6) Frequency Response of CMOS Op-amp |Av(s)| [d. B] |Av(0)| 0 |A v(0)| 0 |p 1 | |p 2 | 0 |p 1 | -180 o -90 o phase margin -180 o -270 o <Av(s) <A v(s) Av(0) p 1 -90 o z' p 2 o z 1 93

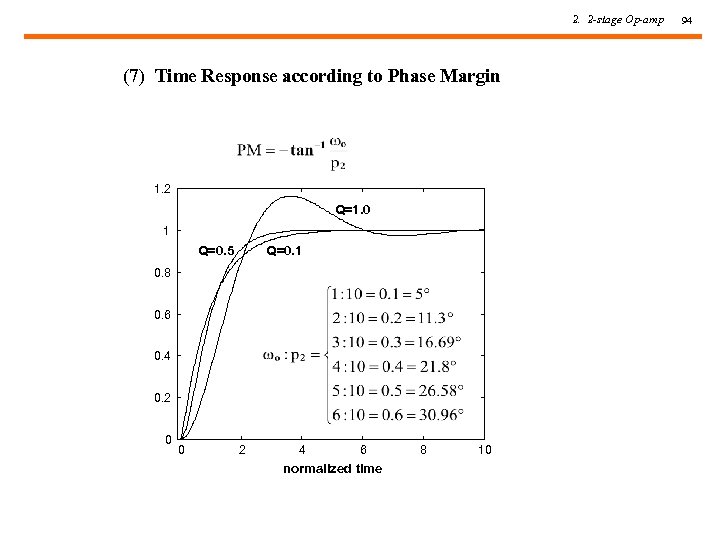

2. 2 -stage Op-amp (7) Time Response according to Phase Margin 1. 2 Q=1. 0 1 Q=0. 5 Q=0. 1 0. 8 0. 6 0. 4 0. 2 0 0 2 4 6 normalized time 8 10 94

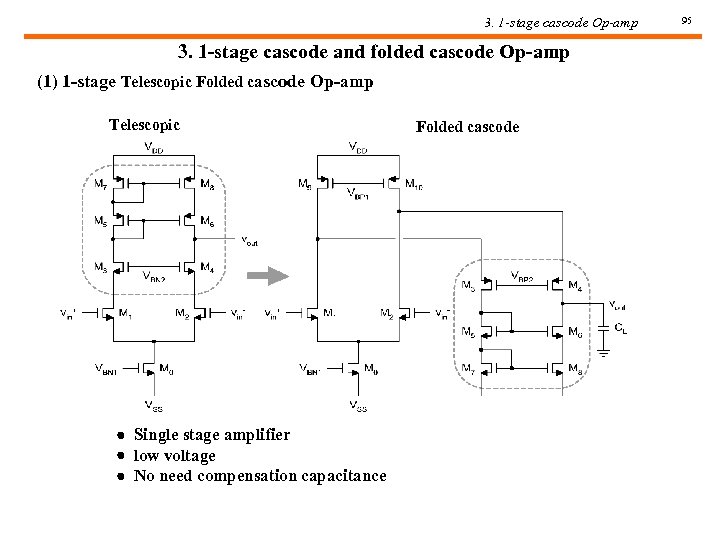

3. 1 -stage cascode Op-amp 3. 1 -stage cascode and folded cascode Op-amp (1) 1 -stage Telescopic Folded cascode Op-amp Telescopic Single stage amplifier low voltage No need compensation capacitance Folded cascode 95

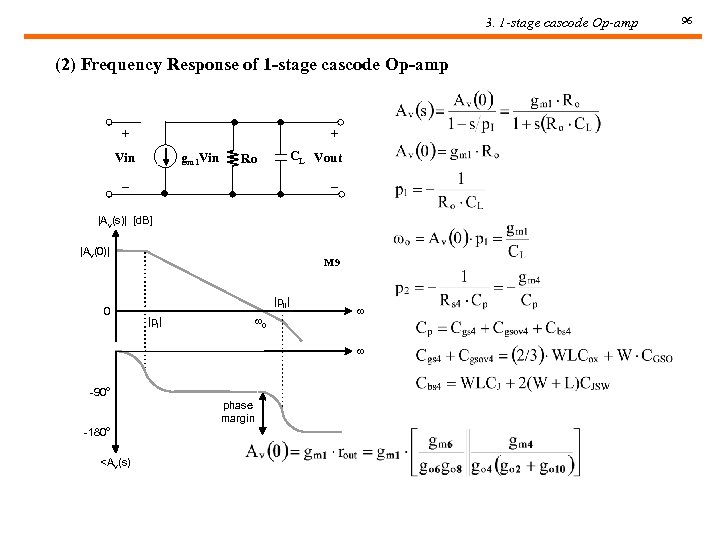

3. 1 -stage cascode Op-amp (2) Frequency Response of 1 -stage cascode Op-amp + + gm 1 Vin Ro CL Vout – – |Av(s)| [d. B] |Av(0)| 0 M 9 |p. II| 0 |p. I| -90 o phase margin -180 o <Av(s) 96

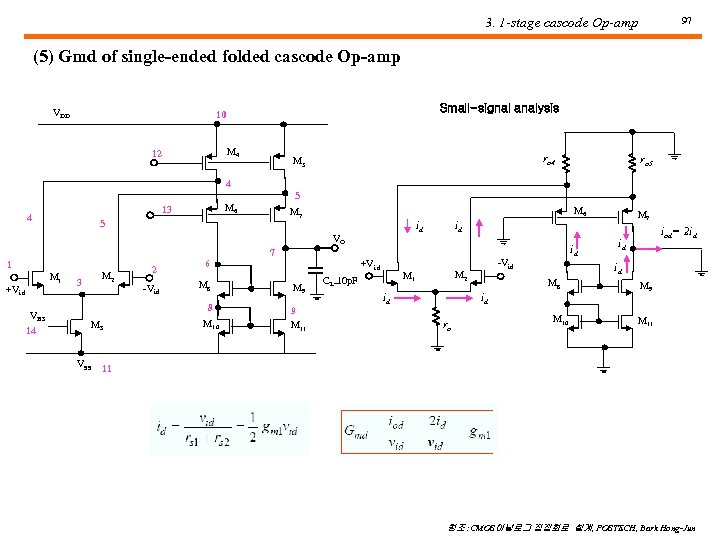

3. 1 -stage cascode Op-amp 97 (5) Gmd of single-ended folded cascode Op-amp VDD Small-signal analysis 10 M 4 12 ro 4 M 5 ro 5 4 5 M 6 13 4 M 6 M 7 5 id VO 7 1 M 1 +Vi d VB 3 14 M 2 3 2 6 +Vi d M 3 VSS M 8 M 9 8 -Vid 9 M 11 M 10 id id -Vid M 2 M 1 CL=10 p. F M 7 id id M 8 id ro iod= 2 id id M 10 M 9 M 11 11 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

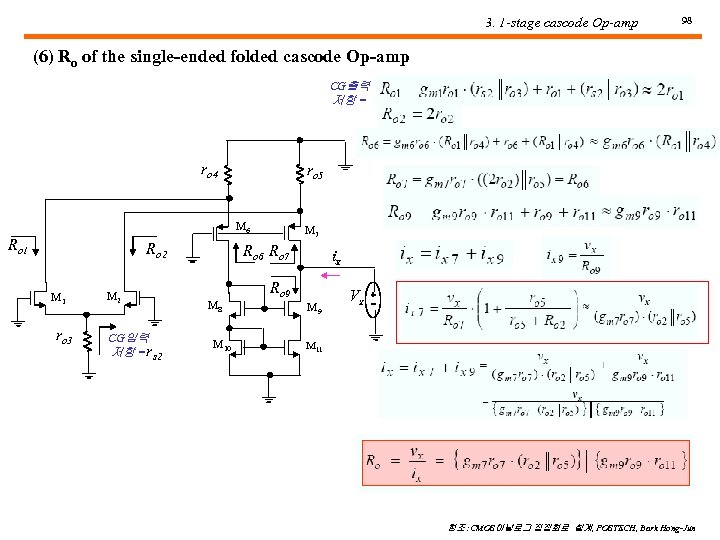

3. 1 -stage cascode Op-amp 98 (6) Ro of the single-ended folded cascode Op-amp CG출력 저항 = ro 4 ro 5 M 6 Ro 1 Ro 2 M 1 ro 3 M 2 CG입력 저항 = rs 2 M 7 Ro 6 Ro 7 M 8 M 10 ix Ro 9 M 9 Vx + - M 11 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

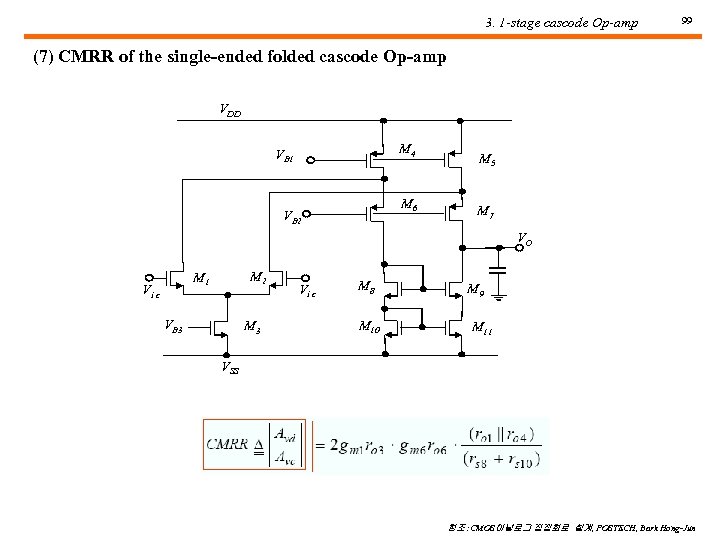

3. 1 -stage cascode Op-amp 99 (7) CMRR of the single-ended folded cascode Op-amp VDD M 4 VB 1 M 6 VB 2 M 5 M 7 VO M 2 M 1 Vi c VB 3 M 3 Vi c M 8 M 10 M 9 M 11 VSS 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

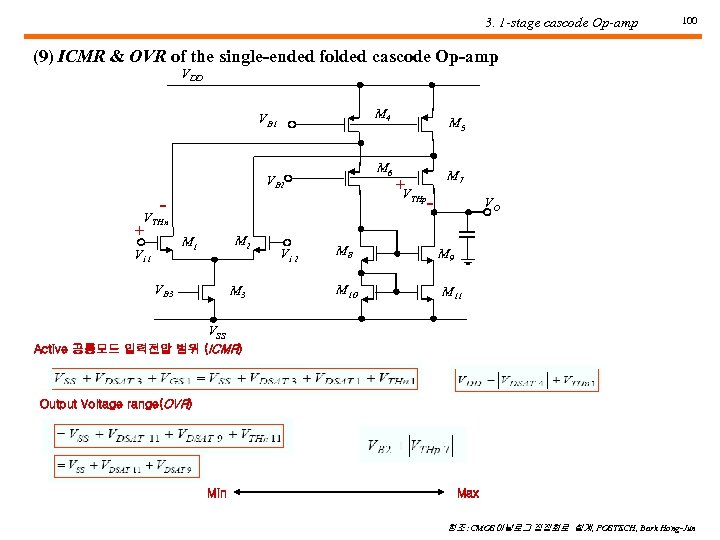

3. 1 -stage cascode Op-amp 100 (9) ICMR & OVR of the single-ended folded cascode Op-amp VDD M 4 VB 1 M 6 VB 2 VTHn M 2 M 1 Vi 1 VB 3 M 3 Vi 2 + VTHp - + M 5 M 8 M 10 M 7 - VO M 9 M 11 VSS Active 공통모드 입력전압 범위 (ICMR) Output Voltage range(OVR) Min Max 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

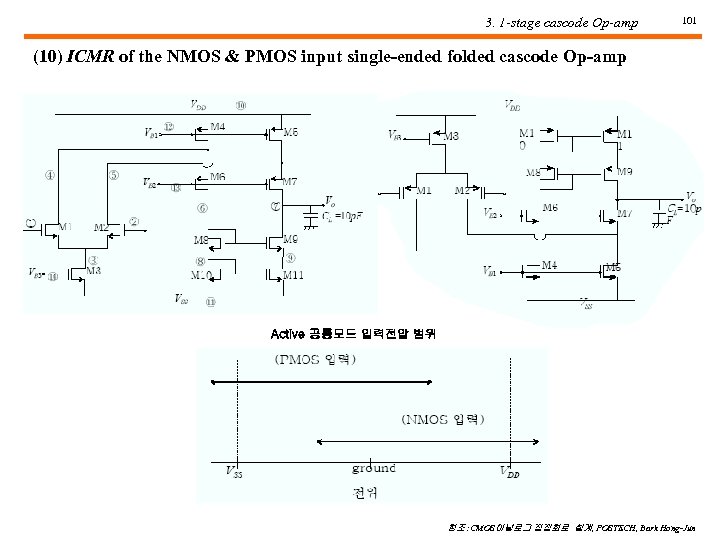

3. 1 -stage cascode Op-amp 101 (10) ICMR of the NMOS & PMOS input single-ended folded cascode Op-amp Active 공통모드 입력전압 범위 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

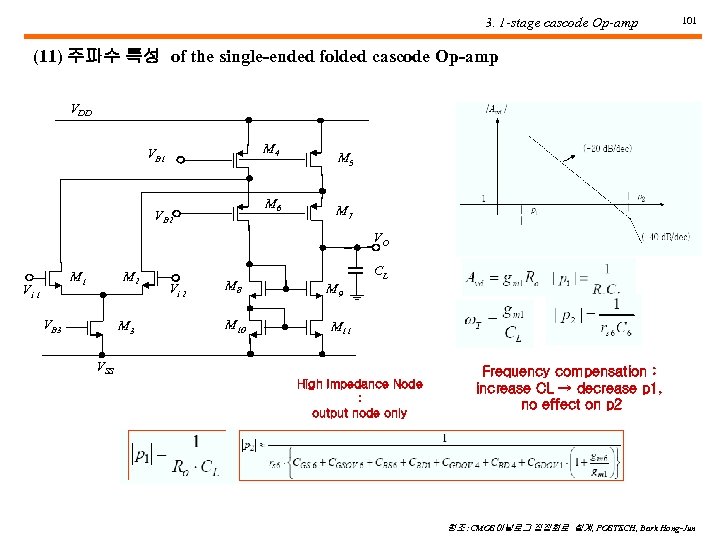

3. 1 -stage cascode Op-amp 101 (11) 주파수 특성 of the single-ended folded cascode Op-amp VDD M 4 VB 1 M 6 VB 2 M 5 M 7 VO M 2 M 1 Vi 1 VB 3 M 3 Vi 2 M 8 M 10 M 9 CL M 11 VSS High Impedance Node : output node only Frequency compensation : increase CL → decrease p 1, no effect on p 2 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

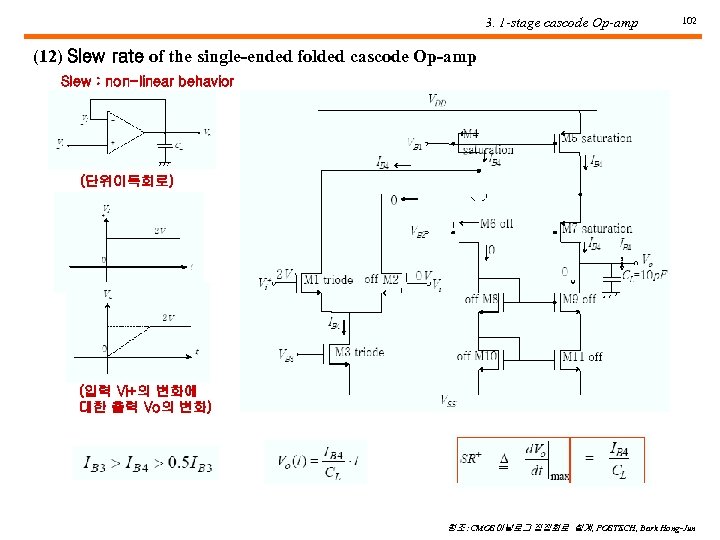

3. 1 -stage cascode Op-amp 102 (12) Slew rate of the single-ended folded cascode Op-amp Slew : non-linear behavior (단위이득회로) (입력 Vi+의 변화에 대한 출력 Vo의 변화) 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

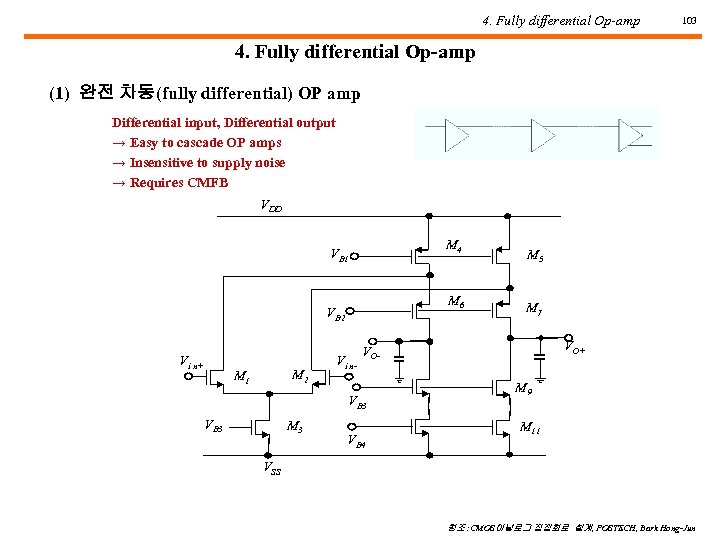

4. Fully differential Op-amp 103 4. Fully differential Op-amp (1) 완전 차동(fully differential) OP amp Differential input, Differential output → Easy to cascade OP amps → Insensitive to supply noise → Requires CMFB VDD M 4 VB 1 M 6 VB 2 Vi n+ M 2 M 1 Vi n- M 3 M 7 VO+ VO- VB 3 M 5 VB 4 M 9 M 11 VSS 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

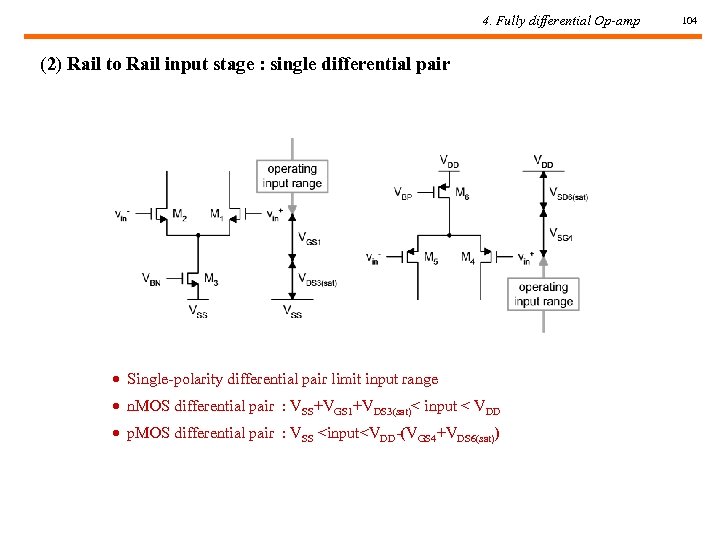

4. Fully differential Op-amp (2) Rail to Rail input stage : single differential pair Single-polarity differential pair limit input range n. MOS differential pair : VSS+VGS 1+VDS 3(sat)< input < VDD p. MOS differential pair : VSS <input<VDD-(VGS 4+VDS 6(sat)) 104

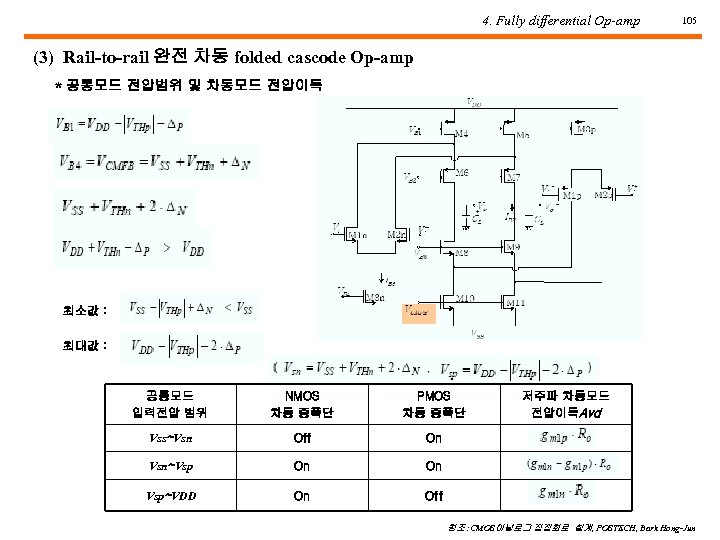

4. Fully differential Op-amp 105 (3) Rail-to-rail 완전 차동 folded cascode Op-amp * 공통모드 전압범위 및 차동모드 전압이득 최소값 : 최대값 : 공통모드 입력전압 범위 NMOS 차동 증폭단 PMOS 차동 증폭단 Vss∼Vsn Off On Vsn∼Vsp On On Vsp∼VDD On 저주파 차동모드 전압이득Avd Off 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

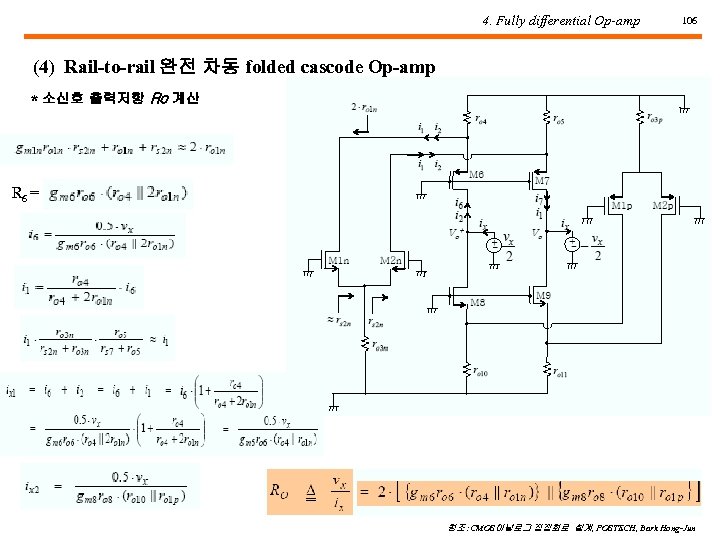

4. Fully differential Op-amp 106 (4) Rail-to-rail 완전 차동 folded cascode Op-amp * 소신호 출력저항 Ro 계산 R 6 = 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

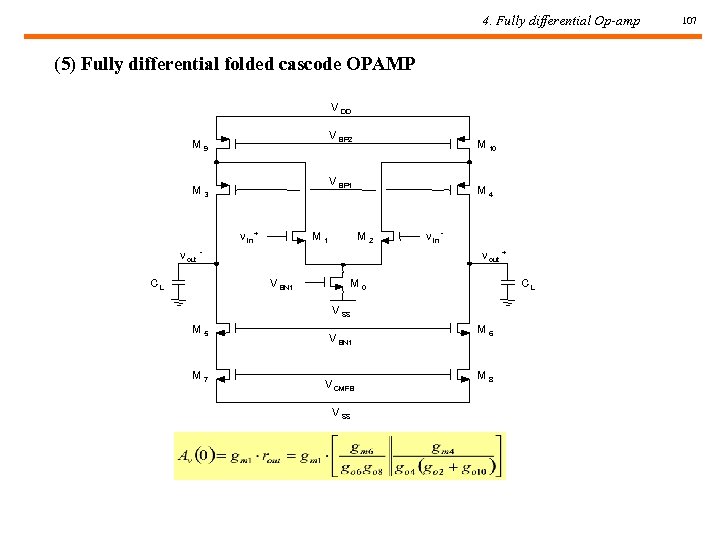

4. Fully differential Op-amp (5) Fully differential folded cascode OPAMP V DD V BP 2 M 9 M 10 V BP 1 M 3 v in + M 1 M 4 M 2 v out CL v in v out + V BN 1 M 0 CL V SS M 5 M 7 V BN 1 V CMFB V SS M 6 M 8 107

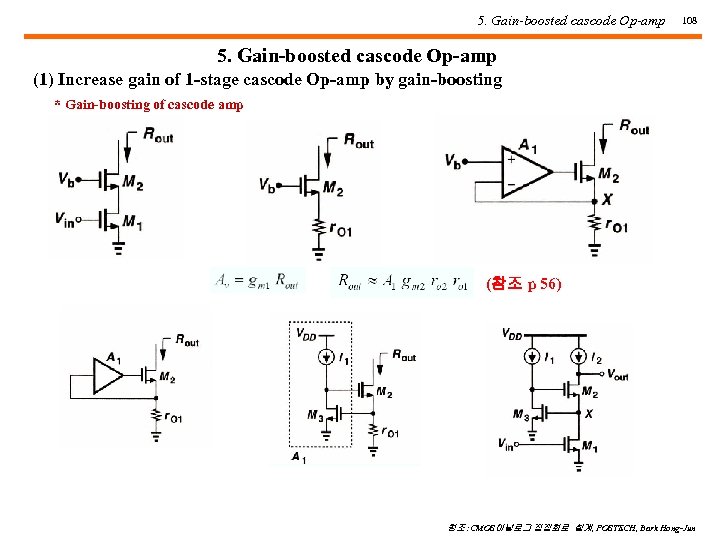

5. Gain-boosted cascode Op-amp 108 5. Gain-boosted cascode Op-amp (1) Increase gain of 1 -stage cascode Op-amp by gain-boosting * Gain-boosting of cascode amp (참조 p 56) 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

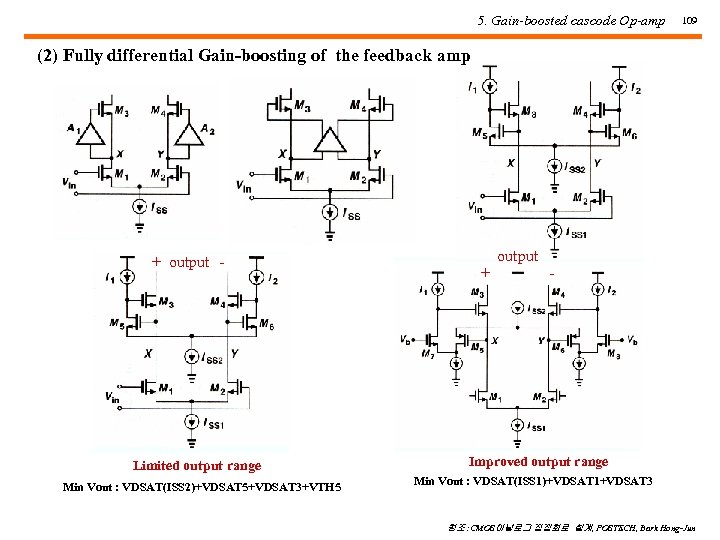

5. Gain-boosted cascode Op-amp 109 (2) Fully differential Gain-boosting of the feedback amp + output - Limited output range Min Vout : VDSAT(ISS 2)+VDSAT 5+VDSAT 3+VTH 5 + output - Improved output range Min Vout : VDSAT(ISS 1)+VDSAT 1+VDSAT 3 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

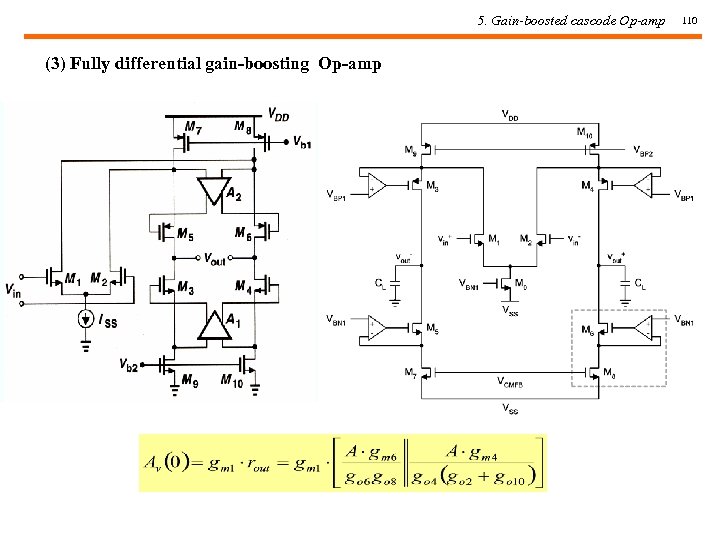

5. Gain-boosted cascode Op-amp (3) Fully differential gain-boosting Op-amp 110

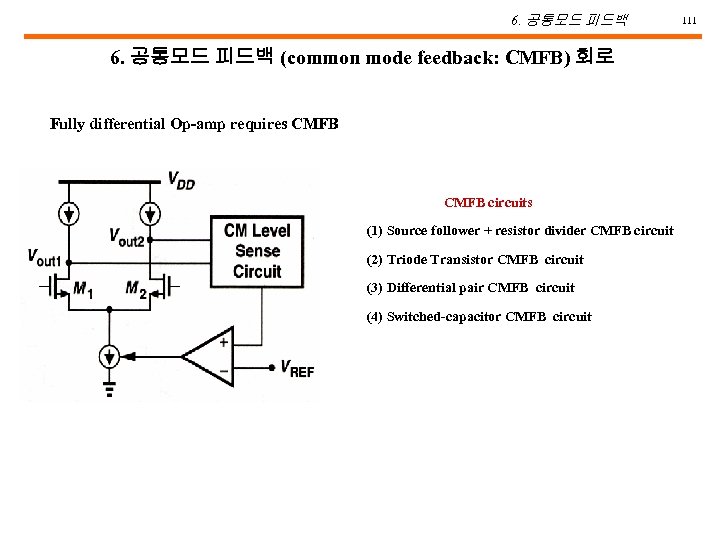

6. 공통모드 피드백 (common mode feedback: CMFB) 회로 Fully differential Op-amp requires CMFB circuits (1) Source follower + resistor divider CMFB circuit (2) Triode Transistor CMFB circuit (3) Differential pair CMFB circuit (4) Switched-capacitor CMFB circuit 111

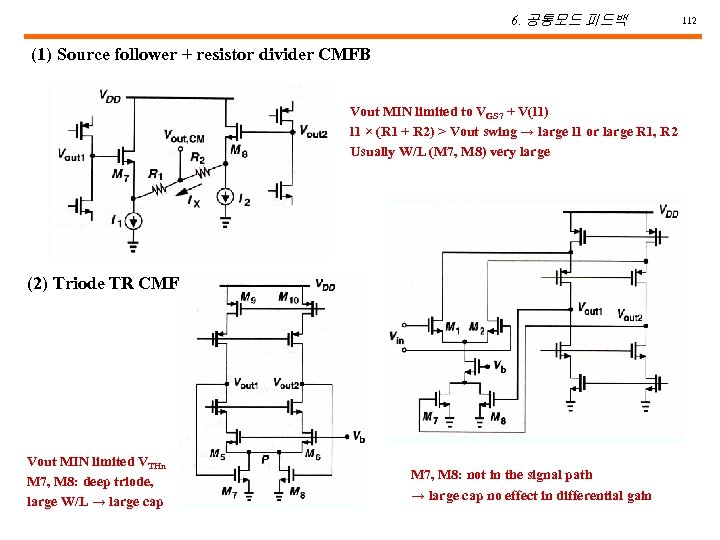

6. 공통모드 피드백 (1) Source follower + resistor divider CMFB Vout MIN limited to VGS 7 + V(l 1) l 1 × (R 1 + R 2) > Vout swing → large l 1 or large R 1, R 2 Usually W/L (M 7, M 8) very large (2) Triode TR CMFB Vout MIN limited VTHn M 7, M 8: deep triode, large W/L → large cap M 7, M 8: not in the signal path → large cap no effect in differential gain 112

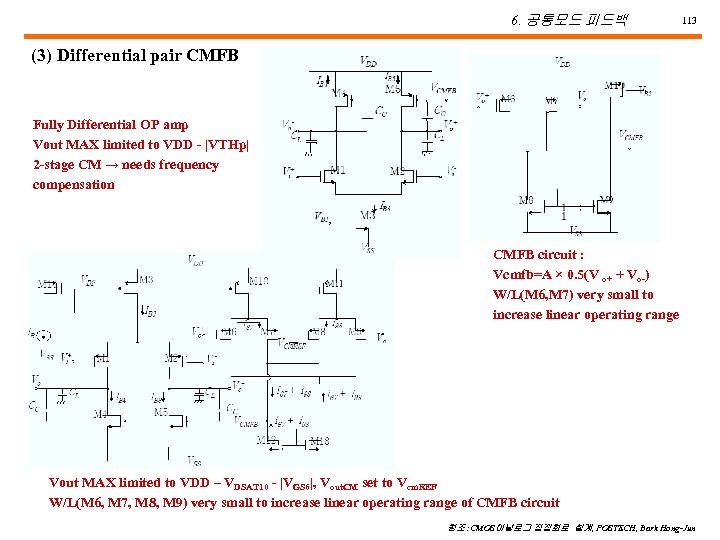

6. 공통모드 피드백 113 (3) Differential pair CMFB Fully Differential OP amp Vout MAX limited to VDD - |VTHp| 2 -stage CM → needs frequency compensation CMFB circuit : Vcmfb=A × 0. 5(V o+ + Vo-) W/L(M 6, M 7) very small to increase linear operating range Vout MAX limited to VDD – VDSAT 10 - |VGS 6|, Vout. CM set to Vcm. REF W/L(M 6, M 7, M 8, M 9) very small to increase linear operating range of CMFB circuit 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

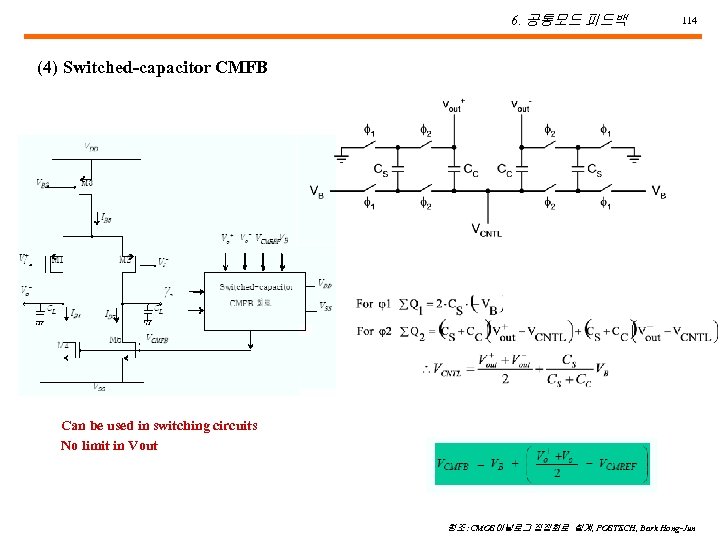

6. 공통모드 피드백 114 (4) Switched-capacitor CMFB Can be used in switching circuits No limit in Vout 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

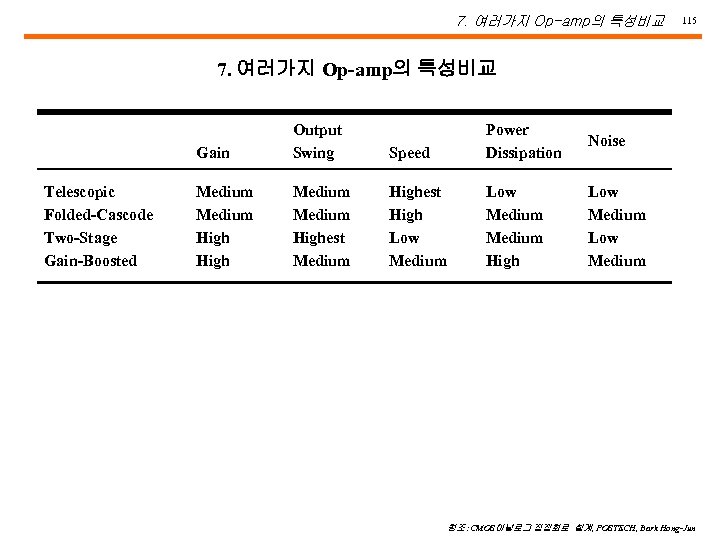

7. 여러가지 Op-amp의 특성비교 115 7. 여러가지 Op-amp의 특성비교 Gain Telescopic Folded-Cascode Two-Stage Gain-Boosted Output Swing Medium Highest Medium Speed Power Dissipation Noise Highest High Low Medium High Low Medium 참조 : CMOS아날로그 집접회로 설계, POSTECH, Bark Hong-Jun

b07bf511b7726906ecbece24be3352a3.ppt