599f4dda31378c7bbd9a88a6dda22cf7.ppt

- Количество слайдов: 24

18 th Panhellenic Conference on Informatics Automated Generation of the Register Set of a SOC and its Verification Environment K. Poulos, K. Adaos, G. P. Alexiou Dept. of Computer Engineering and Informatics Univ. of Patras, Greece

18 th Panhellenic Conference on Informatics Automated Generation of the Register Set of a SOC and its Verification Environment K. Poulos, K. Adaos, G. P. Alexiou Dept. of Computer Engineering and Informatics Univ. of Patras, Greece

Agenda • • Introduction System Environment UVM Register Layer Register Field Template Register File Template Register Generation Procedure Examples Conclusion – Current Work 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 1

Agenda • • Introduction System Environment UVM Register Layer Register Field Template Register File Template Register Generation Procedure Examples Conclusion – Current Work 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 1

Introduction • Part of System-on-Chip Platform for Research and Education • Result of a graduate thesis in the VLSI Lab of CEID. • Target: Develop an automated tool that a) Generates the synthesizabe set of the registers of a SOC b) Generates its verification environment c) Be compliant with design and verification standards 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 2

Introduction • Part of System-on-Chip Platform for Research and Education • Result of a graduate thesis in the VLSI Lab of CEID. • Target: Develop an automated tool that a) Generates the synthesizabe set of the registers of a SOC b) Generates its verification environment c) Be compliant with design and verification standards 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 2

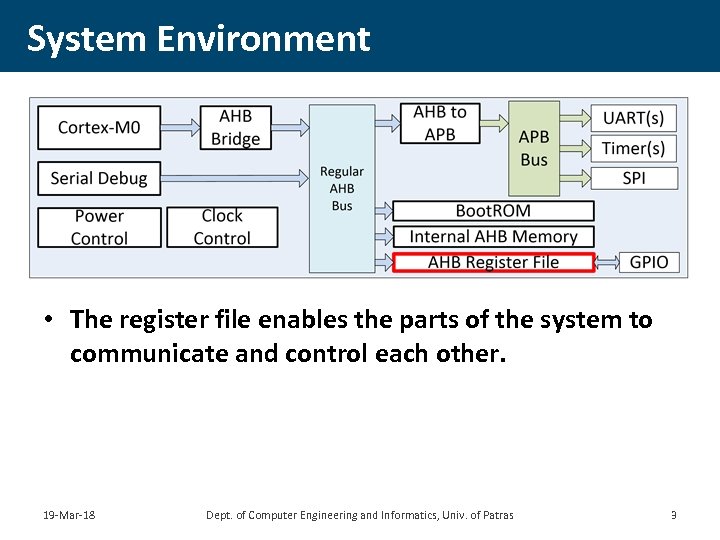

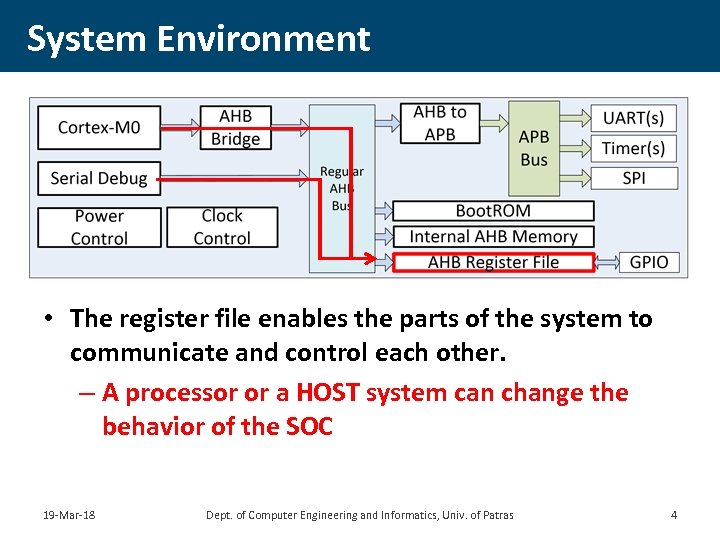

System Environment • The register file enables the parts of the system to communicate and control each other. 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 3

System Environment • The register file enables the parts of the system to communicate and control each other. 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 3

System Environment • The register file enables the parts of the system to communicate and control each other. – A processor or a HOST system can change the behavior of the SOC 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 4

System Environment • The register file enables the parts of the system to communicate and control each other. – A processor or a HOST system can change the behavior of the SOC 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 4

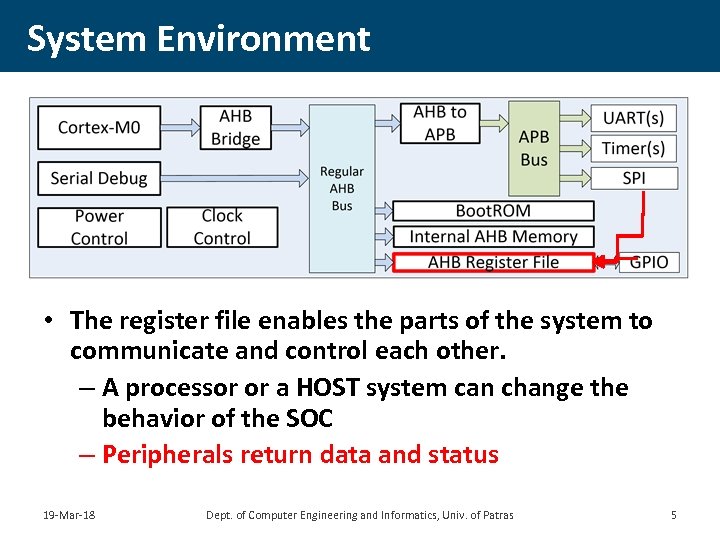

System Environment • The register file enables the parts of the system to communicate and control each other. – A processor or a HOST system can change the behavior of the SOC – Peripherals return data and status 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 5

System Environment • The register file enables the parts of the system to communicate and control each other. – A processor or a HOST system can change the behavior of the SOC – Peripherals return data and status 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 5

UVM Register Layer • UVM is the industry standard for verification • Object Oriented , Based on System. Verilog • Provides a set of predefined agents to control and monitor the bahavior of the DUV • Constraint Randomization Techniques 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 6

UVM Register Layer • UVM is the industry standard for verification • Object Oriented , Based on System. Verilog • Provides a set of predefined agents to control and monitor the bahavior of the DUV • Constraint Randomization Techniques 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 6

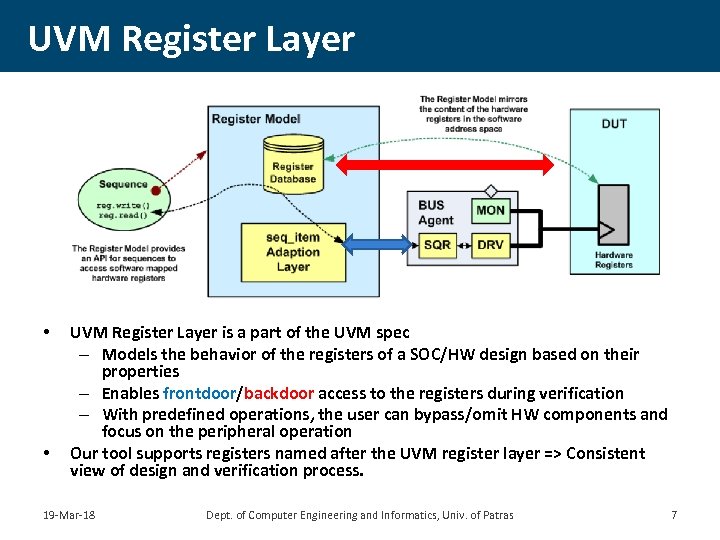

UVM Register Layer • • UVM Register Layer is a part of the UVM spec – Models the behavior of the registers of a SOC/HW design based on their properties – Enables frontdoor/backdoor access to the registers during verification – With predefined operations, the user can bypass/omit HW components and focus on the peripheral operation Our tool supports registers named after the UVM register layer => Consistent view of design and verification process. 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 7

UVM Register Layer • • UVM Register Layer is a part of the UVM spec – Models the behavior of the registers of a SOC/HW design based on their properties – Enables frontdoor/backdoor access to the registers during verification – With predefined operations, the user can bypass/omit HW components and focus on the peripheral operation Our tool supports registers named after the UVM register layer => Consistent view of design and verification process. 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 7

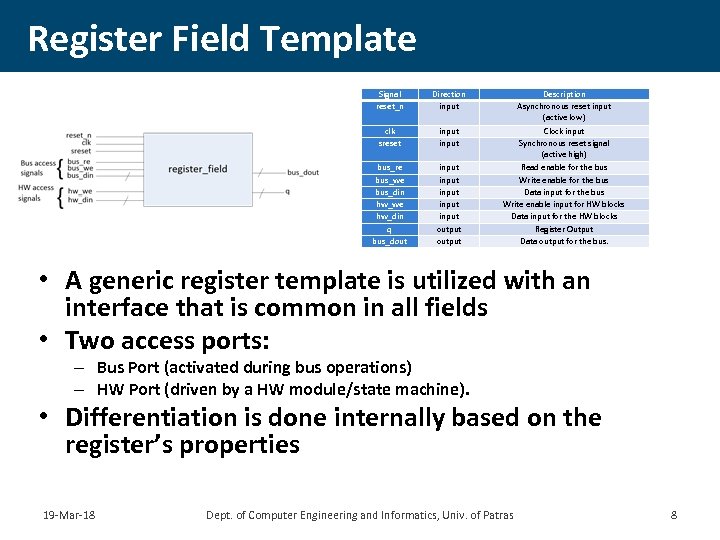

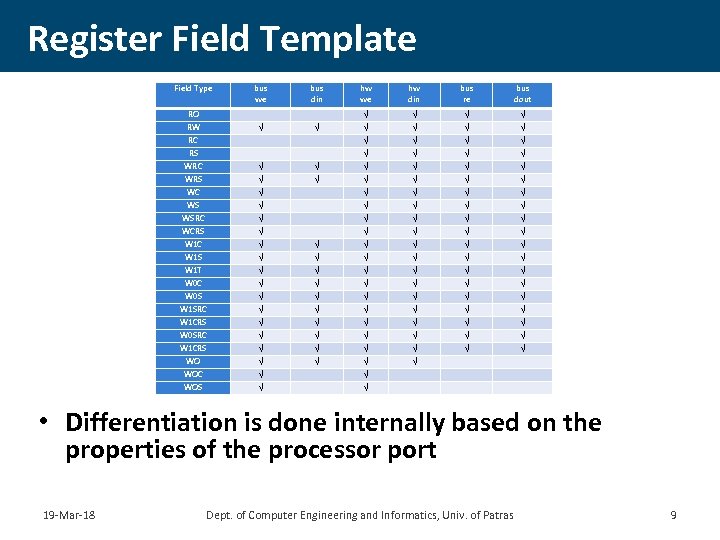

Register Field Template Signal reset_n Direction input Description Asynchronous reset input (active low) clk sreset input Clock input Synchronous reset signal (active high) bus_re bus_we bus_din hw_we hw_din q bus_dout input input output Read enable for the bus Write enable for the bus Data input for the bus Write enable input for HW blocks Data input for the HW blocks Register Output Data output for the bus. • A generic register template is utilized with an interface that is common in all fields • Two access ports: – Bus Port (activated during bus operations) – HW Port (driven by a HW module/state machine). • Differentiation is done internally based on the register’s properties 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 8

Register Field Template Signal reset_n Direction input Description Asynchronous reset input (active low) clk sreset input Clock input Synchronous reset signal (active high) bus_re bus_we bus_din hw_we hw_din q bus_dout input input output Read enable for the bus Write enable for the bus Data input for the bus Write enable input for HW blocks Data input for the HW blocks Register Output Data output for the bus. • A generic register template is utilized with an interface that is common in all fields • Two access ports: – Bus Port (activated during bus operations) – HW Port (driven by a HW module/state machine). • Differentiation is done internally based on the register’s properties 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 8

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • Differentiation is done internally based on the properties of the processor port 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 9

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • Differentiation is done internally based on the properties of the processor port 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 9

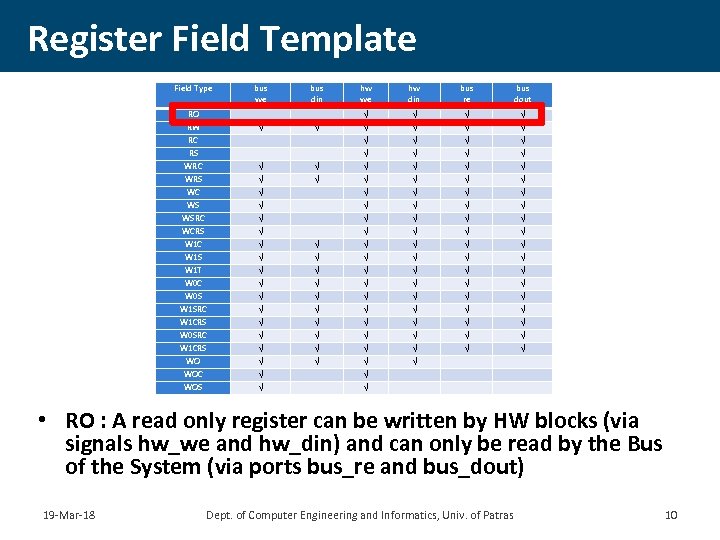

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • RO : A read only register can be written by HW blocks (via signals hw_we and hw_din) and can only be read by the Bus of the System (via ports bus_re and bus_dout) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 10

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • RO : A read only register can be written by HW blocks (via signals hw_we and hw_din) and can only be read by the Bus of the System (via ports bus_re and bus_dout) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 10

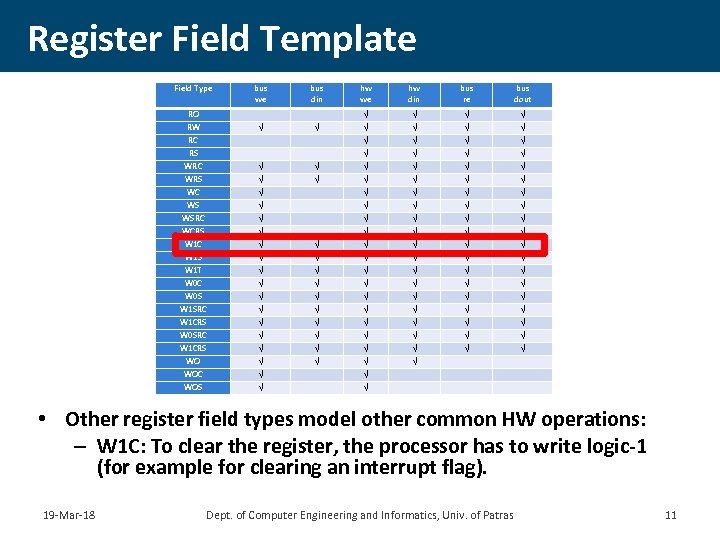

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • Other register field types model other common HW operations: – W 1 C: To clear the register, the processor has to write logic-1 (for example for clearing an interrupt flag). 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 11

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • Other register field types model other common HW operations: – W 1 C: To clear the register, the processor has to write logic-1 (for example for clearing an interrupt flag). 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 11

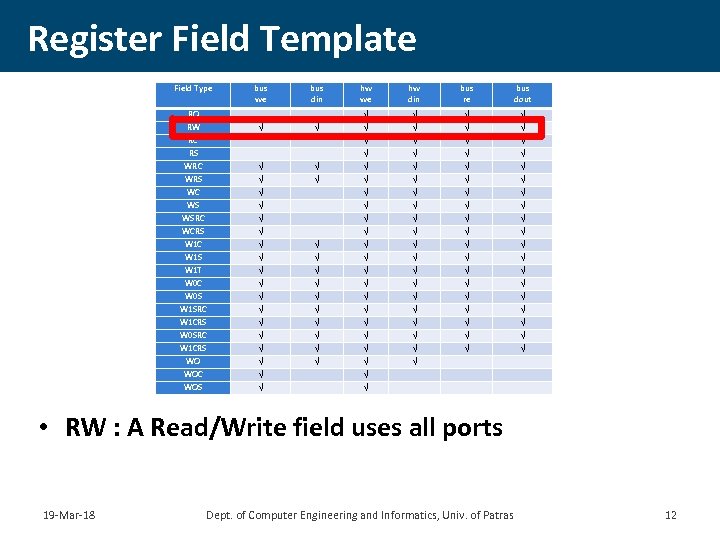

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • RW : A Read/Write field uses all ports 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 12

Register Field Template Field Type bus we bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS • RW : A Read/Write field uses all ports 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 12

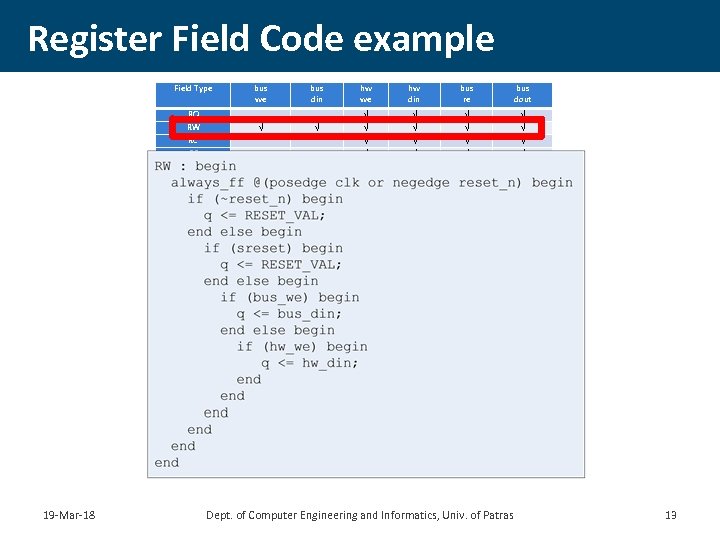

Register Field Code example Field Type bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS 19 -Mar-18 bus we Dept. of Computer Engineering and Informatics, Univ. of Patras 13

Register Field Code example Field Type bus din hw we hw din bus re bus dout RO RW RC RS WRC WRS WC WS WSRC WCRS W 1 C W 1 S W 1 T W 0 C W 0 S W 1 SRC W 1 CRS W 0 SRC W 1 CRS WO WOC WOS 19 -Mar-18 bus we Dept. of Computer Engineering and Informatics, Univ. of Patras 13

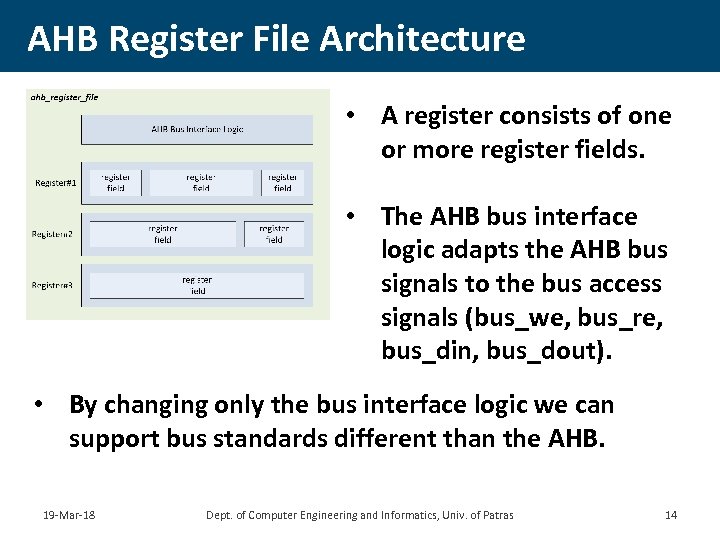

AHB Register File Architecture • A register consists of one or more register fields. • The AHB bus interface logic adapts the AHB bus signals to the bus access signals (bus_we, bus_re, bus_din, bus_dout). • By changing only the bus interface logic we can support bus standards different than the AHB. 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 14

AHB Register File Architecture • A register consists of one or more register fields. • The AHB bus interface logic adapts the AHB bus signals to the bus access signals (bus_we, bus_re, bus_din, bus_dout). • By changing only the bus interface logic we can support bus standards different than the AHB. 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 14

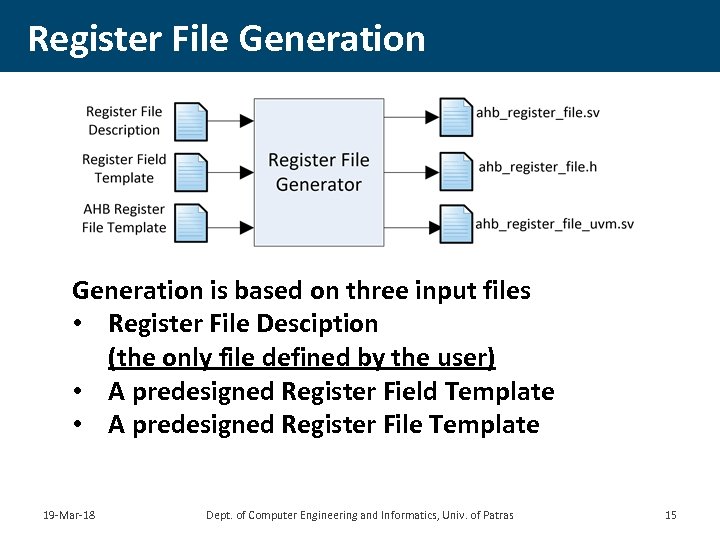

Register File Generation is based on three input files • Register File Desciption (the only file defined by the user) • A predesigned Register Field Template • A predesigned Register File Template 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 15

Register File Generation is based on three input files • Register File Desciption (the only file defined by the user) • A predesigned Register Field Template • A predesigned Register File Template 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 15

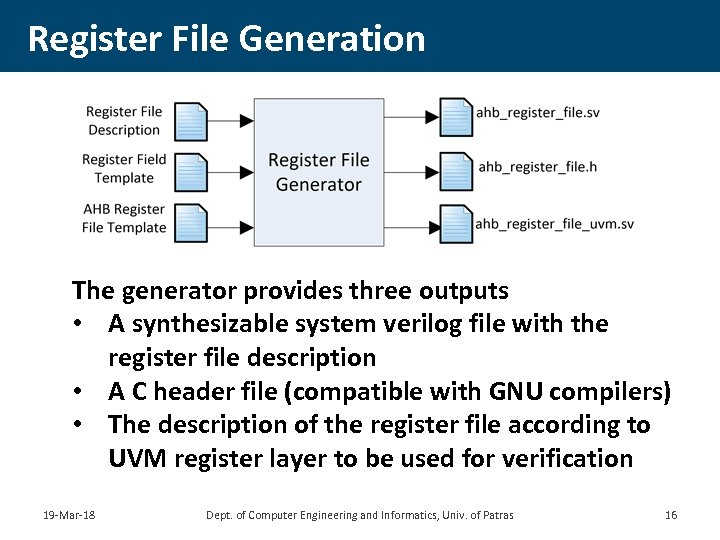

Register File Generation The generator provides three outputs • A synthesizable system verilog file with the register file description • A C header file (compatible with GNU compilers) • The description of the register file according to UVM register layer to be used for verification 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 16

Register File Generation The generator provides three outputs • A synthesizable system verilog file with the register file description • A C header file (compatible with GNU compilers) • The description of the register file according to UVM register layer to be used for verification 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 16

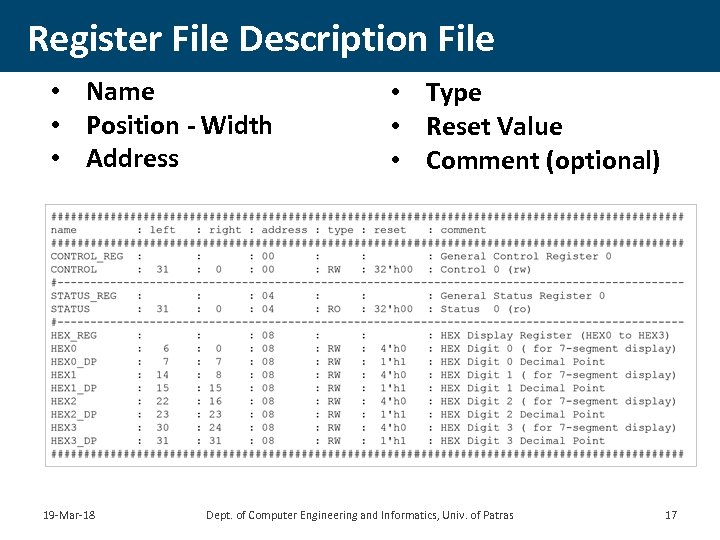

Register File Description File • Name • Position - Width • Address 19 -Mar-18 • Type • Reset Value • Comment (optional) Dept. of Computer Engineering and Informatics, Univ. of Patras 17

Register File Description File • Name • Position - Width • Address 19 -Mar-18 • Type • Reset Value • Comment (optional) Dept. of Computer Engineering and Informatics, Univ. of Patras 17

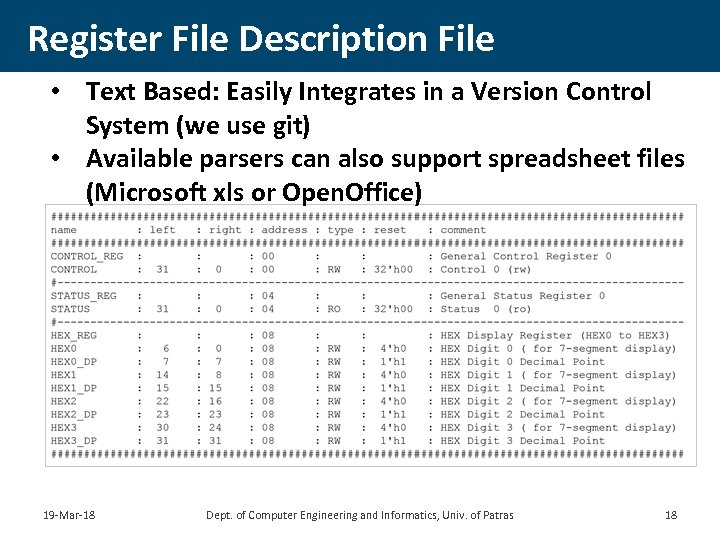

Register File Description File • Text Based: Easily Integrates in a Version Control System (we use git) • Available parsers can also support spreadsheet files (Microsoft xls or Open. Office) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 18

Register File Description File • Text Based: Easily Integrates in a Version Control System (we use git) • Available parsers can also support spreadsheet files (Microsoft xls or Open. Office) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 18

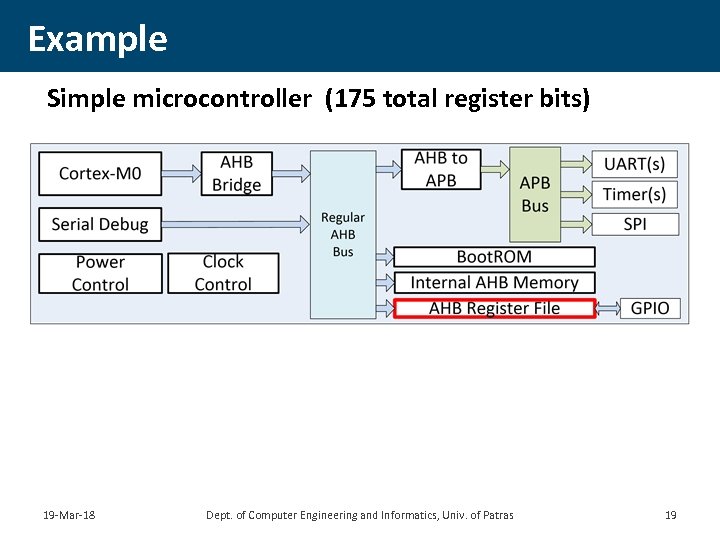

Example Simple microcontroller (175 total register bits) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 19

Example Simple microcontroller (175 total register bits) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 19

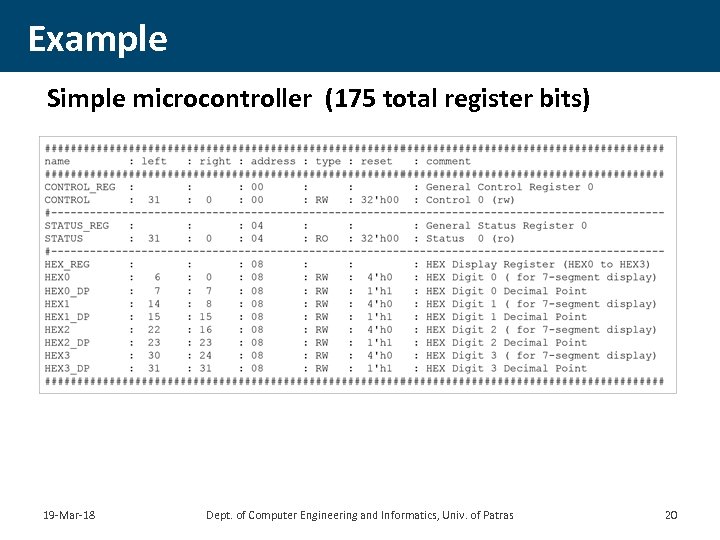

Example Simple microcontroller (175 total register bits) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 20

Example Simple microcontroller (175 total register bits) 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 20

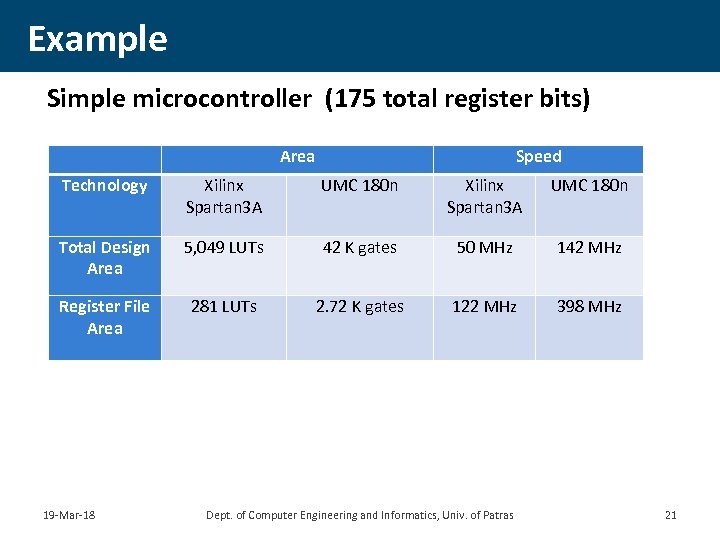

Example Simple microcontroller (175 total register bits) Area Speed Technology Xilinx Spartan 3 A UMC 180 n Total Design Area 5, 049 LUTs 42 K gates 50 MHz 142 MHz Register File Area 281 LUTs 2. 72 K gates 122 MHz 398 MHz 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 21

Example Simple microcontroller (175 total register bits) Area Speed Technology Xilinx Spartan 3 A UMC 180 n Total Design Area 5, 049 LUTs 42 K gates 50 MHz 142 MHz Register File Area 281 LUTs 2. 72 K gates 122 MHz 398 MHz 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 21

Current Work • Support of extra register fields and types • Support of additional bus standards (Wishbone, APB, AXI) • GUI support • Extend automation in other SOC components 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 22

Current Work • Support of extra register fields and types • Support of additional bus standards (Wishbone, APB, AXI) • GUI support • Extend automation in other SOC components 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 22

Automated Generation of the Register Set of a SOC and its Verification Environment adaos@ceid. upatras. gr www. ceid. upatras. gr/webpages/faculty/alexiou/vlsilab 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 23

Automated Generation of the Register Set of a SOC and its Verification Environment adaos@ceid. upatras. gr www. ceid. upatras. gr/webpages/faculty/alexiou/vlsilab 19 -Mar-18 Dept. of Computer Engineering and Informatics, Univ. of Patras 23