1 Микропроцессорные системы и их программирование Архитектура компьютера.

![22 mov al,ch; (al) <-- (ch). mov cx,dx; mov bh,[mems];содержимое ячейки памяти с символическим 22 mov al,ch; (al) <-- (ch). mov cx,dx; mov bh,[mems];содержимое ячейки памяти с символическим](https://present5.com/customparser/19688283_133450166 --- ak_modul1_tema2_11-12.ppt/slide_22.jpg)

![31 Команды сдвига КОП op1,1 или КОП op1,cl shl op1,1 CF:=op1[N]; for i:=N downto 31 Команды сдвига КОП op1,1 или КОП op1,cl shl op1,1 CF:=op1[N]; for i:=N downto](https://present5.com/customparser/19688283_133450166 --- ak_modul1_tema2_11-12.ppt/slide_31.jpg)

ak_modul1_tema2_11-12.ppt

- Количество слайдов: 38

1 Микропроцессорные системы и их программирование Архитектура компьютера. Модуль 1. Тема 2.

1 Микропроцессорные системы и их программирование Архитектура компьютера. Модуль 1. Тема 2.

2 План Микропроцессорные системы. Структурная схема микропроцессора 8086/8088 Команды микропроцессора Введение в программирование микропроцессоров

2 План Микропроцессорные системы. Структурная схема микропроцессора 8086/8088 Команды микропроцессора Введение в программирование микропроцессоров

3 1. Микропроцессорные системы Это системы обработки данных на основе микропроцессоров – программируемых БИС (СБИС, …) Логика обработки задается программой – последовательностью команд, «понятных» процессору

3 1. Микропроцессорные системы Это системы обработки данных на основе микропроцессоров – программируемых БИС (СБИС, …) Логика обработки задается программой – последовательностью команд, «понятных» процессору

4 Структура команды Код операции (КОп) – определяет тип операции, выполняемой ЦП Адресная часть – задает местоположение операндов

4 Структура команды Код операции (КОп) – определяет тип операции, выполняемой ЦП Адресная часть – задает местоположение операндов

5 Интерпретация команды Выборка команды из памяти Анализ кода операции и выделение адресной части Вычисление эффективного адреса операндов Запрос данных Выполнение команды на АЛУ Запись результата

5 Интерпретация команды Выборка команды из памяти Анализ кода операции и выделение адресной части Вычисление эффективного адреса операндов Запрос данных Выполнение команды на АЛУ Запись результата

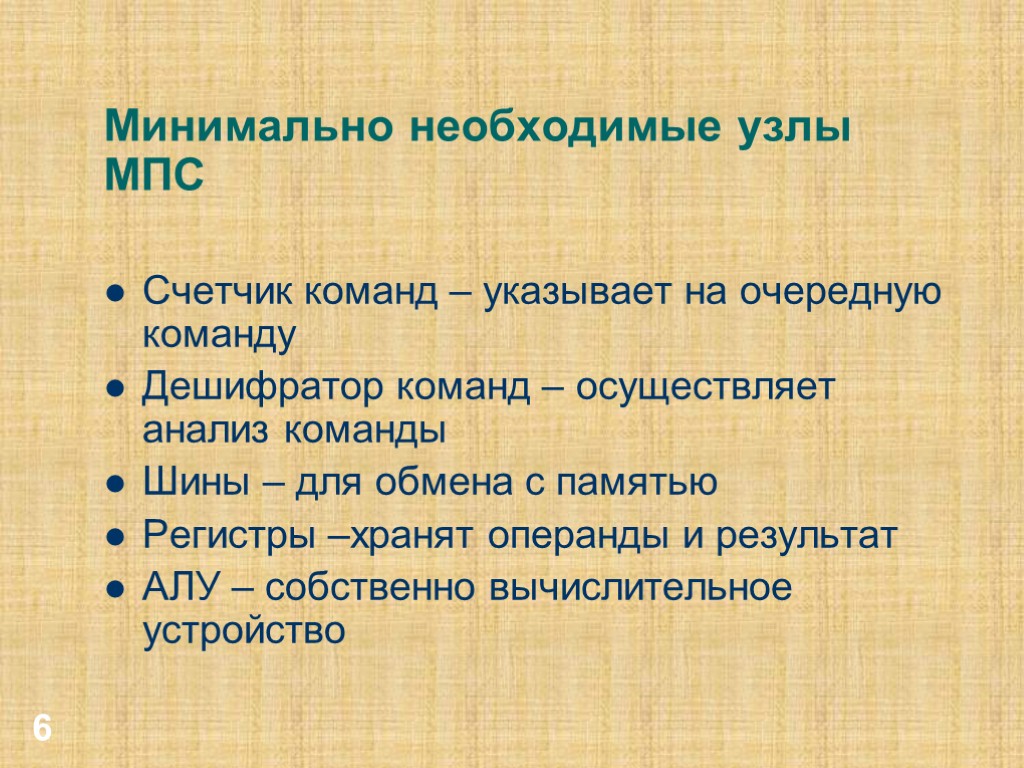

6 Минимально необходимые узлы МПС Счетчик команд – указывает на очередную команду Дешифратор команд – осуществляет анализ команды Шины – для обмена с памятью Регистры –хранят операнды и результат АЛУ – собственно вычислительное устройство

6 Минимально необходимые узлы МПС Счетчик команд – указывает на очередную команду Дешифратор команд – осуществляет анализ команды Шины – для обмена с памятью Регистры –хранят операнды и результат АЛУ – собственно вычислительное устройство

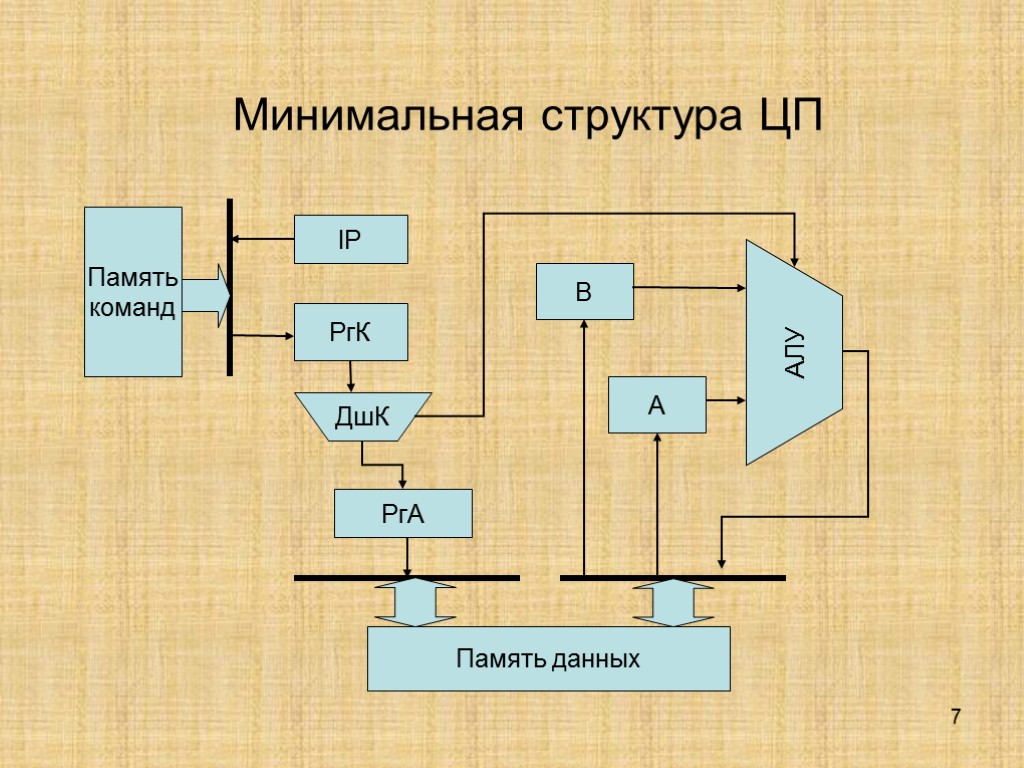

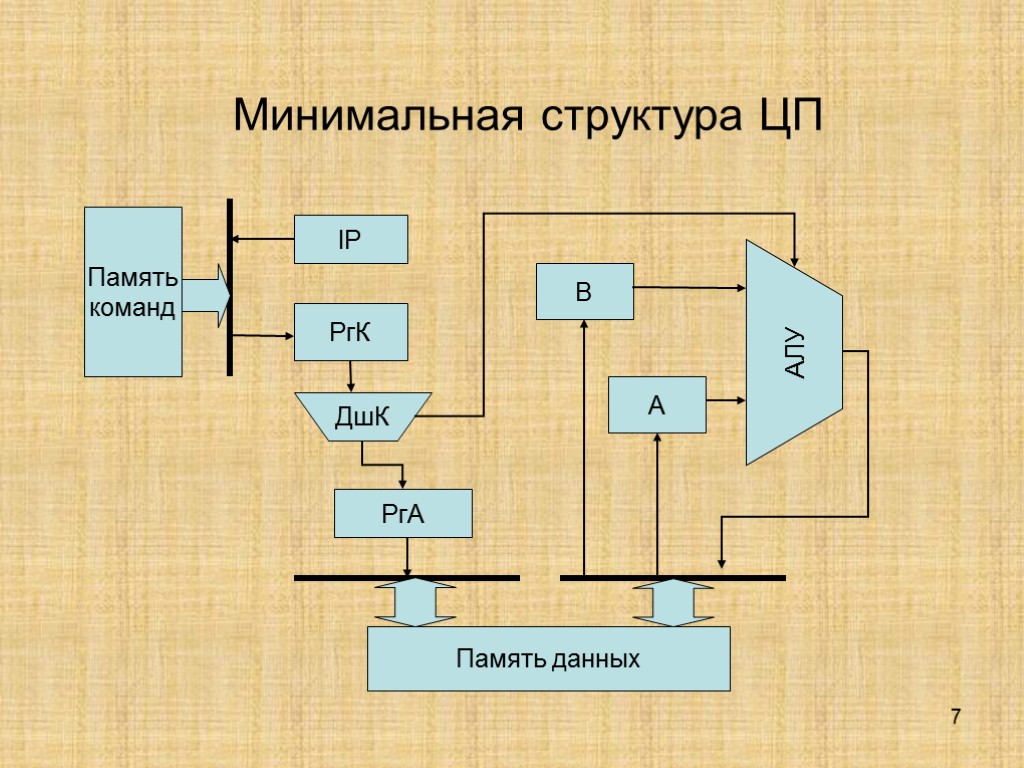

7 Минимальная структура ЦП АЛУ IP A B РгК РгА ДшК Память команд Память данных

7 Минимальная структура ЦП АЛУ IP A B РгК РгА ДшК Память команд Память данных

8 СТРУКТУРНАЯ СХЕМА МИКРОПРОЦЕССОРА 8086/8088

8 СТРУКТУРНАЯ СХЕМА МИКРОПРОЦЕССОРА 8086/8088

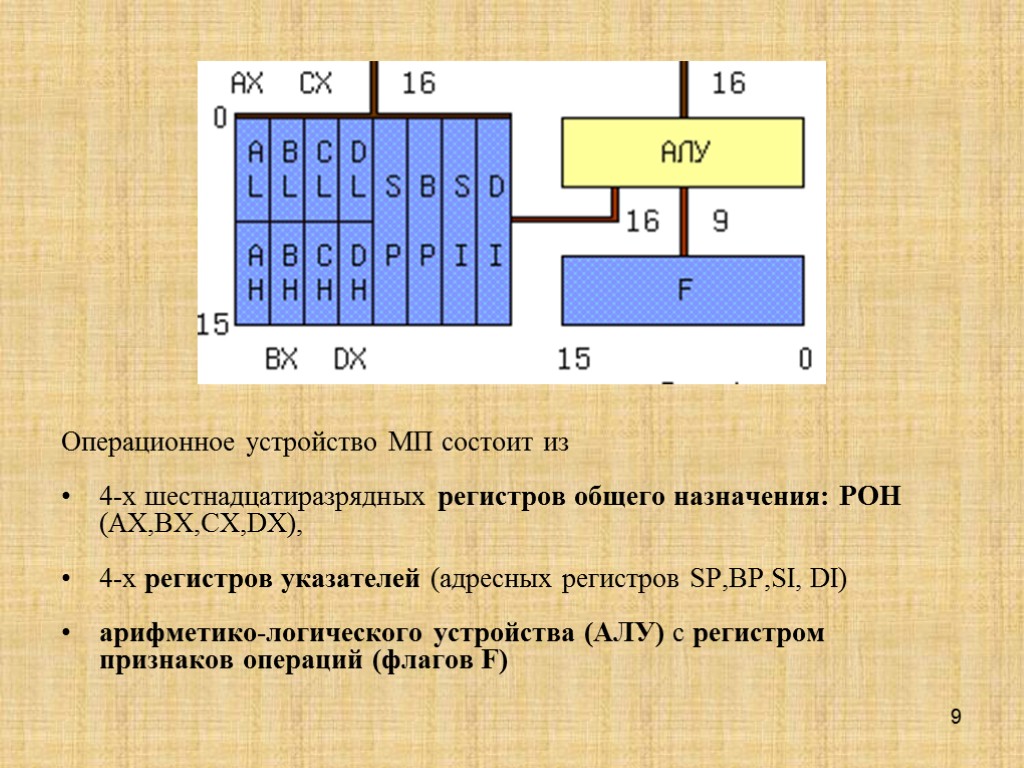

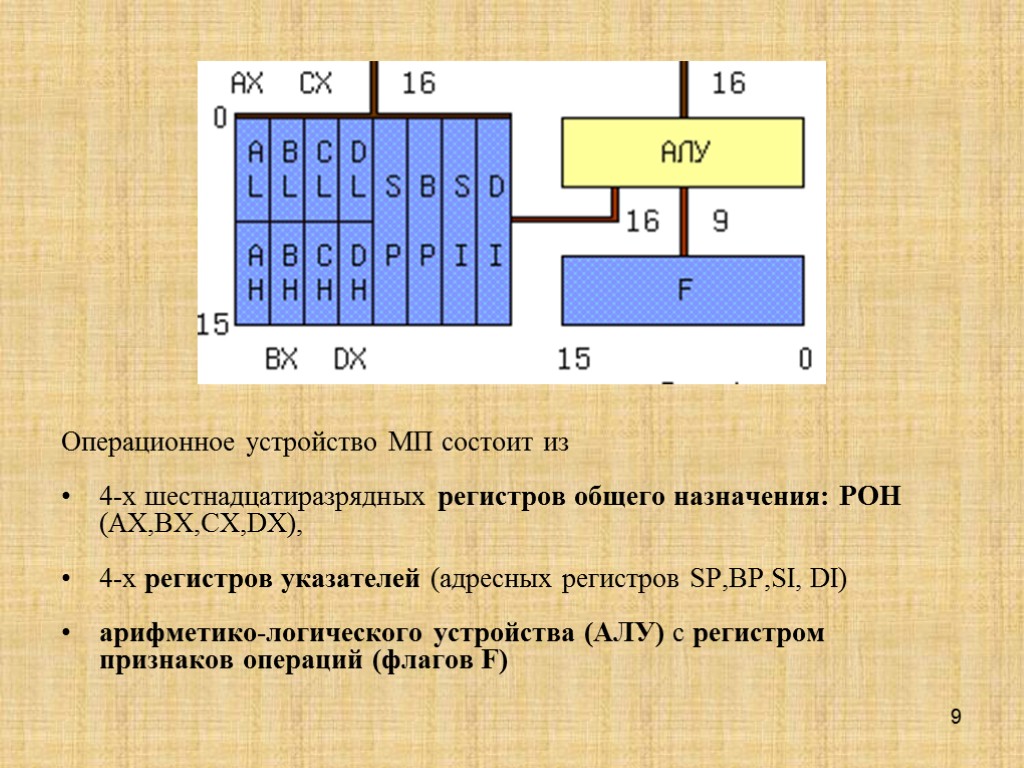

9 Операционное устройство МП состоит из 4-х шестнадцатиразрядных регистров общего назначения: РОН (AX,BX,CX,DX), 4-х регистров указателей (адресных регистров SP,BP,SI, DI) арифметико-логического устройства (АЛУ) с регистром признаков операций (флагов F)

9 Операционное устройство МП состоит из 4-х шестнадцатиразрядных регистров общего назначения: РОН (AX,BX,CX,DX), 4-х регистров указателей (адресных регистров SP,BP,SI, DI) арифметико-логического устройства (АЛУ) с регистром признаков операций (флагов F)

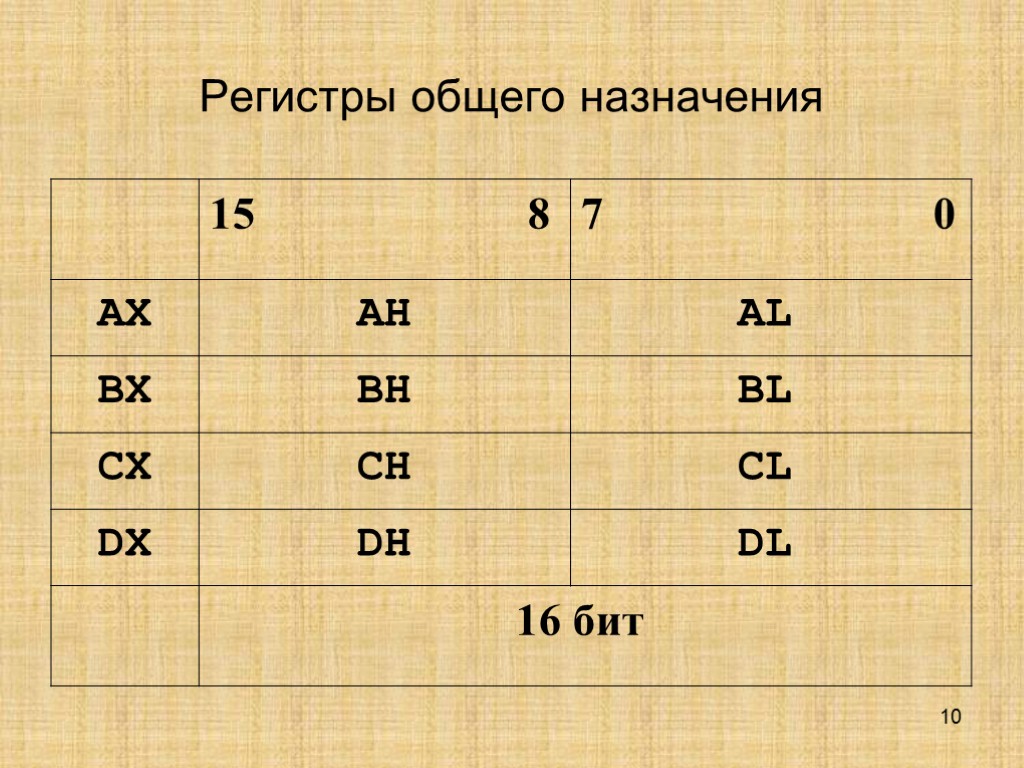

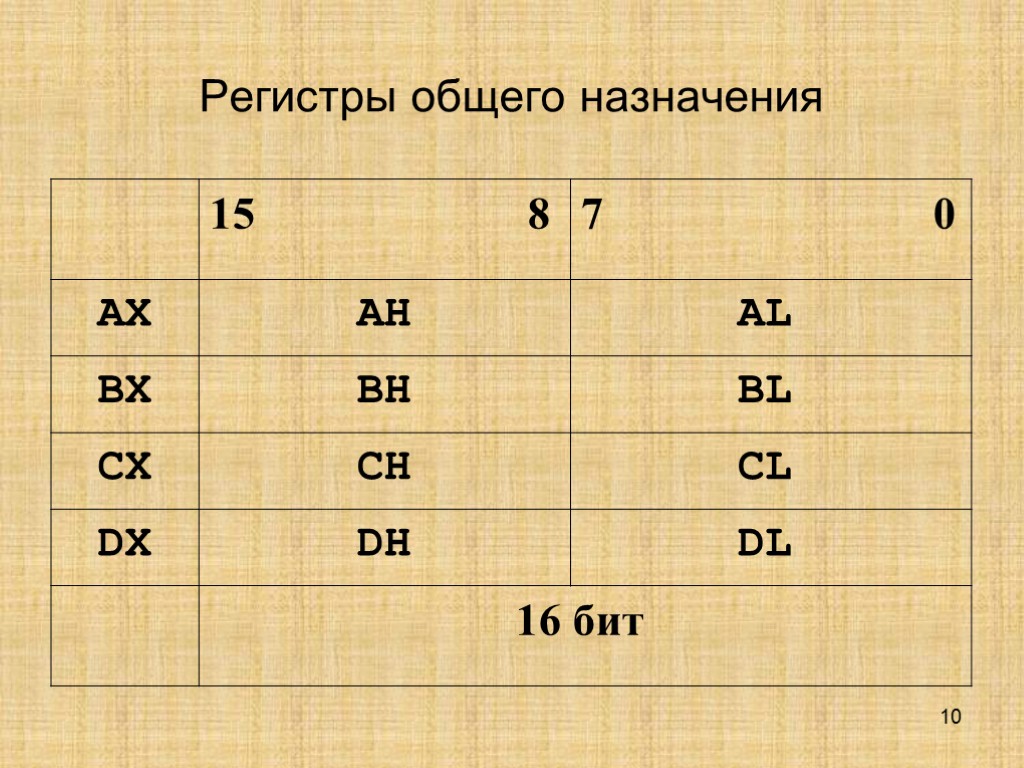

10 Регистры общего назначения

10 Регистры общего назначения

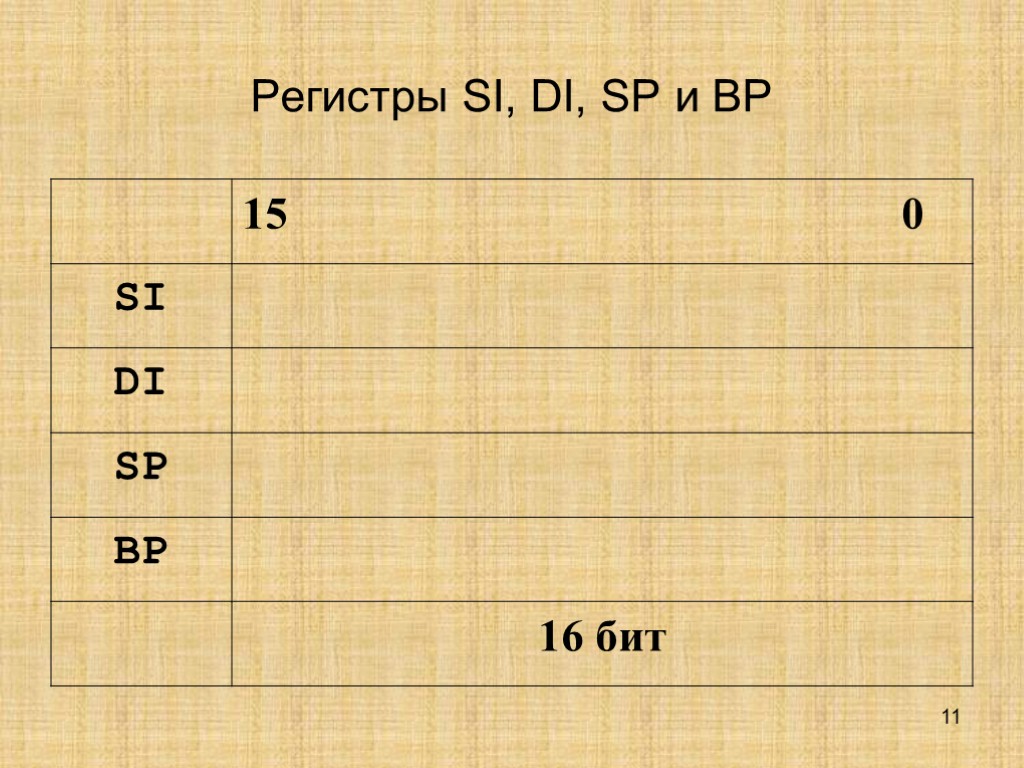

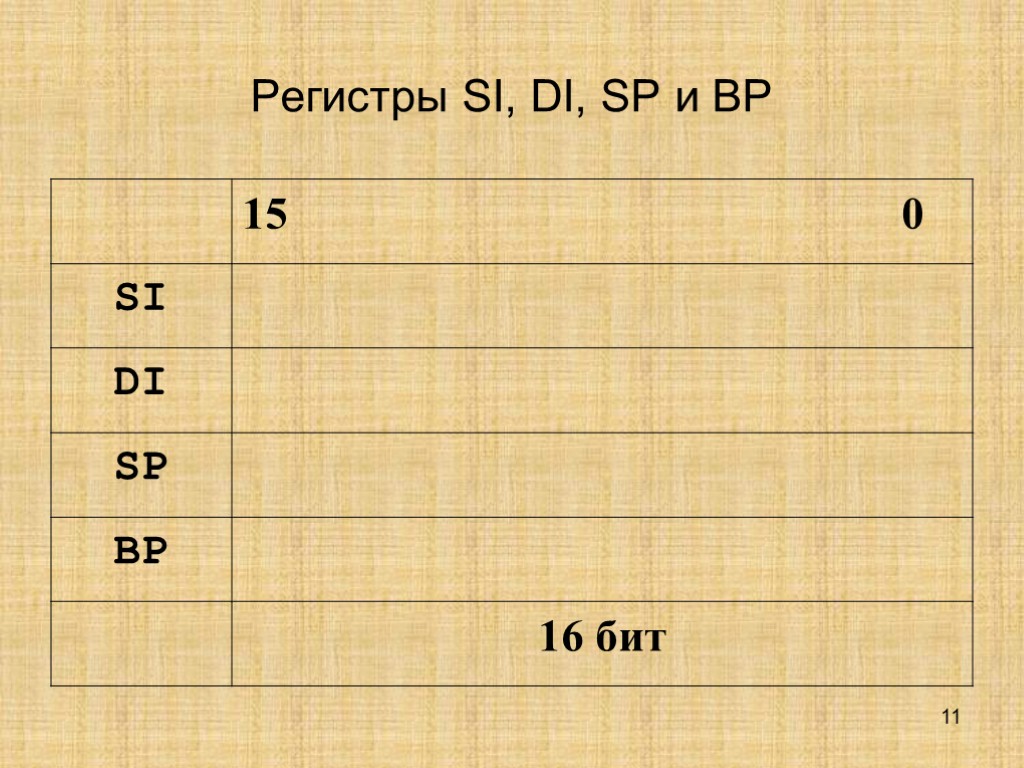

11 Регистры SI, DI, SP и BP

11 Регистры SI, DI, SP и BP

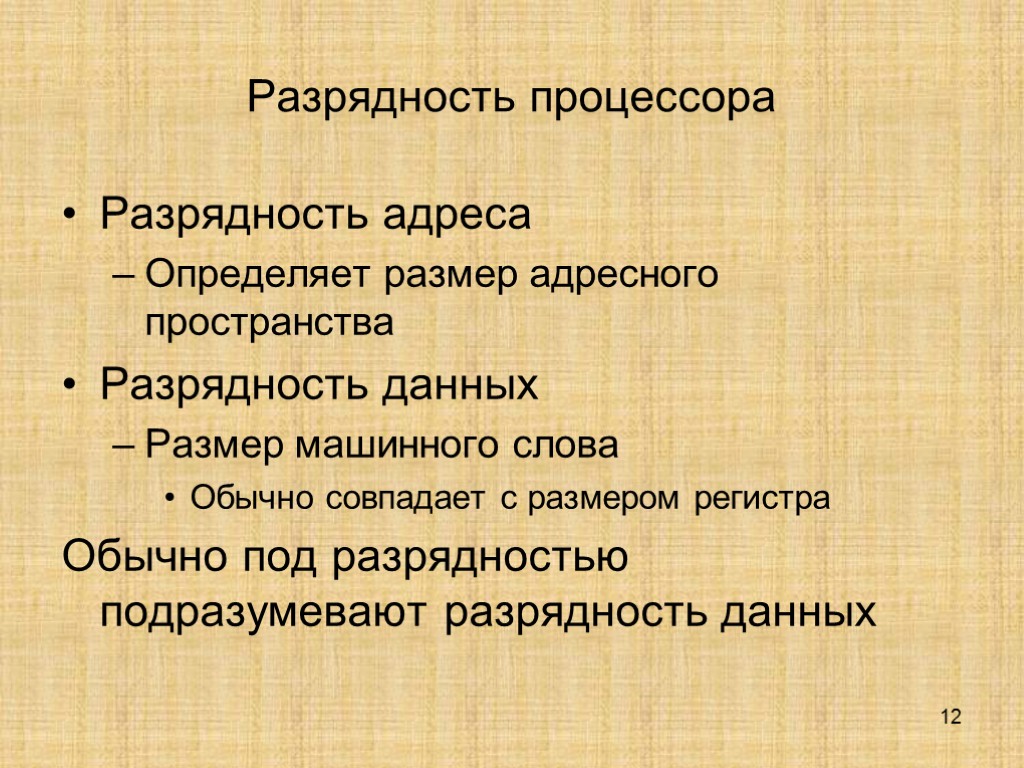

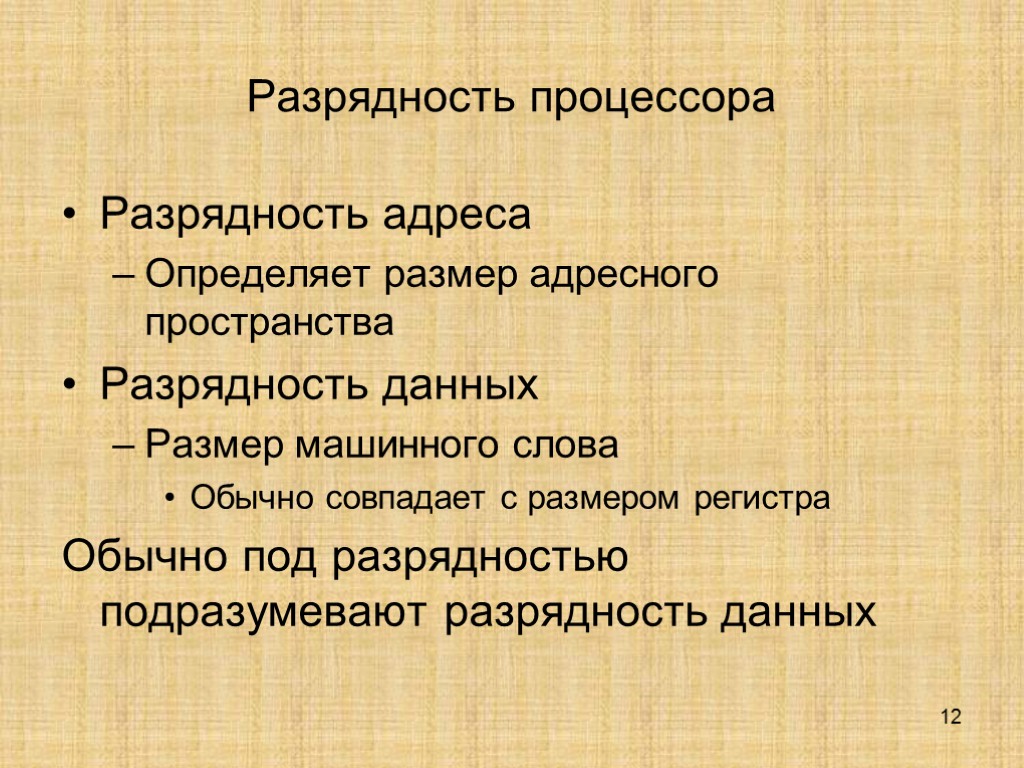

12 Разрядность процессора Разрядность адреса Определяет размер адресного пространства Разрядность данных Размер машинного слова Обычно совпадает с размером регистра Обычно под разрядностью подразумевают разрядность данных

12 Разрядность процессора Разрядность адреса Определяет размер адресного пространства Разрядность данных Размер машинного слова Обычно совпадает с размером регистра Обычно под разрядностью подразумевают разрядность данных

13 2. Команды микропроцессора Далее мы будем изучать синтаксис машинных команд и семантику их выполнения центральным процессором. Для удобства команды будем записывать так, как это принято в языке Ассемблер

13 2. Команды микропроцессора Далее мы будем изучать синтаксис машинных команд и семантику их выполнения центральным процессором. Для удобства команды будем записывать так, как это принято в языке Ассемблер

14 Система команд может быть классифицирована по трем основным признакам - длина команды или число занимаемых ею байтов, функциональное назначение способ адресации.

14 Система команд может быть классифицирована по трем основным признакам - длина команды или число занимаемых ею байтов, функциональное назначение способ адресации.

15 Для МП 8086 команда занимает от одного до шести байтов. Первым байтом команды всегда является код операции, например код команды INT XXh равен CD(HEX).

15 Для МП 8086 команда занимает от одного до шести байтов. Первым байтом команды всегда является код операции, например код команды INT XXh равен CD(HEX).

16 По функциональному признаку инструкции можно разбить на пять больших групп: 1) команды пересылки данных, 2) арифметические команды, 3) логические команды, 4) команды переходов, 5) команды управления.

16 По функциональному признаку инструкции можно разбить на пять больших групп: 1) команды пересылки данных, 2) арифметические команды, 3) логические команды, 4) команды переходов, 5) команды управления.

17 Существует пять основных способов адресации: регистровая, непосредственная, прямая, косвенная стековая.

17 Существует пять основных способов адресации: регистровая, непосредственная, прямая, косвенная стековая.

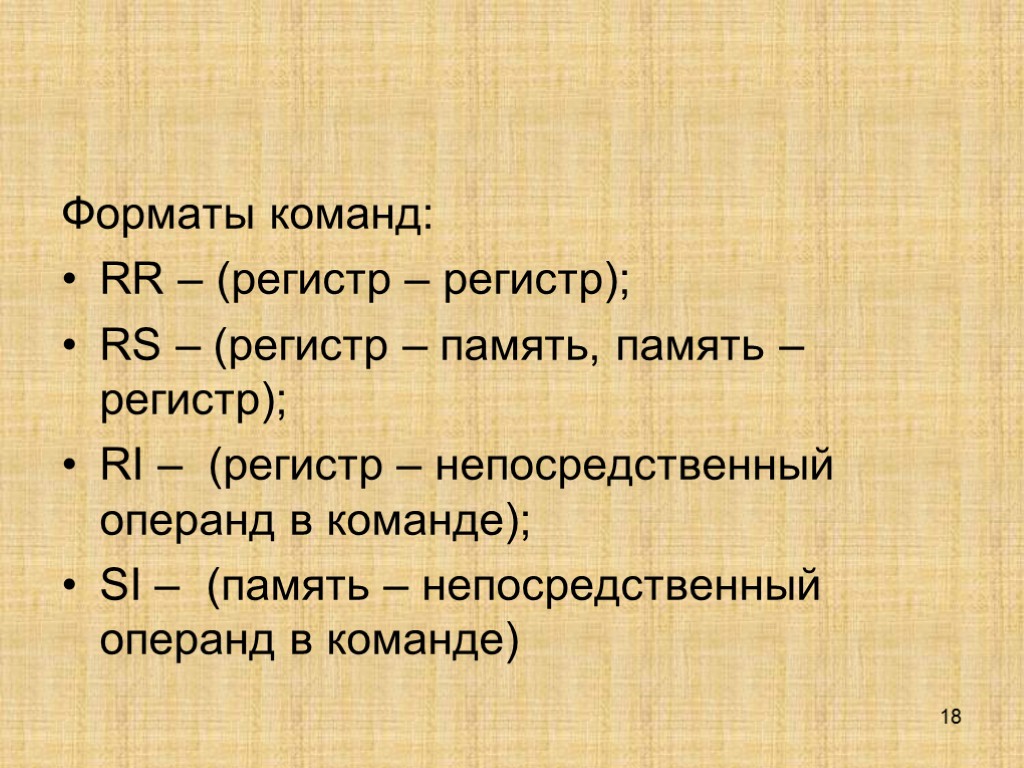

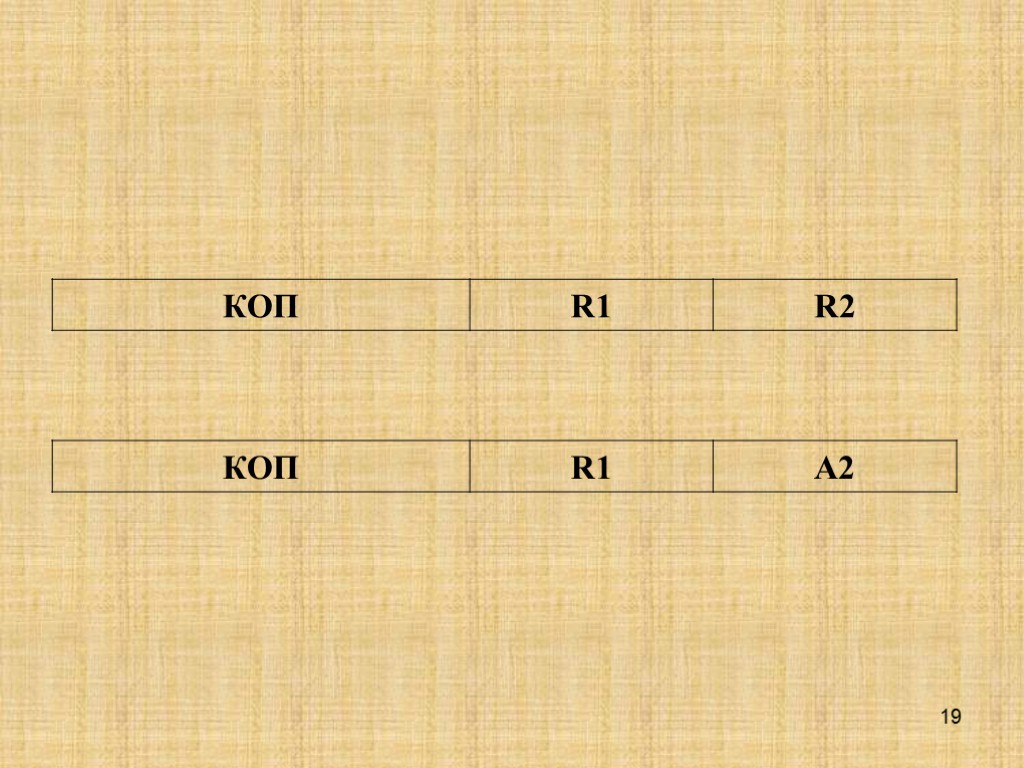

18 Форматы команд: RR – (регистр – регистр); RS – (регистр – память, память – регистр); RI – (регистр – непосредственный операнд в команде); SI – (память – непосредственный операнд в команде)

18 Форматы команд: RR – (регистр – регистр); RS – (регистр – память, память – регистр); RI – (регистр – непосредственный операнд в команде); SI – (память – непосредственный операнд в команде)

19

19

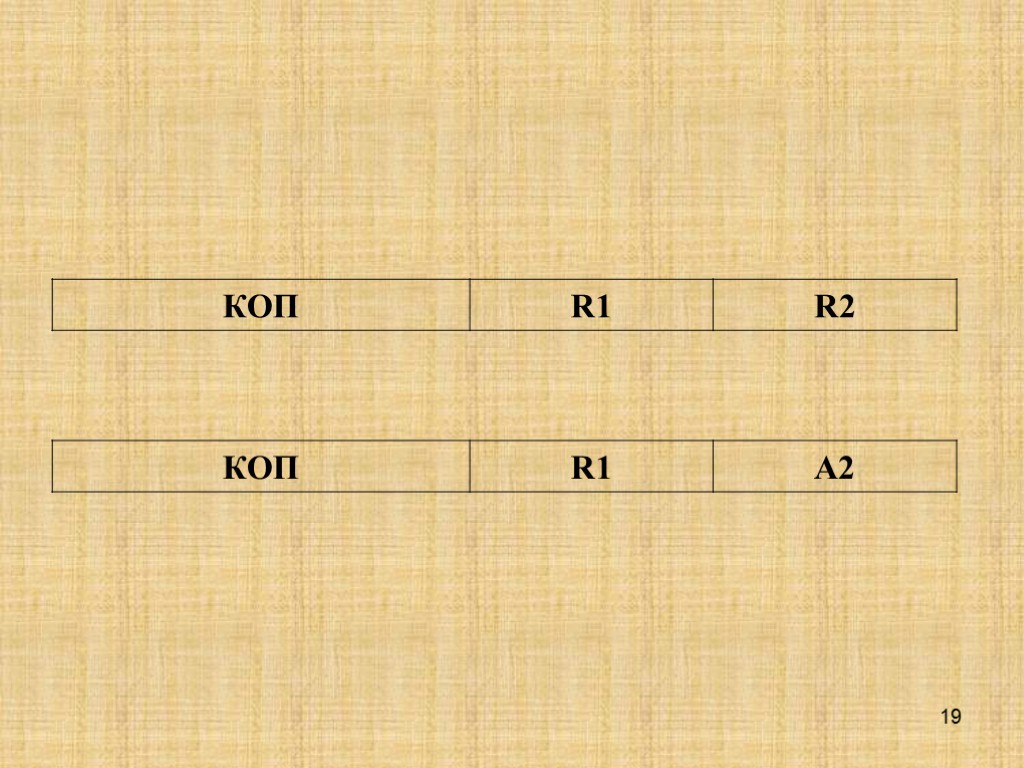

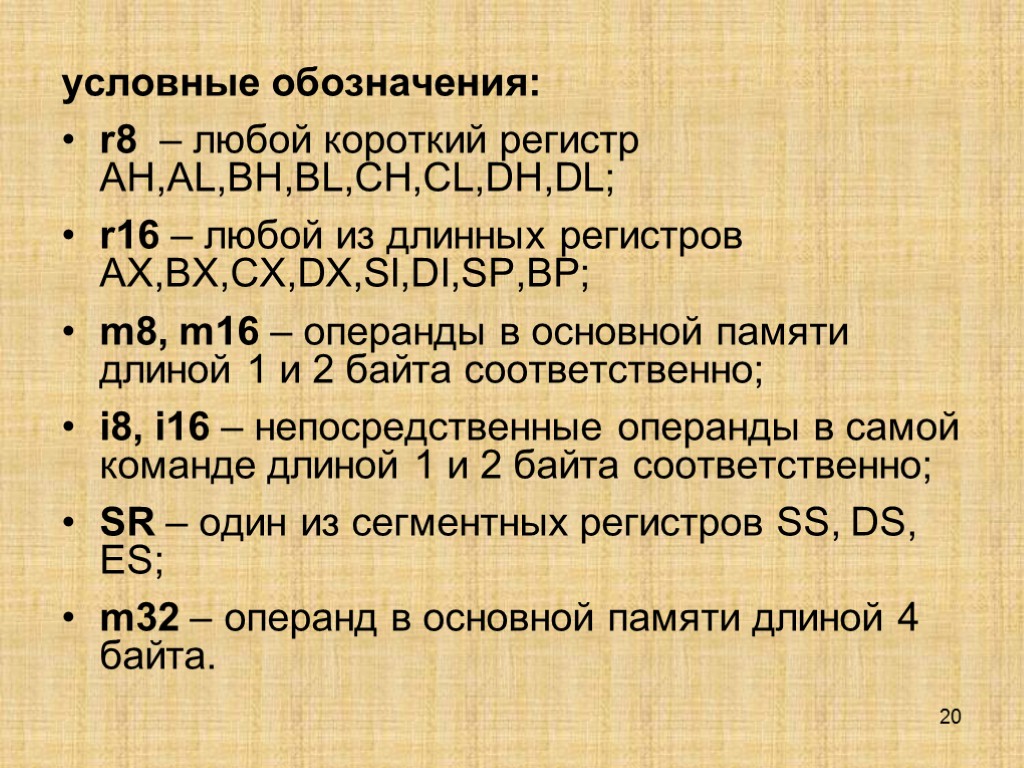

20 условные обозначения: r8 – любой короткий регистр AH,AL,BH,BL,CH,CL,DH,DL; r16 – любой из длинных регистров AX,BX,CX,DX,SI,DI,SP,BP; m8, m16 – операнды в основной памяти длиной 1 и 2 байта соответственно; i8, i16 – непосредственные операнды в самой команде длиной 1 и 2 байта соответственно; SR – один из сегментных регистров SS, DS, ES; m32 – операнд в основной памяти длиной 4 байта.

20 условные обозначения: r8 – любой короткий регистр AH,AL,BH,BL,CH,CL,DH,DL; r16 – любой из длинных регистров AX,BX,CX,DX,SI,DI,SP,BP; m8, m16 – операнды в основной памяти длиной 1 и 2 байта соответственно; i8, i16 – непосредственные операнды в самой команде длиной 1 и 2 байта соответственно; SR – один из сегментных регистров SS, DS, ES; m32 – операнд в основной памяти длиной 4 байта.

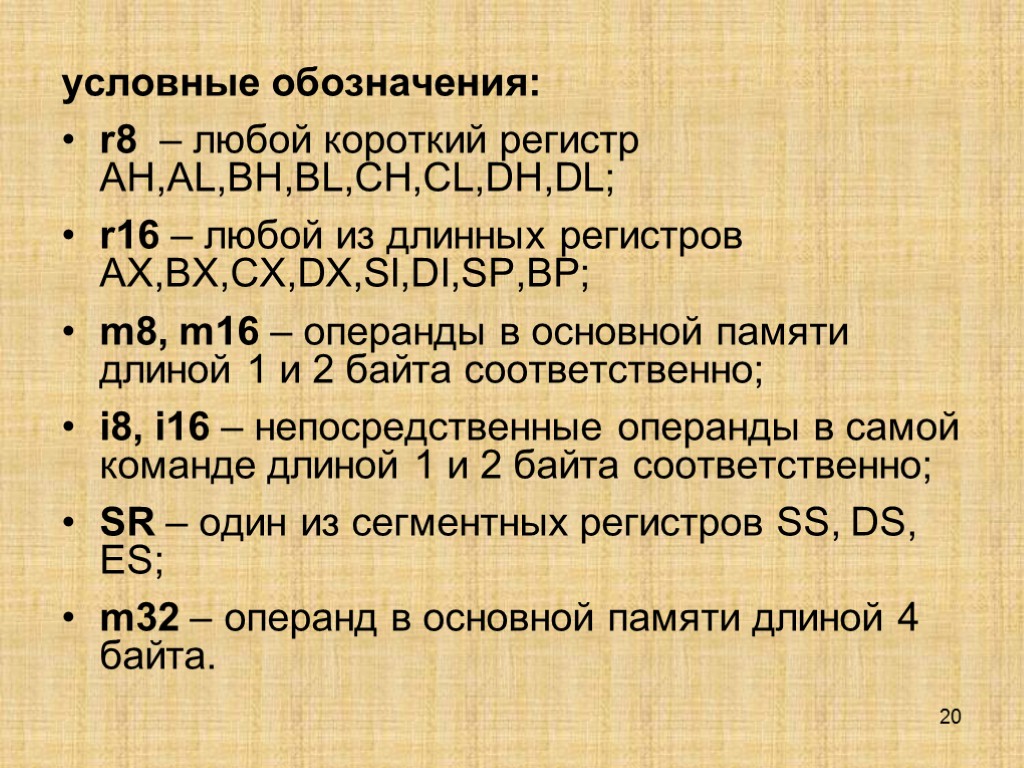

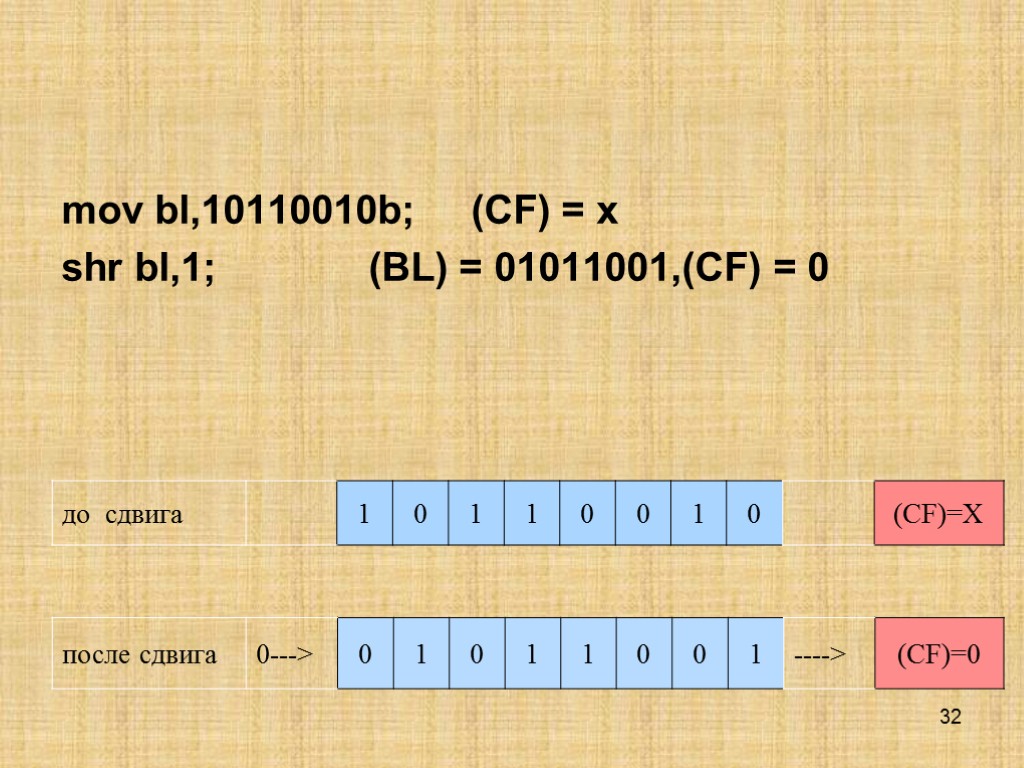

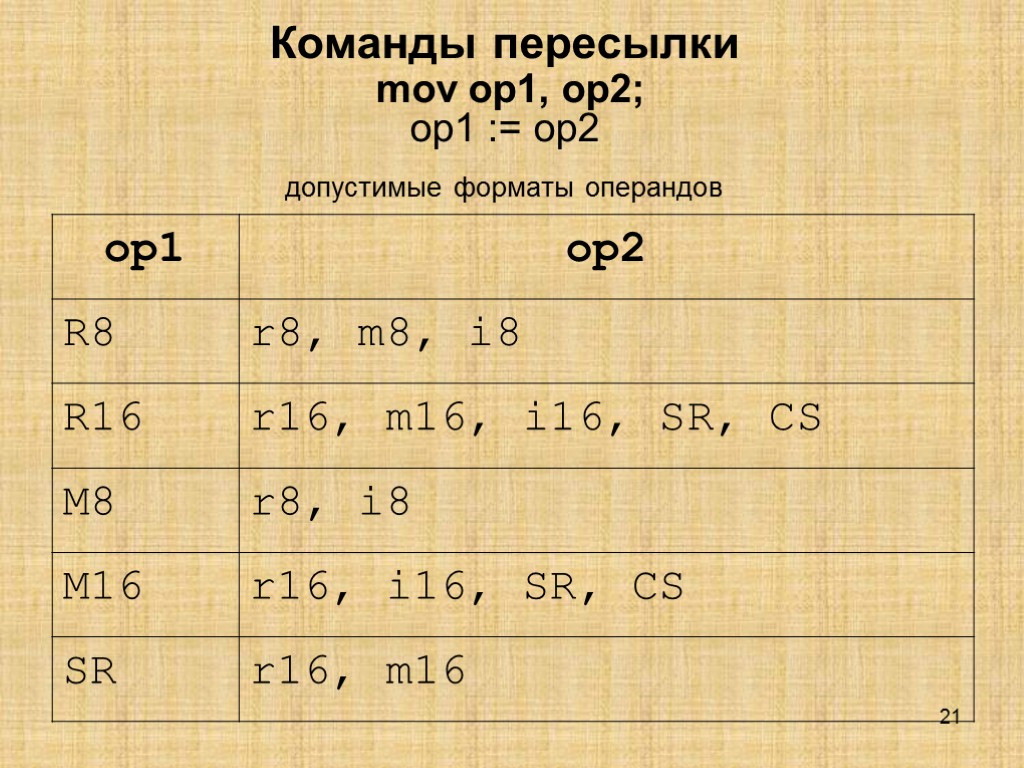

21 Команды пересылки mov op1, op2; op1 := op2 допустимые форматы операндов

21 Команды пересылки mov op1, op2; op1 := op2 допустимые форматы операндов

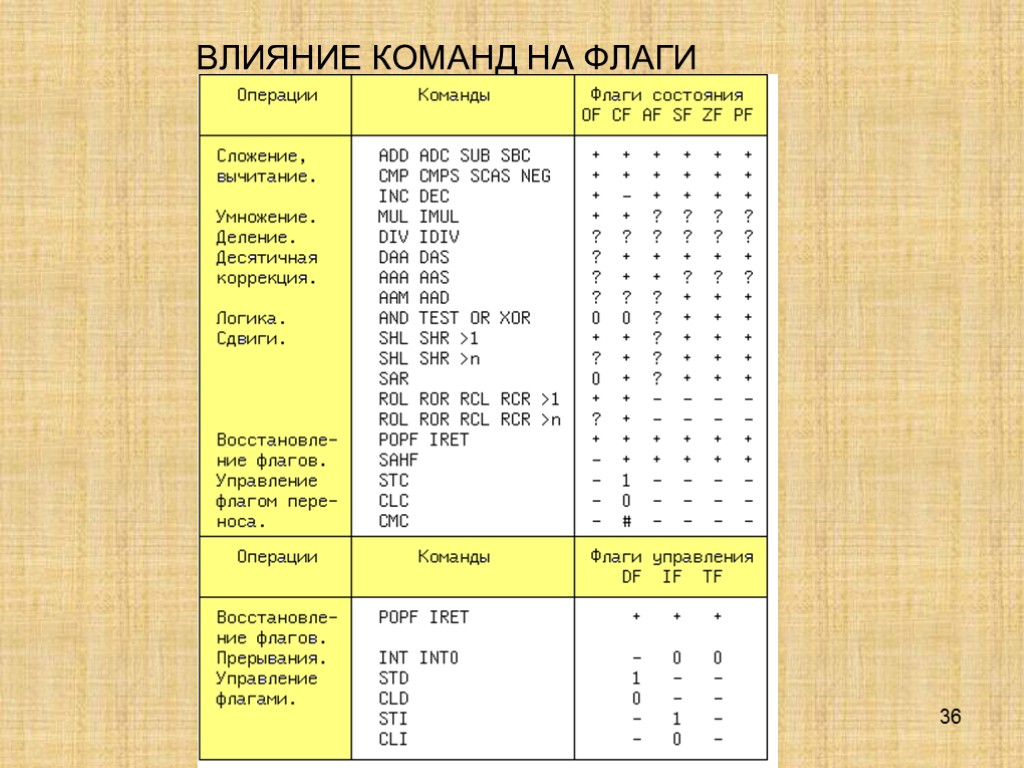

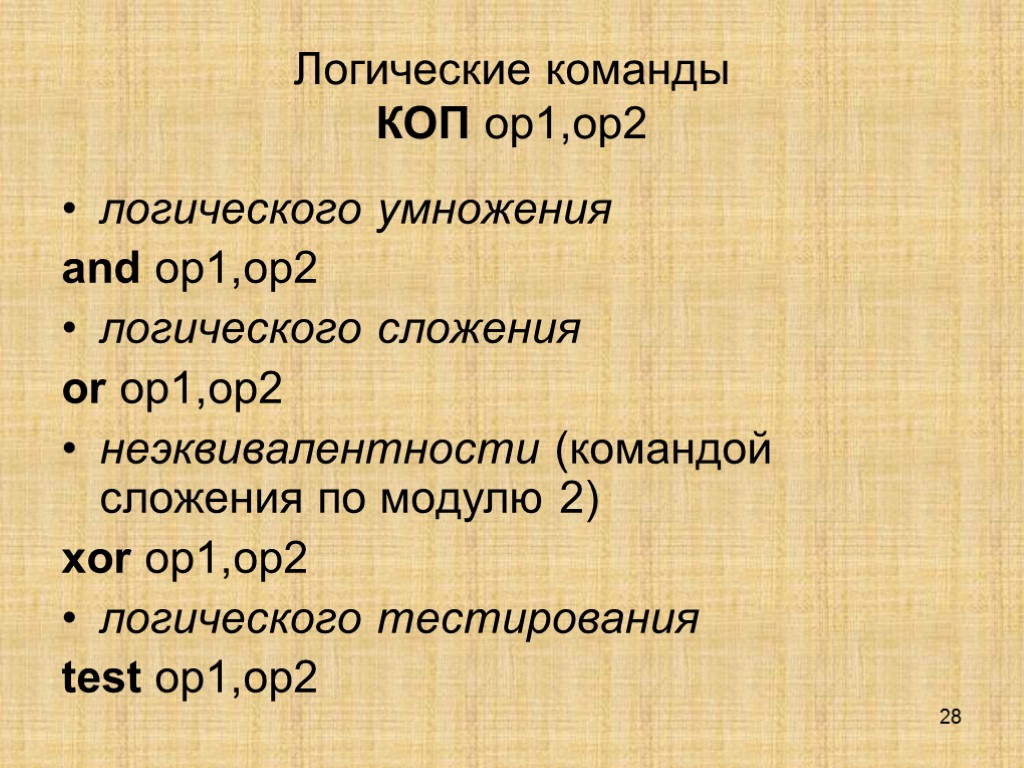

![>22 mov al,ch; (al) <-- (ch). mov cx,dx; mov bh,[mems];содержимое ячейки памяти с символическим >22 mov al,ch; (al) <-- (ch). mov cx,dx; mov bh,[mems];содержимое ячейки памяти с символическим](https://present5.com/customparser/19688283_133450166 --- ak_modul1_tema2_11-12.ppt/slide_22.jpg) 22 mov al,ch; (al) <-- (ch). mov cx,dx; mov bh,[mems];содержимое ячейки памяти с символическим адресом mems переслать в регистр BH. Можно: mov bh,mems. mov al,[bx];переслать в аккумулятор содержимое ячейки памяти с адресом находящимся в регистре BX . mov bx,OFFSET src; поместить в BX смещение адреса ячейки памяти SRC, в текущем сегменте. mov al,table[bx]; загрузить в аккумулятор элемент таблицы байтов с символическим адресом первого элемента table и отстоящий от этого элемента на (bx) байтов. Другие варианты: mov al,[table + bx] или mov al,table + bx.

22 mov al,ch; (al) <-- (ch). mov cx,dx; mov bh,[mems];содержимое ячейки памяти с символическим адресом mems переслать в регистр BH. Можно: mov bh,mems. mov al,[bx];переслать в аккумулятор содержимое ячейки памяти с адресом находящимся в регистре BX . mov bx,OFFSET src; поместить в BX смещение адреса ячейки памяти SRC, в текущем сегменте. mov al,table[bx]; загрузить в аккумулятор элемент таблицы байтов с символическим адресом первого элемента table и отстоящий от этого элемента на (bx) байтов. Другие варианты: mov al,[table + bx] или mov al,table + bx.

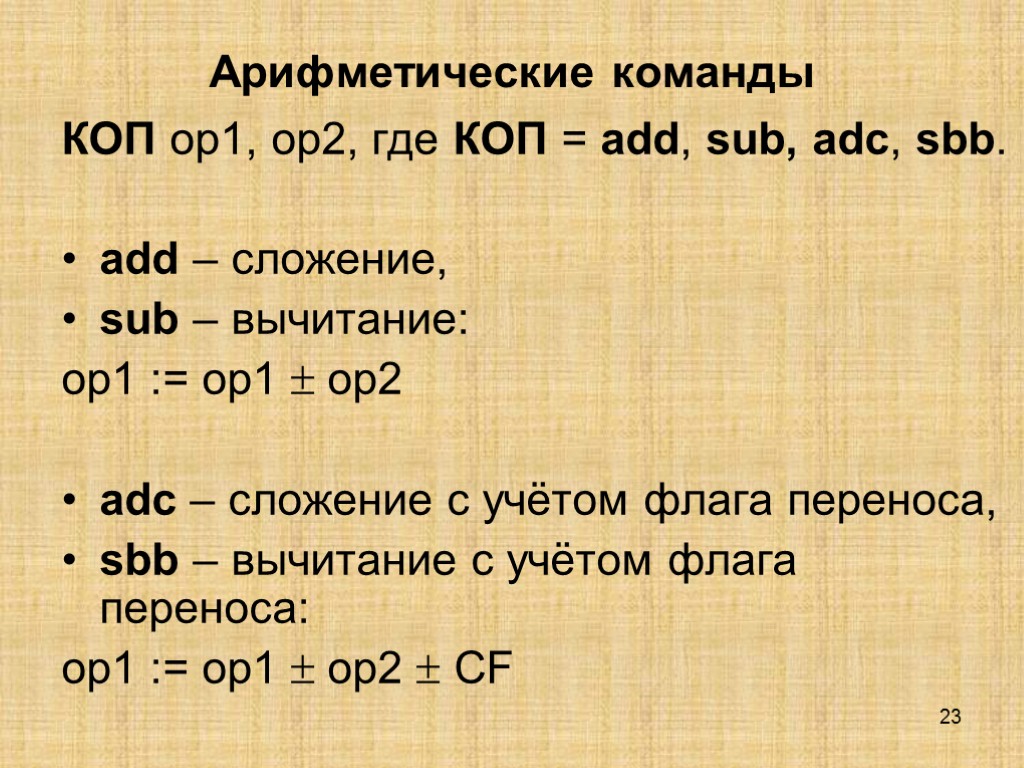

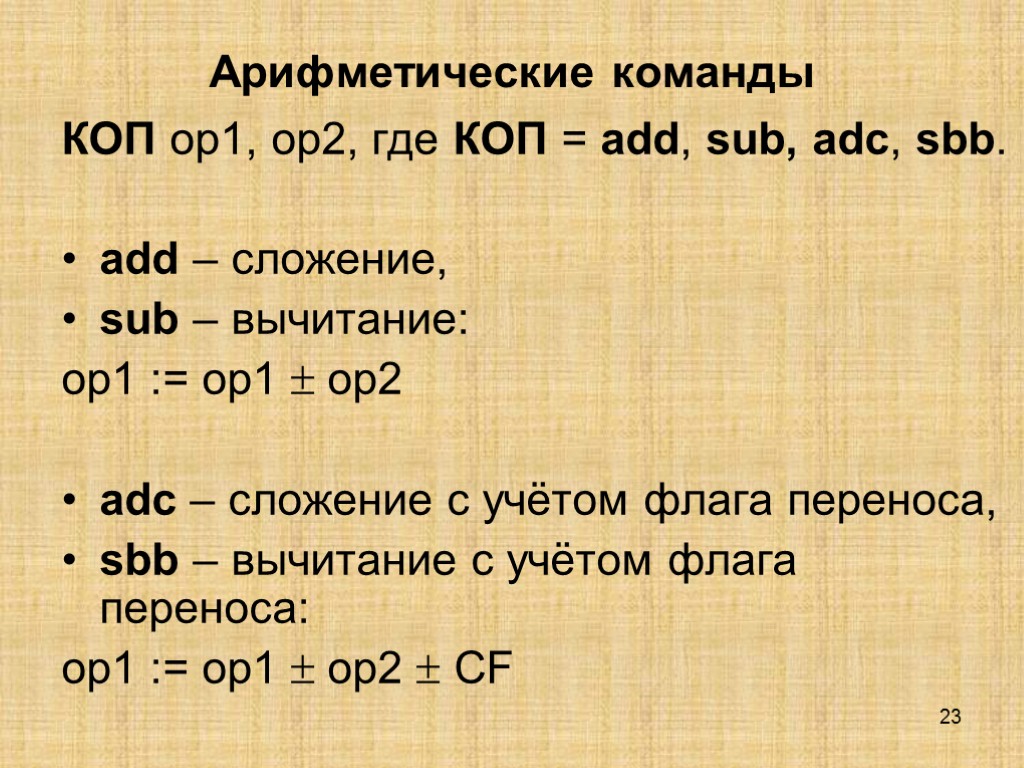

23 Арифметические команды КОП op1, op2, где КОП = add, sub, adc, sbb. add – сложение, sub – вычитание: op1 := op1 op2 adc – сложение с учётом флага переноса, sbb – вычитание с учётом флага переноса: op1 := op1 op2 CF

23 Арифметические команды КОП op1, op2, где КОП = add, sub, adc, sbb. add – сложение, sub – вычитание: op1 := op1 op2 adc – сложение с учётом флага переноса, sbb – вычитание с учётом флага переноса: op1 := op1 op2 CF

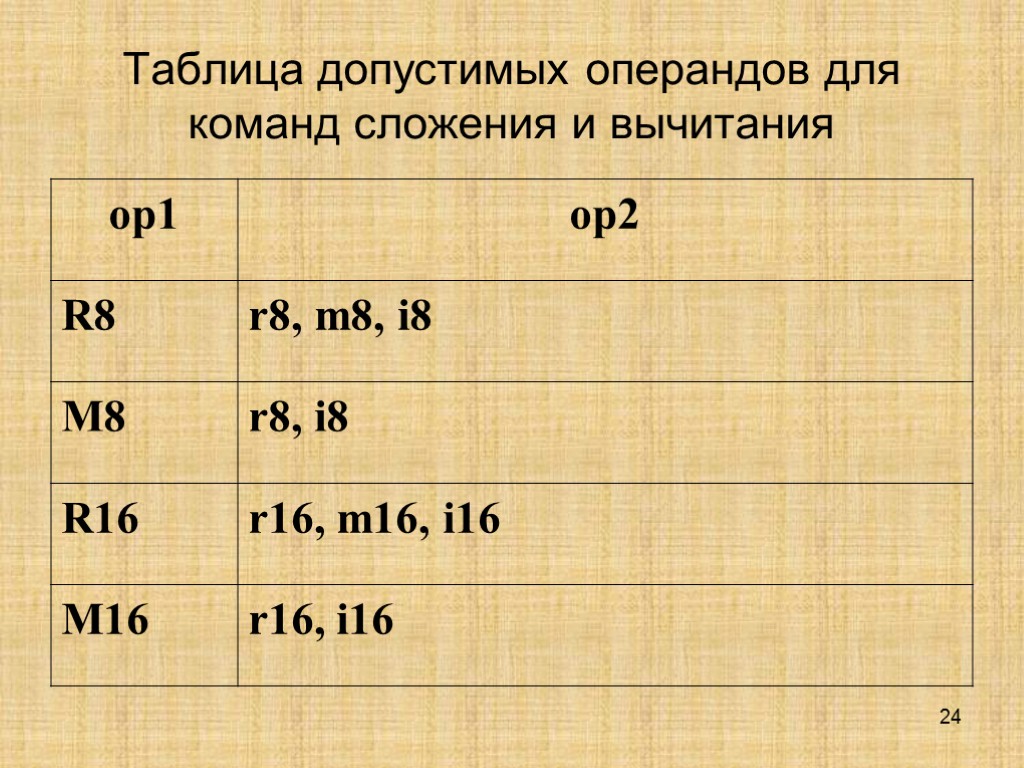

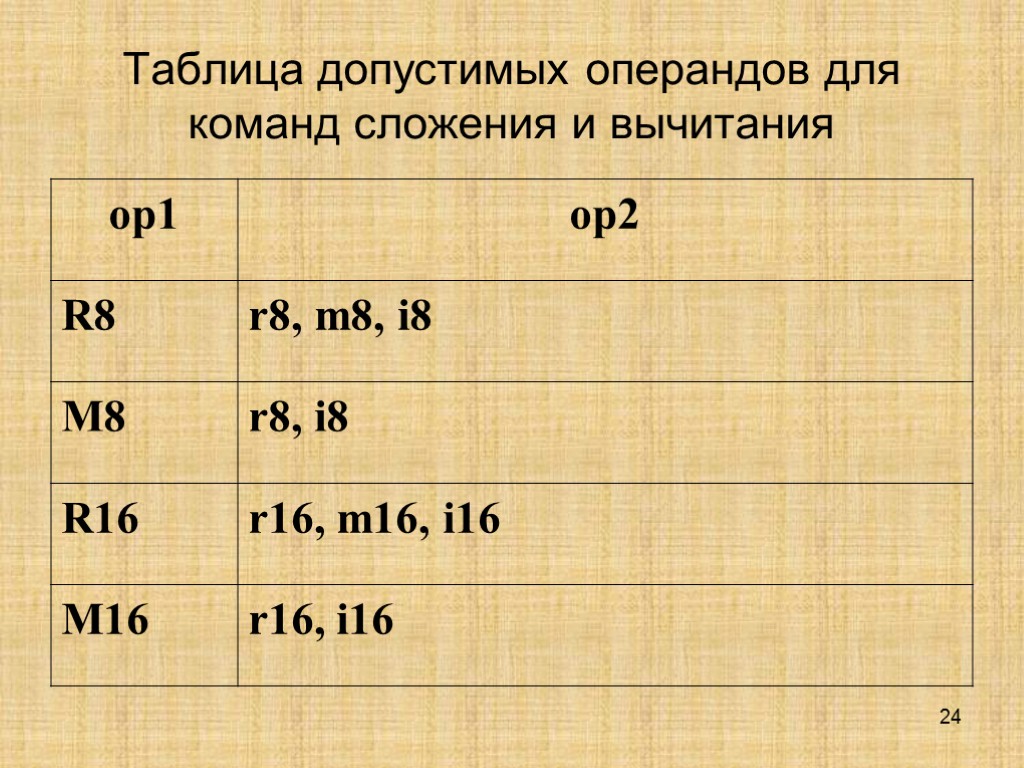

24 Таблица допустимых операндов для команд сложения и вычитания

24 Таблица допустимых операндов для команд сложения и вычитания

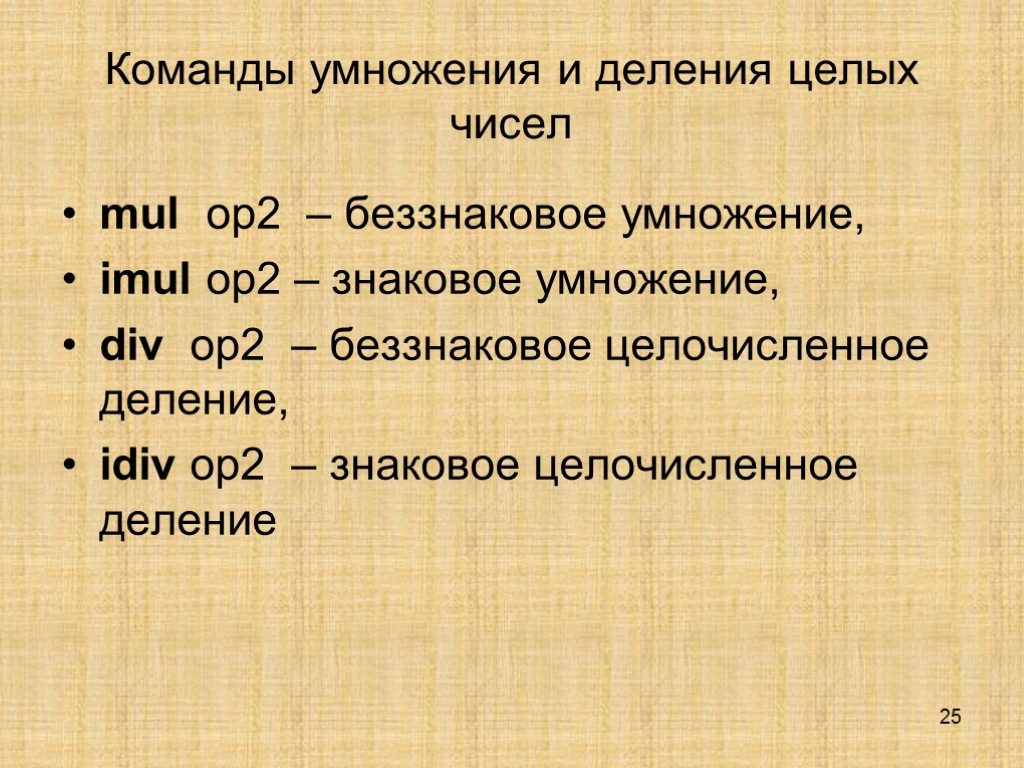

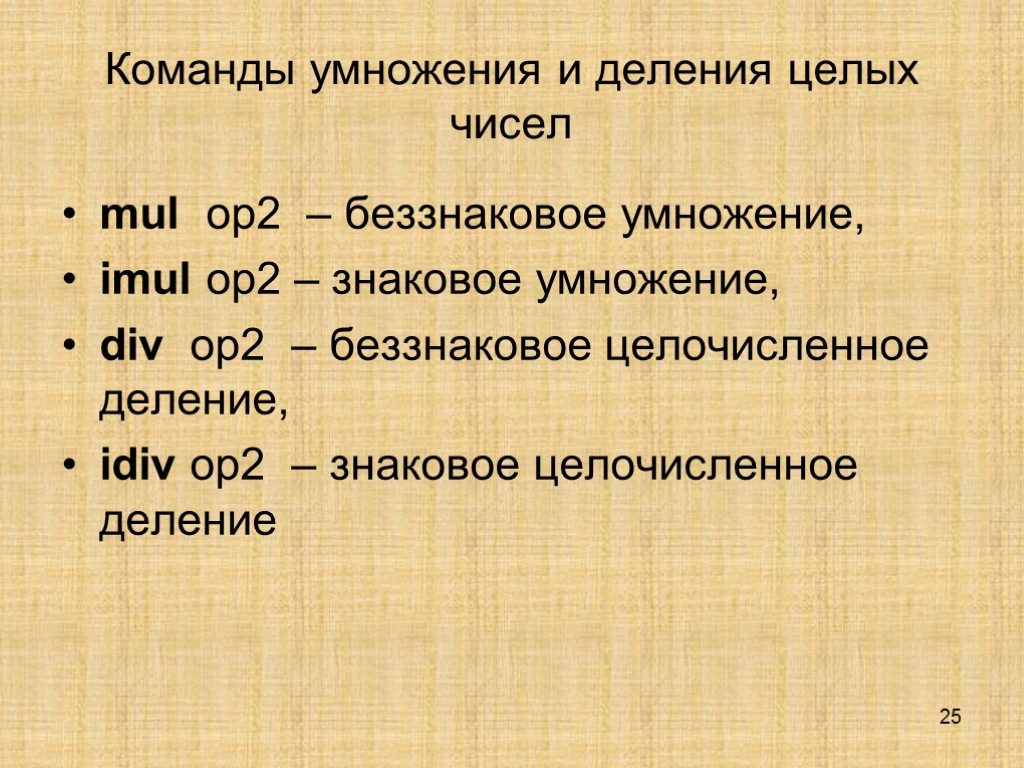

25 Команды умножения и деления целых чисел mul op2 – беззнаковое умножение, imul op2 – знаковое умножение, div op2 – беззнаковое целочисленное деление, idiv op2 – знаковое целочисленное деление

25 Команды умножения и деления целых чисел mul op2 – беззнаковое умножение, imul op2 – знаковое умножение, div op2 – беззнаковое целочисленное деление, idiv op2 – знаковое целочисленное деление

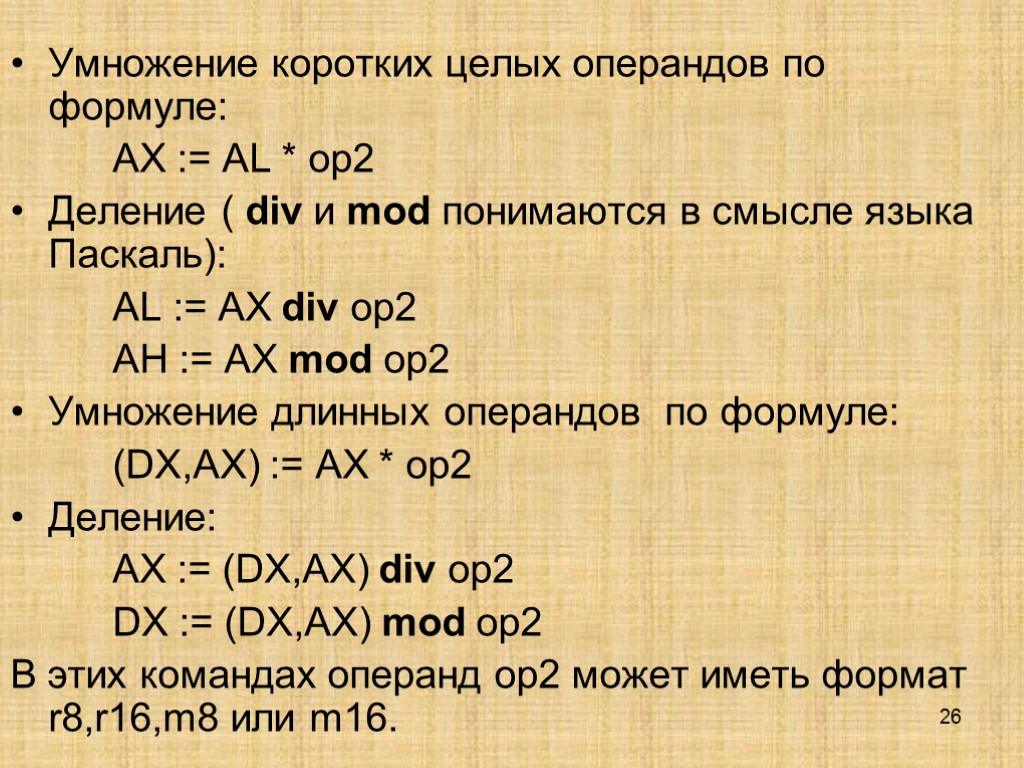

26 Умножение коротких целых операндов по формуле: AX := AL * op2 Деление ( div и mod понимаются в смысле языка Паскаль): AL := AX div op2 AH := AX mod op2 Умножение длинных операндов по формуле: (DX,AX) := AX * op2 Деление: AX := (DX,AX) div op2 DX := (DX,AX) mod op2 В этих командах операнд op2 может иметь формат r8,r16,m8 или m16.

26 Умножение коротких целых операндов по формуле: AX := AL * op2 Деление ( div и mod понимаются в смысле языка Паскаль): AL := AX div op2 AH := AX mod op2 Умножение длинных операндов по формуле: (DX,AX) := AX * op2 Деление: AX := (DX,AX) div op2 DX := (DX,AX) mod op2 В этих командах операнд op2 может иметь формат r8,r16,m8 или m16.

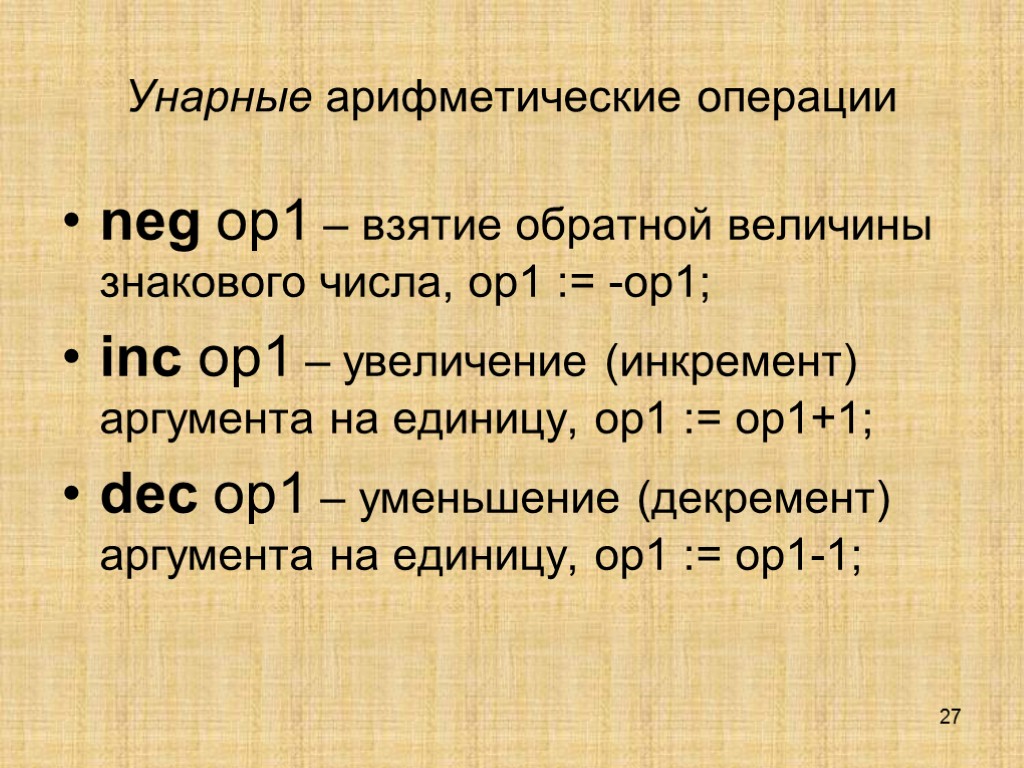

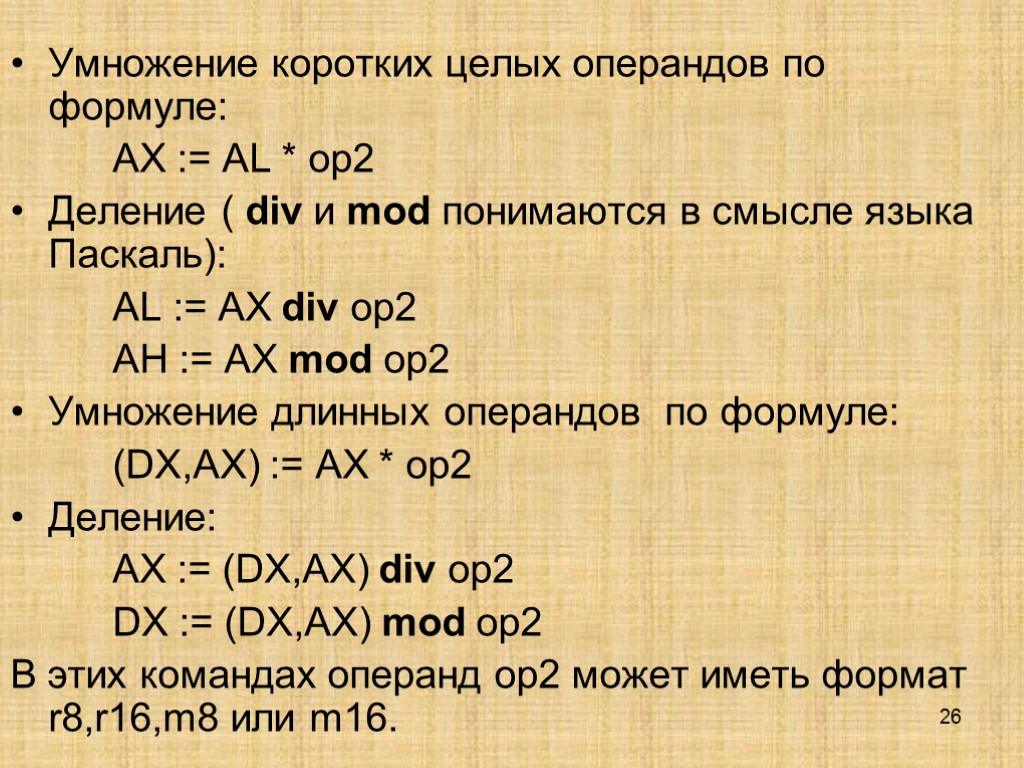

27 Унарные арифметические операции neg op1 – взятие обратной величины знакового числа, op1 := -op1; inc op1 – увеличение (инкремент) аргумента на единицу, op1 := op1+1; dec op1 – уменьшение (декремент) аргумента на единицу, op1 := op1-1;

27 Унарные арифметические операции neg op1 – взятие обратной величины знакового числа, op1 := -op1; inc op1 – увеличение (инкремент) аргумента на единицу, op1 := op1+1; dec op1 – уменьшение (декремент) аргумента на единицу, op1 := op1-1;

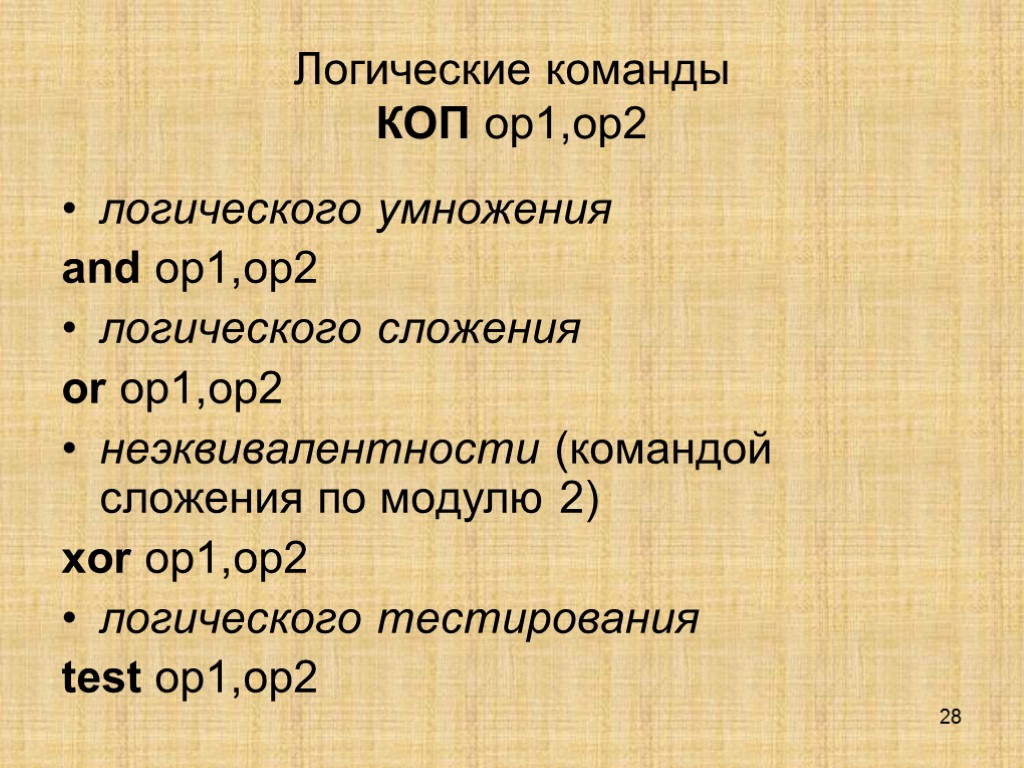

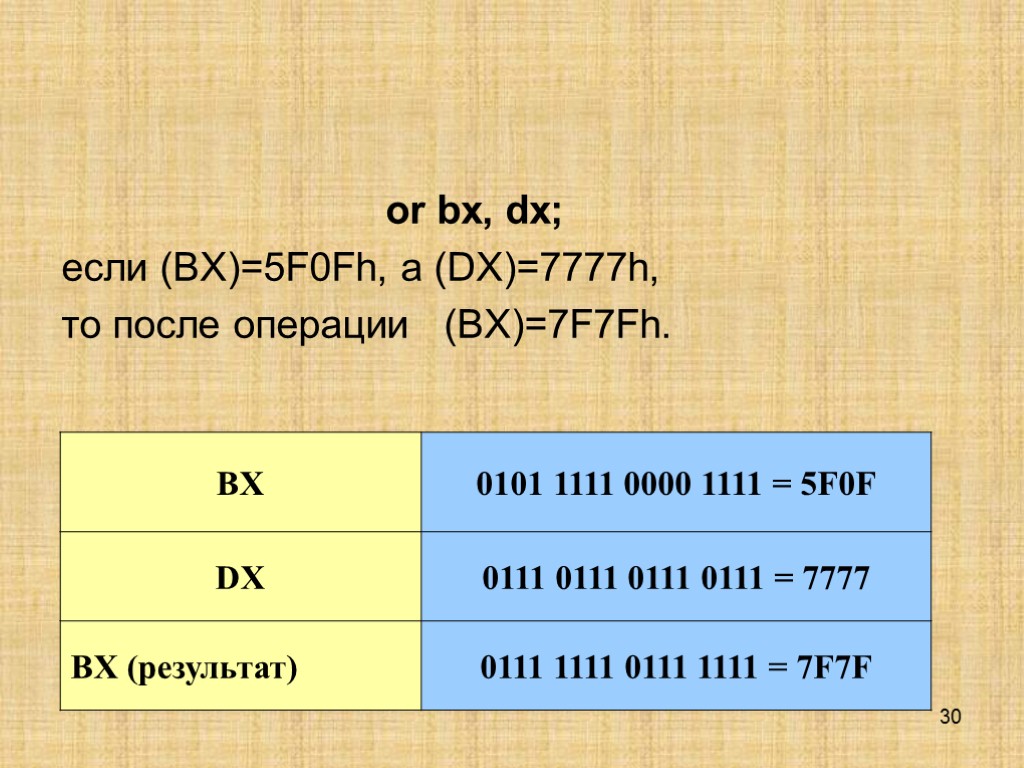

28 Логические команды КОП op1,op2 логического умножения and op1,op2 логического сложения or op1,op2 неэквивалентности (командой сложения по модулю 2) xor op1,op2 логического тестирования test op1,op2

28 Логические команды КОП op1,op2 логического умножения and op1,op2 логического сложения or op1,op2 неэквивалентности (командой сложения по модулю 2) xor op1,op2 логического тестирования test op1,op2

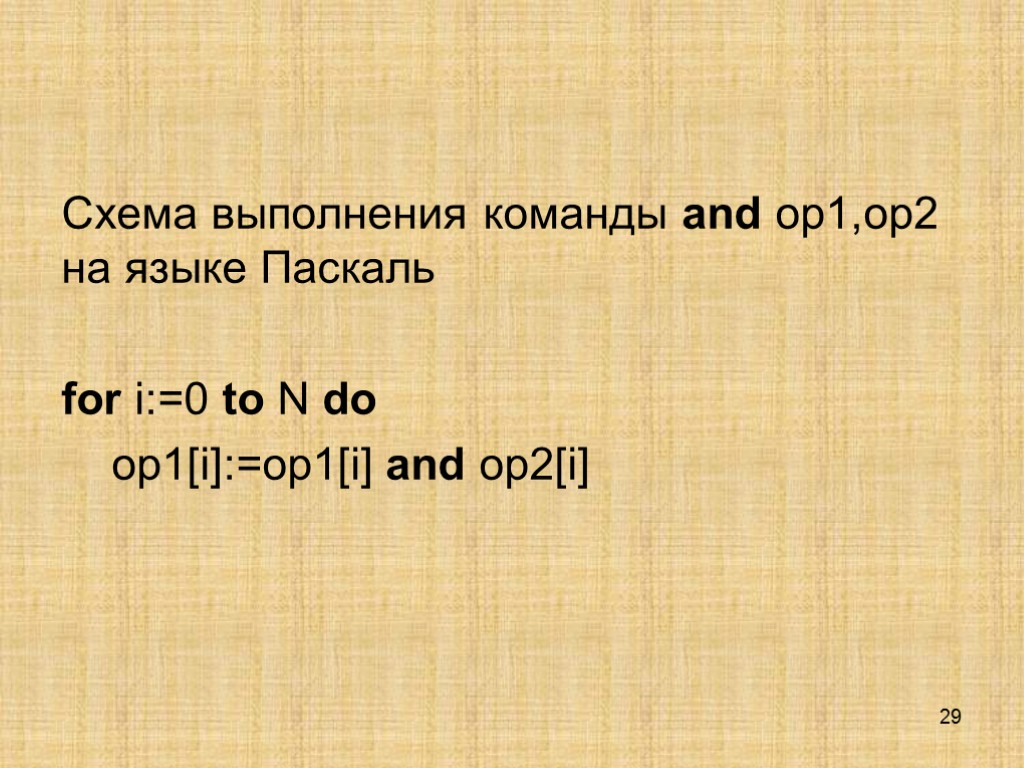

29 Схема выполнения команды and op1,op2 на языке Паскаль for i:=0 to N do op1[i]:=op1[i] and op2[i]

29 Схема выполнения команды and op1,op2 на языке Паскаль for i:=0 to N do op1[i]:=op1[i] and op2[i]

30 or bx, dx; если (BX)=5F0Fh, а (DX)=7777h, то после операции (BX)=7F7Fh.

30 or bx, dx; если (BX)=5F0Fh, а (DX)=7777h, то после операции (BX)=7F7Fh.

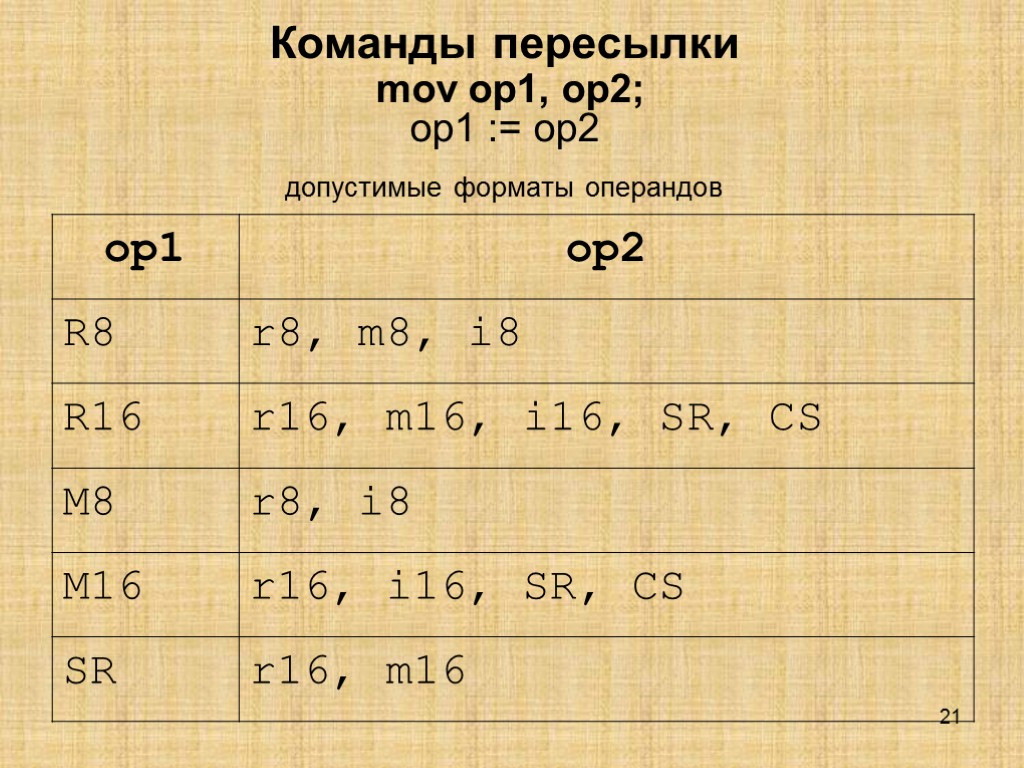

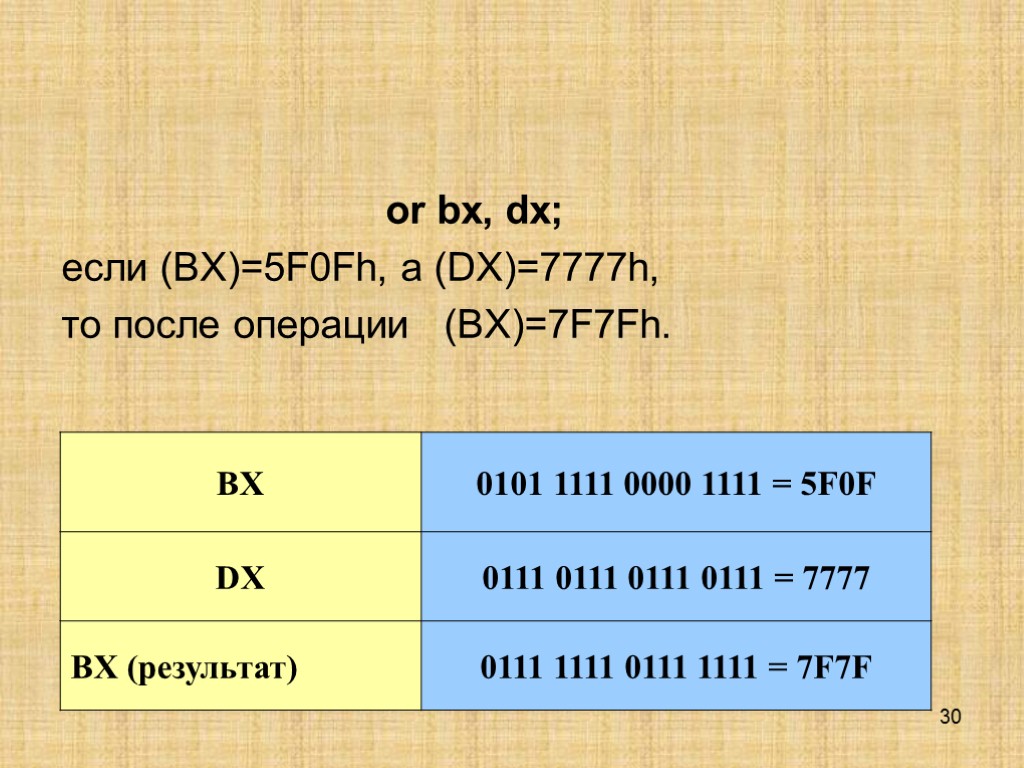

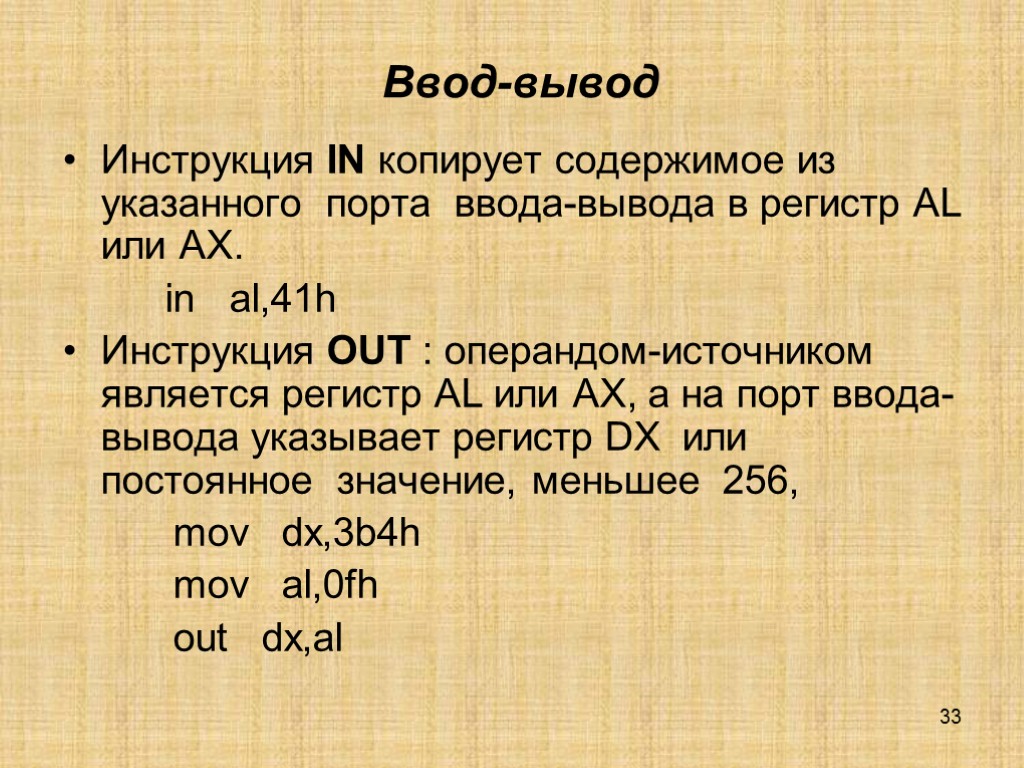

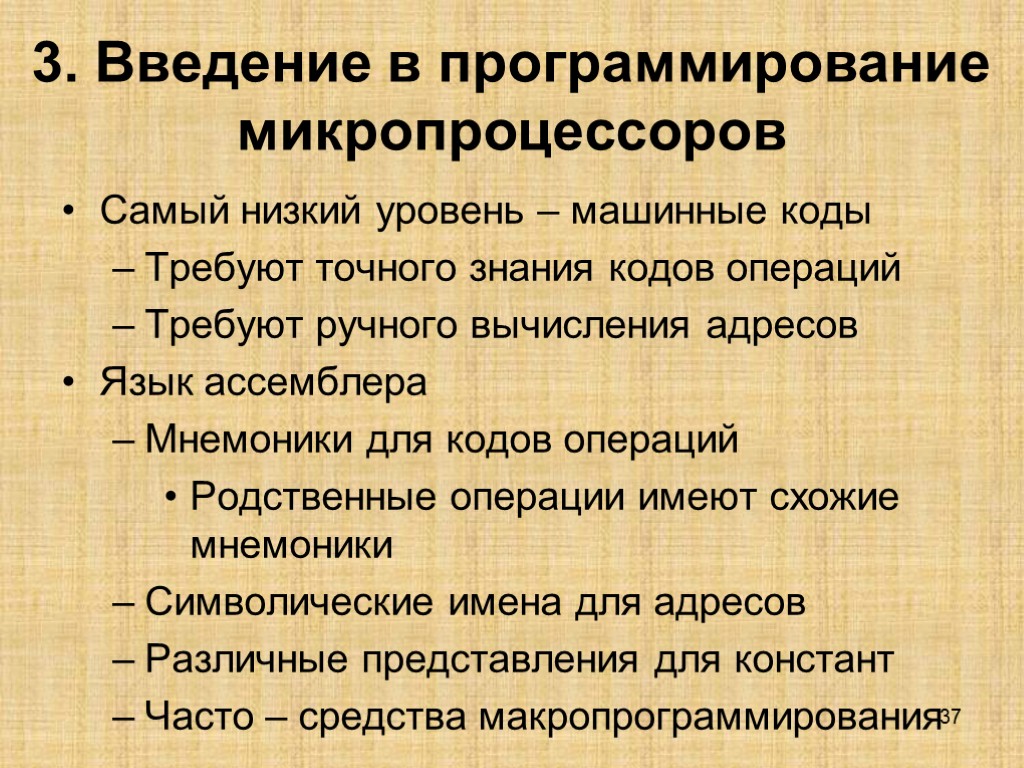

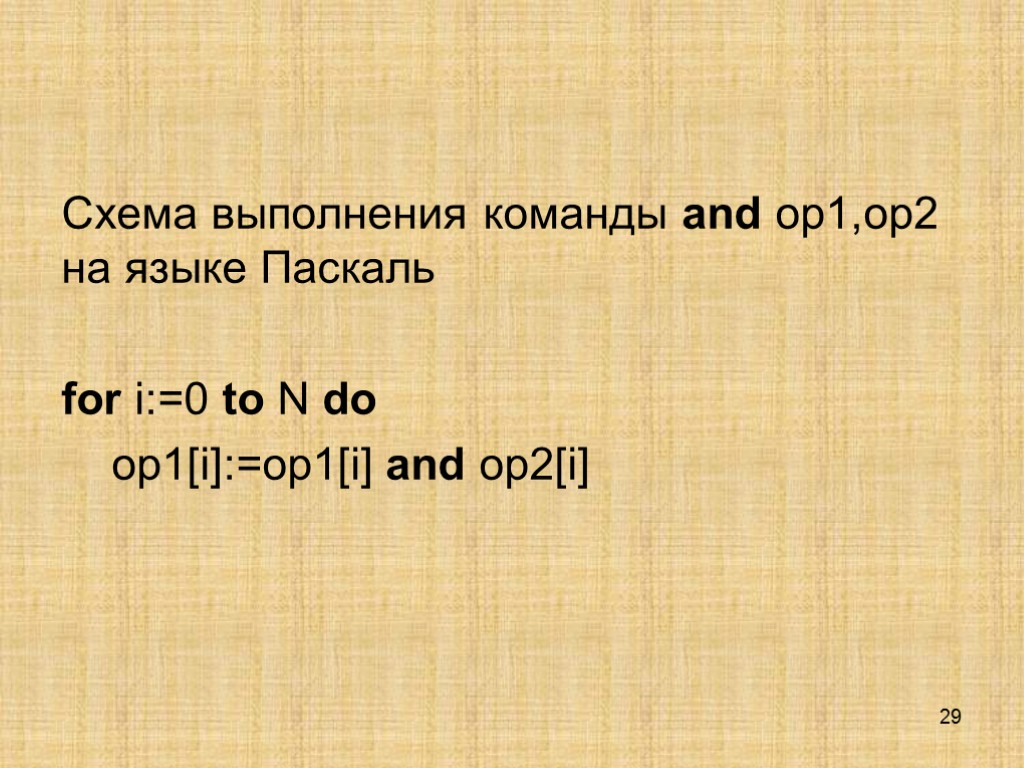

![>31 Команды сдвига КОП op1,1 или КОП op1,cl shl op1,1 CF:=op1[N]; for i:=N downto >31 Команды сдвига КОП op1,1 или КОП op1,cl shl op1,1 CF:=op1[N]; for i:=N downto](https://present5.com/customparser/19688283_133450166 --- ak_modul1_tema2_11-12.ppt/slide_31.jpg) 31 Команды сдвига КОП op1,1 или КОП op1,cl shl op1,1 CF:=op1[N]; for i:=N downto 1 do op1[i]:=op1[i-1]; op1[0]:=0 shr op1,1 CF:=op1[0]; for i:=0 to N-1 do op1[i]:=op1[i+1]; op1[N]:=0 rol op1,1 выполняется по правилу shl op1,1; op1[0]:=CF

31 Команды сдвига КОП op1,1 или КОП op1,cl shl op1,1 CF:=op1[N]; for i:=N downto 1 do op1[i]:=op1[i-1]; op1[0]:=0 shr op1,1 CF:=op1[0]; for i:=0 to N-1 do op1[i]:=op1[i+1]; op1[N]:=0 rol op1,1 выполняется по правилу shl op1,1; op1[0]:=CF

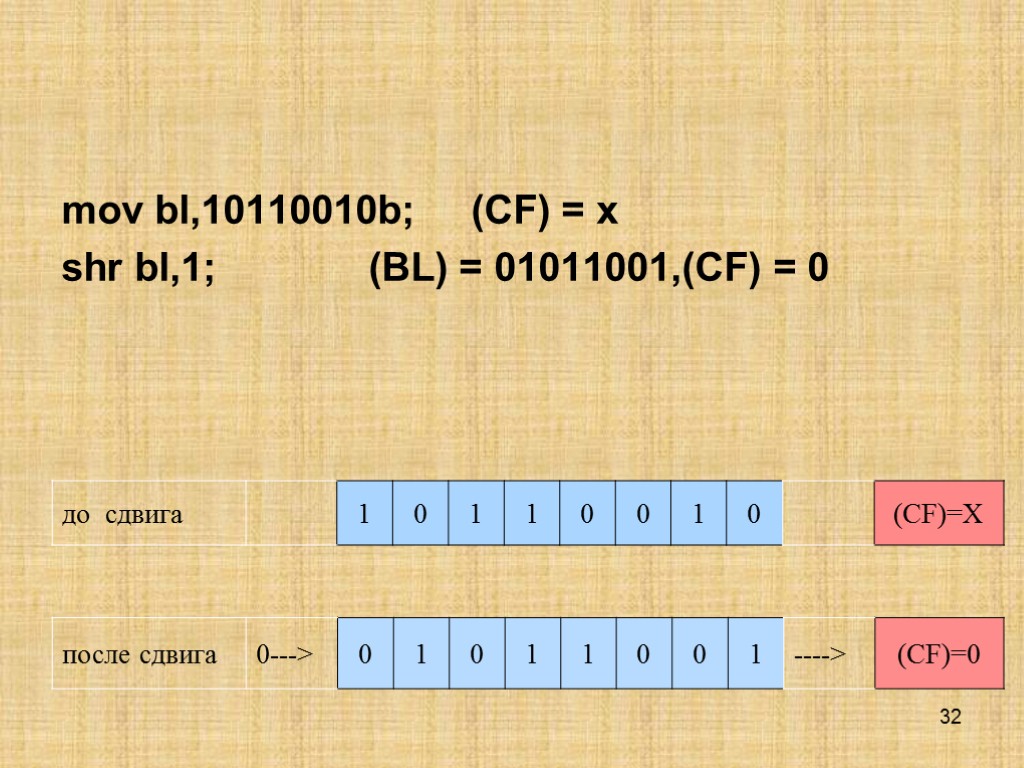

32 mov bl,10110010b; (CF) = x shr bl,1; (BL) = 01011001,(CF) = 0

32 mov bl,10110010b; (CF) = x shr bl,1; (BL) = 01011001,(CF) = 0

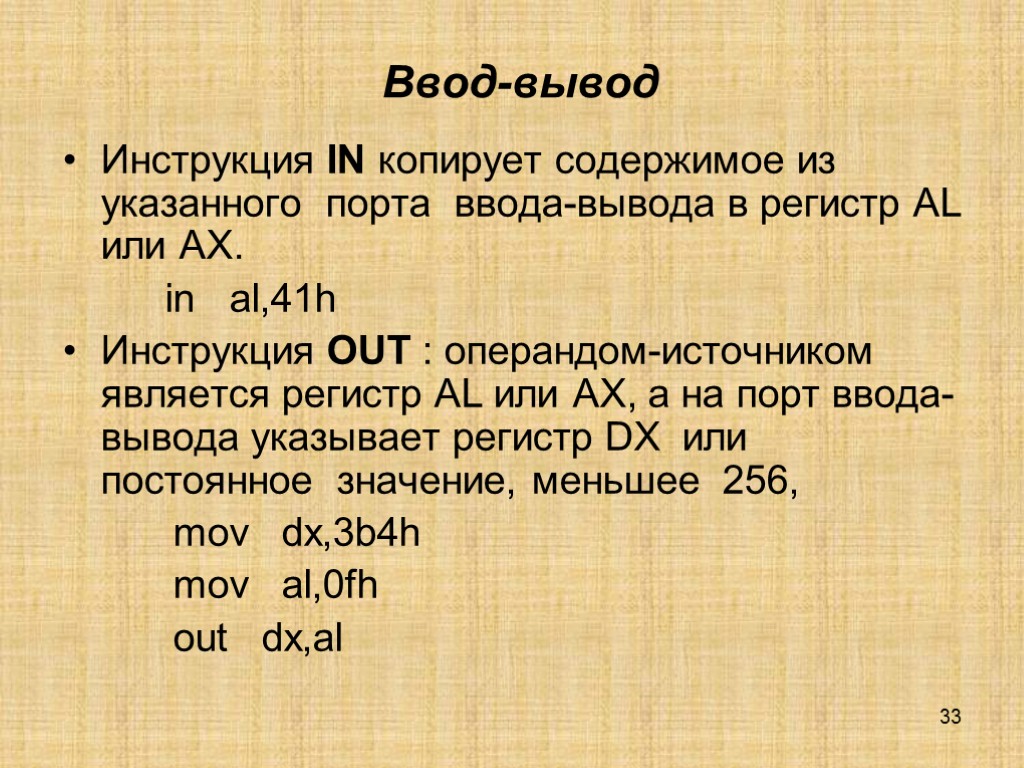

33 Ввод-вывод Инструкция IN копирует содержимое из указанного порта ввода-вывода в регистр AL или AX. in al,41h Инструкция OUT : операндом-источником является регистр AL или AX, а на порт ввода-вывода указывает регистр DX или постоянное значение, меньшее 256, mov dx,3b4h mov al,0fh out dx,al

33 Ввод-вывод Инструкция IN копирует содержимое из указанного порта ввода-вывода в регистр AL или AX. in al,41h Инструкция OUT : операндом-источником является регистр AL или AX, а на порт ввода-вывода указывает регистр DX или постоянное значение, меньшее 256, mov dx,3b4h mov al,0fh out dx,al

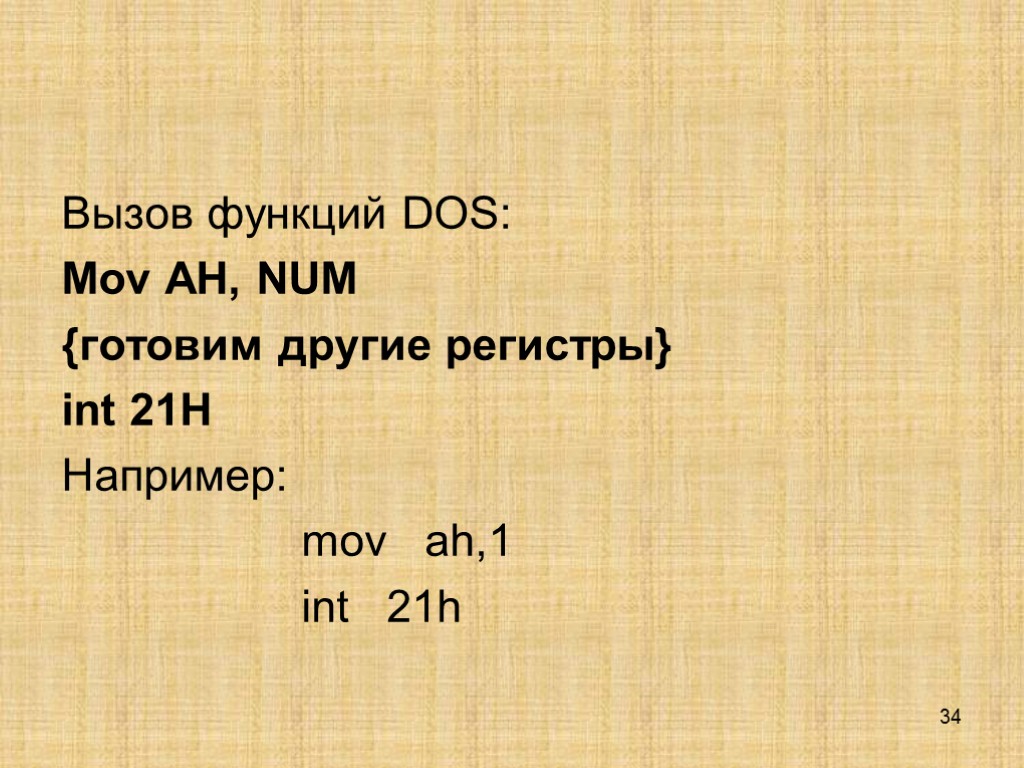

34 Вызов функций DOS: Mov AH, NUM {готовим другие регистры} int 21H Например: mov ah,1 int 21h

34 Вызов функций DOS: Mov AH, NUM {готовим другие регистры} int 21H Например: mov ah,1 int 21h

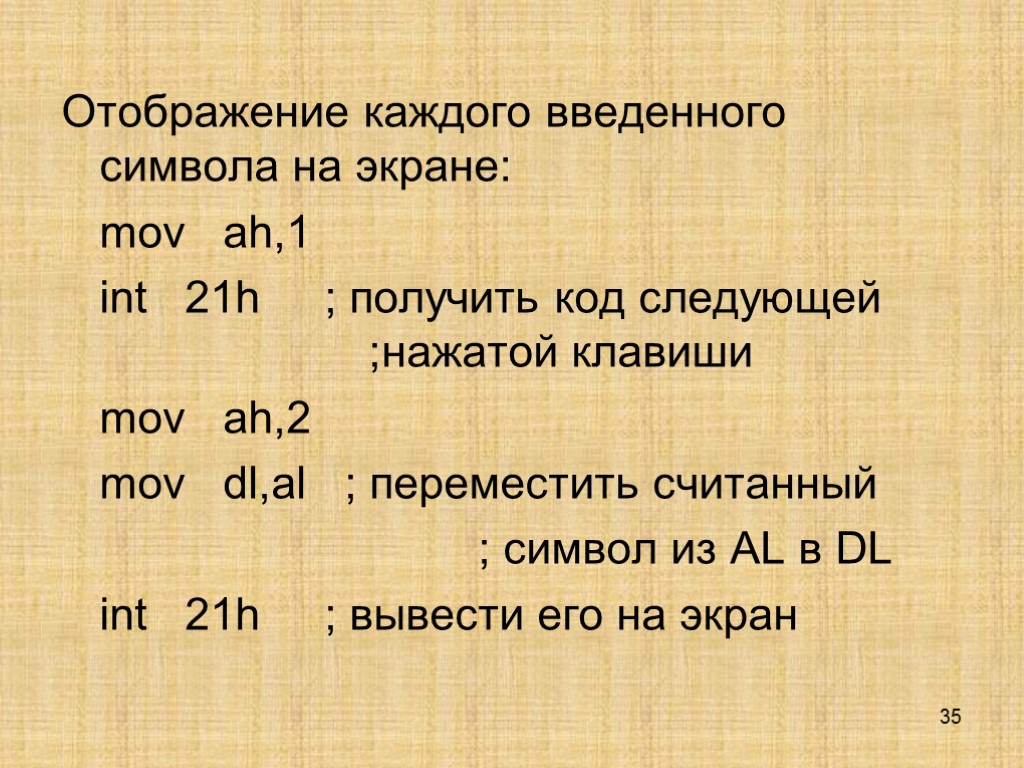

35 Отображение каждого введенного символа на экране: mov ah,1 int 21h ; получить код следующей ;нажатой клавиши mov ah,2 mov dl,al ; переместить считанный ; символ из AL в DL int 21h ; вывести его на экран

35 Отображение каждого введенного символа на экране: mov ah,1 int 21h ; получить код следующей ;нажатой клавиши mov ah,2 mov dl,al ; переместить считанный ; символ из AL в DL int 21h ; вывести его на экран

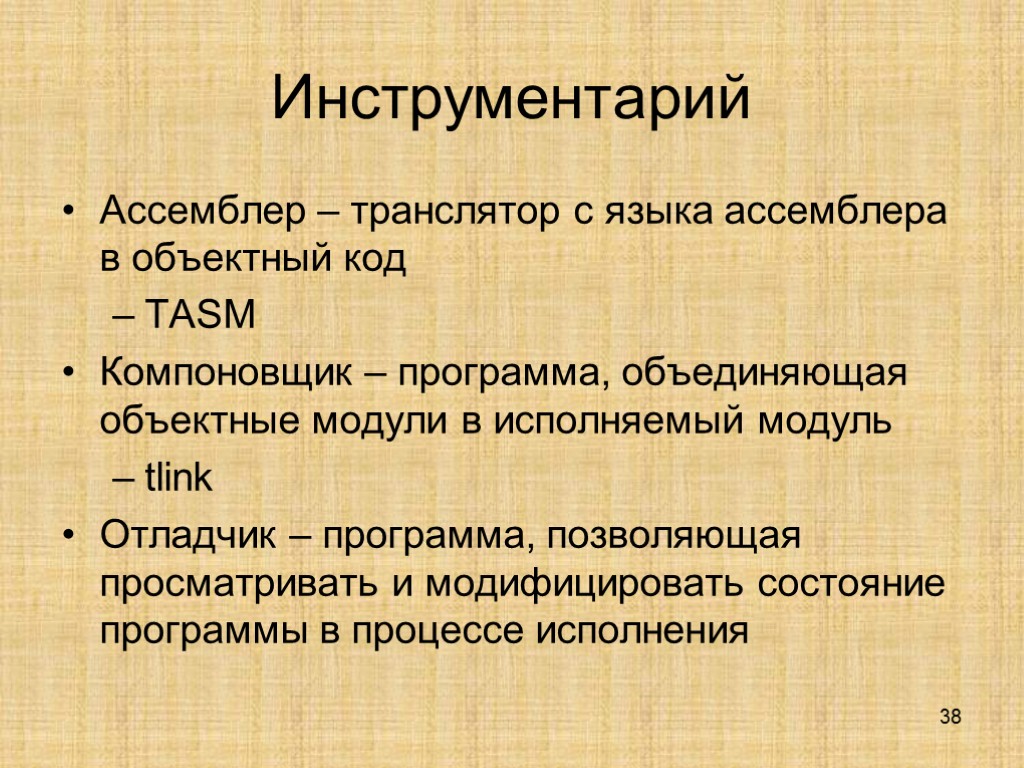

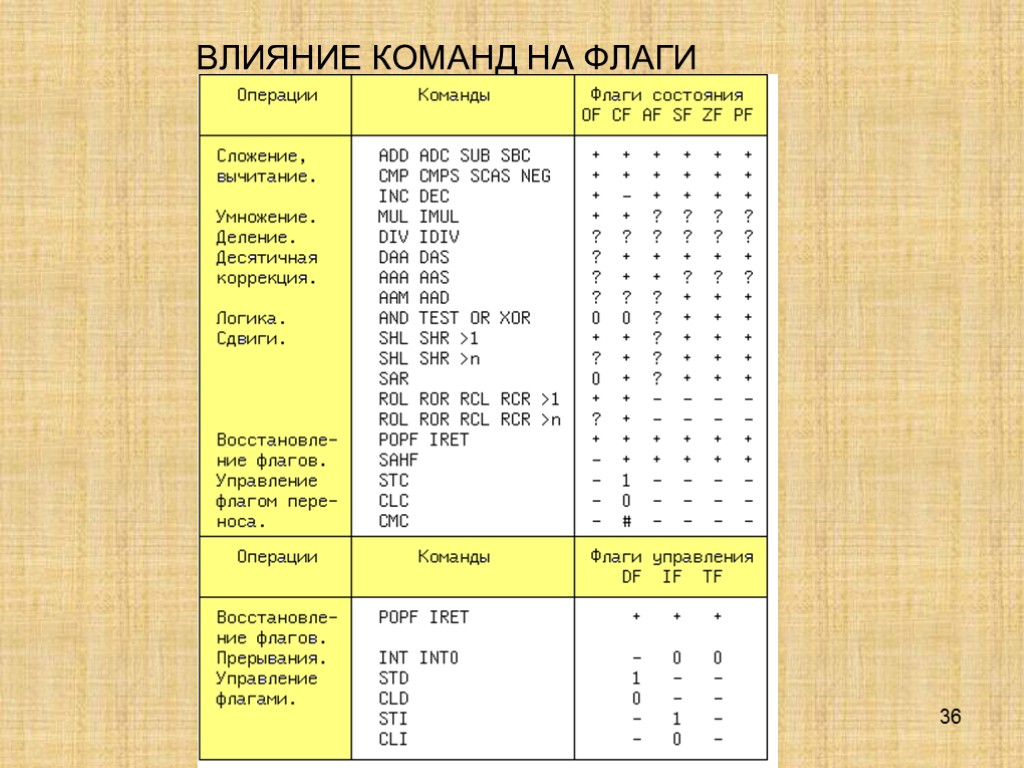

36 ВЛИЯНИЕ КОМАНД НА ФЛАГИ

36 ВЛИЯНИЕ КОМАНД НА ФЛАГИ

37 3. Введение в программирование микропроцессоров Самый низкий уровень – машинные коды Требуют точного знания кодов операций Требуют ручного вычисления адресов Язык ассемблера Мнемоники для кодов операций Родственные операции имеют схожие мнемоники Символические имена для адресов Различные представления для констант Часто – средства макропрограммирования

37 3. Введение в программирование микропроцессоров Самый низкий уровень – машинные коды Требуют точного знания кодов операций Требуют ручного вычисления адресов Язык ассемблера Мнемоники для кодов операций Родственные операции имеют схожие мнемоники Символические имена для адресов Различные представления для констант Часто – средства макропрограммирования

38 Инструментарий Ассемблер – транслятор с языка ассемблера в объектный код TASM Компоновщик – программа, объединяющая объектные модули в исполняемый модуль tlink Отладчик – программа, позволяющая просматривать и модифицировать состояние программы в процессе исполнения

38 Инструментарий Ассемблер – транслятор с языка ассемблера в объектный код TASM Компоновщик – программа, объединяющая объектные модули в исполняемый модуль tlink Отладчик – программа, позволяющая просматривать и модифицировать состояние программы в процессе исполнения