1a5a90b01310d8529d941d30713e20aa.ppt

- Количество слайдов: 47

07/10/07 1 Forward Vertex Detector Status: R&D: Scientific and Technical Resources • Technical Design Overview • Design status • R&D • Cost and schedule • Scientific Resources and Manpower • Issues and Concerns D. M. Lee, LANL

07/10/07 1 Forward Vertex Detector Status: R&D: Scientific and Technical Resources • Technical Design Overview • Design status • R&D • Cost and schedule • Scientific Resources and Manpower • Issues and Concerns D. M. Lee, LANL

07/10/07 2 Forward Vertex Detector Technical Design – Specifications • Cover the Muon Spectrometer Acceptance – both Arms (10 -35 deg) • Full Azimuthal coverage – hermetic • DCA resolution < 200 µm at 5 Ge. V • ≥ 3 space points / track • Maximum Radiation Length < 2. 4% • Survive 10 year integrated dose = 200 k Rad • Low Occupancy in Au – Au Central < 10. 0% • Co-exist with barrel VTX • Compatible with PHENIX DAQ D. M. Lee, LANL

07/10/07 2 Forward Vertex Detector Technical Design – Specifications • Cover the Muon Spectrometer Acceptance – both Arms (10 -35 deg) • Full Azimuthal coverage – hermetic • DCA resolution < 200 µm at 5 Ge. V • ≥ 3 space points / track • Maximum Radiation Length < 2. 4% • Survive 10 year integrated dose = 200 k Rad • Low Occupancy in Au – Au Central < 10. 0% • Co-exist with barrel VTX • Compatible with PHENIX DAQ D. M. Lee, LANL

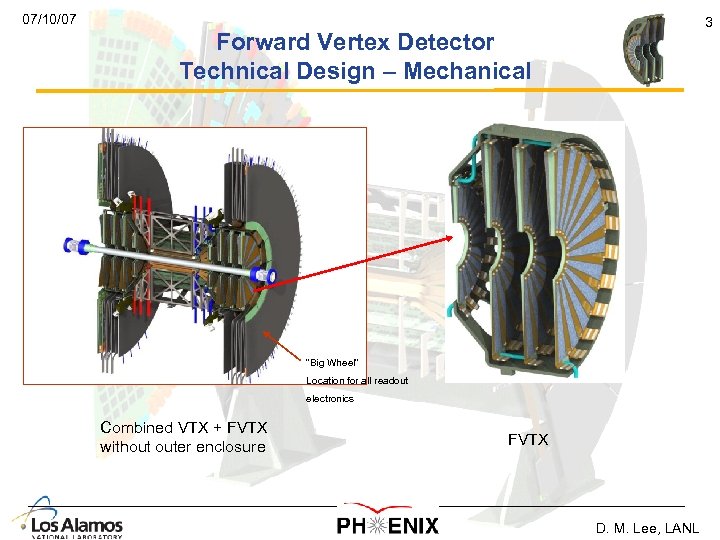

07/10/07 3 Forward Vertex Detector Technical Design – Mechanical “Big Wheel” Location for all readout electronics Combined VTX + FVTX without outer enclosure FVTX D. M. Lee, LANL

07/10/07 3 Forward Vertex Detector Technical Design – Mechanical “Big Wheel” Location for all readout electronics Combined VTX + FVTX without outer enclosure FVTX D. M. Lee, LANL

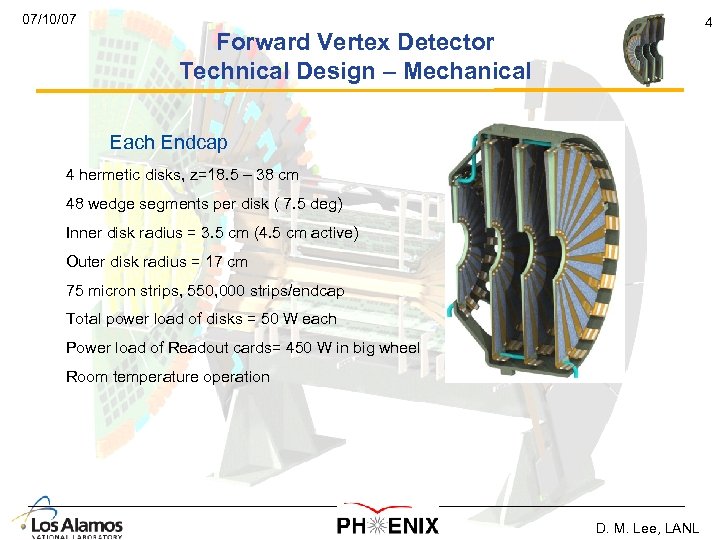

07/10/07 4 Forward Vertex Detector Technical Design – Mechanical Each Endcap 4 hermetic disks, z=18. 5 – 38 cm 48 wedge segments per disk ( 7. 5 deg) Inner disk radius = 3. 5 cm (4. 5 cm active) Outer disk radius = 17 cm 75 micron strips, 550, 000 strips/endcap Total power load of disks = 50 W each Power load of Readout cards= 450 W in big wheel Room temperature operation D. M. Lee, LANL

07/10/07 4 Forward Vertex Detector Technical Design – Mechanical Each Endcap 4 hermetic disks, z=18. 5 – 38 cm 48 wedge segments per disk ( 7. 5 deg) Inner disk radius = 3. 5 cm (4. 5 cm active) Outer disk radius = 17 cm 75 micron strips, 550, 000 strips/endcap Total power load of disks = 50 W each Power load of Readout cards= 450 W in big wheel Room temperature operation D. M. Lee, LANL

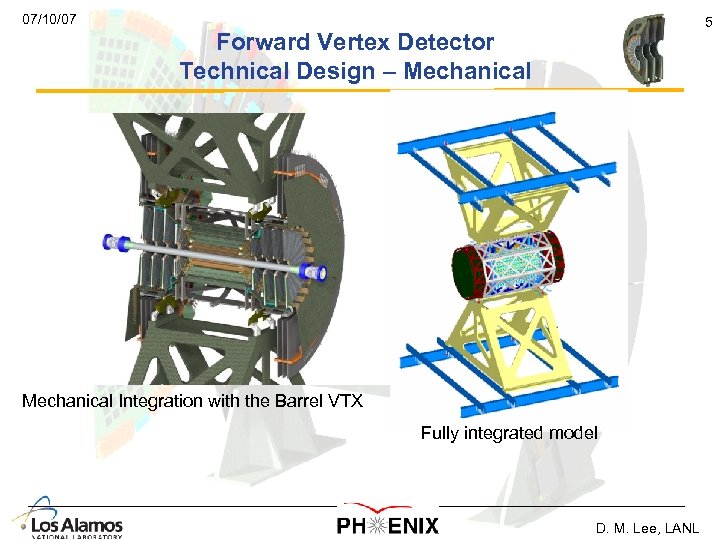

07/10/07 5 Forward Vertex Detector Technical Design – Mechanical Integration with the Barrel VTX Fully integrated model D. M. Lee, LANL

07/10/07 5 Forward Vertex Detector Technical Design – Mechanical Integration with the Barrel VTX Fully integrated model D. M. Lee, LANL

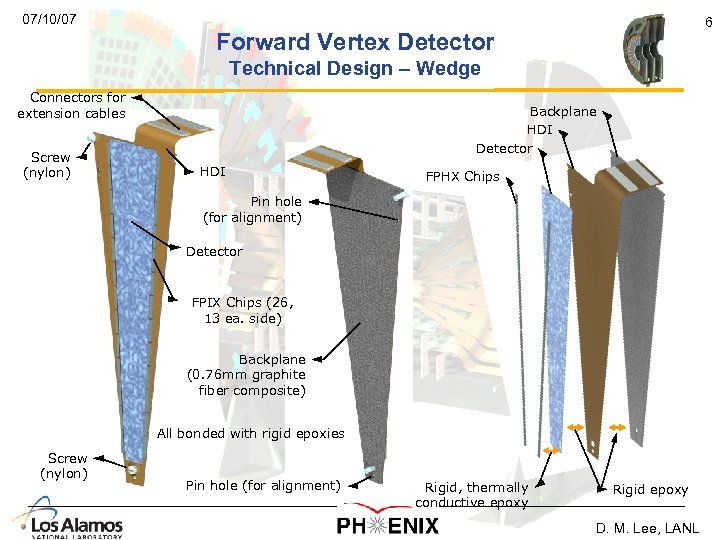

07/10/07 6 Forward Vertex Detector Technical Design – Wedge Connectors for extension cables Screw (nylon) Backplane HDI Detector HDI FPHX Chips Pin hole (for alignment) Detector FPIX Chips (26, 13 ea. side) Backplane (0. 76 mm graphite fiber composite) All bonded with rigid epoxies Screw (nylon) Pin hole (for alignment) Rigid, thermally conductive epoxy Rigid epoxy D. M. Lee, LANL

07/10/07 6 Forward Vertex Detector Technical Design – Wedge Connectors for extension cables Screw (nylon) Backplane HDI Detector HDI FPHX Chips Pin hole (for alignment) Detector FPIX Chips (26, 13 ea. side) Backplane (0. 76 mm graphite fiber composite) All bonded with rigid epoxies Screw (nylon) Pin hole (for alignment) Rigid, thermally conductive epoxy Rigid epoxy D. M. Lee, LANL

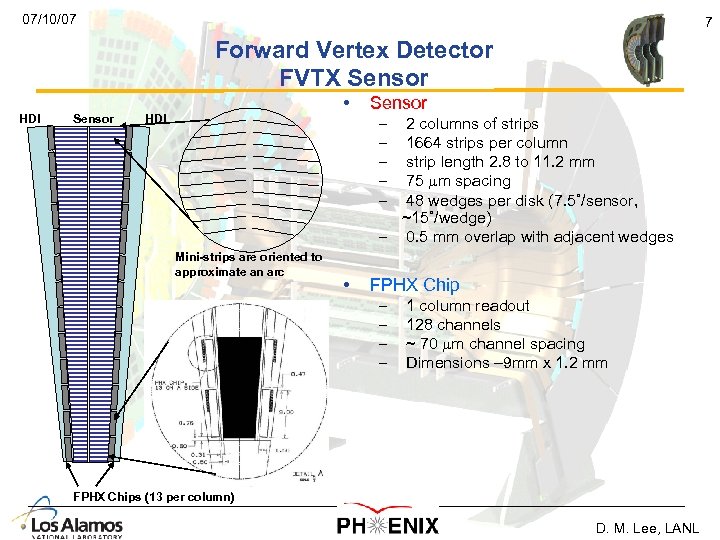

07/10/07 7 Forward Vertex Detector FVTX Sensor HDI Sensor • Sensor HDI – – – 2 columns of strips 1664 strips per column strip length 2. 8 to 11. 2 mm 75 µm spacing 48 wedges per disk (7. 5˚/sensor, ~15˚/wedge) – 0. 5 mm overlap with adjacent wedges Mini-strips are oriented to approximate an arc • FPHX Chip – – 1 column readout 128 channels ~ 70 µm channel spacing Dimensions – 9 mm x 1. 2 mm FPHX Chips (13 per column) D. M. Lee, LANL

07/10/07 7 Forward Vertex Detector FVTX Sensor HDI Sensor • Sensor HDI – – – 2 columns of strips 1664 strips per column strip length 2. 8 to 11. 2 mm 75 µm spacing 48 wedges per disk (7. 5˚/sensor, ~15˚/wedge) – 0. 5 mm overlap with adjacent wedges Mini-strips are oriented to approximate an arc • FPHX Chip – – 1 column readout 128 channels ~ 70 µm channel spacing Dimensions – 9 mm x 1. 2 mm FPHX Chips (13 per column) D. M. Lee, LANL

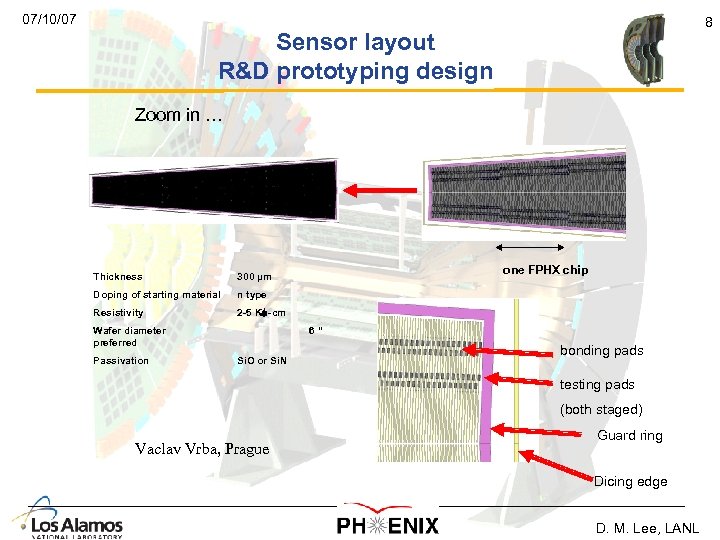

07/10/07 8 Sensor layout R&D prototyping design Zoom in … Thickness Doping of starting material n type Resistivity one FPHX chip 300 µm 2 -5 K -cm Wafer diameter preferred Passivation 6“ Si. O or Si. N bonding pads testing pads (both staged) Vaclav Vrba, Prague Guard ring Dicing edge D. M. Lee, LANL

07/10/07 8 Sensor layout R&D prototyping design Zoom in … Thickness Doping of starting material n type Resistivity one FPHX chip 300 µm 2 -5 K -cm Wafer diameter preferred Passivation 6“ Si. O or Si. N bonding pads testing pads (both staged) Vaclav Vrba, Prague Guard ring Dicing edge D. M. Lee, LANL

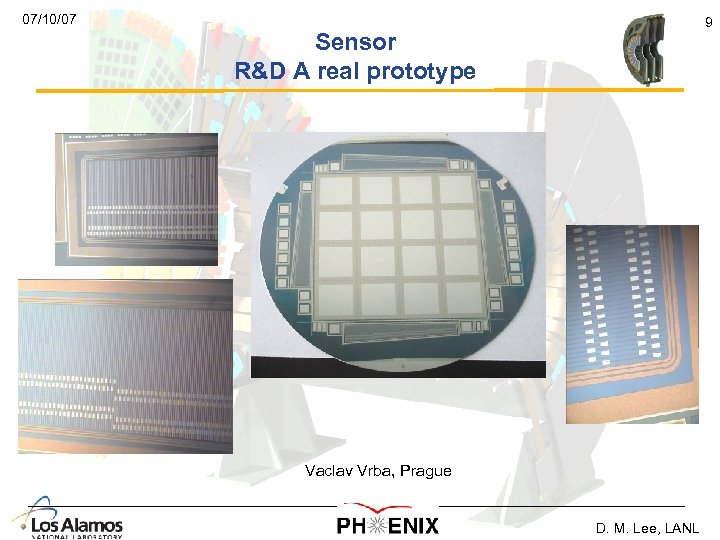

07/10/07 9 Sensor R&D A real prototype Vaclav Vrba, Prague D. M. Lee, LANL

07/10/07 9 Sensor R&D A real prototype Vaclav Vrba, Prague D. M. Lee, LANL

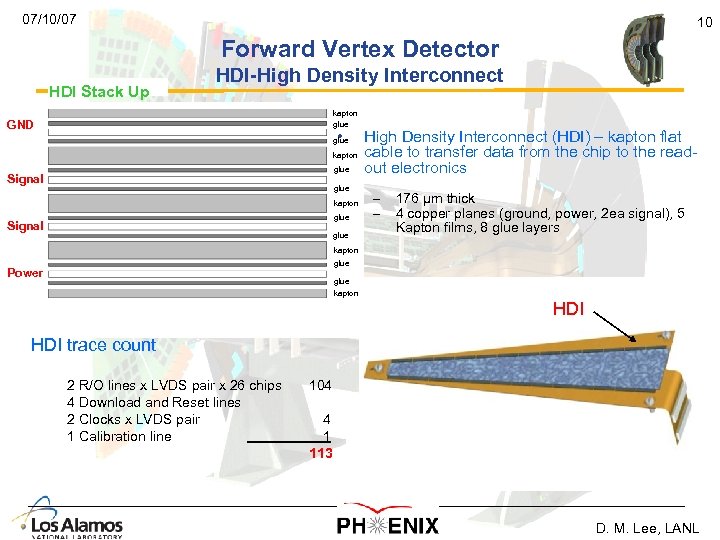

07/10/07 10 Forward Vertex Detector HDI Stack Up HDI-High Density Interconnect kapton glue GND • glue kapton glue Signal glue High Density Interconnect (HDI) – kapton flat cable to transfer data from the chip to the readout electronics – – 176 μm thick 4 copper planes (ground, power, 2 ea signal), 5 Kapton films, 8 glue layers kapton glue Power glue kapton HDI trace count 2 R/O lines x LVDS pair x 26 chips 4 Download and Reset lines 2 Clocks x LVDS pair 1 Calibration line 104 4 4 1 113 D. M. Lee, LANL

07/10/07 10 Forward Vertex Detector HDI Stack Up HDI-High Density Interconnect kapton glue GND • glue kapton glue Signal glue High Density Interconnect (HDI) – kapton flat cable to transfer data from the chip to the readout electronics – – 176 μm thick 4 copper planes (ground, power, 2 ea signal), 5 Kapton films, 8 glue layers kapton glue Power glue kapton HDI trace count 2 R/O lines x LVDS pair x 26 chips 4 Download and Reset lines 2 Clocks x LVDS pair 1 Calibration line 104 4 4 1 113 D. M. Lee, LANL

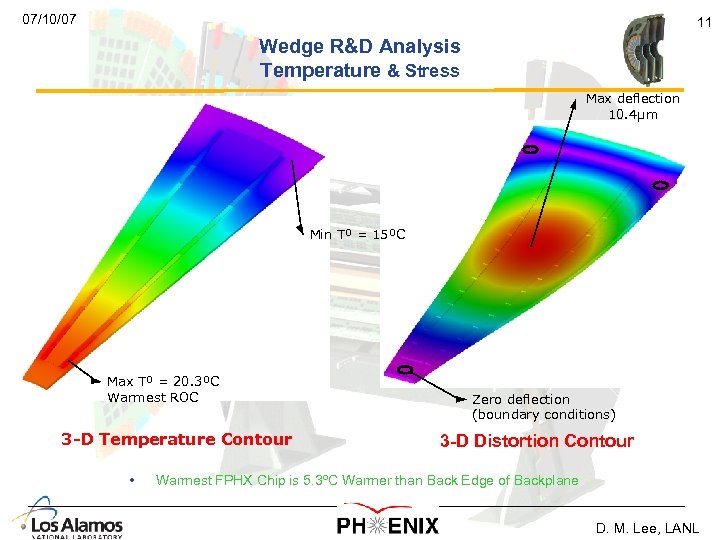

07/10/07 11 Wedge R&D Analysis Temperature & Stress Max deflection 10. 4μm Min Tº = 15ºC Max Tº = 20. 3ºC Warmest ROC 3 -D Temperature Contour • Zero deflection (boundary conditions) 3 -D Distortion Contour Warmest FPHX Chip is 5. 3ºC Warmer than Back Edge of Backplane D. M. Lee, LANL

07/10/07 11 Wedge R&D Analysis Temperature & Stress Max deflection 10. 4μm Min Tº = 15ºC Max Tº = 20. 3ºC Warmest ROC 3 -D Temperature Contour • Zero deflection (boundary conditions) 3 -D Distortion Contour Warmest FPHX Chip is 5. 3ºC Warmer than Back Edge of Backplane D. M. Lee, LANL

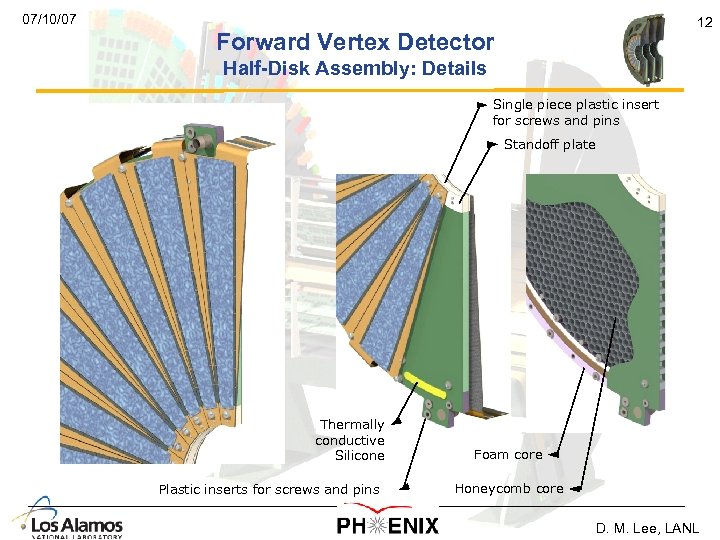

07/10/07 12 Forward Vertex Detector Half-Disk Assembly: Details Single piece plastic insert for screws and pins Standoff plate Thermally conductive Silicone Plastic inserts for screws and pins Foam core Honeycomb core D. M. Lee, LANL

07/10/07 12 Forward Vertex Detector Half-Disk Assembly: Details Single piece plastic insert for screws and pins Standoff plate Thermally conductive Silicone Plastic inserts for screws and pins Foam core Honeycomb core D. M. Lee, LANL

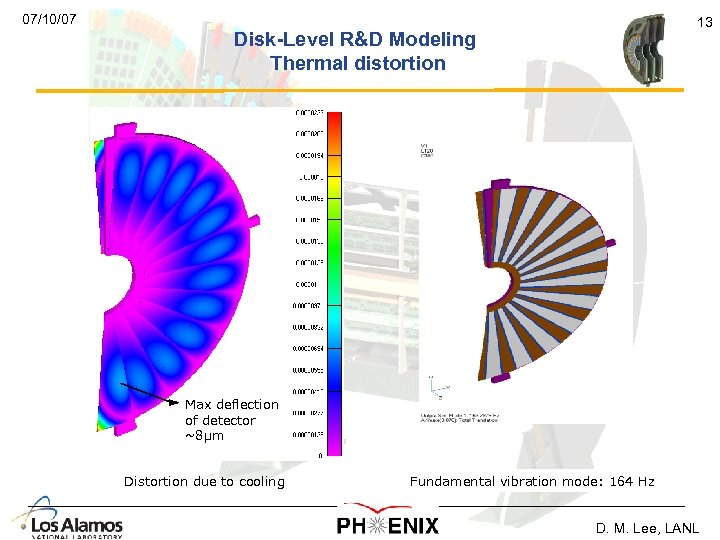

07/10/07 13 Disk-Level R&D Modeling Thermal distortion Max deflection of detector ~8μm Distortion due to cooling Fundamental vibration mode: 164 Hz D. M. Lee, LANL

07/10/07 13 Disk-Level R&D Modeling Thermal distortion Max deflection of detector ~8μm Distortion due to cooling Fundamental vibration mode: 164 Hz D. M. Lee, LANL

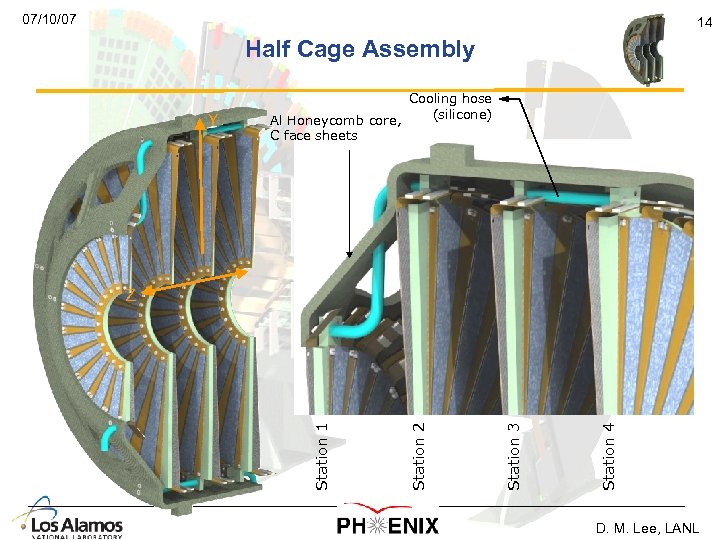

07/10/07 14 Half Cage Assembly Y Cooling hose (silicone) Al Honeycomb core, C face sheets Station 4 Station 3 Station 2 Station 1 Z D. M. Lee, LANL

07/10/07 14 Half Cage Assembly Y Cooling hose (silicone) Al Honeycomb core, C face sheets Station 4 Station 3 Station 2 Station 1 Z D. M. Lee, LANL

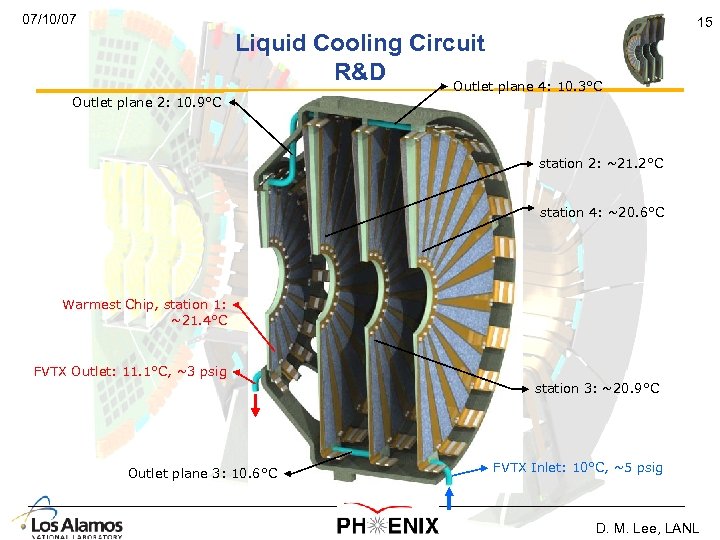

07/10/07 Liquid Cooling Circuit R&D Outlet plane 4: 10. 3°C 15 Outlet plane 2: 10. 9°C station 2: ~21. 2°C station 4: ~20. 6°C Warmest Chip, station 1: ~21. 4°C FVTX Outlet: 11. 1°C, ~3 psig station 3: ~20. 9°C Outlet plane 3: 10. 6°C FVTX Inlet: 10°C, ~5 psig D. M. Lee, LANL

07/10/07 Liquid Cooling Circuit R&D Outlet plane 4: 10. 3°C 15 Outlet plane 2: 10. 9°C station 2: ~21. 2°C station 4: ~20. 6°C Warmest Chip, station 1: ~21. 4°C FVTX Outlet: 11. 1°C, ~3 psig station 3: ~20. 9°C Outlet plane 3: 10. 6°C FVTX Inlet: 10°C, ~5 psig D. M. Lee, LANL

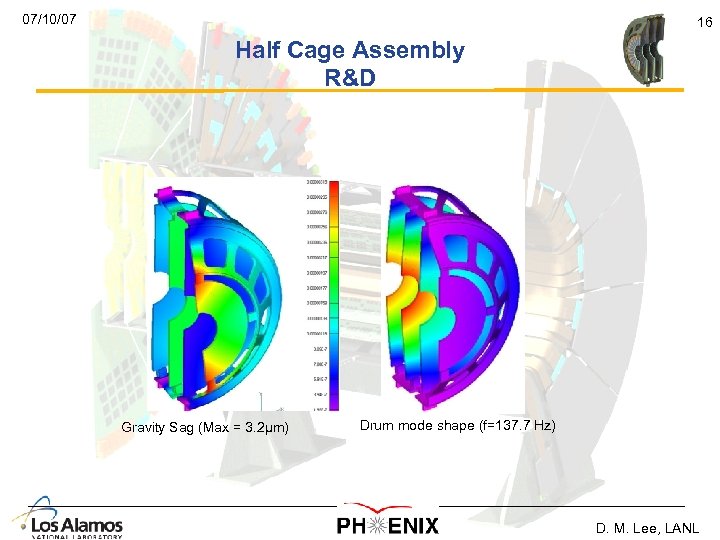

07/10/07 16 Half Cage Assembly R&D Gravity Sag (Max = 3. 2µm) Drum mode shape (f=137. 7 Hz) D. M. Lee, LANL

07/10/07 16 Half Cage Assembly R&D Gravity Sag (Max = 3. 2µm) Drum mode shape (f=137. 7 Hz) D. M. Lee, LANL

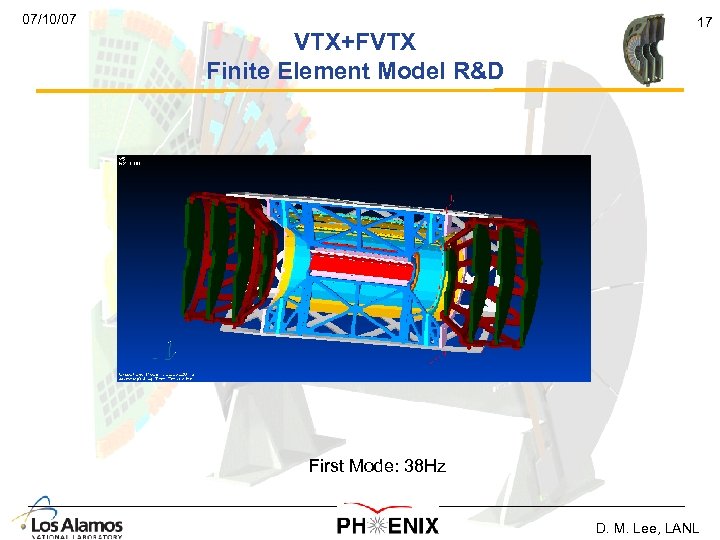

07/10/07 VTX+FVTX Finite Element Model R&D 17 First Mode: 38 Hz D. M. Lee, LANL

07/10/07 VTX+FVTX Finite Element Model R&D 17 First Mode: 38 Hz D. M. Lee, LANL

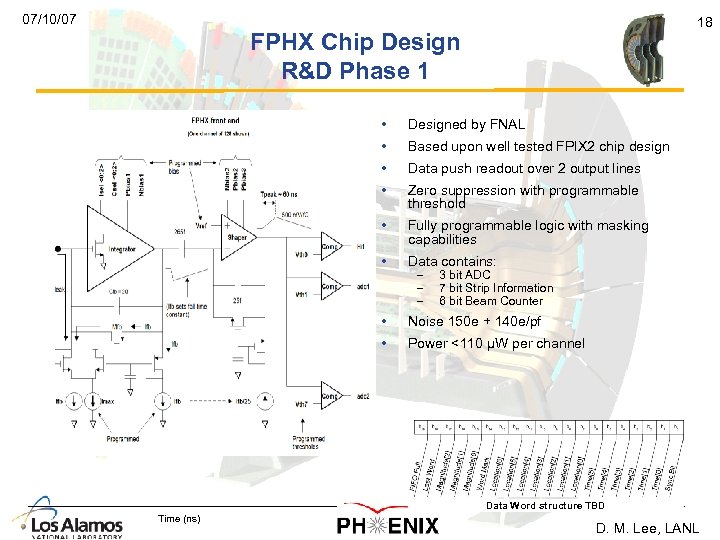

07/10/07 18 FPHX Chip Design R&D Phase 1 • • Designed by FNAL • Fully programmable logic with masking capabilities • Data contains: • • Noise 150 e + 140 e/pf Based upon well tested FPIX 2 chip design Data push readout over 2 output lines Zero suppression with programmable threshold – – – 3 bit ADC 7 bit Strip Information 6 bit Beam Counter Power <110 µW per channel Data Word structure TBD Time (ns) D. M. Lee, LANL

07/10/07 18 FPHX Chip Design R&D Phase 1 • • Designed by FNAL • Fully programmable logic with masking capabilities • Data contains: • • Noise 150 e + 140 e/pf Based upon well tested FPIX 2 chip design Data push readout over 2 output lines Zero suppression with programmable threshold – – – 3 bit ADC 7 bit Strip Information 6 bit Beam Counter Power <110 µW per channel Data Word structure TBD Time (ns) D. M. Lee, LANL

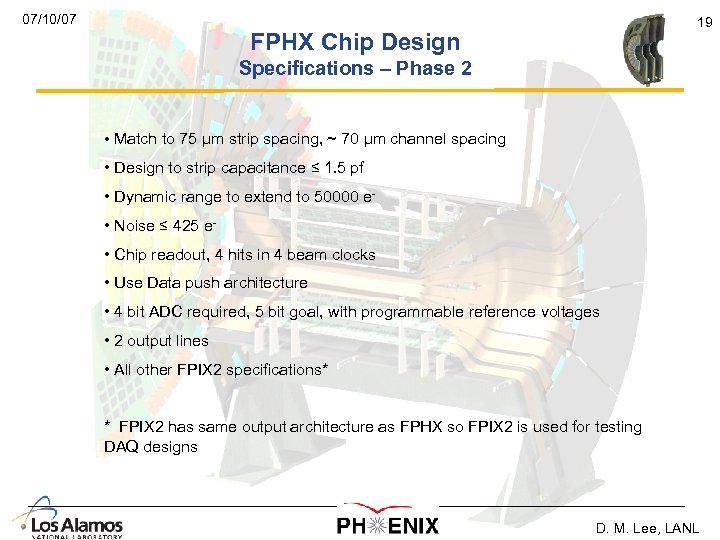

07/10/07 19 FPHX Chip Design Specifications – Phase 2 • Match to 75 µm strip spacing, ~ 70 µm channel spacing • Design to strip capacitance ≤ 1. 5 pf • Dynamic range to extend to 50000 e • Noise ≤ 425 e • Chip readout, 4 hits in 4 beam clocks • Use Data push architecture • 4 bit ADC required, 5 bit goal, with programmable reference voltages • 2 output lines • All other FPIX 2 specifications* * FPIX 2 has same output architecture as FPHX so FPIX 2 is used for testing DAQ designs D. M. Lee, LANL

07/10/07 19 FPHX Chip Design Specifications – Phase 2 • Match to 75 µm strip spacing, ~ 70 µm channel spacing • Design to strip capacitance ≤ 1. 5 pf • Dynamic range to extend to 50000 e • Noise ≤ 425 e • Chip readout, 4 hits in 4 beam clocks • Use Data push architecture • 4 bit ADC required, 5 bit goal, with programmable reference voltages • 2 output lines • All other FPIX 2 specifications* * FPIX 2 has same output architecture as FPHX so FPIX 2 is used for testing DAQ designs D. M. Lee, LANL

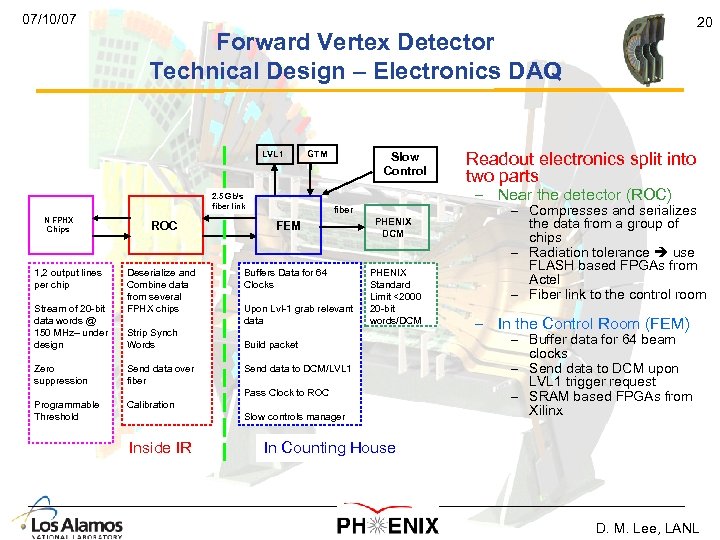

07/10/07 20 Forward Vertex Detector Technical Design – Electronics DAQ LVL 1 GTM 2. 5 Gb/s fiber link N FPHX Chips 1, 2 output lines per chip Stream of 20 -bit data words @ 150 MHz– under design ROC Deserialize and Combine data from several FPHX chips Strip Synch Words Zero suppression Send data over fiber Programmable Threshold Slow Control – Near the detector (ROC) fiber FEM Buffers Data for 64 Clocks Upon Lvl-1 grab relevant data PHENIX DCM PHENIX Standard Limit <2000 20 -bit words/DCM Build packet Calibration Send data to DCM/LVL 1 Pass Clock to ROC Slow controls manager Inside IR Readout electronics split into two parts – Compresses and serializes the data from a group of chips – Radiation tolerance use FLASH based FPGAs from Actel – Fiber link to the control room – In the Control Room (FEM) – Buffer data for 64 beam clocks – Send data to DCM upon LVL 1 trigger request – SRAM based FPGAs from Xilinx In Counting House D. M. Lee, LANL

07/10/07 20 Forward Vertex Detector Technical Design – Electronics DAQ LVL 1 GTM 2. 5 Gb/s fiber link N FPHX Chips 1, 2 output lines per chip Stream of 20 -bit data words @ 150 MHz– under design ROC Deserialize and Combine data from several FPHX chips Strip Synch Words Zero suppression Send data over fiber Programmable Threshold Slow Control – Near the detector (ROC) fiber FEM Buffers Data for 64 Clocks Upon Lvl-1 grab relevant data PHENIX DCM PHENIX Standard Limit <2000 20 -bit words/DCM Build packet Calibration Send data to DCM/LVL 1 Pass Clock to ROC Slow controls manager Inside IR Readout electronics split into two parts – Compresses and serializes the data from a group of chips – Radiation tolerance use FLASH based FPGAs from Actel – Fiber link to the control room – In the Control Room (FEM) – Buffer data for 64 beam clocks – Send data to DCM upon LVL 1 trigger request – SRAM based FPGAs from Xilinx In Counting House D. M. Lee, LANL

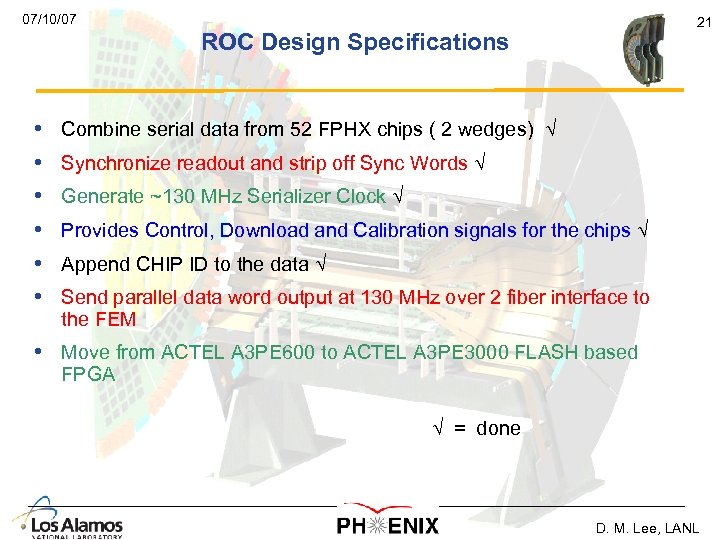

07/10/07 21 ROC Design Specifications • • • Combine serial data from 52 FPHX chips ( 2 wedges) Synchronize readout and strip off Sync Words Generate ~130 MHz Serializer Clock Provides Control, Download and Calibration signals for the chips Append CHIP ID to the data Send parallel data word output at 130 MHz over 2 fiber interface to the FEM • Move from ACTEL A 3 PE 600 to ACTEL A 3 PE 3000 FLASH based FPGA = done D. M. Lee, LANL

07/10/07 21 ROC Design Specifications • • • Combine serial data from 52 FPHX chips ( 2 wedges) Synchronize readout and strip off Sync Words Generate ~130 MHz Serializer Clock Provides Control, Download and Calibration signals for the chips Append CHIP ID to the data Send parallel data word output at 130 MHz over 2 fiber interface to the FEM • Move from ACTEL A 3 PE 600 to ACTEL A 3 PE 3000 FLASH based FPGA = done D. M. Lee, LANL

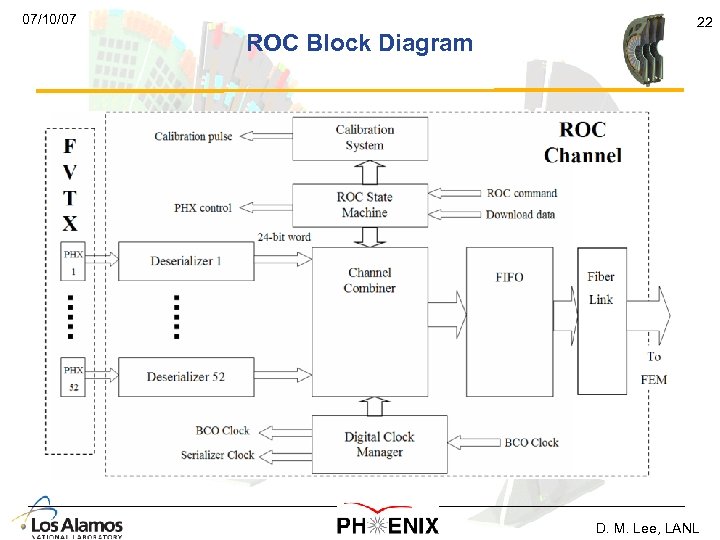

07/10/07 ROC Block Diagram 22 D. M. Lee, LANL

07/10/07 ROC Block Diagram 22 D. M. Lee, LANL

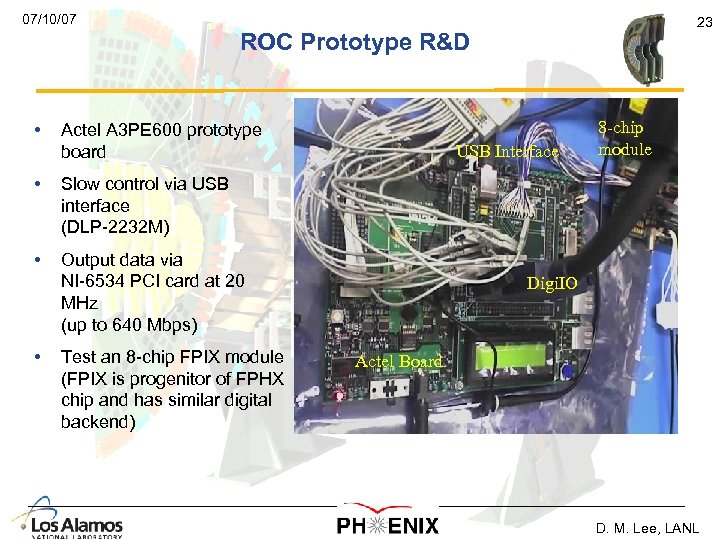

07/10/07 23 ROC Prototype R&D • Actel A 3 PE 600 prototype USB Interface board 8 -chip module • Slow control via USB interface (DLP-2232 M) • Output data via NI-6534 PCI card at 20 MHz (up to 640 Mbps) • Test an 8 -chip FPIX module (FPIX is progenitor of FPHX chip and has similar digital backend) Digi. IO Actel Board D. M. Lee, LANL

07/10/07 23 ROC Prototype R&D • Actel A 3 PE 600 prototype USB Interface board 8 -chip module • Slow control via USB interface (DLP-2232 M) • Output data via NI-6534 PCI card at 20 MHz (up to 640 Mbps) • Test an 8 -chip FPIX module (FPIX is progenitor of FPHX chip and has similar digital backend) Digi. IO Actel Board D. M. Lee, LANL

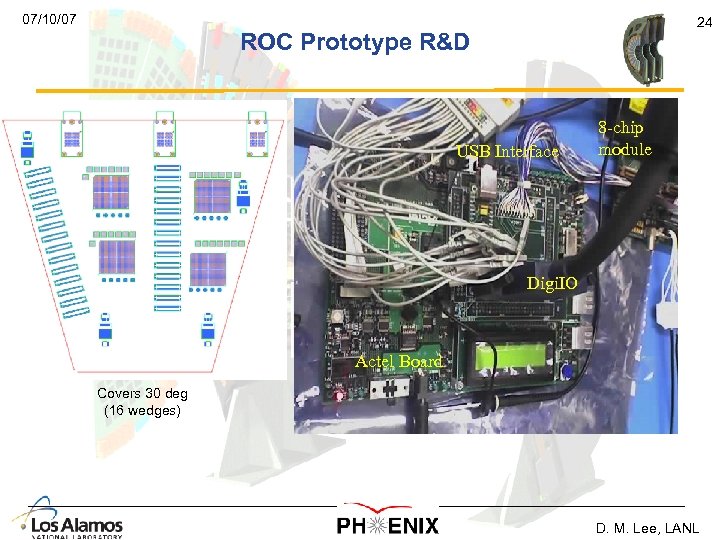

07/10/07 24 ROC Prototype R&D USB Interface 8 -chip module Digi. IO Actel Board Covers 30 deg (16 wedges) D. M. Lee, LANL

07/10/07 24 ROC Prototype R&D USB Interface 8 -chip module Digi. IO Actel Board Covers 30 deg (16 wedges) D. M. Lee, LANL

07/10/07 25 FEM Design Specifications • FEM receives data from a single ROC channel over two fibers at fixed rate of 2. 5 Gbits/s • Main functionality – – Store the data by BCO counter Buffer data for 64 BCO clocks Read the data from certain clock to output buffer at 300 MHz Send the output buffer content to the DCM • Plan to combine the data from 4 FEM channels on single FEM board • Implementation – Xilinx mid-scale Virtex-4 FPGA VC 4 VSX 35 – Use built-in FIFOs and Relationally Placed Macros (RPMs) for maximum performance and predictability (Provided by XILINX) = done D. M. Lee, LANL

07/10/07 25 FEM Design Specifications • FEM receives data from a single ROC channel over two fibers at fixed rate of 2. 5 Gbits/s • Main functionality – – Store the data by BCO counter Buffer data for 64 BCO clocks Read the data from certain clock to output buffer at 300 MHz Send the output buffer content to the DCM • Plan to combine the data from 4 FEM channels on single FEM board • Implementation – Xilinx mid-scale Virtex-4 FPGA VC 4 VSX 35 – Use built-in FIFOs and Relationally Placed Macros (RPMs) for maximum performance and predictability (Provided by XILINX) = done D. M. Lee, LANL

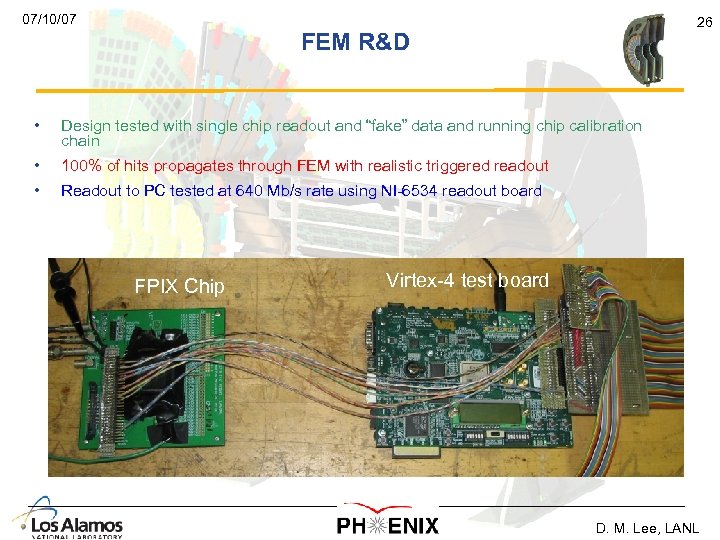

07/10/07 26 FEM R&D • Design tested with single chip readout and “fake” data and running chip calibration chain • • 100% of hits propagates through FEM with realistic triggered readout Readout to PC tested at 640 Mb/s rate using NI-6534 readout board FPIX Chip Virtex-4 test board D. M. Lee, LANL

07/10/07 26 FEM R&D • Design tested with single chip readout and “fake” data and running chip calibration chain • • 100% of hits propagates through FEM with realistic triggered readout Readout to PC tested at 640 Mb/s rate using NI-6534 readout board FPIX Chip Virtex-4 test board D. M. Lee, LANL

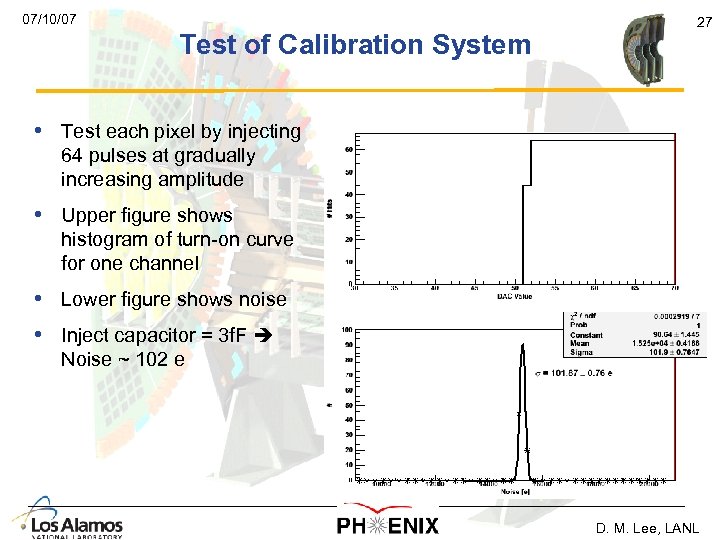

07/10/07 Test of Calibration System 27 • Test each pixel by injecting 64 pulses at gradually increasing amplitude • Upper figure shows histogram of turn-on curve for one channel • Lower figure shows noise • Inject capacitor = 3 f. F Noise ~ 102 e D. M. Lee, LANL

07/10/07 Test of Calibration System 27 • Test each pixel by injecting 64 pulses at gradually increasing amplitude • Upper figure shows histogram of turn-on curve for one channel • Lower figure shows noise • Inject capacitor = 3 f. F Noise ~ 102 e D. M. Lee, LANL

07/10/07 28 Summary Designs and R&D • Mechanical design is well along and mature • Some mechanical prototyping needed • Sensor prototype finished and ready for testing • Readout ROC and FEM prototyped and tested – Fiber link prototyped and under test – All other requirements met – Calibration circuit designed and to be implemented on ROC board • FPHX conceptual design done, first pass FEM with fiber readout • FPHX R&D critical path D. M. Lee, LANL

07/10/07 28 Summary Designs and R&D • Mechanical design is well along and mature • Some mechanical prototyping needed • Sensor prototype finished and ready for testing • Readout ROC and FEM prototyped and tested – Fiber link prototyped and under test – All other requirements met – Calibration circuit designed and to be implemented on ROC board • FPHX conceptual design done, first pass FEM with fiber readout • FPHX R&D critical path D. M. Lee, LANL

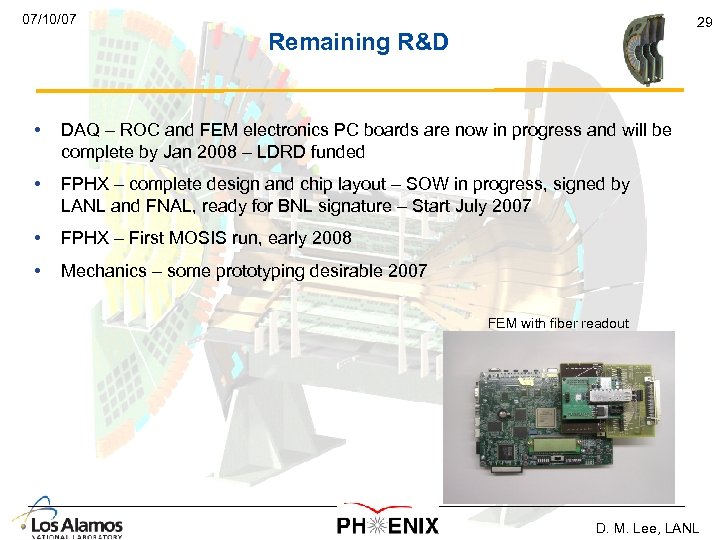

07/10/07 29 Remaining R&D • DAQ – ROC and FEM electronics PC boards are now in progress and will be complete by Jan 2008 – LDRD funded • FPHX – complete design and chip layout – SOW in progress, signed by LANL and FNAL, ready for BNL signature – Start July 2007 • FPHX – First MOSIS run, early 2008 • Mechanics – some prototyping desirable 2007 FEM with fiber readout D. M. Lee, LANL

07/10/07 29 Remaining R&D • DAQ – ROC and FEM electronics PC boards are now in progress and will be complete by Jan 2008 – LDRD funded • FPHX – complete design and chip layout – SOW in progress, signed by LANL and FNAL, ready for BNL signature – Start July 2007 • FPHX – First MOSIS run, early 2008 • Mechanics – some prototyping desirable 2007 FEM with fiber readout D. M. Lee, LANL

07/10/07 30 Cost Basis - Major Items Mechanical structures – HYTEC estimate based on prior experience with VTX and ATLAS Sensors – Quotes from CIS, MICRON FPHX – FNAL estimate based on prior experience Electronics Interface DAQ – estimate based on prior experience Wire bonding – PROMEX quote DCM, slow controls, etc – Muon system experience, Steve Boose D. M. Lee, LANL

07/10/07 30 Cost Basis - Major Items Mechanical structures – HYTEC estimate based on prior experience with VTX and ATLAS Sensors – Quotes from CIS, MICRON FPHX – FNAL estimate based on prior experience Electronics Interface DAQ – estimate based on prior experience Wire bonding – PROMEX quote DCM, slow controls, etc – Muon system experience, Steve Boose D. M. Lee, LANL

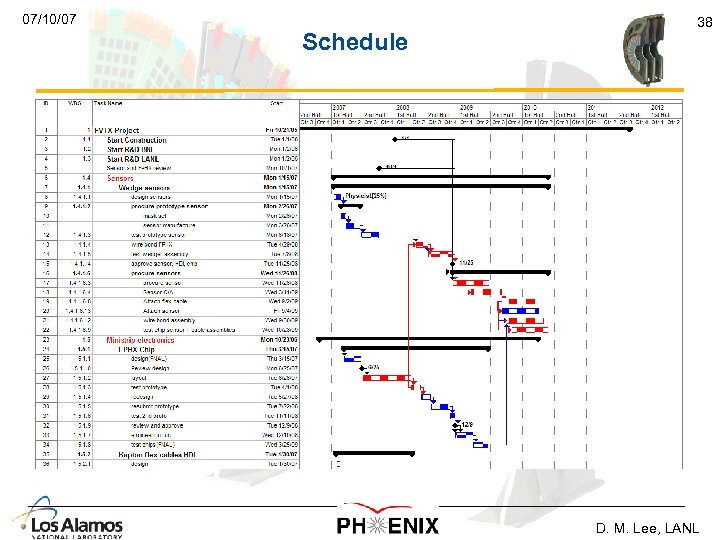

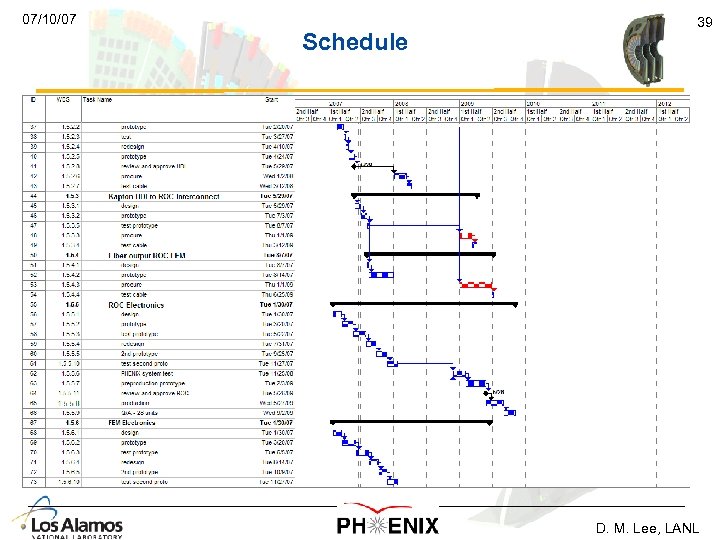

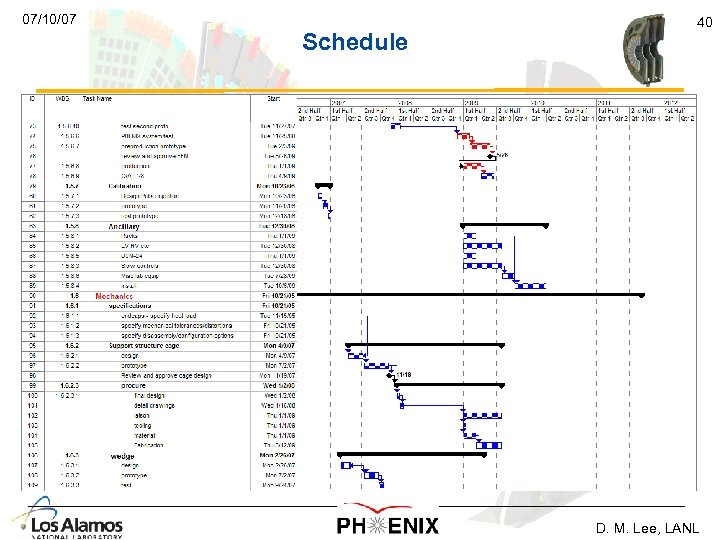

07/10/07 31 FVTX Schedule Assumptions • Construction start – January 1, 2008 ( 2 nd QTR FY 08) • LANL R&D start - January 2006 • BNL R&D start – October 2006 • Schedule durations determined by engineering estimates, vendor quotes • Duration of project made to match funding profile • VTX and LDRD impact the schedule especially R&D • Wedge assemblies tested at a rate of 3/day ( automated computer tests) • Disk assembly assembled in 2 week, metrology of disk in 2 week • Commissioning for 8 months D. M. Lee, LANL

07/10/07 31 FVTX Schedule Assumptions • Construction start – January 1, 2008 ( 2 nd QTR FY 08) • LANL R&D start - January 2006 • BNL R&D start – October 2006 • Schedule durations determined by engineering estimates, vendor quotes • Duration of project made to match funding profile • VTX and LDRD impact the schedule especially R&D • Wedge assemblies tested at a rate of 3/day ( automated computer tests) • Disk assembly assembled in 2 week, metrology of disk in 2 week • Commissioning for 8 months D. M. Lee, LANL

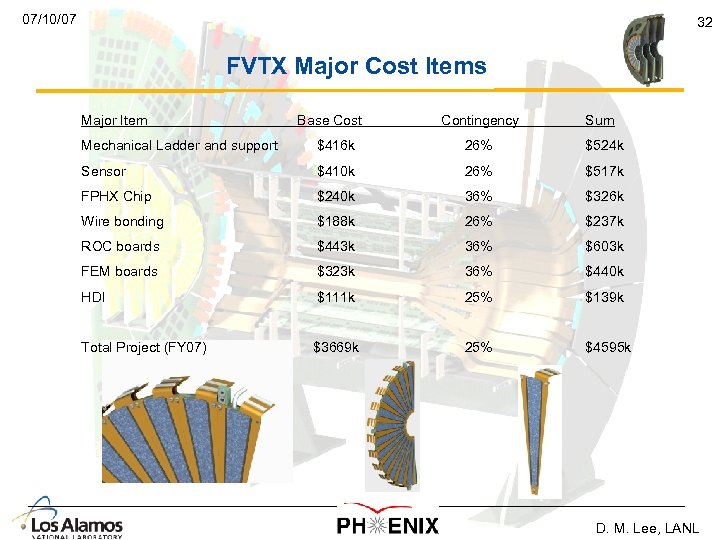

07/10/07 32 FVTX Major Cost Items Major Item Base Cost Contingency Sum Mechanical Ladder and support $416 k 26% $524 k Sensor $410 k 26% $517 k FPHX Chip $240 k 36% $326 k Wire bonding $188 k 26% $237 k ROC boards $443 k 36% $603 k FEM boards $323 k 36% $440 k HDI $111 k 25% $139 k Total Project (FY 07) $3669 k 25% $4595 k D. M. Lee, LANL

07/10/07 32 FVTX Major Cost Items Major Item Base Cost Contingency Sum Mechanical Ladder and support $416 k 26% $524 k Sensor $410 k 26% $517 k FPHX Chip $240 k 36% $326 k Wire bonding $188 k 26% $237 k ROC boards $443 k 36% $603 k FEM boards $323 k 36% $440 k HDI $111 k 25% $139 k Total Project (FY 07) $3669 k 25% $4595 k D. M. Lee, LANL

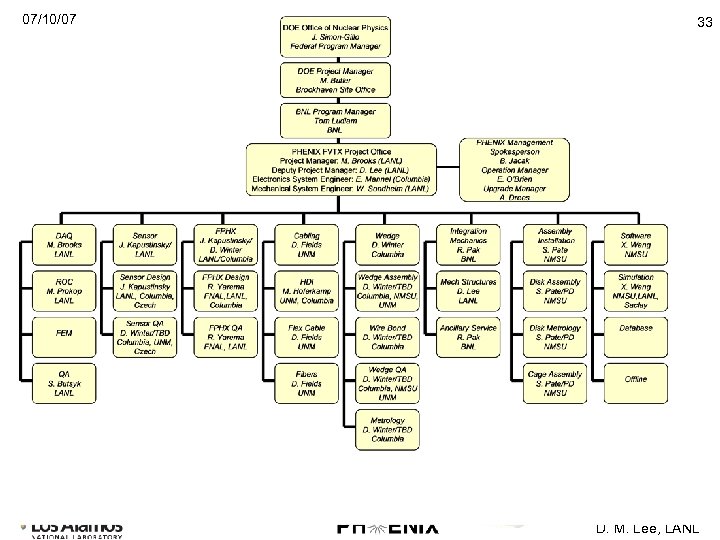

07/10/07 Scientific resources and Manpower 33 D. M. Lee, LANL

07/10/07 Scientific resources and Manpower 33 D. M. Lee, LANL

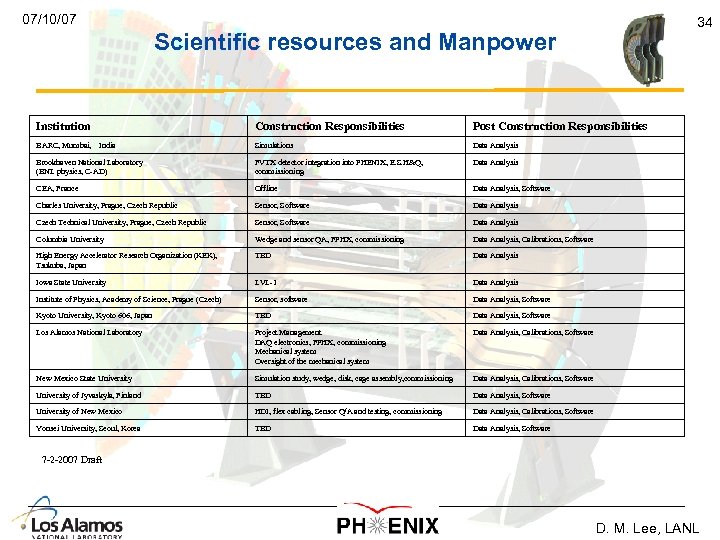

07/10/07 34 Scientific resources and Manpower Institution Construction Responsibilities Post Construction Responsibilities Simulations Data Analysis Brookhaven National Laboratory (BNL physics, C-AD) FVTX detector integration into PHENIX, E. S. H&Q, commissioning Data Analysis CEA, France Offline Data Analysis, Software Charles University, Prague, Czech Republic Sensor, Software Data Analysis Czech Technical University, Prague, Czech Republic Sensor, Software Data Analysis Columbia University Wedge and sensor QA, FPHX, commissioning Data Analysis, Calibrations, Software High Energy Accelerator Research Organization (KEK), Tsukuba, Japan TBD Data Analysis Iowa State University LVL-1 Data Analysis Institute of Physics, Academy of Science, Prague (Czech) Sensor, software Data Analysis, Software Kyoto University, Kyoto 606, Japan TBD Data Analysis, Software Los Alamos National Laboratory Project Management DAQ electronics, FPHX, commissioning Mechanical system Oversight of the mechanical system Data Analysis, Calibrations, Software New Mexico State University Simulation study, wedge, disk, cage assembly, commissioning Data Analysis, Calibrations, Software University of Jyvaskyla, Finland TBD Data Analysis, Software University of New Mexico HDI, flex cabling, Sensor Q/A and testing, commissioning Data Analysis, Calibrations, Software Yonsei University, Seoul, Korea TBD Data Analysis, Software BARC, Mumbai, India 7 -2 -2007 Draft D. M. Lee, LANL

07/10/07 34 Scientific resources and Manpower Institution Construction Responsibilities Post Construction Responsibilities Simulations Data Analysis Brookhaven National Laboratory (BNL physics, C-AD) FVTX detector integration into PHENIX, E. S. H&Q, commissioning Data Analysis CEA, France Offline Data Analysis, Software Charles University, Prague, Czech Republic Sensor, Software Data Analysis Czech Technical University, Prague, Czech Republic Sensor, Software Data Analysis Columbia University Wedge and sensor QA, FPHX, commissioning Data Analysis, Calibrations, Software High Energy Accelerator Research Organization (KEK), Tsukuba, Japan TBD Data Analysis Iowa State University LVL-1 Data Analysis Institute of Physics, Academy of Science, Prague (Czech) Sensor, software Data Analysis, Software Kyoto University, Kyoto 606, Japan TBD Data Analysis, Software Los Alamos National Laboratory Project Management DAQ electronics, FPHX, commissioning Mechanical system Oversight of the mechanical system Data Analysis, Calibrations, Software New Mexico State University Simulation study, wedge, disk, cage assembly, commissioning Data Analysis, Calibrations, Software University of Jyvaskyla, Finland TBD Data Analysis, Software University of New Mexico HDI, flex cabling, Sensor Q/A and testing, commissioning Data Analysis, Calibrations, Software Yonsei University, Seoul, Korea TBD Data Analysis, Software BARC, Mumbai, India 7 -2 -2007 Draft D. M. Lee, LANL

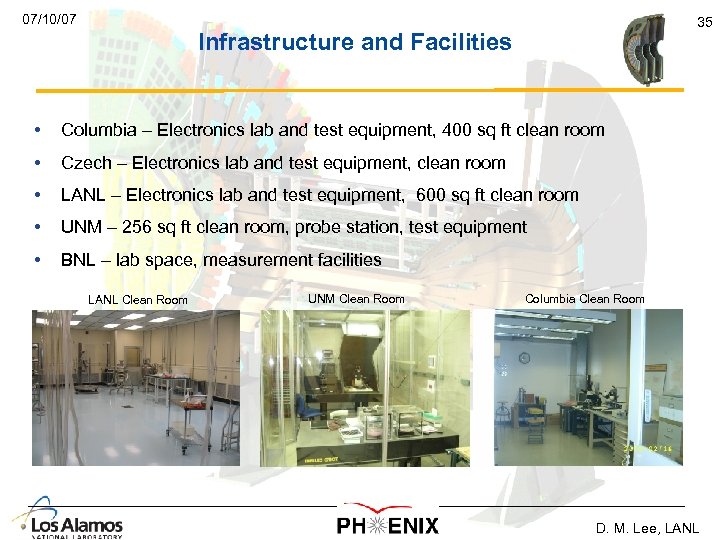

07/10/07 35 Infrastructure and Facilities • Columbia – Electronics lab and test equipment, 400 sq ft clean room • Czech – Electronics lab and test equipment, clean room • LANL – Electronics lab and test equipment, 600 sq ft clean room • UNM – 256 sq ft clean room, probe station, test equipment • BNL – lab space, measurement facilities LANL Clean Room UNM Clean Room Columbia Clean Room D. M. Lee, LANL

07/10/07 35 Infrastructure and Facilities • Columbia – Electronics lab and test equipment, 400 sq ft clean room • Czech – Electronics lab and test equipment, clean room • LANL – Electronics lab and test equipment, 600 sq ft clean room • UNM – 256 sq ft clean room, probe station, test equipment • BNL – lab space, measurement facilities LANL Clean Room UNM Clean Room Columbia Clean Room D. M. Lee, LANL

07/10/07 36 Issues and Concerns • FPHX is new and the highest risk item – will require careful attention • Integration – VTX/FVTX integration – Strip layers still being designed – Big wheel electronics • Electrical – grounding and shielding • Extensive system tests will be required D. M. Lee, LANL

07/10/07 36 Issues and Concerns • FPHX is new and the highest risk item – will require careful attention • Integration – VTX/FVTX integration – Strip layers still being designed – Big wheel electronics • Electrical – grounding and shielding • Extensive system tests will be required D. M. Lee, LANL

07/10/07 Backups 37 D. M. Lee, LANL

07/10/07 Backups 37 D. M. Lee, LANL

07/10/07 Schedule 38 D. M. Lee, LANL

07/10/07 Schedule 38 D. M. Lee, LANL

07/10/07 Schedule 39 D. M. Lee, LANL

07/10/07 Schedule 39 D. M. Lee, LANL

07/10/07 Schedule 40 D. M. Lee, LANL

07/10/07 Schedule 40 D. M. Lee, LANL

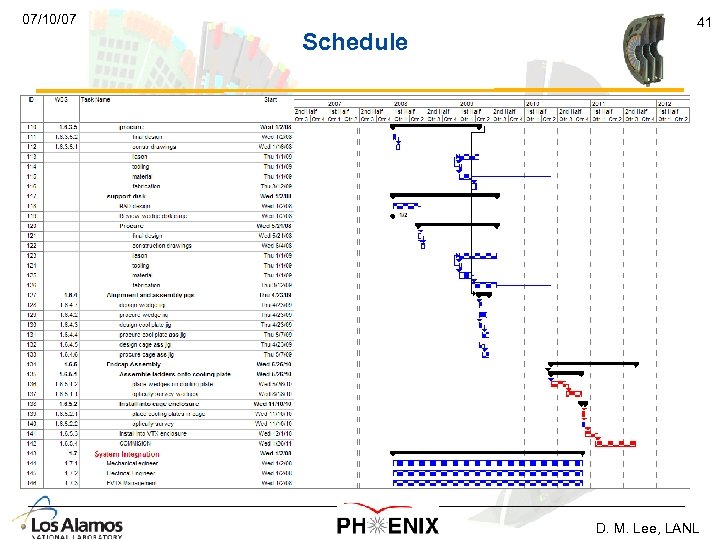

07/10/07 Schedule 41 D. M. Lee, LANL

07/10/07 Schedule 41 D. M. Lee, LANL

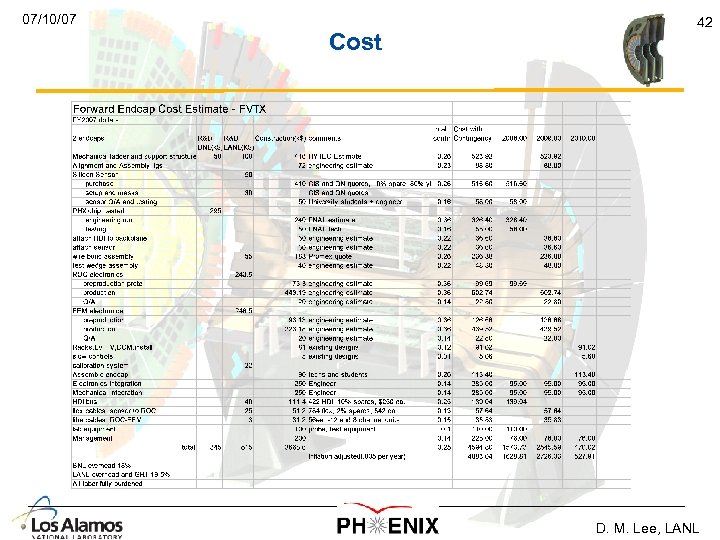

07/10/07 Cost 42 D. M. Lee, LANL

07/10/07 Cost 42 D. M. Lee, LANL

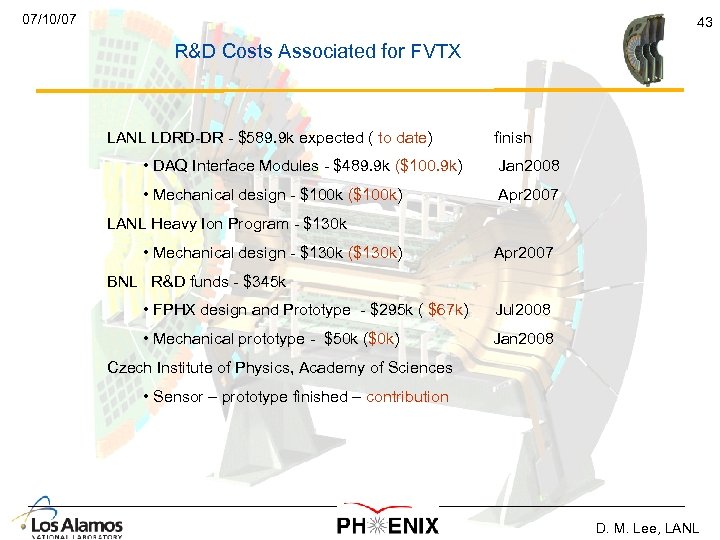

07/10/07 43 R&D Costs Associated for FVTX LANL LDRD-DR - $589. 9 k expected ( to date) finish • DAQ Interface Modules - $489. 9 k ($100. 9 k) Jan 2008 • Mechanical design - $100 k ($100 k) Apr 2007 LANL Heavy Ion Program - $130 k • Mechanical design - $130 k ($130 k) Apr 2007 BNL R&D funds - $345 k • FPHX design and Prototype - $295 k ( $67 k) Jul 2008 • Mechanical prototype - $50 k ($0 k) Jan 2008 Czech Institute of Physics, Academy of Sciences • Sensor – prototype finished – contribution D. M. Lee, LANL

07/10/07 43 R&D Costs Associated for FVTX LANL LDRD-DR - $589. 9 k expected ( to date) finish • DAQ Interface Modules - $489. 9 k ($100. 9 k) Jan 2008 • Mechanical design - $100 k ($100 k) Apr 2007 LANL Heavy Ion Program - $130 k • Mechanical design - $130 k ($130 k) Apr 2007 BNL R&D funds - $345 k • FPHX design and Prototype - $295 k ( $67 k) Jul 2008 • Mechanical prototype - $50 k ($0 k) Jan 2008 Czech Institute of Physics, Academy of Sciences • Sensor – prototype finished – contribution D. M. Lee, LANL

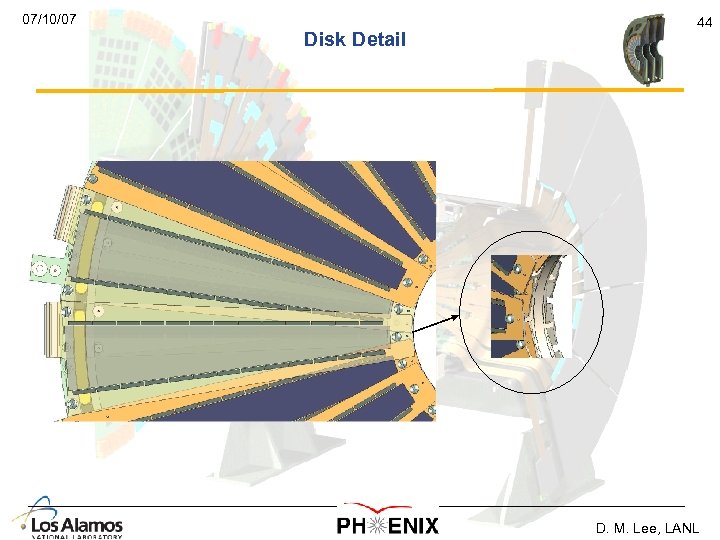

07/10/07 Disk Detail 44 D. M. Lee, LANL

07/10/07 Disk Detail 44 D. M. Lee, LANL

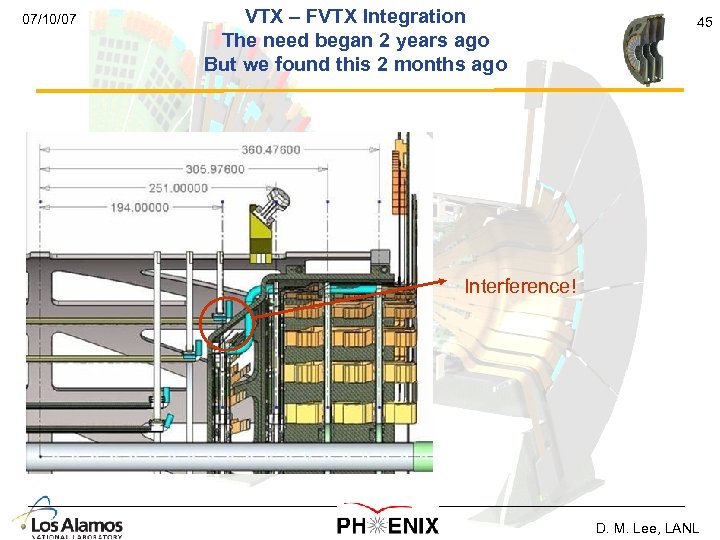

07/10/07 VTX – FVTX Integration The need began 2 years ago But we found this 2 months ago 45 Interference! D. M. Lee, LANL

07/10/07 VTX – FVTX Integration The need began 2 years ago But we found this 2 months ago 45 Interference! D. M. Lee, LANL

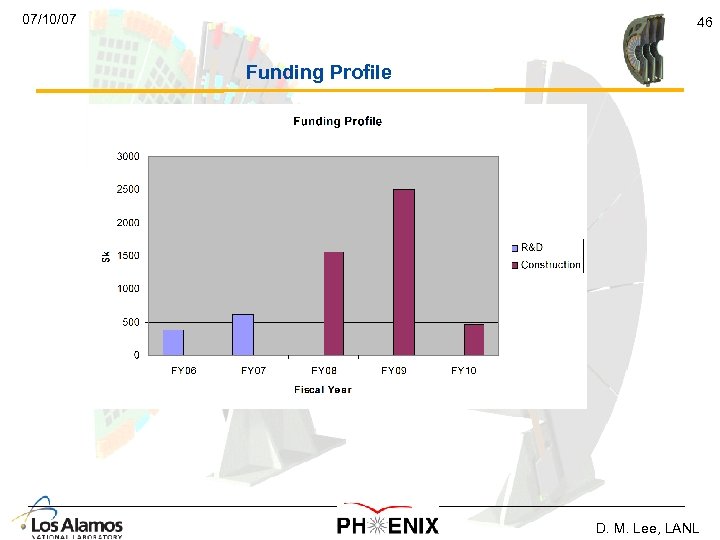

07/10/07 46 Funding Profile D. M. Lee, LANL

07/10/07 46 Funding Profile D. M. Lee, LANL

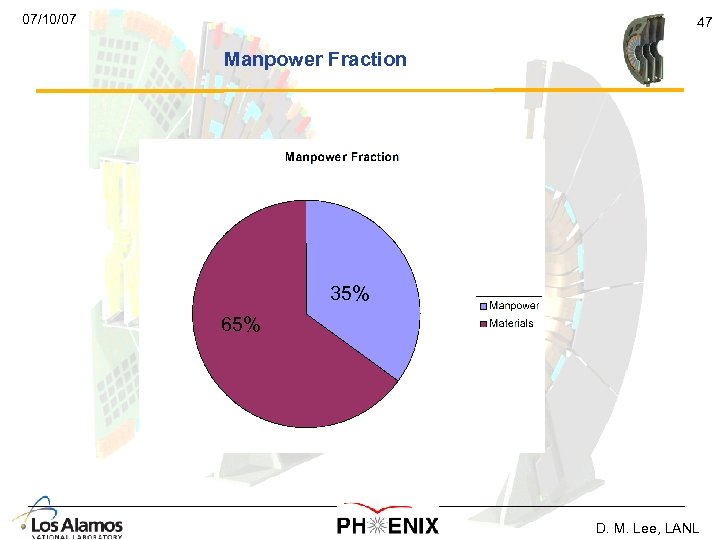

07/10/07 47 Manpower Fraction 35% 65% D. M. Lee, LANL

07/10/07 47 Manpower Fraction 35% 65% D. M. Lee, LANL