6a51effa7d67934f1735f1a875c28033.ppt

- Количество слайдов: 112

제 5장 Interface between CPU and I/O

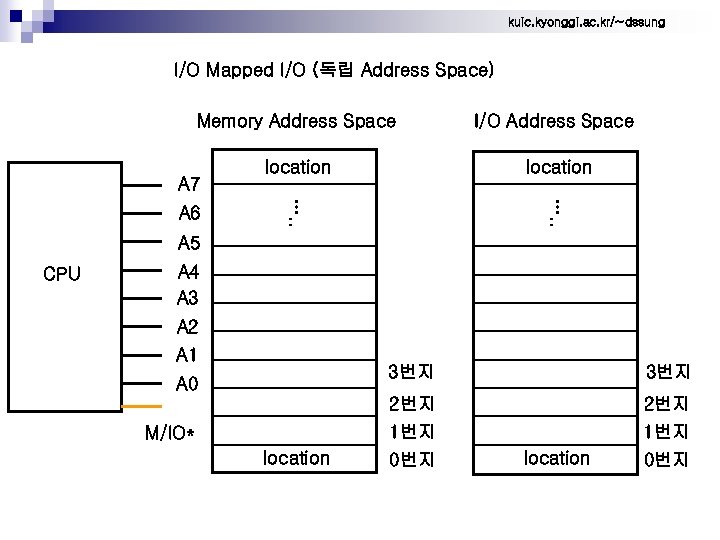

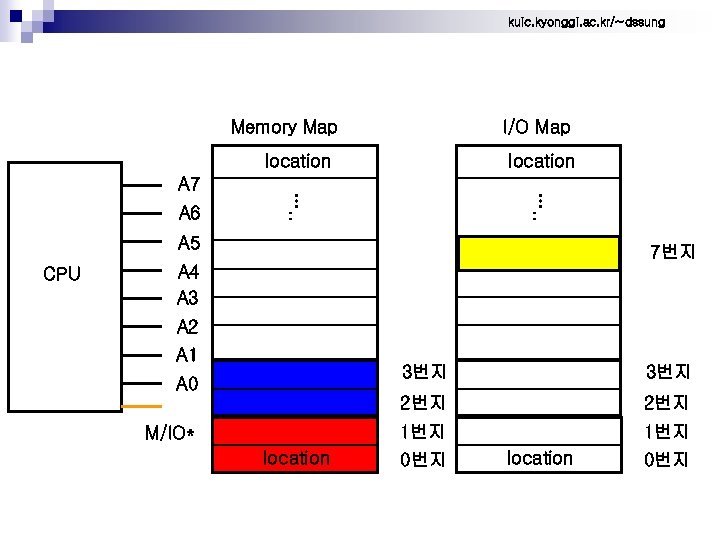

kuic. kyonggi. ac. kr/~dssung 5. 1 CPU와 I/O사이의 통신 특성 및 방법 (1). Fundamentally, a CPU communicates with I/O the same way (map) it does with memory. logically, CPU <--> Memory Map <--> Memory Devices physically, CPU <--> Memory Interface <--> Memory Devices logically, CPU <--> I/O Map <--> I/O Devices physically, CPU <--> I/O Interface <--> I/O Devices

kuic. kyonggi. ac. kr/~dssung I/O Mapped I/O (독립 Address Space) Memory Address Space I/O Address Space location A 7 …. . A 6 A 5 CPU A 4 A 3 A 2 A 1 3번지 location 2번지 1번지 M/IO* 3번지 2번지 A 0 1번지 0번지 location 0번지

kuic. kyonggi. ac. kr/~dssung Memory Map I/O Map location …. . A 6 …. . A 7 location A 5 CPU 7번지 A 4 A 3 A 2 A 1 3번지 location 2번지 1번지 M/IO* 3번지 2번지 A 0 1번지 0번지 location 0번지

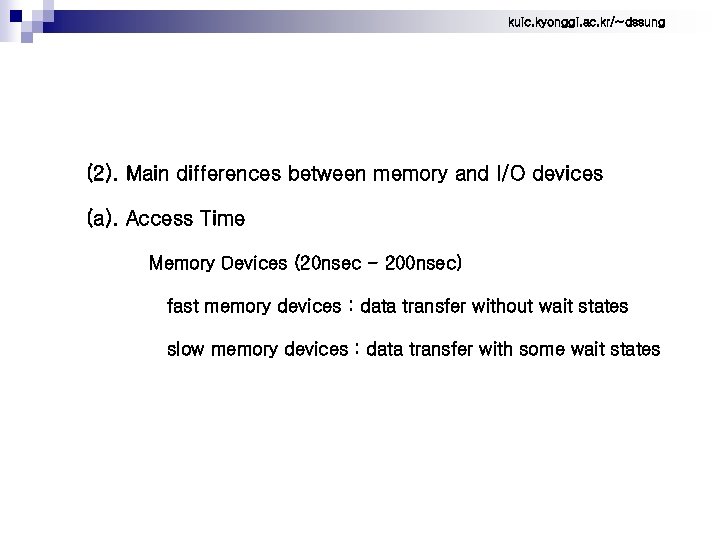

kuic. kyonggi. ac. kr/~dssung (2). Main differences between memory and I/O devices (a). Access Time Memory Devices (20 nsec - 200 nsec) fast memory devices : data transfer without wait states slow memory devices : data transfer with some wait states

kuic. kyonggi. ac. kr/~dssung I/O Devices (5 nsec - unlimited time) In case of Direct I/O method fast I/O devices : data transfer without wait states slow I/O devices : data transfer with many wait states Generally, Speed : Memory devices >> I/O devices (1000 times) State of CPU in wait states is idle state

kuic. kyonggi. ac. kr/~dssung Therefore, Other methods are necessary for data transfer with slow I/O devices first method : polled I/O status information의 이용 - 상태 정보가 만족할 경우 정보교환 - 상태 정보의 확인 : CPU가 확인 (I/O Interface의 입장에서 수동적)

kuic. kyonggi. ac. kr/~dssung second method : interrupt driven I/O - 상태 정보가 만족할 경우 정보교환 - 상태 정보의 확인 : I/O Interface (I/O Interface의 입장에서 능동 적) - 상태 정보가 만족할 경우 I/O Interface는 interrupt를 이용하여 이를 CPU에게 알림 - Polled I/O에 비하여 장점 : CPU가 주기적으로 상태정보를 확인할 필요가 없으며 이 시간에 다른 일을 할 수 있다. - Polled I/O에 비하여 단점 : I/O Interface의 하드웨어 복잡도가 높아짐

kuic. kyonggi. ac. kr/~dssung Direct I/O, Polled I/O, Interrupt Driven I/O와의 공통점 - 정보 교환의 통로 : I/O map (I/O location) Direct I/O <--> Polled I/O, Interrupt Driven I/O와의 차이점 - 상태 정보의 이용 Polled I/O <--> Interrupt Driven I/O와의 차이점 - 상태 정보의 확인 방법

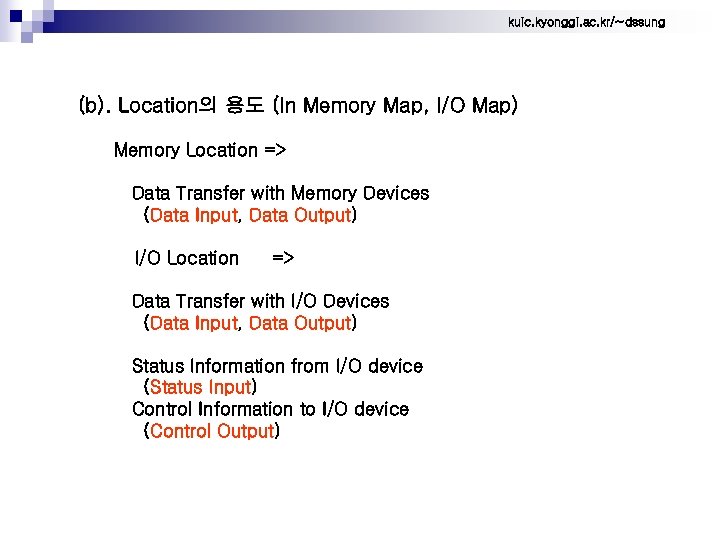

kuic. kyonggi. ac. kr/~dssung (b). Location의 용도 (In Memory Map, I/O Map) Memory Location => Data Transfer with Memory Devices (Data Input, Data Output) I/O Location => Data Transfer with I/O Devices (Data Input, Data Output) Status Information from I/O device (Status Input) Control Information to I/O device (Control Output)

kuic. kyonggi. ac. kr/~dssung (3). 결론 - Fundamentally, a CPU communicates with I/O the same way (map) it does with memory. - Main differences between memory and I/O devices (1) additions of methods for data transfer (Direct) + (Polled I/O, Interrupt Driven I/O) (2) additions of status information and control information (Data Input, Data Output) + (Status Input, Control Output) - Direct I/O, Polled I/O를 programmed I/O라고 한다.

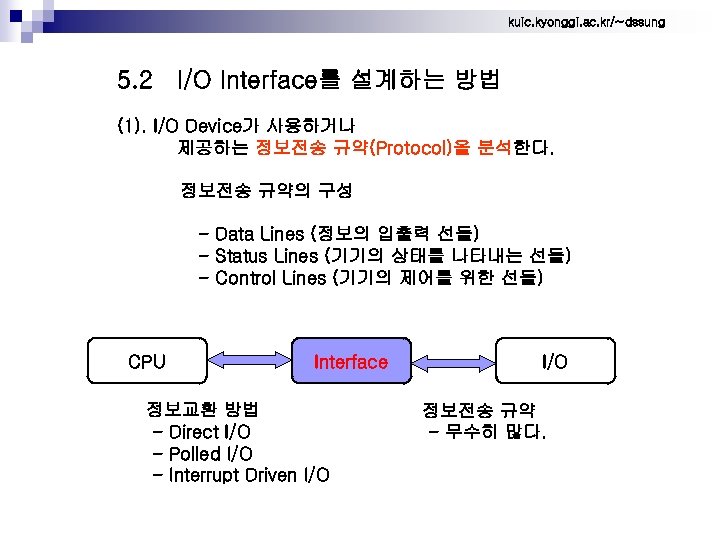

kuic. kyonggi. ac. kr/~dssung 5. 2 I/O Interface를 설계하는 방법 (1). I/O Device가 사용하거나 제공하는 정보전송 규약(Protocol)을 분석한다. 정보전송 규약의 구성 - Data Lines (정보의 입출력 선들) - Status Lines (기기의 상태를 나타내는 선들) - Control Lines (기기의 제어를 위한 선들) CPU Interface 정보교환 방법 - Direct I/O - Polled I/O - Interrupt Driven I/O 정보전송 규약 - 무수히 많다.

kuic. kyonggi. ac. kr/~dssung (2). 분석 결과로부터 I/O interface와 CPU사이의 전송 방법을 결정한다. - Direct I/O, Polled I/O, Interrupt Driven I/O (3). 정보전송을 위한 통로를 I/O Map에 사상(Mapping)한다. - 통로 결정 (4). 전송규약, 전송방법, 사상된 I/O Map을 토대로 I/O Interface를 설계한다. 전송 통로 결정 3 CPU 2 전송 방법 결정 Interface 4 설계 I/O 1 프로토콜 분석

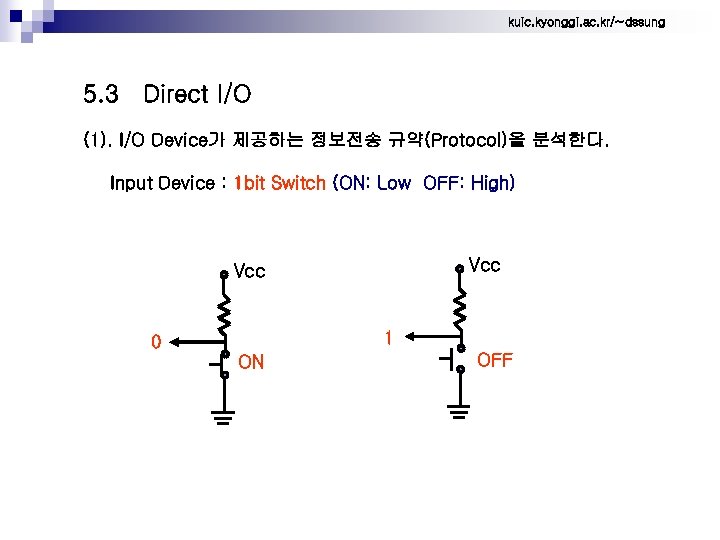

kuic. kyonggi. ac. kr/~dssung 5. 3 Direct I/O (1). I/O Device가 제공하는 정보전송 규약(Protocol)을 분석한다. Input Device : 1 bit Switch (ON: Low OFF: High) Vcc 1 0 ON OFF

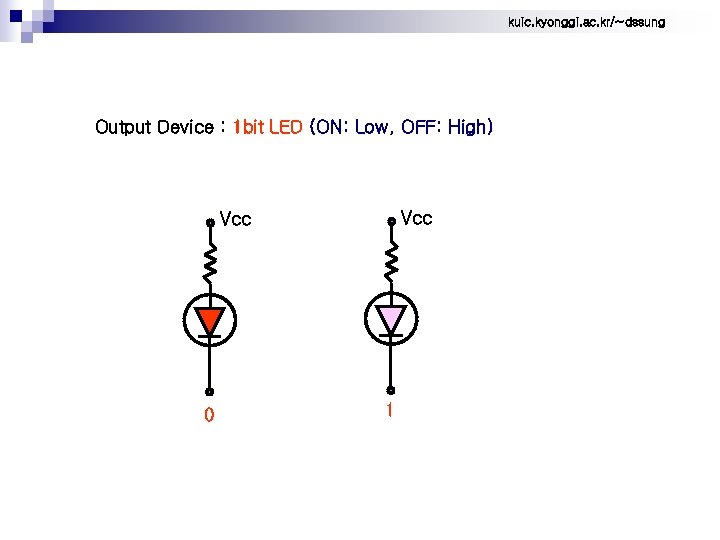

kuic. kyonggi. ac. kr/~dssung Output Device : 1 bit LED (ON: Low, OFF: High) Vcc 0 1

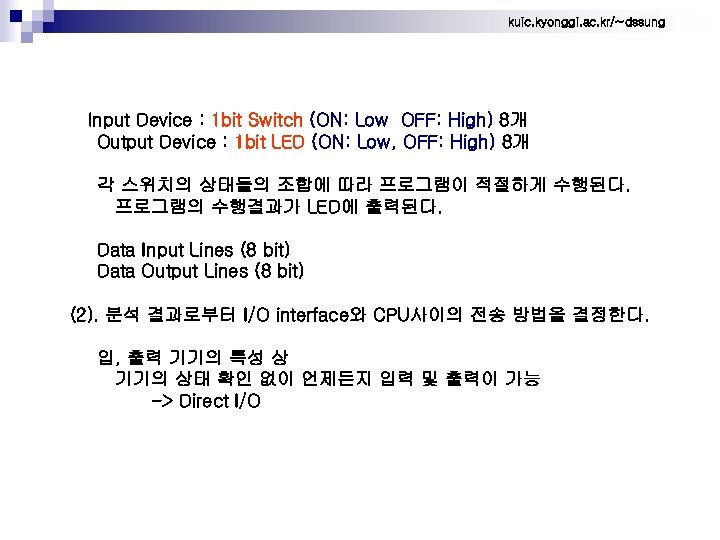

kuic. kyonggi. ac. kr/~dssung Input Device : 1 bit Switch (ON: Low OFF: High) 8개 Output Device : 1 bit LED (ON: Low, OFF: High) 8개 각 스위치의 상태들의 조합에 따라 프로그램이 적절하게 수행된다. 프로그램의 수행결과가 LED에 출력된다. Data Input Lines (8 bit) Data Output Lines (8 bit) (2). 분석 결과로부터 I/O interface와 CPU사이의 전송 방법을 결정한다. 입, 출력 기기의 특성 상 기기의 상태 확인 없이 언제든지 입력 및 출력이 가능 -> Direct I/O

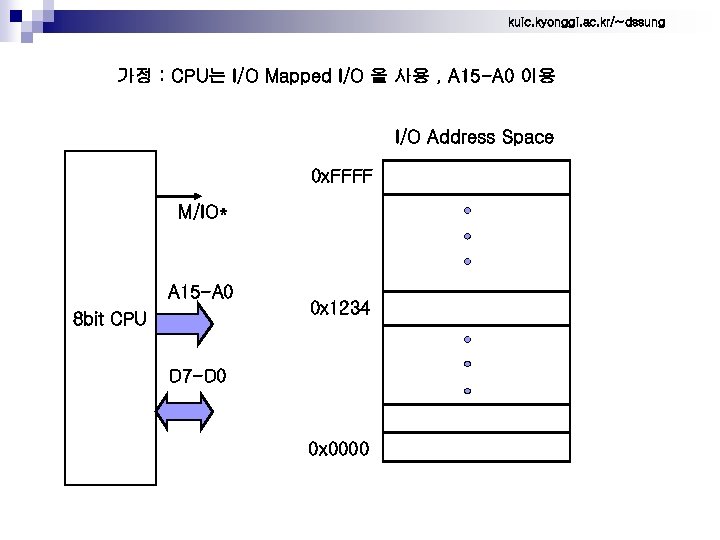

kuic. kyonggi. ac. kr/~dssung 가정 : CPU는 I/O Mapped I/O 을 사용 , A 15 -A 0 이용 I/O Address Space 0 x. FFFF M/IO* A 15 -A 0 8 bit CPU 0 x 1234 D 7 -D 0 0 x 0000

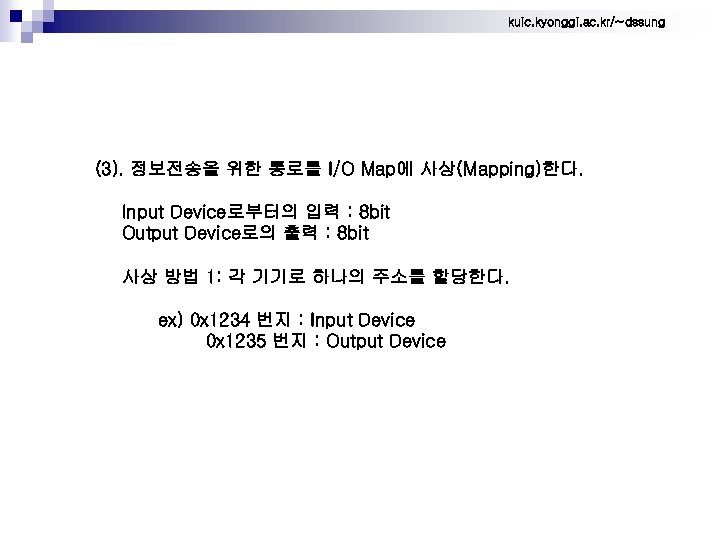

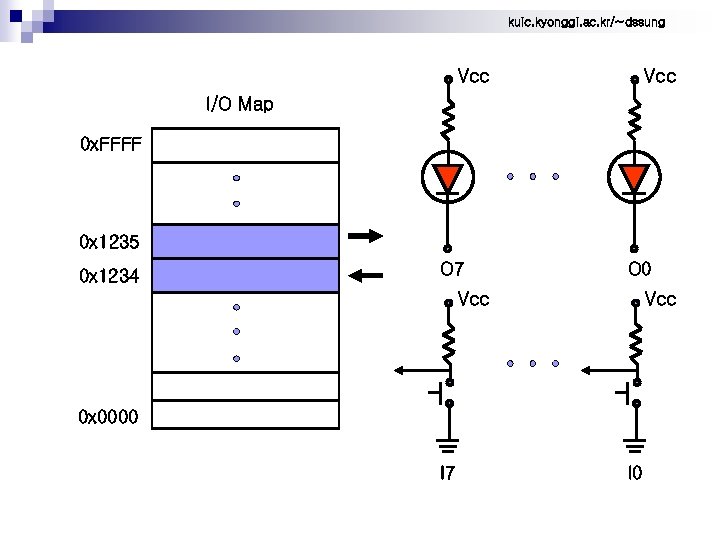

kuic. kyonggi. ac. kr/~dssung (3). 정보전송을 위한 통로를 I/O Map에 사상(Mapping)한다. Input Device로부터의 입력 : 8 bit Output Device로의 출력 : 8 bit 사상 방법 1: 각 기기로 하나의 주소를 할당한다. ex) 0 x 1234 번지 : Input Device 0 x 1235 번지 : Output Device

kuic. kyonggi. ac. kr/~dssung Vcc I/O Map 0 x. FFFF 0 x 1235 0 x 1234 O 7 O 0 Vcc 0 x 0000 I 7 I 0

kuic. kyonggi. ac. kr/~dssung 사상 방법 2: 하나의 주소를 이용하여 입력과 출력이 가능하며 따라서 하나의 주소를 할당한다. ex) 0 x 1234 번지 : Read 시 Input Device로 정보의 입력 Write 시 Output Device로 정보의 출력

kuic. kyonggi. ac. kr/~dssung Vcc I/O Map 0 x. FFFF O 7 0 x 1234 O 0 Vcc 0 x 0000 I 7 I 0

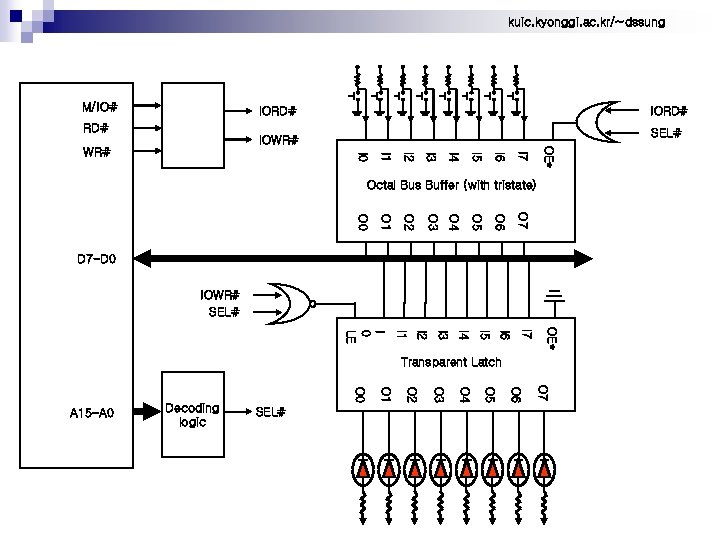

kuic. kyonggi. ac. kr/~dssung (4). 전송규약, 전송방법, 사상된 I/O Map을 토대로 I/O Interface를 설계한다. 아래의 그림은 사상2를 채택

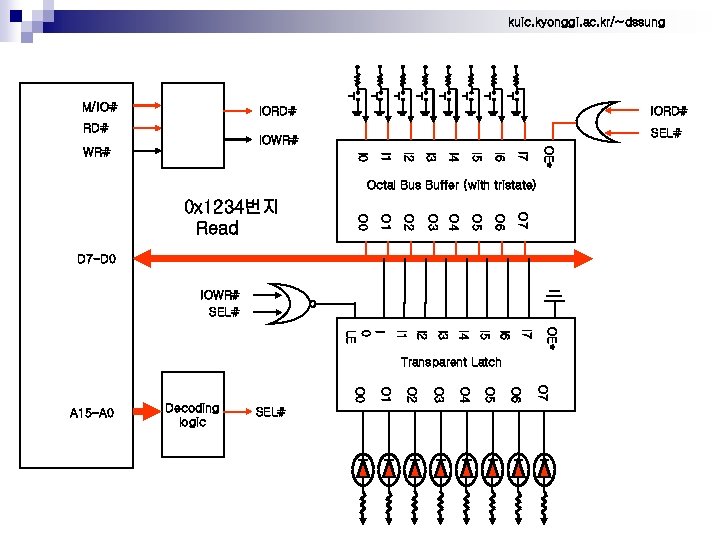

kuic. kyonggi. ac. kr/~dssung M/IO# IORD# RD# SEL# IOWR# OE* I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 WR# Octal Bus Buffer (with tristate) O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 D 7 -D 0 IOWR# SEL# OE* I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 SEL# O 1 Decoding logic O 0 A 15 -A 0

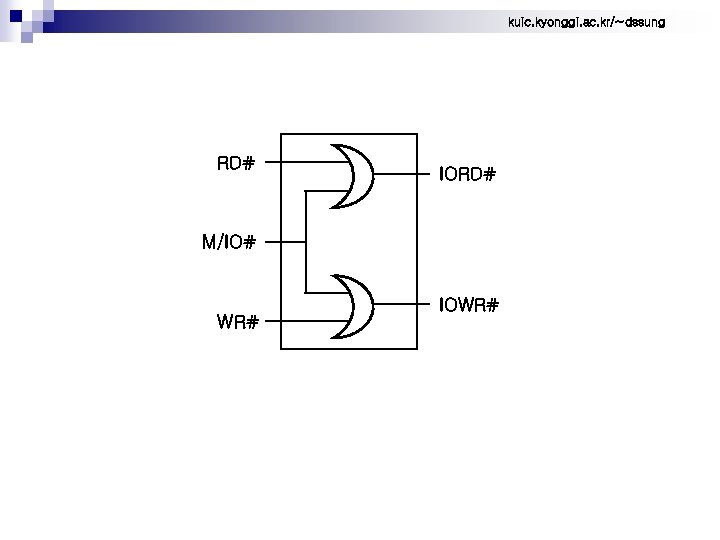

kuic. kyonggi. ac. kr/~dssung RD# IORD# M/IO# WR# IOWR#

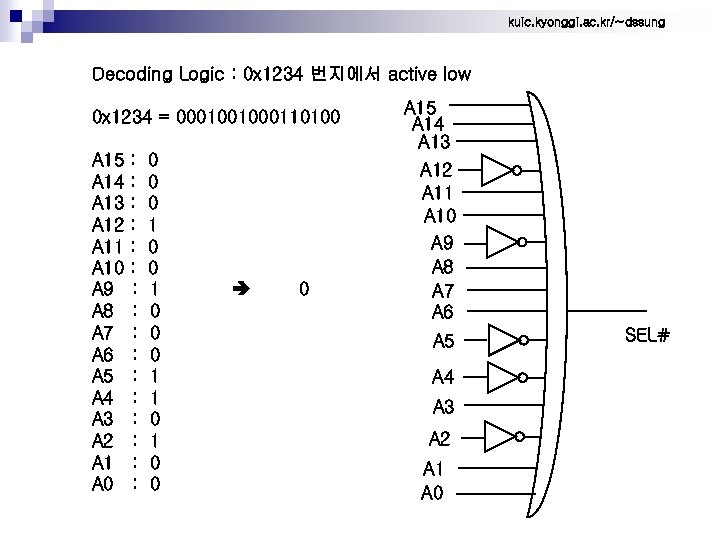

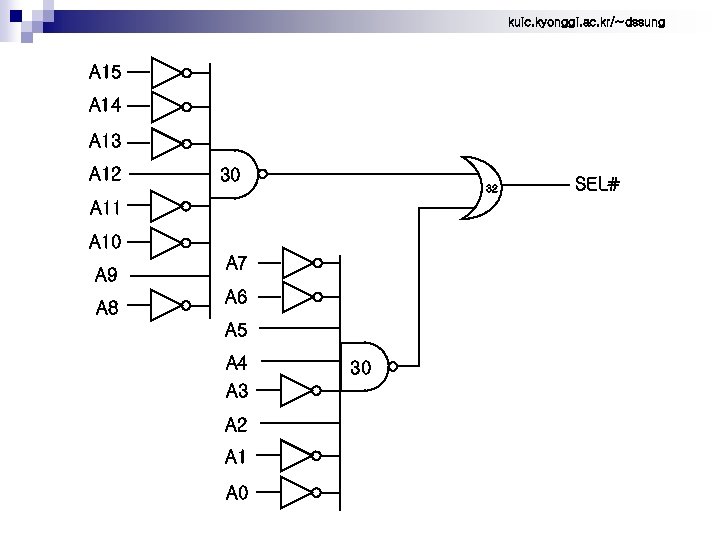

kuic. kyonggi. ac. kr/~dssung Decoding Logic : 0 x 1234 번지에서 active low 0 x 1234 = 0001001000110100 A 15 A 14 A 13 A 12 A 11 A 10 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 : : : : 0 0 0 1 1 0 0 A 15 A 14 A 13 A 12 A 11 A 10 0 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 SEL#

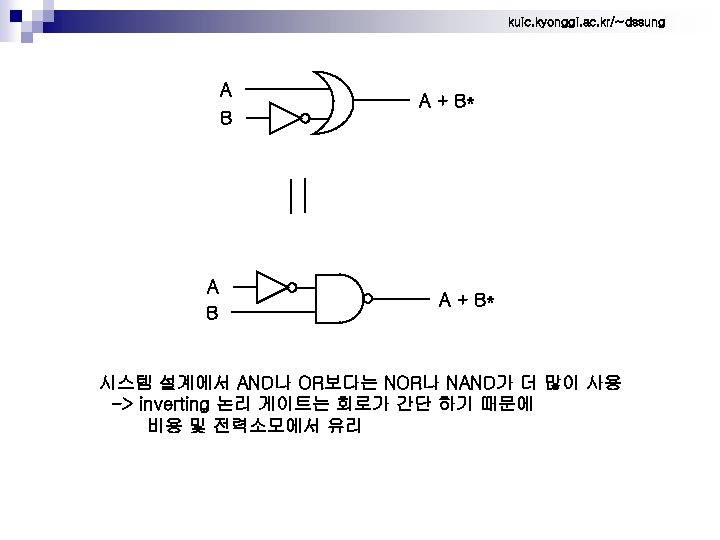

kuic. kyonggi. ac. kr/~dssung A B A + B* 시스템 설계에서 AND나 OR보다는 NOR나 NAND가 더 많이 사용 -> inverting 논리 게이트는 회로가 간단 하기 때문에 비용 및 전력소모에서 유리

kuic. kyonggi. ac. kr/~dssung A 15 A 14 A 13 A 12 30 32 A 11 A 10 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 30 SEL#

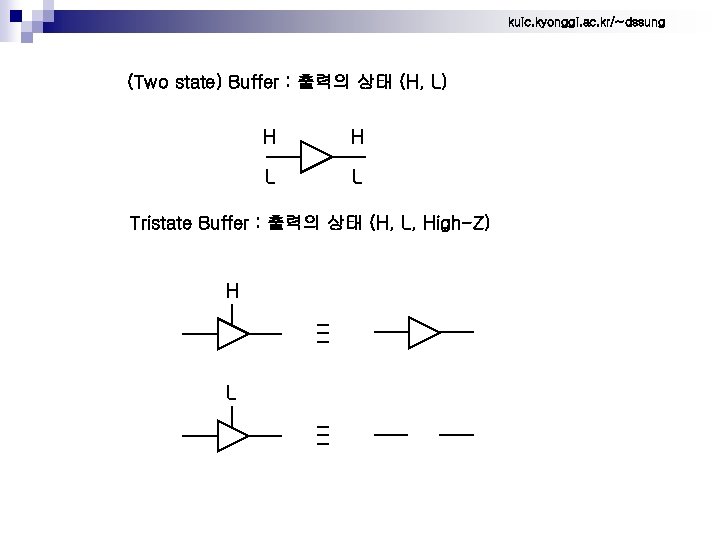

kuic. kyonggi. ac. kr/~dssung (Two state) Buffer : 출력의 상태 (H, L) H H L L Tristate Buffer : 출력의 상태 (H, L, High-Z) H L

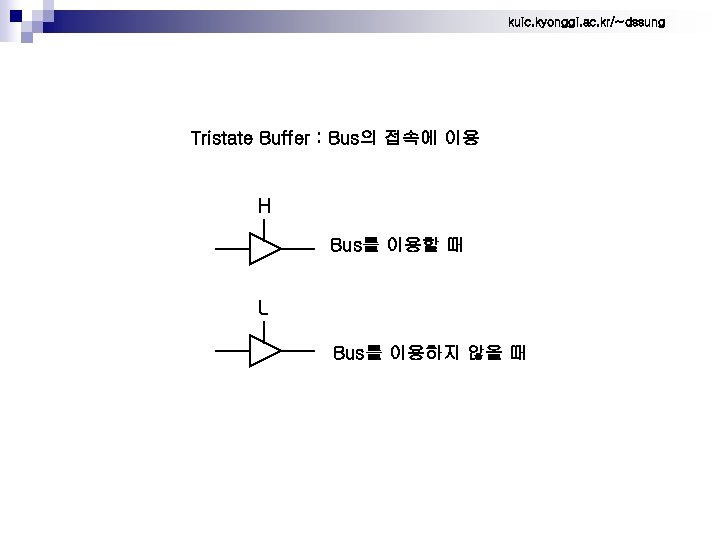

kuic. kyonggi. ac. kr/~dssung Tristate Buffer : Bus의 접속에 이용 H Bus를 이용할 때 L Bus를 이용하지 않을 때

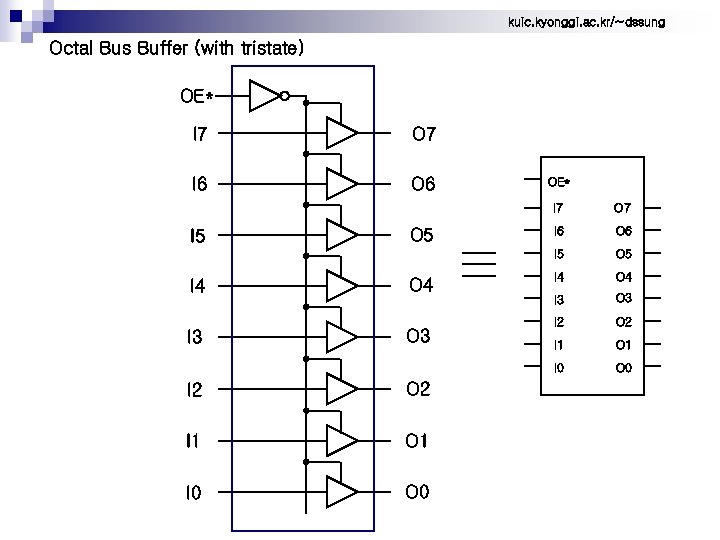

kuic. kyonggi. ac. kr/~dssung Octal Bus Buffer (with tristate) OE* I 7 O 7 I 6 OE* I 7 I 3 O 4 O 3 I 2 O 2 I 1 O 1 I 0 O 6 O 5 I 4 O 4 I 3 O 3 I 2 O 2 I 1 O 1 I 0 I 4 O 5 I 6 I 5 O 7 O 0

kuic. kyonggi. ac. kr/~dssung M/IO# IORD# RD# SEL# IOWR# OE* I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 WR# Octal Bus Buffer (with tristate) O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 0 x 1234번지 Read D 7 -D 0 IOWR# SEL# OE* I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 SEL# O 1 Decoding logic O 0 A 15 -A 0

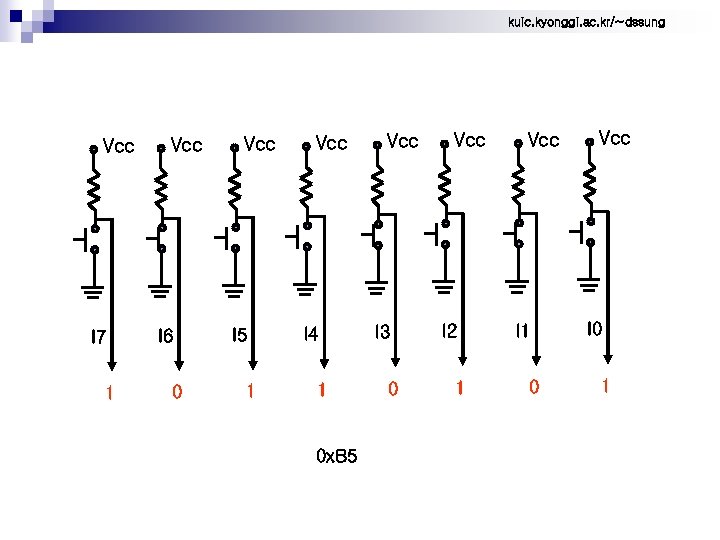

kuic. kyonggi. ac. kr/~dssung Vcc I 7 1 Vcc I 6 0 Vcc I 5 1 Vcc I 4 1 0 x. B 5 Vcc I 3 0 Vcc I 2 1 Vcc I 1 0 Vcc I 0 1

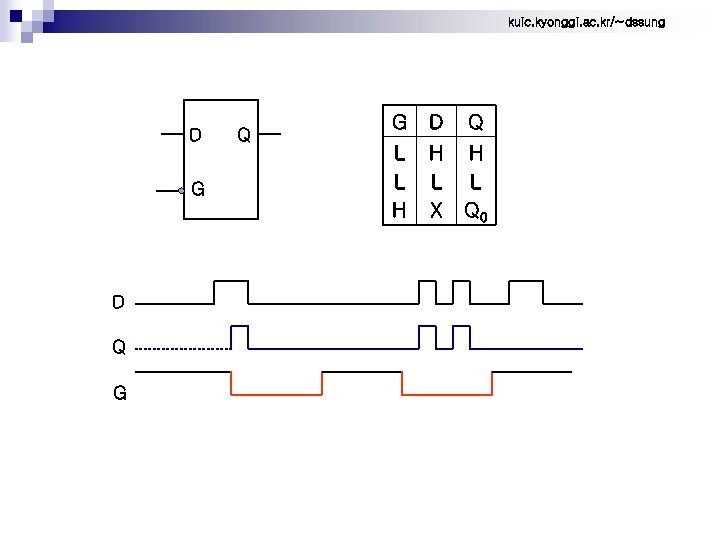

kuic. kyonggi. ac. kr/~dssung Level Triggered D Flip Flops D G Q G D Q H H L X H L Q 0 D Q G Flip Flop의 상태는 제어신호의 순간적인 변화에 의하여 바뀐다. 이 순간적인 변화를 트리거(trigger)라고 한다.

kuic. kyonggi. ac. kr/~dssung D G D Q L L H H L X H L Q 0

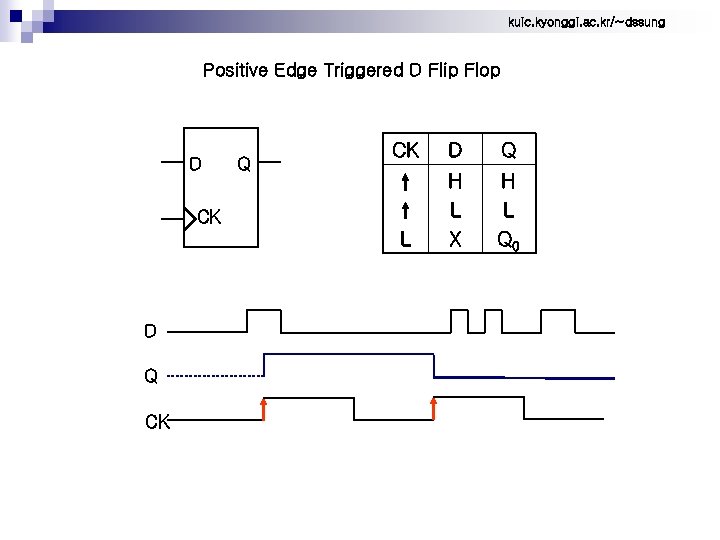

kuic. kyonggi. ac. kr/~dssung Positive Edge Triggered D Flip Flop Q CK D Q L D H L X H L Q 0 CK D Q CK

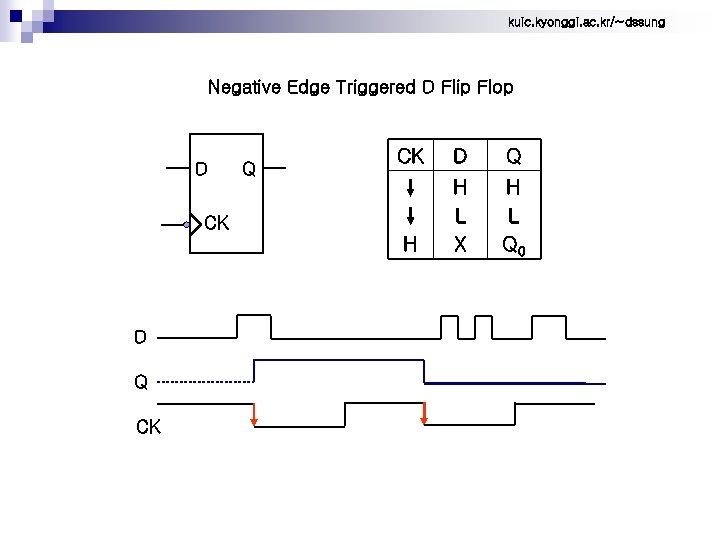

kuic. kyonggi. ac. kr/~dssung Negative Edge Triggered D Flip Flop Q CK D Q H D H L X H L Q 0 CK D Q CK

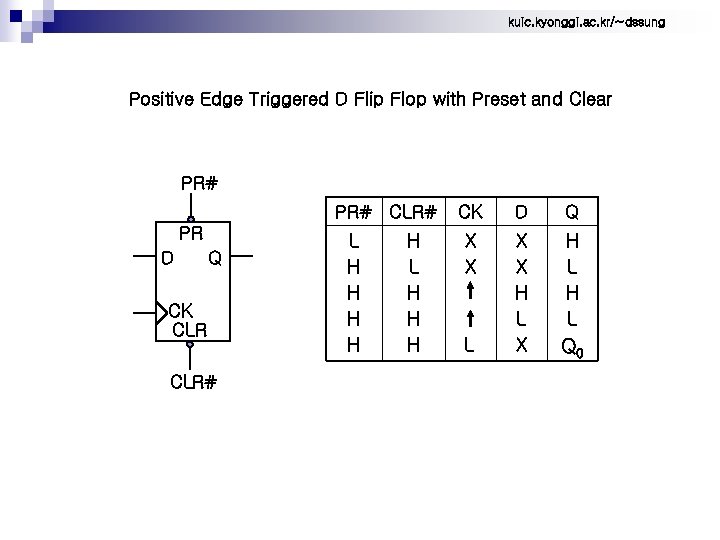

kuic. kyonggi. ac. kr/~dssung Positive Edge Triggered D Flip Flop with Preset and Clear PR# CLR# PR D Q CK CLR# L H H H CK D Q X X H L L Q 0

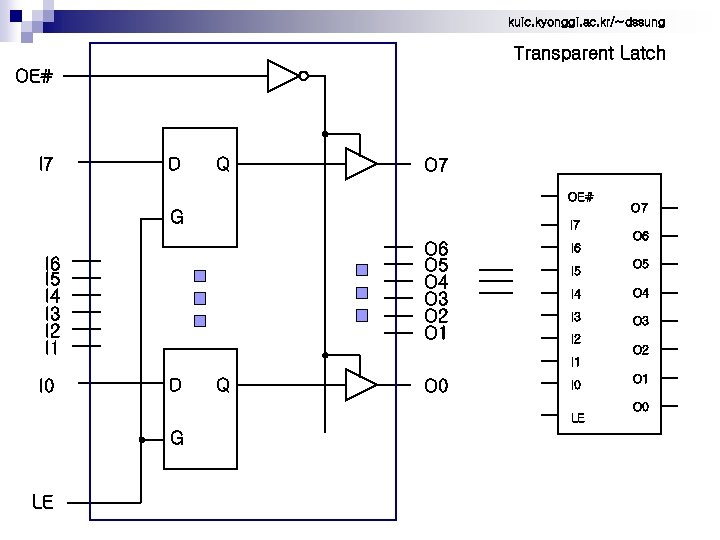

kuic. kyonggi. ac. kr/~dssung Transparent Latch OE# I 7 D Q O 7 OE# G I 7 O 6 O 5 O 4 O 3 O 2 O 1 I 6 I 5 I 4 I 3 I 2 I 1 I 0 Q O 0 I 5 LE O 5 I 4 O 4 I 3 O 3 I 2 I 0 LE G O 6 I 1 D O 7 O 2 O 1 O 0

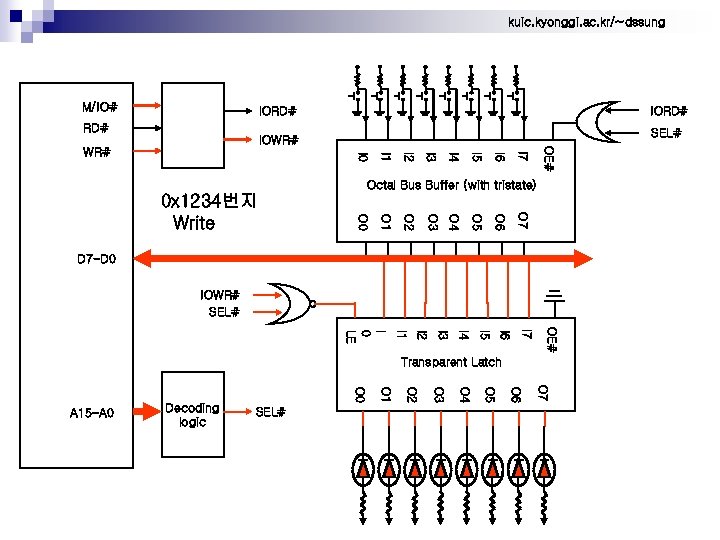

kuic. kyonggi. ac. kr/~dssung M/IO# IORD# RD# SEL# IOWR# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 WR# Octal Bus Buffer (with tristate) O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 0 x 1234번지 Write D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 SEL# O 1 Decoding logic O 0 A 15 -A 0

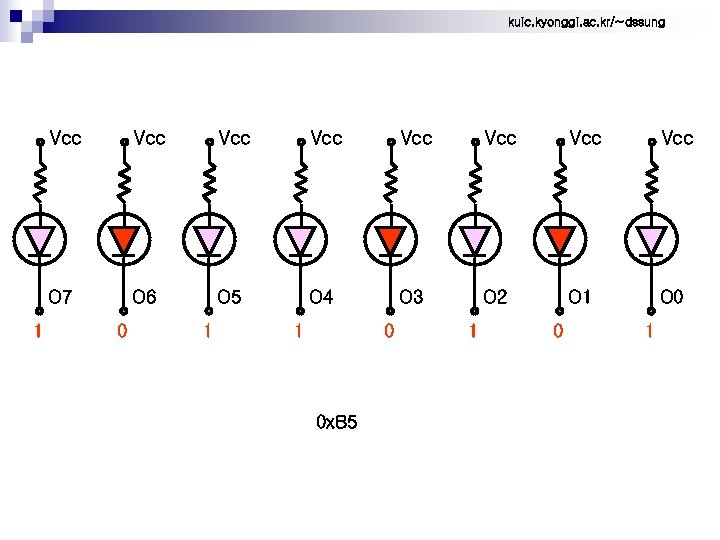

kuic. kyonggi. ac. kr/~dssung Vcc Vcc O 7 1 Vcc O 6 O 5 O 4 O 3 O 2 O 1 O 0 0 1 1 0 0 x. B 5 1 0 1

kuic. kyonggi. ac. kr/~dssung 5. 4 Polled I/O Example) Simple Printer (1). Printer Device가 제공하는 정보전송 규약(Protocol)을 분석한다. control line status line data output lines

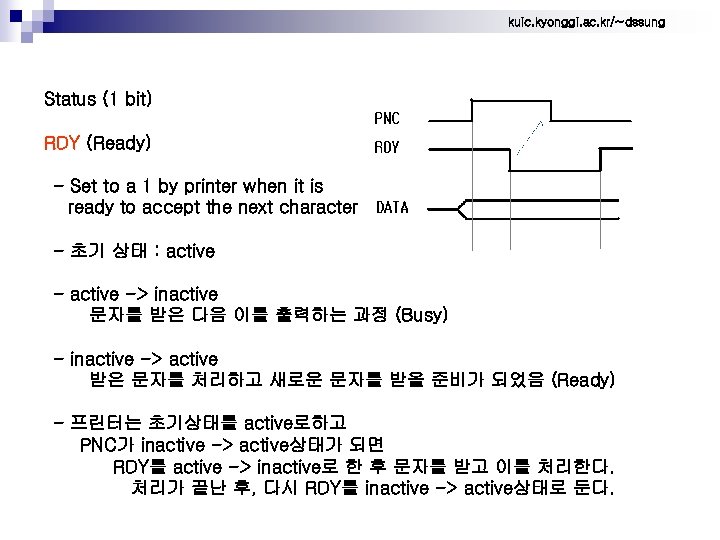

kuic. kyonggi. ac. kr/~dssung Status (1 bit) RDY (Ready) - Set to a 1 by printer when it is ready to accept the next character - 초기 상태 : active -> inactive 문자를 받은 다음 이를 출력하는 과정 (Busy) - inactive -> active 받은 문자를 처리하고 새로운 문자를 받을 준비가 되었음 (Ready) - 프린터는 초기상태를 active로하고 PNC가 inactive -> active상태가 되면 RDY를 active -> inactive로 한 후 문자를 받고 이를 처리한다. 처리가 끝난 후, 다시 RDY를 inactive -> active상태로 둔다.

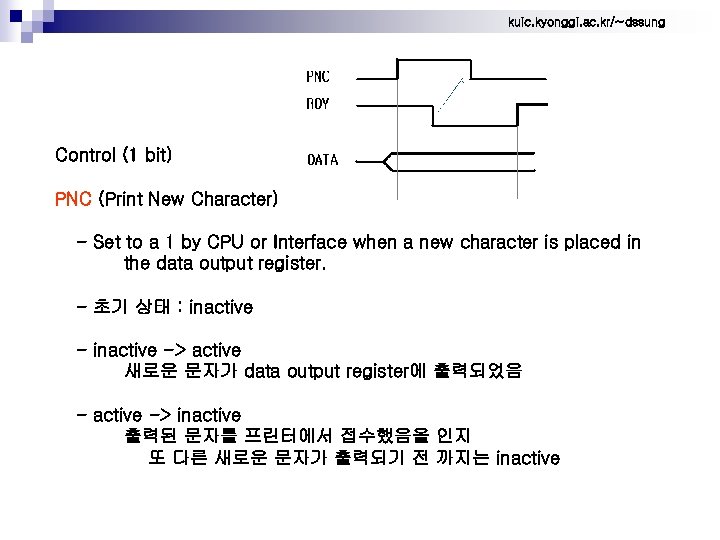

kuic. kyonggi. ac. kr/~dssung Control (1 bit) PNC (Print New Character) - Set to a 1 by CPU or Interface when a new character is placed in the data output register. - 초기 상태 : inactive - inactive -> active 새로운 문자가 data output register에 출력되었음 - active -> inactive 출력된 문자를 프린터에서 접수했음을 인지 또 다른 새로운 문자가 출력되기 전 까지는 inactive

kuic. kyonggi. ac. kr/~dssung Data Output (8 bit) - New character from CPU (2). 분석 결과로부터 I/O interface와 CPU사이의 전송 방법을 결정한다. 프린터가 문자를 받을 준비가 되었을 때 문자를 전송해야 한다. -> Polled I/O or Interrupt Driven I/O

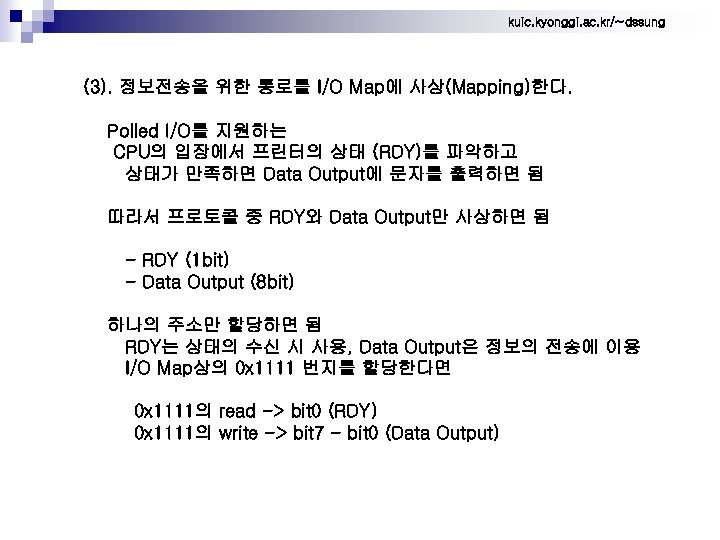

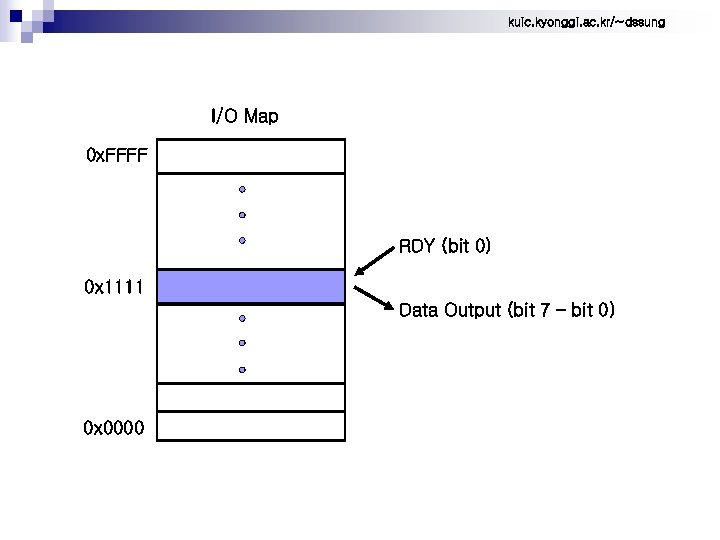

kuic. kyonggi. ac. kr/~dssung (3). 정보전송을 위한 통로를 I/O Map에 사상(Mapping)한다. Polled I/O를 지원하는 CPU의 입장에서 프린터의 상태 (RDY)를 파악하고 상태가 만족하면 Data Output에 문자를 출력하면 됨 따라서 프로토콜 중 RDY와 Data Output만 사상하면 됨 - RDY (1 bit) - Data Output (8 bit) 하나의 주소만 할당하면 됨 RDY는 상태의 수신 시 사용, Data Output은 정보의 전송에 이용 I/O Map상의 0 x 1111 번지를 할당한다면 0 x 1111의 read -> bit 0 (RDY) 0 x 1111의 write -> bit 7 - bit 0 (Data Output)

kuic. kyonggi. ac. kr/~dssung I/O Map 0 x. FFFF RDY (bit 0) 0 x 1111 Data Output (bit 7 – bit 0) 0 x 0000

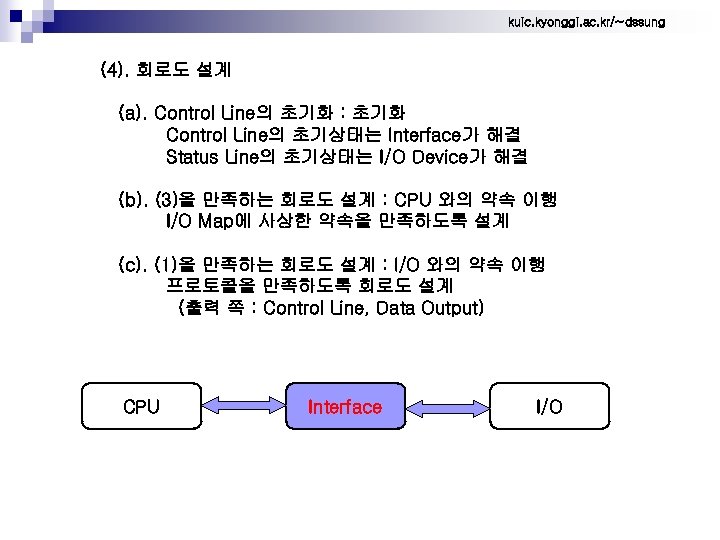

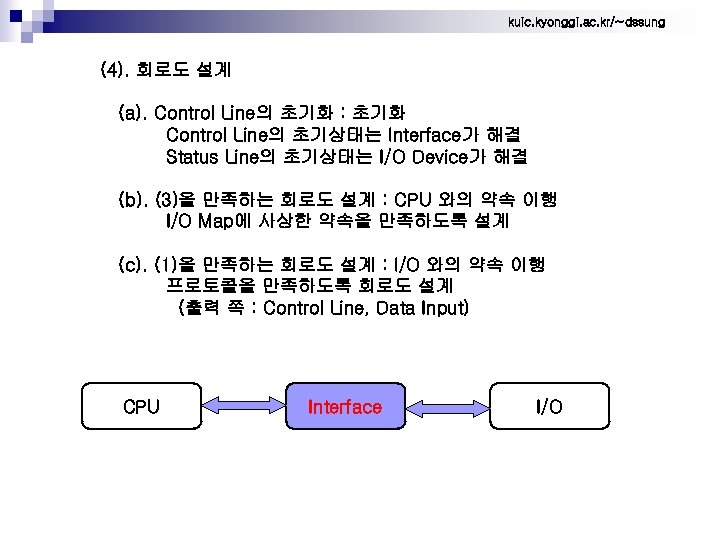

kuic. kyonggi. ac. kr/~dssung (4). 회로도 설계 (a). Control Line의 초기화 : 초기화 Control Line의 초기상태는 Interface가 해결 Status Line의 초기상태는 I/O Device가 해결 (b). (3)을 만족하는 회로도 설계 : CPU 와의 약속 이행 I/O Map에 사상한 약속을 만족하도록 설계 (c). (1)을 만족하는 회로도 설계 : I/O 와의 약속 이행 프로토콜을 만족하도록 회로도 설계 (출력 쪽 : Control Line, Data Output) CPU Interface I/O

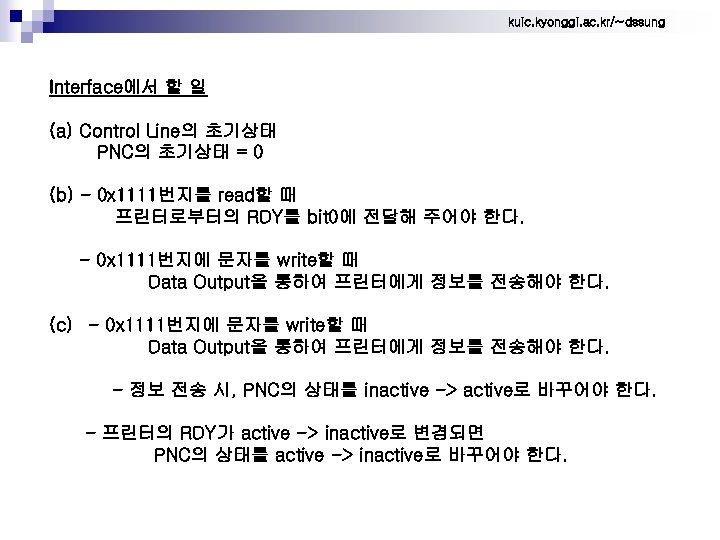

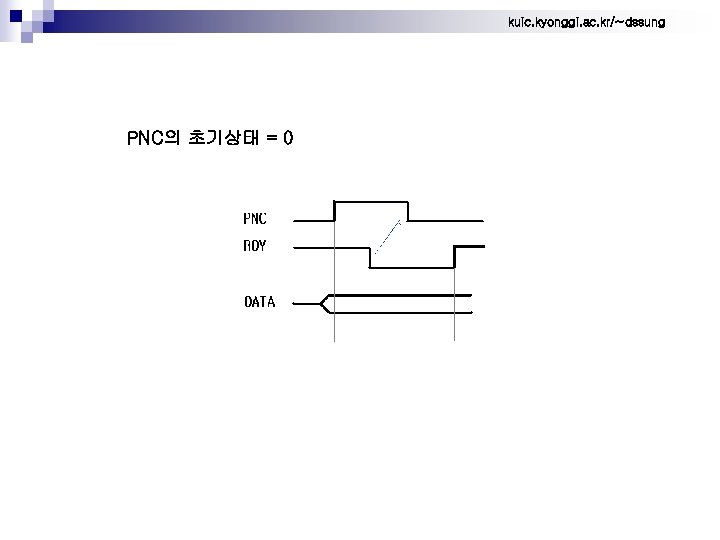

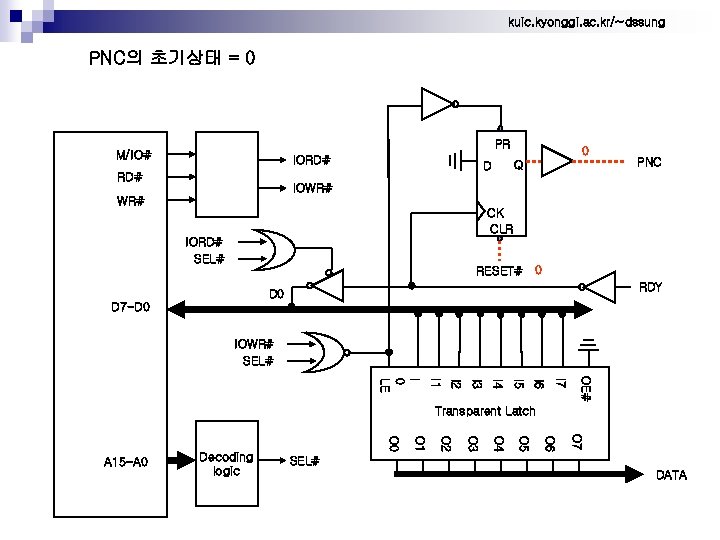

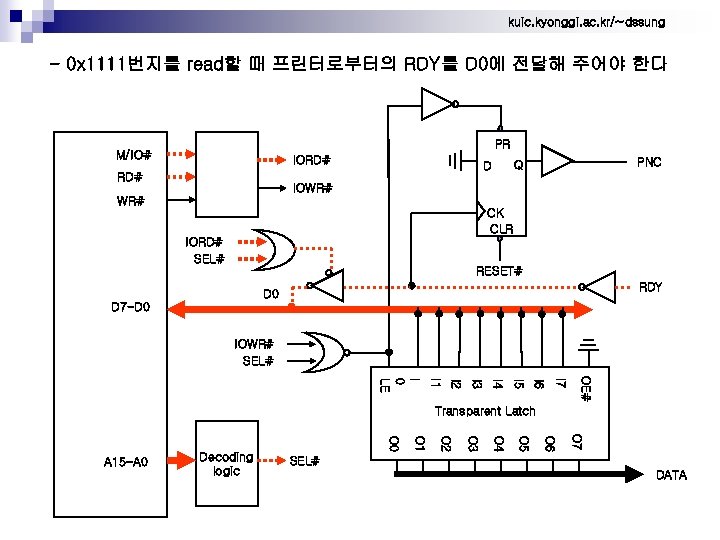

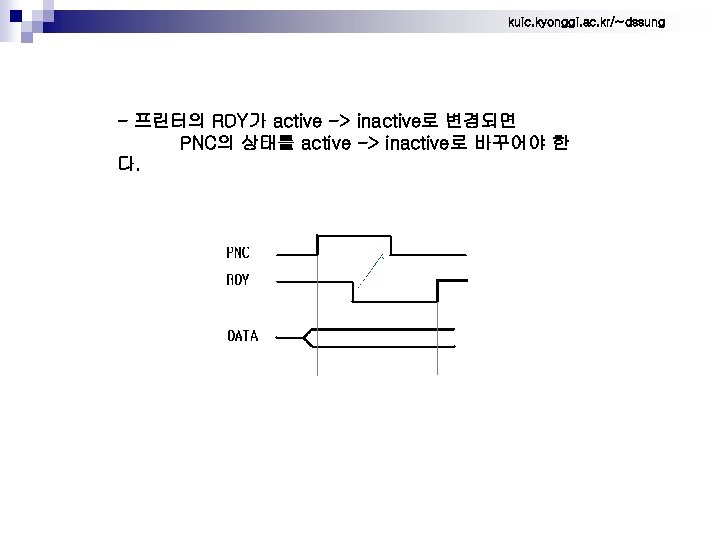

kuic. kyonggi. ac. kr/~dssung Interface에서 할 일 (a) Control Line의 초기상태 PNC의 초기상태 = 0 (b) - 0 x 1111번지를 read할 때 프린터로부터의 RDY를 bit 0에 전달해 주어야 한다. - 0 x 1111번지에 문자를 write할 때 Data Output을 통하여 프린터에게 정보를 전송해야 한다. (c) - 0 x 1111번지에 문자를 write할 때 Data Output을 통하여 프린터에게 정보를 전송해야 한다. - 정보 전송 시, PNC의 상태를 inactive -> active로 바꾸어야 한다. - 프린터의 RDY가 active -> inactive로 변경되면 PNC의 상태를 active -> inactive로 바꾸어야 한다.

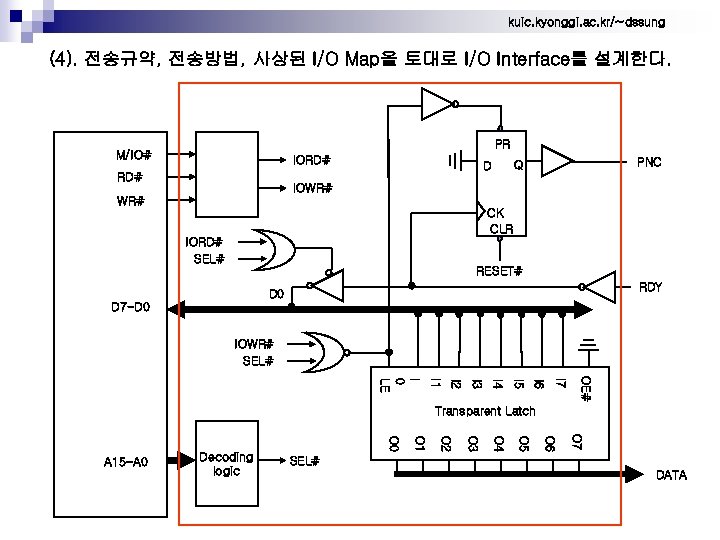

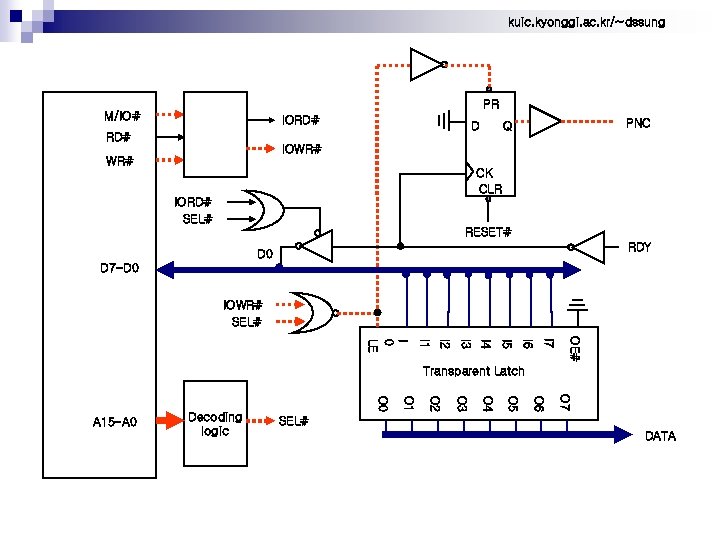

kuic. kyonggi. ac. kr/~dssung (4). 전송규약, 전송방법, 사상된 I/O Map을 토대로 I/O Interface를 설계한다. PR M/IO# IORD# PNC Q D IOWR# CK CLR IORD# SEL# RESET# RDY D 0 D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 O 1 Decoding logic O 0 A 15 -A 0 SEL# DATA

kuic. kyonggi. ac. kr/~dssung PNC의 초기상태 = 0

kuic. kyonggi. ac. kr/~dssung PNC의 초기상태 = 0 PR M/IO# IORD# 0 Q D PNC IOWR# CK CLR IORD# SEL# RESET# 0 RDY D 0 D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 O 1 Decoding logic O 0 A 15 -A 0 SEL# DATA

kuic. kyonggi. ac. kr/~dssung - 0 x 1111번지를 read할 때 프린터로부터의 RDY를 D 0에 전달해 주어야 한다 PR M/IO# IORD# PNC Q D IOWR# CK CLR IORD# SEL# RESET# RDY D 0 D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 O 1 Decoding logic O 0 A 15 -A 0 SEL# DATA

kuic. kyonggi. ac. kr/~dssung - 0 x 1111번지에 문자를 write할 때 Data Output을 통하여 프린터에게 정보를 전송해야 한다. PNC의 상태를 inactive -> active로 바꾸어야 한다.

kuic. kyonggi. ac. kr/~dssung PR M/IO# IORD# PNC Q D IOWR# CK CLR IORD# SEL# RESET# RDY D 0 D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 O 1 Decoding logic O 0 A 15 -A 0 SEL# DATA

kuic. kyonggi. ac. kr/~dssung - 프린터의 RDY가 active -> inactive로 변경되면 PNC의 상태를 active -> inactive로 바꾸어야 한 다.

kuic. kyonggi. ac. kr/~dssung PR M/IO# IORD# PNC Q D IOWR# CK CLR IORD# SEL# RESET# RDY D 0 D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 O 1 Decoding logic O 0 A 15 -A 0 SEL# DATA

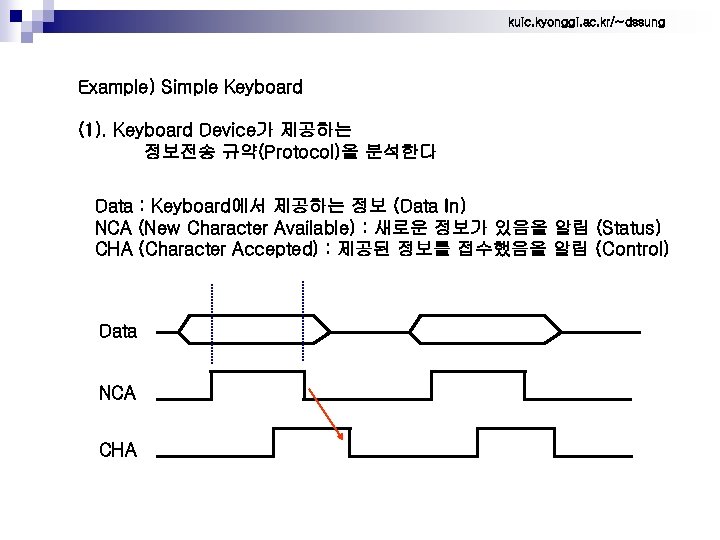

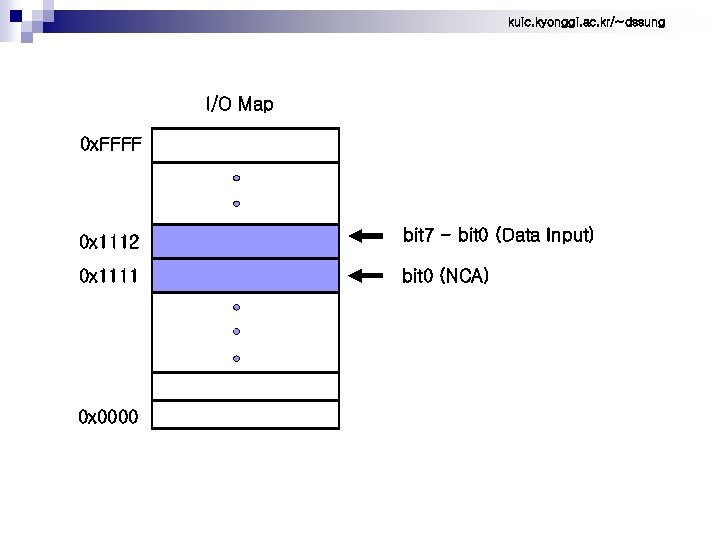

kuic. kyonggi. ac. kr/~dssung Example) Simple Keyboard (1). Keyboard Device가 제공하는 정보전송 규약(Protocol)을 분석한다 Data : Keyboard에서 제공하는 정보 (Data In) NCA (New Character Available) : 새로운 정보가 있음을 알림 (Status) CHA (Character Accepted) : 제공된 정보를 접수했음을 알림 (Control) Data NCA CHA

kuic. kyonggi. ac. kr/~dssung Data Input (8 bit) - New character from Keyboard

kuic. kyonggi. ac. kr/~dssung Status (1 bit) NCA (New Character Available) - Set to a 1 by keyboard when a new character is placed in the data input register. - 초기 상태 : inactive -> active 새로운 문자가 제공되었음을 알림 - active -> inactive 제공된 문자를 CPU에서 접수했음을 인지 또 다른 새로운 문자가 제공되기 전 까지는 inactive

kuic. kyonggi. ac. kr/~dssung Control (1 bit) CHA (Character Accepted) - Set to a 1 by CPU after reading a new character from the data input register. - 초기 상태 : inactive - inactive -> active 제공된 문자를 받았음을 알림 - active -> inactive NCA가 active에서 inactive 상태가 되면 제공된 제어정보(제공된 문자를 받았음을 알림 )를 인지했음을 의미하며 따라서 상태를 inactive로 바꿈

kuic. kyonggi. ac. kr/~dssung (2). 분석 결과로부터 I/O interface와 CPU사이의 전송 방법을 결정한다. Keyboard 문자를 제공했을 때 CPU는 문자를 받을 수 있다. -> Polled I/O or Interrupt Driven I/O

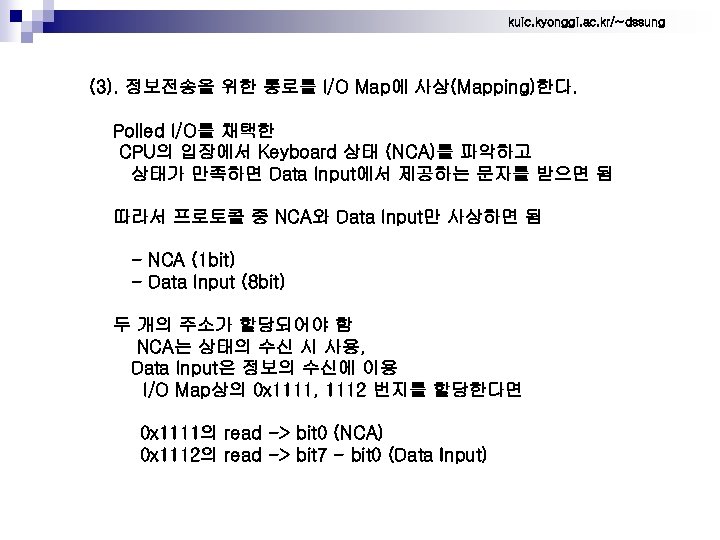

kuic. kyonggi. ac. kr/~dssung (3). 정보전송을 위한 통로를 I/O Map에 사상(Mapping)한다. Polled I/O를 채택한 CPU의 입장에서 Keyboard 상태 (NCA)를 파악하고 상태가 만족하면 Data Input에서 제공하는 문자를 받으면 됨 따라서 프로토콜 중 NCA와 Data Input만 사상하면 됨 - NCA (1 bit) - Data Input (8 bit) 두 개의 주소가 할당되어야 함 NCA는 상태의 수신 시 사용, Data Input은 정보의 수신에 이용 I/O Map상의 0 x 1111, 1112 번지를 할당한다면 0 x 1111의 read -> bit 0 (NCA) 0 x 1112의 read -> bit 7 - bit 0 (Data Input)

kuic. kyonggi. ac. kr/~dssung I/O Map 0 x. FFFF 0 x 1112 bit 7 - bit 0 (Data Input) 0 x 1111 bit 0 (NCA) 0 x 0000

kuic. kyonggi. ac. kr/~dssung Data NCA CHA

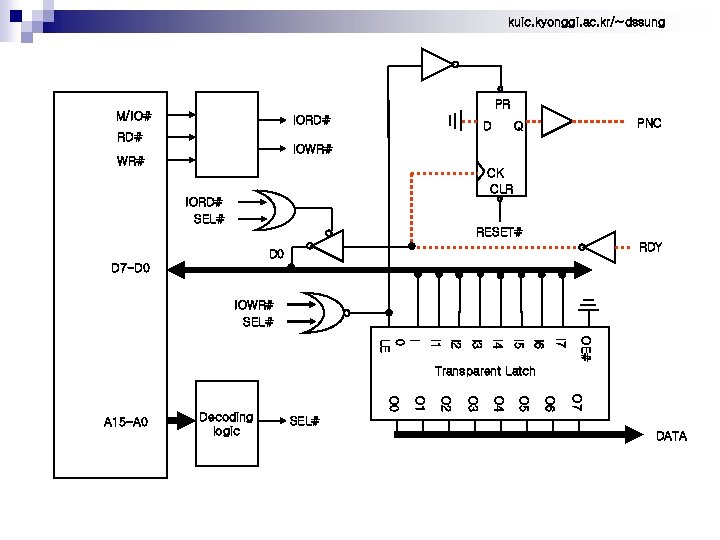

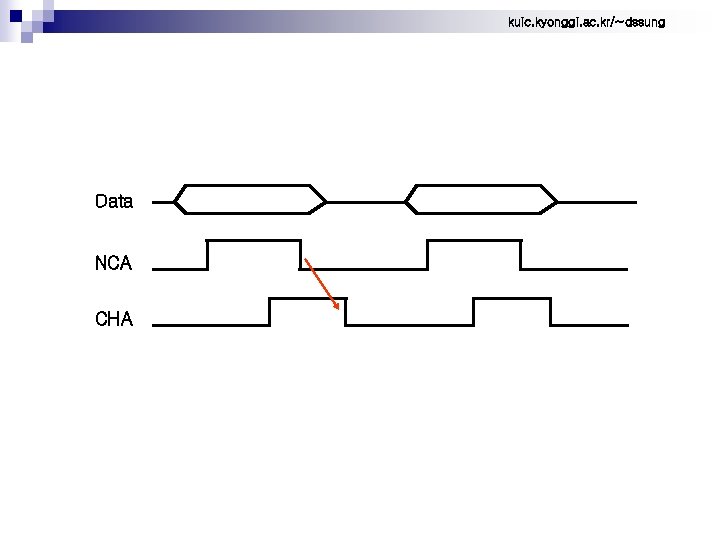

kuic. kyonggi. ac. kr/~dssung (4). 회로도 설계 (a). Control Line의 초기화 : 초기화 Control Line의 초기상태는 Interface가 해결 Status Line의 초기상태는 I/O Device가 해결 (b). (3)을 만족하는 회로도 설계 : CPU 와의 약속 이행 I/O Map에 사상한 약속을 만족하도록 설계 (c). (1)을 만족하는 회로도 설계 : I/O 와의 약속 이행 프로토콜을 만족하도록 회로도 설계 (출력 쪽 : Control Line, Data Input) CPU Interface I/O

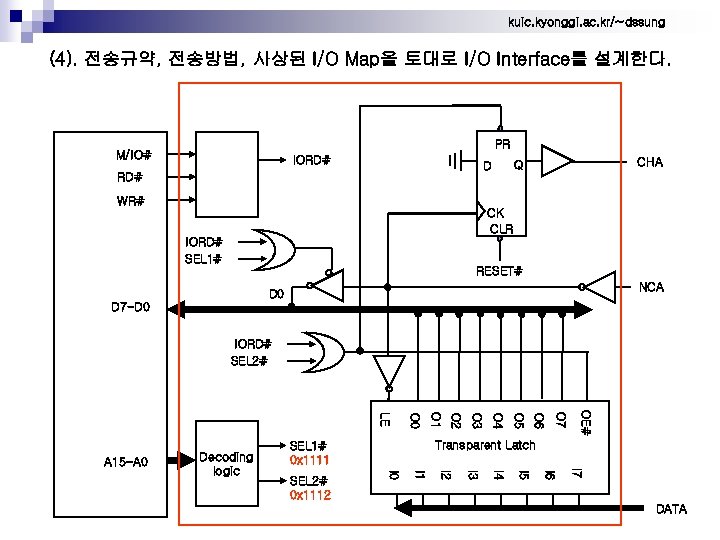

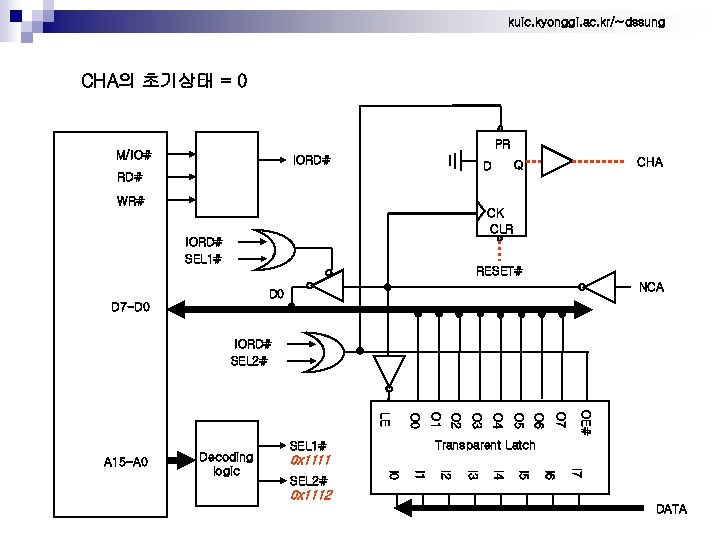

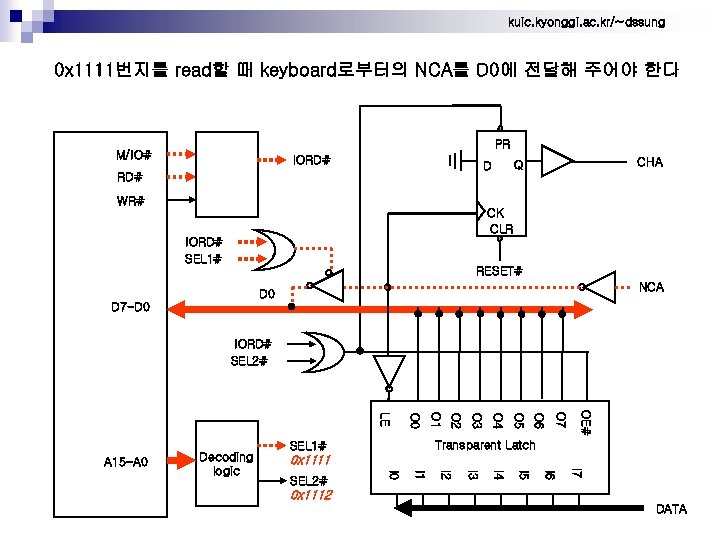

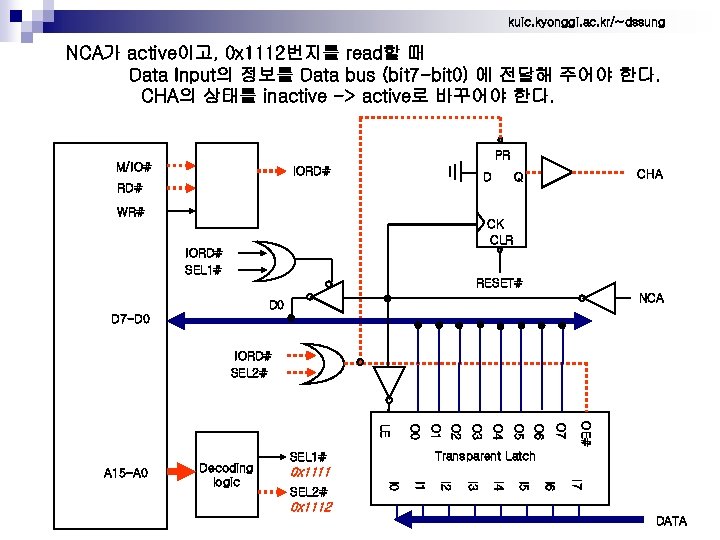

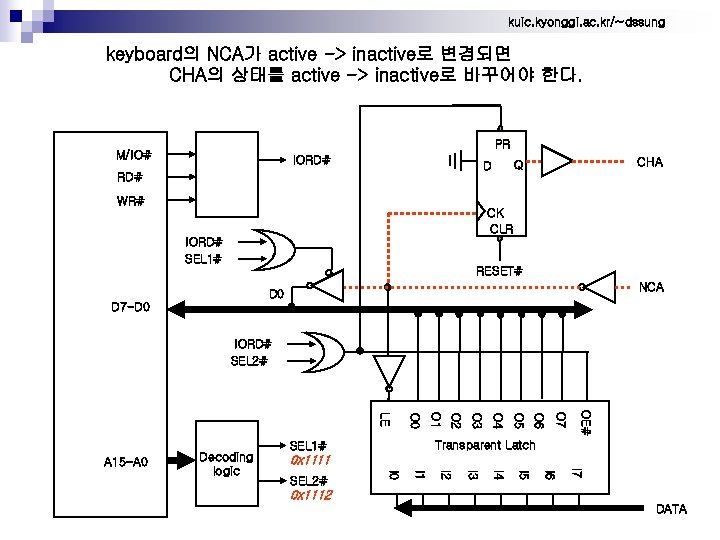

kuic. kyonggi. ac. kr/~dssung Interface에서 할 일 (a) CHA의 초기상태 = 0 (b) - 0 x 1111번지를 read할 때 keyboard로부터의 NCA를 bit 0에 전달해 주어야 한다. - NCA가 active이고, 0 x 1112번지를 read할 때 Data Input의 정보를 Data bus (bit 7 -bit 0) 에 전달해 주어야 한다. (c) - NCA가 active이고, 0 x 1112번지를 read할 때 Data Input의 정보를 Data bus (bit 7 -bit 0) 에 전달해 주어야 한다. - 정보 입력 시 CHA의 상태를 inactive -> active로 바꾸어야 한다. - keyboard의 NCA가 active -> inactive로 변경되면 CHA의 상태를 active -> inactive로 바꾸어야 한다.

kuic. kyonggi. ac. kr/~dssung (4). 전송규약, 전송방법, 사상된 I/O Map을 토대로 I/O Interface를 설계한다. PR M/IO# IORD# CHA Q D WR# CK CLR IORD# SEL 1# RESET# NCA D 0 D 7 -D 0 IORD# SEL 2# OE# O 7 O 6 O 5 O 4 O 3 O 2 Transparent Latch SEL 1# 0 x 1111 I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 SEL 2# 0 x 1112 O 1 O 0 LE A 15 -A 0 Decoding logic DATA

kuic. kyonggi. ac. kr/~dssung CHA의 초기상태 = 0 PR M/IO# IORD# CHA Q D WR# CK CLR IORD# SEL 1# RESET# NCA D 0 D 7 -D 0 IORD# SEL 2# OE# O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 LE A 15 -A 0 Transparent Latch SEL 1# 0 x 1111 I 7 I 6 I 5 I 4 I 3 I 2 I 1 SEL 2# I 0 Decoding logic 0 x 1112 DATA

kuic. kyonggi. ac. kr/~dssung 0 x 1111번지를 read할 때 keyboard로부터의 NCA를 D 0에 전달해 주어야 한다 PR M/IO# IORD# CHA Q D WR# CK CLR IORD# SEL 1# RESET# NCA D 0 D 7 -D 0 IORD# SEL 2# OE# O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 LE A 15 -A 0 Transparent Latch SEL 1# 0 x 1111 I 7 I 6 I 5 I 4 I 3 I 2 I 1 SEL 2# I 0 Decoding logic 0 x 1112 DATA

kuic. kyonggi. ac. kr/~dssung NCA가 active이고, 0 x 1112번지를 read할 때 Data Input의 정보를 Data bus (bit 7 -bit 0) 에 전달해 주어야 한다. CHA의 상태를 inactive -> active로 바꾸어야 한다. PR M/IO# IORD# CHA Q D WR# CK CLR IORD# SEL 1# RESET# NCA D 0 D 7 -D 0 IORD# SEL 2# OE# O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 LE A 15 -A 0 Transparent Latch SEL 1# 0 x 1111 I 7 I 6 I 5 I 4 I 3 I 2 I 1 SEL 2# I 0 Decoding logic 0 x 1112 DATA

kuic. kyonggi. ac. kr/~dssung keyboard의 NCA가 active -> inactive로 변경되면 CHA의 상태를 active -> inactive로 바꾸어야 한다. PR M/IO# IORD# CHA Q D WR# CK CLR IORD# SEL 1# RESET# NCA D 0 D 7 -D 0 IORD# SEL 2# OE# O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 LE A 15 -A 0 Transparent Latch SEL 1# 0 x 1111 I 7 I 6 I 5 I 4 I 3 I 2 I 1 SEL 2# I 0 Decoding logic 0 x 1112 DATA

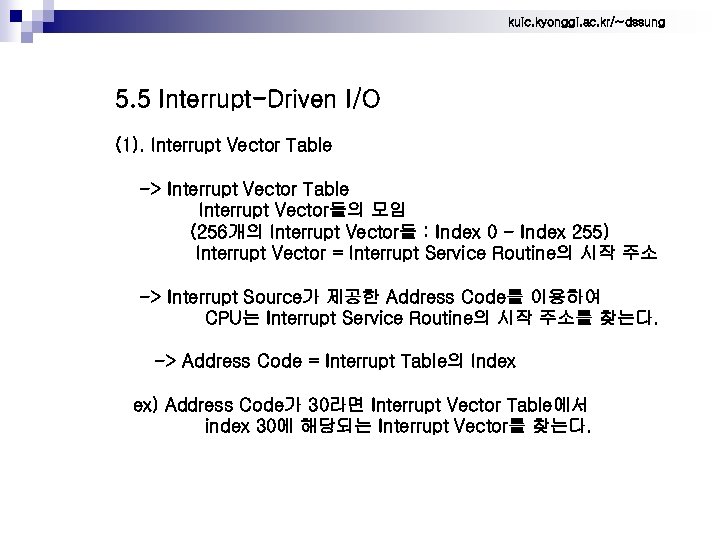

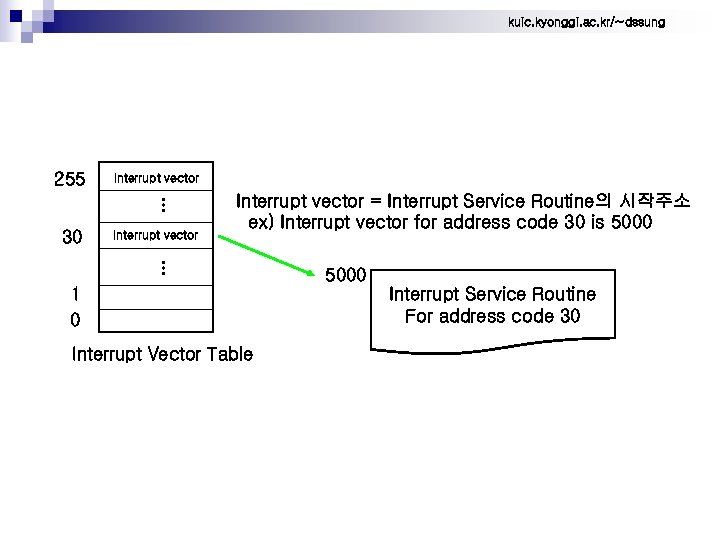

kuic. kyonggi. ac. kr/~dssung 5. 5 Interrupt-Driven I/O (1). Interrupt Vector Table -> Interrupt Vector Table Interrupt Vector들의 모임 (256개의 Interrupt Vector들 : Index 0 - Index 255) Interrupt Vector = Interrupt Service Routine의 시작 주소 -> Interrupt Source가 제공한 Address Code를 이용하여 CPU는 Interrupt Service Routine의 시작 주소를 찾는다. -> Address Code = Interrupt Table의 Index ex) Address Code가 30라면 Interrupt Vector Table에서 index 30에 해당되는 Interrupt Vector를 찾는다.

kuic. kyonggi. ac. kr/~dssung 255 Interrupt vector … 30 Interrupt vector = Interrupt Service Routine의 시작주소 ex) Interrupt vector for address code 30 is 5000 … 1 0 Interrupt Vector Table 5000 Interrupt Service Routine For address code 30

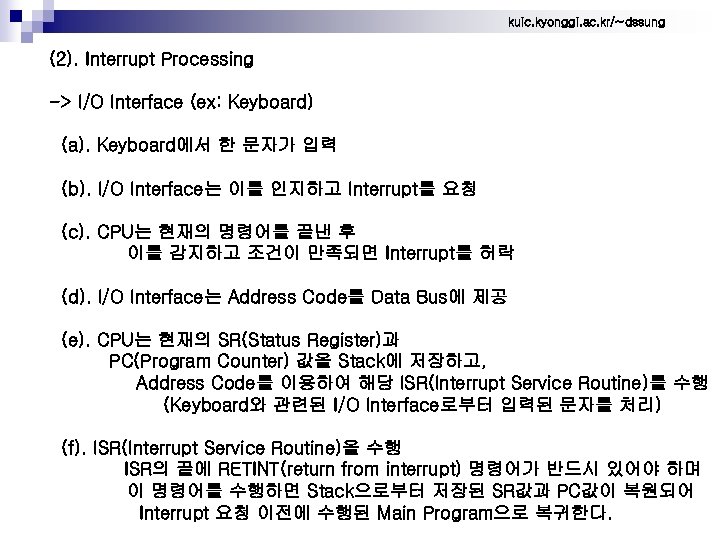

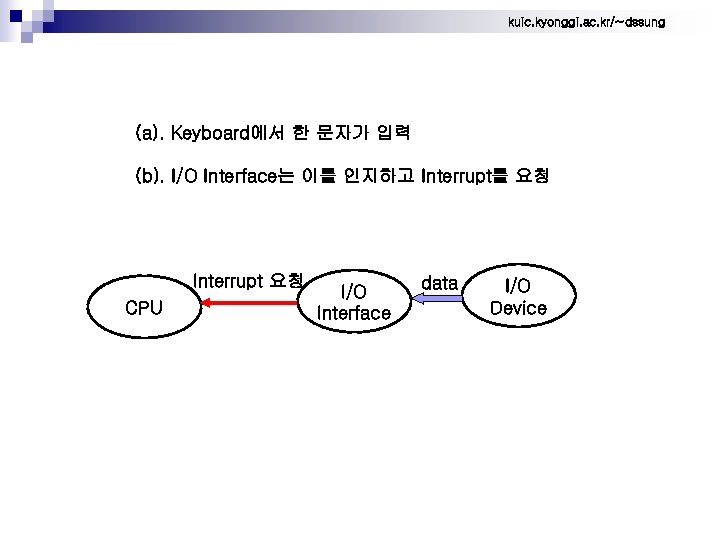

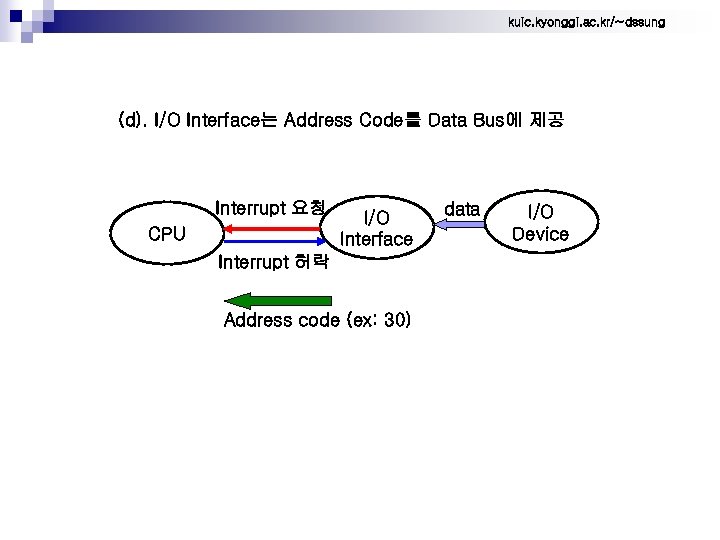

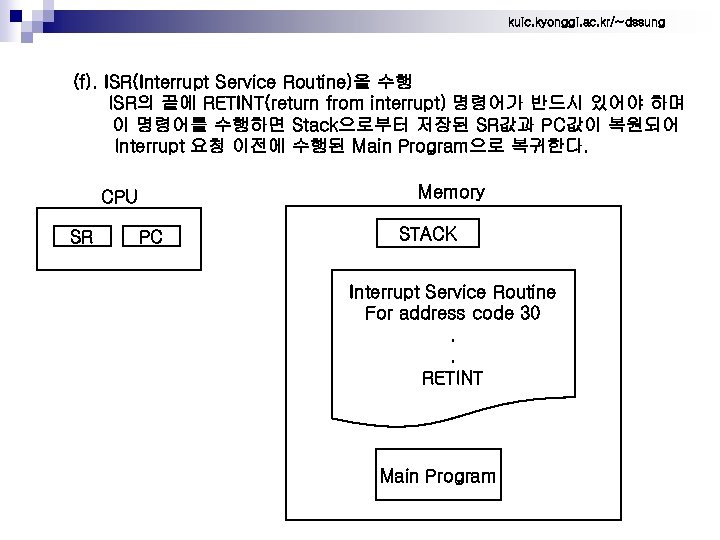

kuic. kyonggi. ac. kr/~dssung (2). Interrupt Processing -> I/O Interface (ex: Keyboard) (a). Keyboard에서 한 문자가 입력 (b). I/O Interface는 이를 인지하고 Interrupt를 요청 (c). CPU는 현재의 명령어를 끝낸 후 이를 감지하고 조건이 만족되면 Interrupt를 허락 (d). I/O Interface는 Address Code를 Data Bus에 제공 (e). CPU는 현재의 SR(Status Register)과 PC(Program Counter) 값을 Stack에 저장하고, Address Code를 이용하여 해당 ISR(Interrupt Service Routine)를 수행 (Keyboard와 관련된 I/O Interface로부터 입력된 문자를 처리) (f). ISR(Interrupt Service Routine)을 수행 ISR의 끝에 RETINT(return from interrupt) 명령어가 반드시 있어야 하며 이 명령어를 수행하면 Stack으로부터 저장된 SR값과 PC값이 복원되어 Interrupt 요청 이전에 수행된 Main Program으로 복귀한다.

kuic. kyonggi. ac. kr/~dssung (a). Keyboard에서 한 문자가 입력 (b). I/O Interface는 이를 인지하고 Interrupt를 요청 Interrupt 요청 CPU I/O Interface data I/O Device

kuic. kyonggi. ac. kr/~dssung (c). CPU는 현재의 명령어를 끝낸 후 이를 감지하고 조건이 만족되면 Interrupt를 허락 Interrupt 요청 CPU Interrupt 허락 Memory Interface Memory Device I/O Interface data I/O Device

kuic. kyonggi. ac. kr/~dssung (d). I/O Interface는 Address Code를 Data Bus에 제공 Interrupt 요청 CPU I/O Interface Interrupt 허락 Address code (ex: 30) data I/O Device

kuic. kyonggi. ac. kr/~dssung (e). CPU는 현재의 SR (Status Register)과 PC (Program Counter) 값을 Stack에 저장하고, Address Code를 이용하여 해당 ISR (Interrupt Service Routine)를 수행 (Keyboard와 관련된 I/O Interface로부터 입력된 문자를 처리) Memory CPU SR STACK PC Interrupt vector 30 Interrupt vector … 255 Interrupt Service Routine For address code 30 … 1 0 Interrupt Vector Table

kuic. kyonggi. ac. kr/~dssung (f). ISR(Interrupt Service Routine)을 수행 ISR의 끝에 RETINT(return from interrupt) 명령어가 반드시 있어야 하며 이 명령어를 수행하면 Stack으로부터 저장된 SR값과 PC값이 복원되어 Interrupt 요청 이전에 수행된 Main Program으로 복귀한다. Memory CPU SR PC STACK Interrupt Service Routine For address code 30. . RETINT Main Program

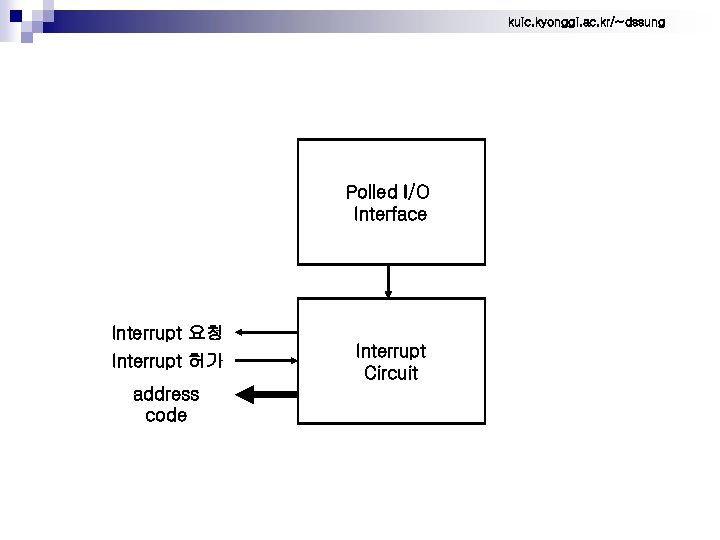

kuic. kyonggi. ac. kr/~dssung (3). External Interrupt Circuits Interrupt Driven I/O에서는 Interface가 조건이 만족하면 Interrupt를 요청하는 회로 및 CPU에서 인터럽트를 허용할 때 Address Code를 제공하는 회로가 필요하다. 이를 External Interrupt Circuit라 한다. 따라서 Interrupt Driven I/O에서는 Polled Driven I/O에서의 Interface회로에 External Interrupt Circuit가 추가되어야 함을 알 수 있다.

kuic. kyonggi. ac. kr/~dssung Polled I/O Interface Interrupt 요청 Interrupt 허가 address code Interrupt Circuit

kuic. kyonggi. ac. kr/~dssung Interrupt Circuit에서 고려 사항 - 조건이 만족할 경우 Interrupt를 발생 Interrupt 허용 시 address code 제공 - 초기 상태에서 인터럽트 요청하지 않기 - 인터럽트가 서비스 될 때 인터럽트를 요청하지 않기

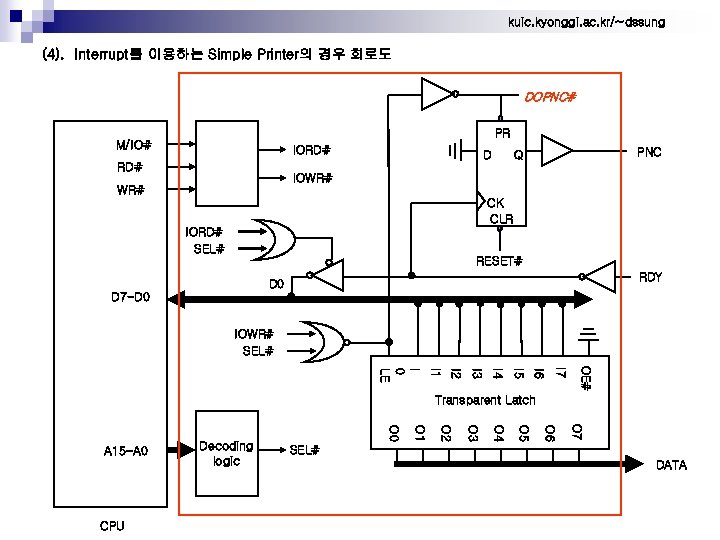

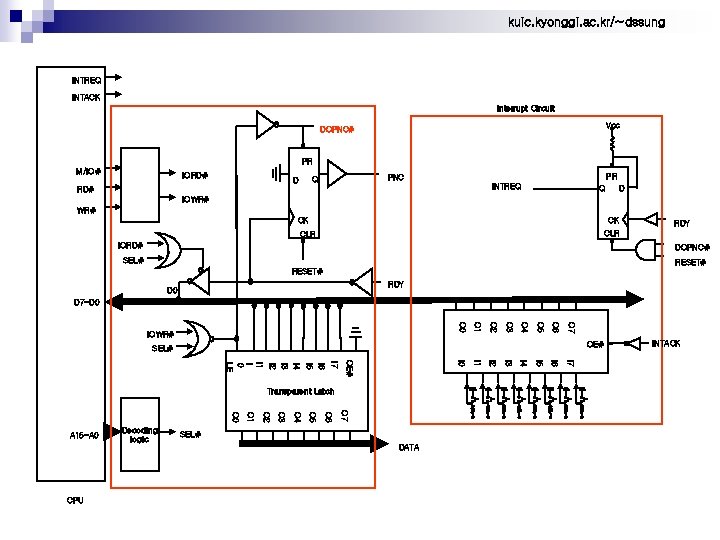

kuic. kyonggi. ac. kr/~dssung (4). Interrupt를 이용하는 Simple Printer의 경우 회로도 DOPNC# PR M/IO# IORD# PNC Q D IOWR# CK CLR IORD# SEL# RESET# RDY D 0 D 7 -D 0 IOWR# SEL# OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch O 7 O 6 O 5 O 4 O 3 O 2 O 1 CPU Decoding logic O 0 A 15 -A 0 SEL# DATA

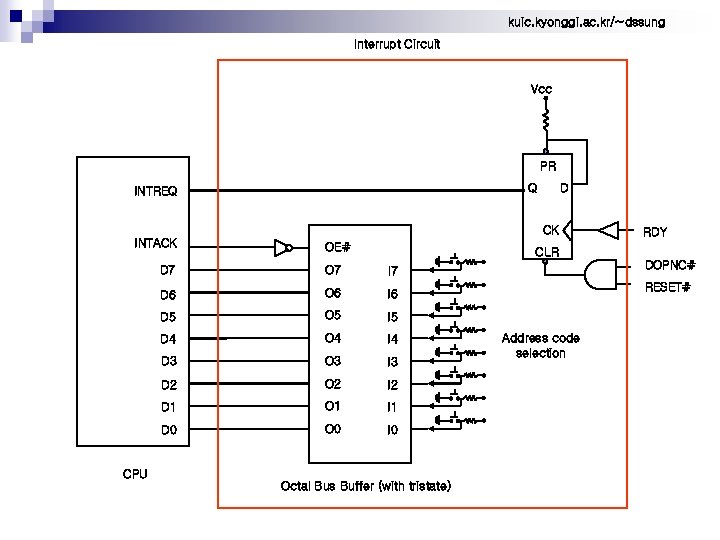

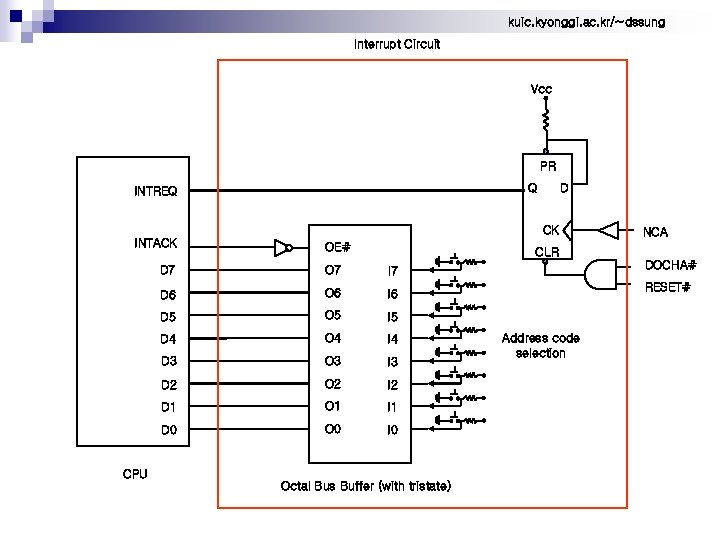

kuic. kyonggi. ac. kr/~dssung Interrupt Circuit Vcc PR D Q INTREQ CK INTACK OE# CLR D 7 O 6 I 6 D 5 O 5 I 5 D 4 O 4 I 4 D 3 O 3 I 3 D 2 O 2 I 2 D 1 O 1 I 1 D 0 O 0 I 0 DOPNC# I 7 D 6 CPU RDY Octal Bus Buffer (with tristate) RESET# Address code selection

kuic. kyonggi. ac. kr/~dssung INTREQ INTACK Interrupt Circuit Vcc DOPNC# PR M/IO# IORD# PR PNC Q D INTREQ RD# Q D IOWR# CK CK RDY CLR IORD# DOPNC# SEL# RESET# RDY D 0 D 7 -D 0 O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 IOWR# OE# SEL# I 7 I 6 I 5 I 4 DATA I 3 SEL# I 2 O 7 O 6 O 5 O 4 O 3 O 2 CPU Decoding logic O 1 O 0 A 15 -A 0 I 1 I 0 OE# I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 LE Transparent Latch INTACK

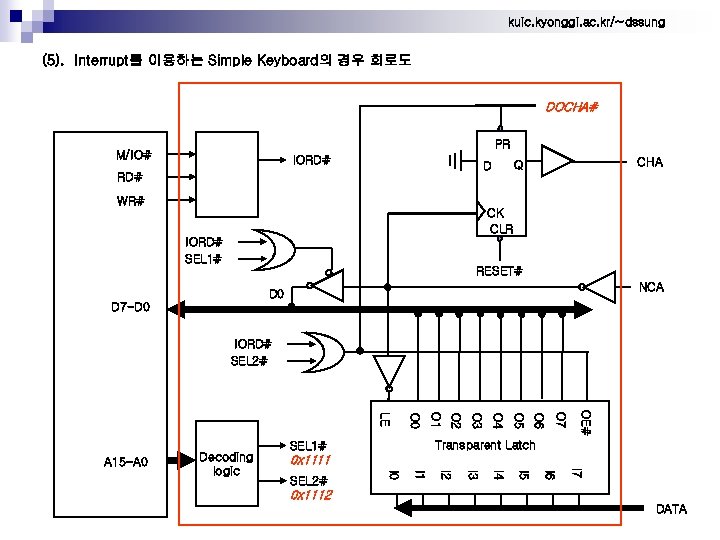

kuic. kyonggi. ac. kr/~dssung (5). Interrupt를 이용하는 Simple Keyboard의 경우 회로도 DOCHA# PR M/IO# IORD# CHA Q D WR# CK CLR IORD# SEL 1# RESET# NCA D 0 D 7 -D 0 IORD# SEL 2# OE# O 7 O 6 O 5 O 4 O 3 O 2 O 1 O 0 LE A 15 -A 0 Transparent Latch SEL 1# 0 x 1111 I 7 I 6 I 5 I 4 I 3 I 2 I 1 SEL 2# I 0 Decoding logic 0 x 1112 DATA

kuic. kyonggi. ac. kr/~dssung Interrupt Circuit Vcc PR D Q INTREQ CK INTACK OE# CLR D 7 O 6 I 6 D 5 O 5 I 5 D 4 O 4 I 4 D 3 O 3 I 3 D 2 O 2 I 2 D 1 O 1 I 1 D 0 O 0 I 0 DOCHA# I 7 D 6 CPU NCA Octal Bus Buffer (with tristate) RESET# Address code selection

kuic. kyonggi. ac. kr/~dssung (6). Interrupt Source가 다수 있는 경우 방법 : Priority Encoder의 이용 O 2 O 1 O 0 Priority Encoder I 2 I 3 I 4 I 5 I 6 I 7 0 0 0 0 0 1 1 X X X X 0 0 0 1 X X X 0 0 1 0 0 0 1 X X X 0 1 0 0 0 1 X X 0 1 1 0 0 0 1 X X X 1 0 0 0 0 1 X 1 1 0 0 0 I 1 I 2 I 3 I 4 I 5 I 6 I 7 I 1 0 GS# 0 0 0 1 1 0 GS* (Group Signal) O 2 O 1 O 0 GS* I 0

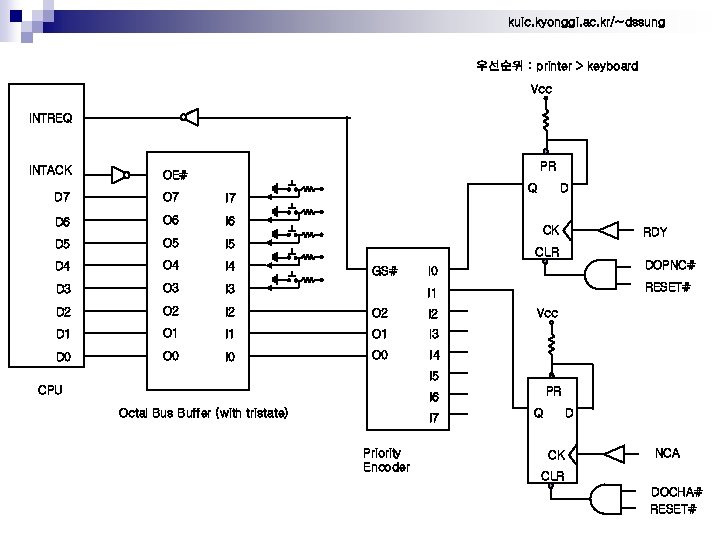

kuic. kyonggi. ac. kr/~dssung 우선순위 : printer > keyboard Vcc INTREQ INTACK PR OE# D Q D 7 O 7 I 7 D 6 O 6 I 6 D 5 O 5 I 5 D 4 O 4 I 4 D 3 O 3 I 3 D 2 O 2 I 2 D 1 O 1 I 3 D 0 O 0 I 4 CK RDY CLR I 0 DOPNC# I 1 GS# RESET# Vcc I 5 CPU PR I 6 Octal Bus Buffer (with tristate) I 7 Priority Encoder D Q CK NCA CLR DOCHA# RESET#

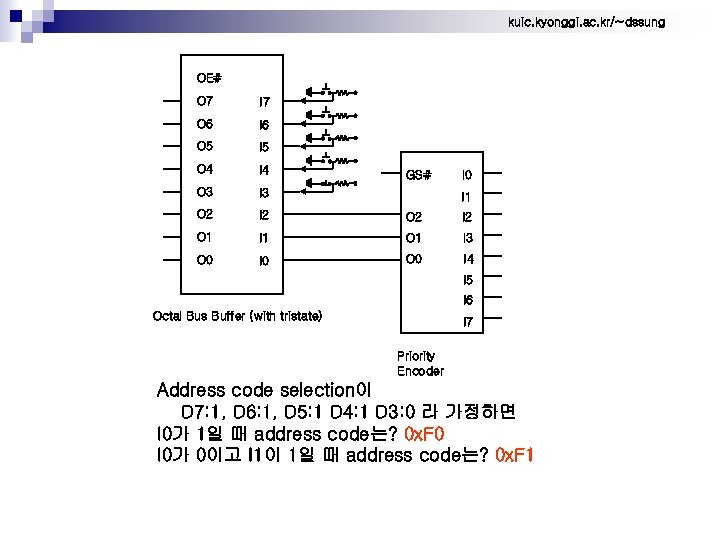

kuic. kyonggi. ac. kr/~dssung OE# O 7 I 7 O 6 I 6 O 5 I 5 O 4 I 4 O 3 I 3 O 2 I 2 O 1 I 1 O 1 I 3 O 0 I 0 O 0 I 4 GS# I 0 I 1 I 5 I 6 Octal Bus Buffer (with tristate) I 7 Priority Encoder Address code selection이 D 7: 1, D 6: 1, D 5: 1 D 4: 1 D 3: 0 라 가정하면 I 0가 1일 때 address code는? 0 x. F 0 I 0가 0이고 I 1이 1일 때 address code는? 0 x. F 1

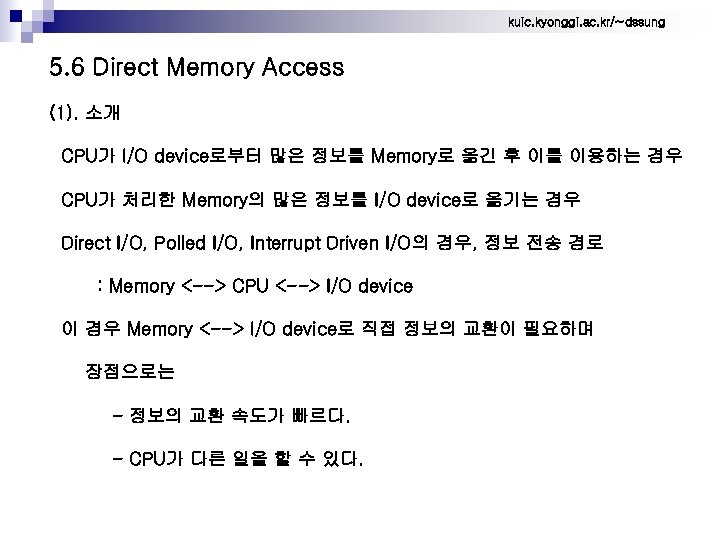

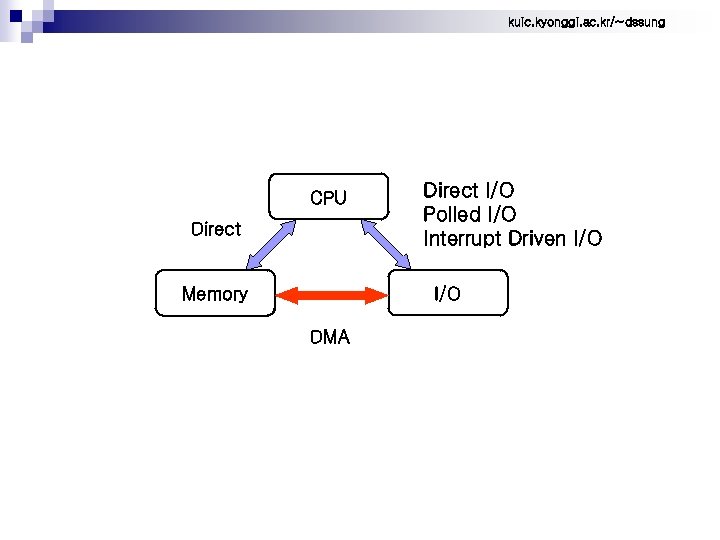

kuic. kyonggi. ac. kr/~dssung 5. 6 Direct Memory Access (1). 소개 CPU가 I/O device로부터 많은 정보를 Memory로 옮긴 후 이를 이용하는 경우 CPU가 처리한 Memory의 많은 정보를 I/O device로 옮기는 경우 Direct I/O, Polled I/O, Interrupt Driven I/O의 경우, 정보 전송 경로 : Memory <--> CPU <--> I/O device 이 경우 Memory <--> I/O device로 직접 정보의 교환이 필요하며 장점으로는 - 정보의 교환 속도가 빠르다. - CPU가 다른 일을 할 수 있다.

kuic. kyonggi. ac. kr/~dssung CPU Direct I/O Polled I/O Interrupt Driven I/O Memory DMA

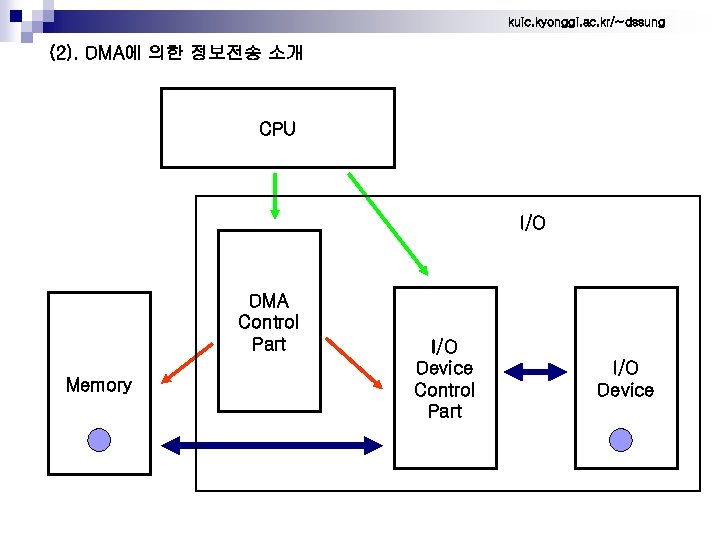

kuic. kyonggi. ac. kr/~dssung (2). DMA에 의한 정보전송 소개 CPU I/O DMA Control Part Memory I/O Device Control Part I/O Device

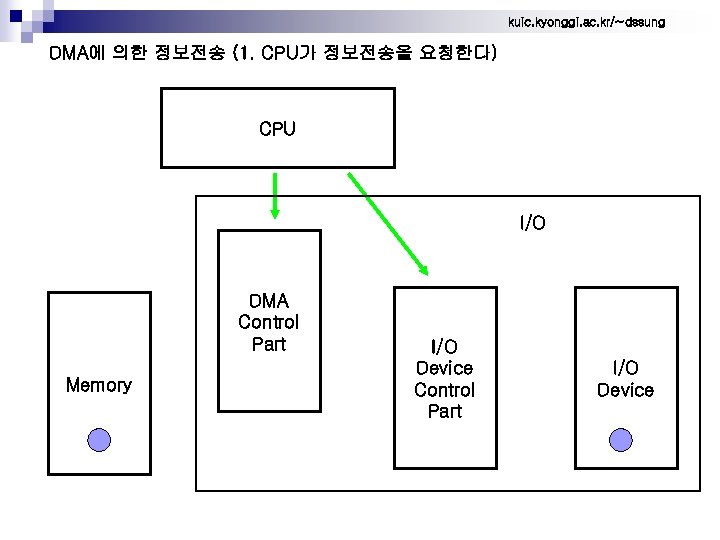

kuic. kyonggi. ac. kr/~dssung DMA에 의한 정보전송 (1. CPU가 정보전송을 요청한다) CPU I/O DMA Control Part Memory I/O Device Control Part I/O Device

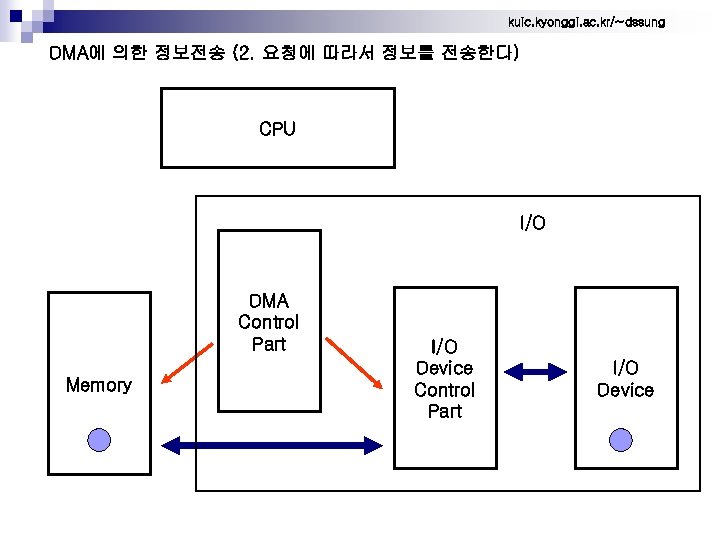

kuic. kyonggi. ac. kr/~dssung DMA에 의한 정보전송 (2. 요청에 따라서 정보를 전송한다) CPU I/O DMA Control Part Memory I/O Device Control Part I/O Device

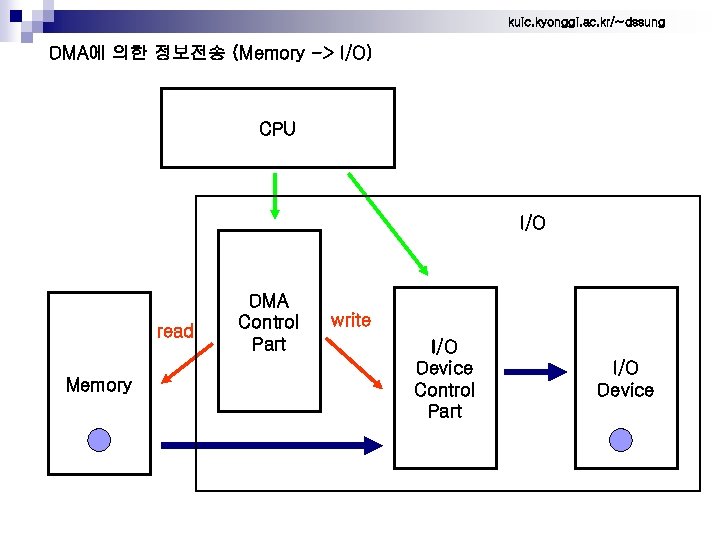

kuic. kyonggi. ac. kr/~dssung DMA에 의한 정보전송 (Memory -> I/O) CPU I/O read Memory DMA Control Part write I/O Device Control Part I/O Device

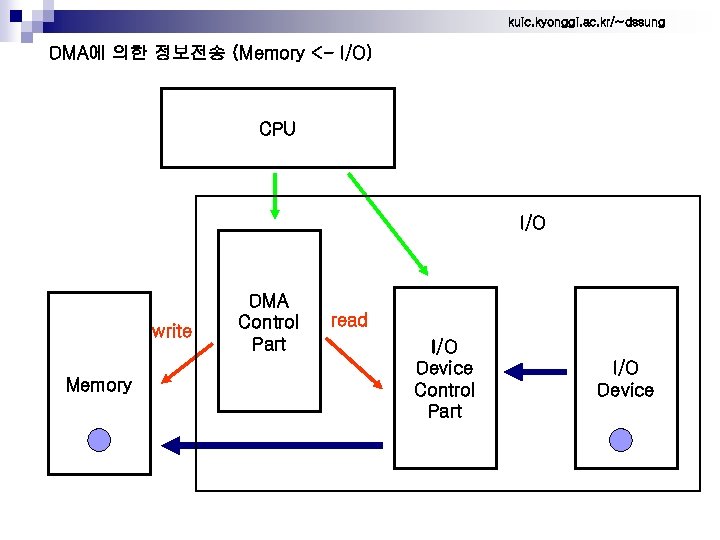

kuic. kyonggi. ac. kr/~dssung DMA에 의한 정보전송 (Memory <- I/O) CPU I/O write Memory DMA Control Part read I/O Device Control Part I/O Device

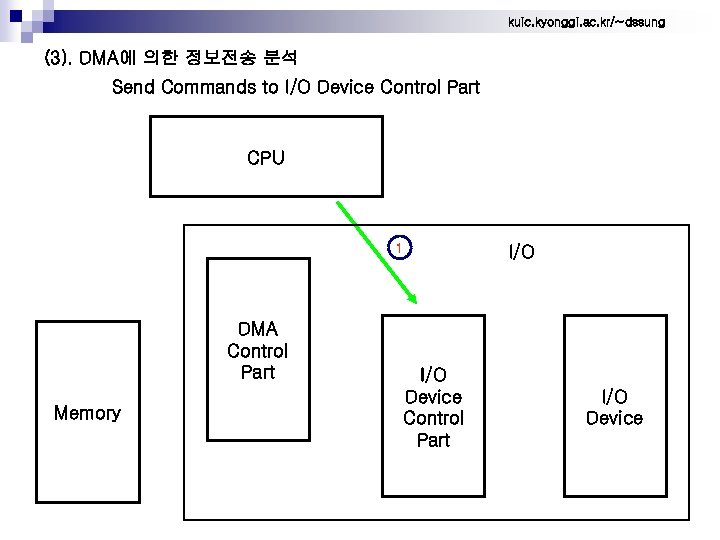

kuic. kyonggi. ac. kr/~dssung (3). DMA에 의한 정보전송 분석 Send Commands to I/O Device Control Part CPU 1 DMA Control Part Memory I/O Device Control Part I/O Device

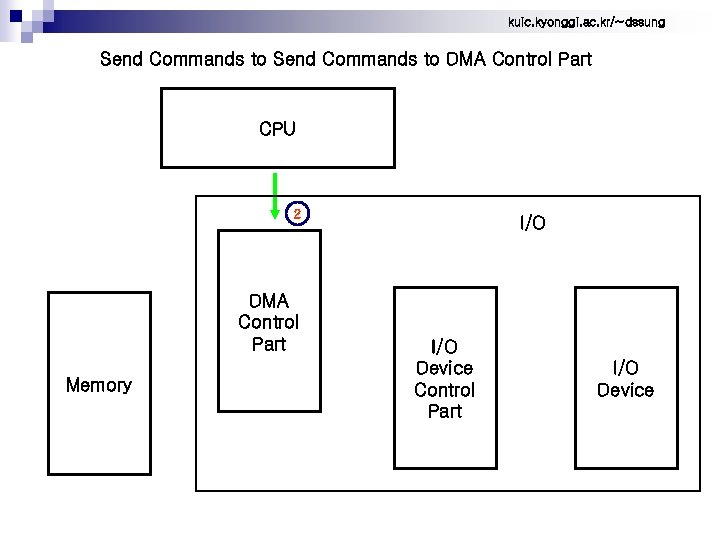

kuic. kyonggi. ac. kr/~dssung Send Commands to DMA Control Part CPU 2 DMA Control Part Memory I/O Device Control Part I/O Device

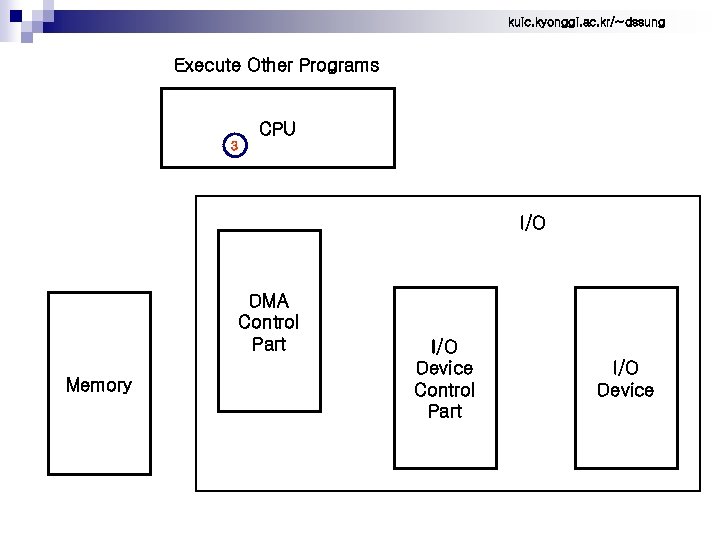

kuic. kyonggi. ac. kr/~dssung Execute Other Programs CPU 3 I/O DMA Control Part Memory I/O Device Control Part I/O Device

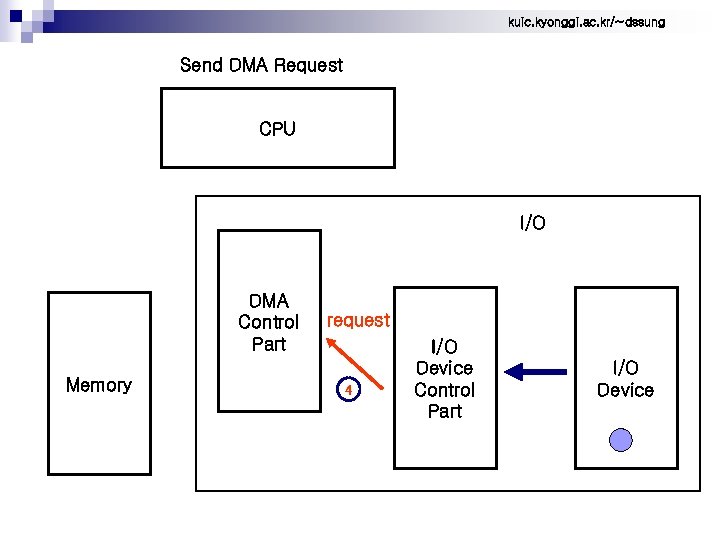

kuic. kyonggi. ac. kr/~dssung Send DMA Request CPU I/O DMA Control Part Memory request 4 I/O Device Control Part I/O Device

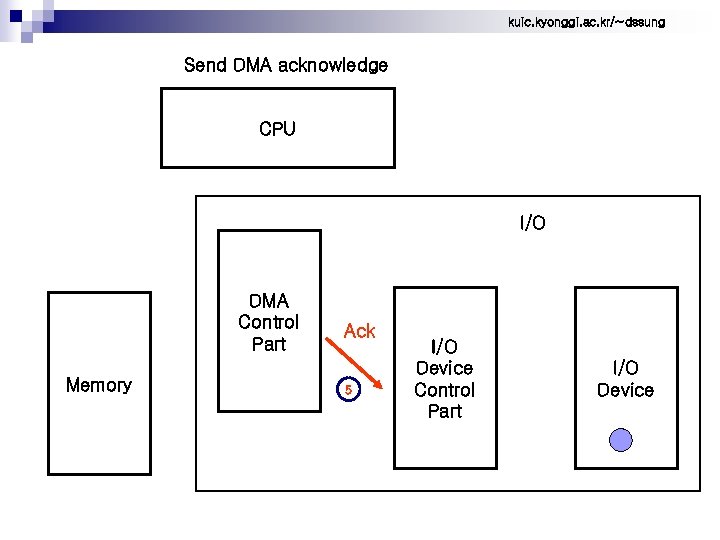

kuic. kyonggi. ac. kr/~dssung Send DMA acknowledge CPU I/O DMA Control Part Memory Ack 5 I/O Device Control Part I/O Device

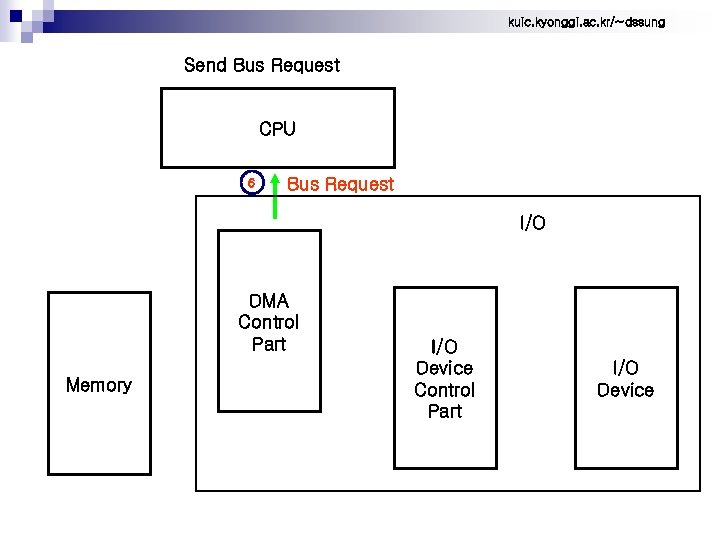

kuic. kyonggi. ac. kr/~dssung Send Bus Request CPU 6 Bus Request I/O DMA Control Part Memory I/O Device Control Part I/O Device

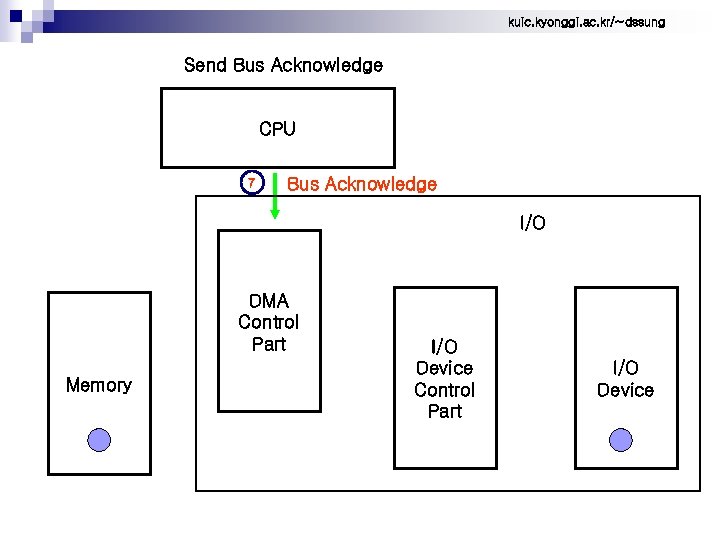

kuic. kyonggi. ac. kr/~dssung Send Bus Acknowledge CPU 7 Bus Acknowledge I/O DMA Control Part Memory I/O Device Control Part I/O Device

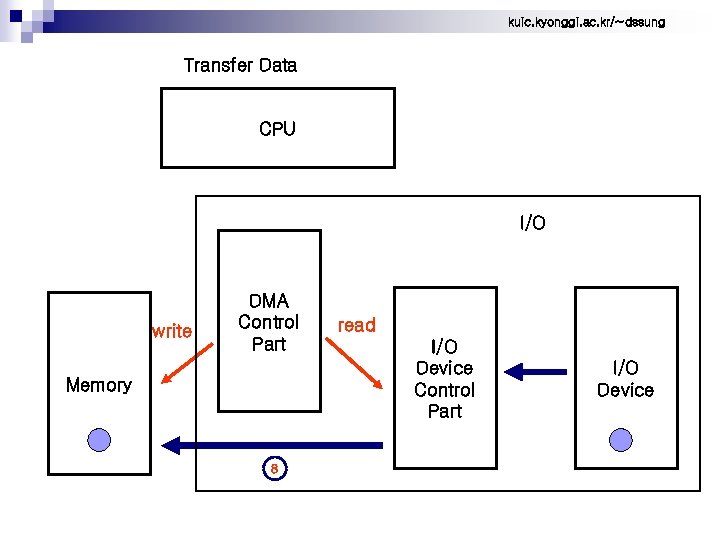

kuic. kyonggi. ac. kr/~dssung Transfer Data CPU I/O write DMA Control Part Memory 8 read I/O Device Control Part I/O Device

![kuic. kyonggi. ac. kr/~dssung (4). DMA에 의한 정보전송 정리 [CPU] (a). CPU -> I/O kuic. kyonggi. ac. kr/~dssung (4). DMA에 의한 정보전송 정리 [CPU] (a). CPU -> I/O](https://present5.com/presentation/6a51effa7d67934f1735f1a875c28033/image-106.jpg)

kuic. kyonggi. ac. kr/~dssung (4). DMA에 의한 정보전송 정리 [CPU] (a). CPU -> I/O Device Control Part Send Commands to I/O Device Control Part ex) 7 T 8 S read (b). CPU -> DMA Control Part (DMA Controller) Send Commands to DMA Control Part (DMA Controller) - Starting Memory Address ex) 5000 - Count ex) 500 - Direction (Memory -> I/O, Memory <- I/O) ex) Memory <- I/O - Start Command (c). Execute Other Programs (g). CPU -> DMA Control Part Send Bus Acknowledge

![kuic. kyonggi. ac. kr/~dssung [I/O Device Control Part] (d). I/O Device Control Part -> kuic. kyonggi. ac. kr/~dssung [I/O Device Control Part] (d). I/O Device Control Part ->](https://present5.com/presentation/6a51effa7d67934f1735f1a875c28033/image-107.jpg)

kuic. kyonggi. ac. kr/~dssung [I/O Device Control Part] (d). I/O Device Control Part -> DMA Control Part Send DMA Request after executes Commands from CPU

![kuic. kyonggi. ac. kr/~dssung [DMA Control Part] (e). DMA Control Part -> I/O Device kuic. kyonggi. ac. kr/~dssung [DMA Control Part] (e). DMA Control Part -> I/O Device](https://present5.com/presentation/6a51effa7d67934f1735f1a875c28033/image-108.jpg)

kuic. kyonggi. ac. kr/~dssung [DMA Control Part] (e). DMA Control Part -> I/O Device Control Part Send DMA acknowledge (f). DMA Control Part -> CPU Send Bus Request (h). Transfer Data (Memory -> I/O) [DMA Control Part -> Memory] Send Address, Data Transfer Control (Read) [DMA Control Part -> I/O Device Control Part] Send I/O Write (Memory <- I/O) [DMA Control Part -> I/O Device Control Part] Send I/O Read [DMA Control Part -> Memory] Send Address, Data Transfer Control (Write)

kuic. kyonggi. ac. kr/~dssung (i). Decrement Word Count Increment Starting Address (j). if Word Count Zero then Bus Release and Generate Interrupt to CPU else Go to Step (h).

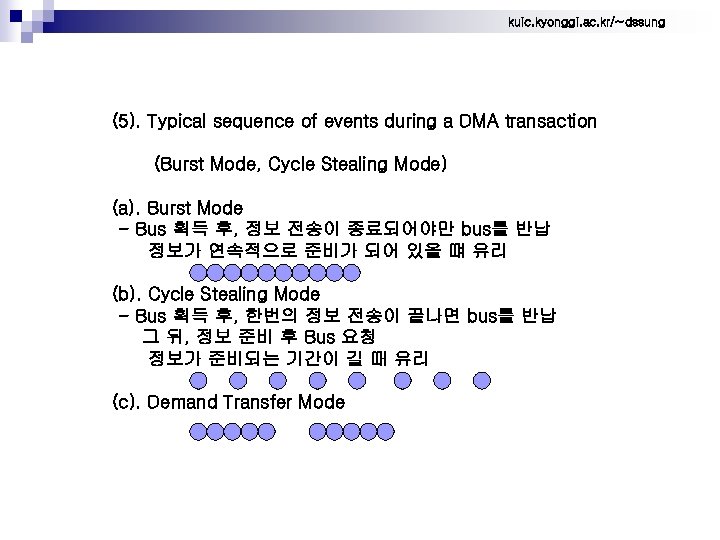

kuic. kyonggi. ac. kr/~dssung (5). Typical sequence of events during a DMA transaction (Burst Mode, Cycle Stealing Mode) (a). Burst Mode - Bus 획득 후, 정보 전송이 종료되어야만 bus를 반납 정보가 연속적으로 준비가 되어 있을 떄 유리 (b). Cycle Stealing Mode - Bus 획득 후, 한번의 정보 전송이 끝나면 bus를 반납 그 뒤, 정보 준비 후 Bus 요청 정보가 준비되는 기간이 길 때 유리 (c). Demand Transfer Mode

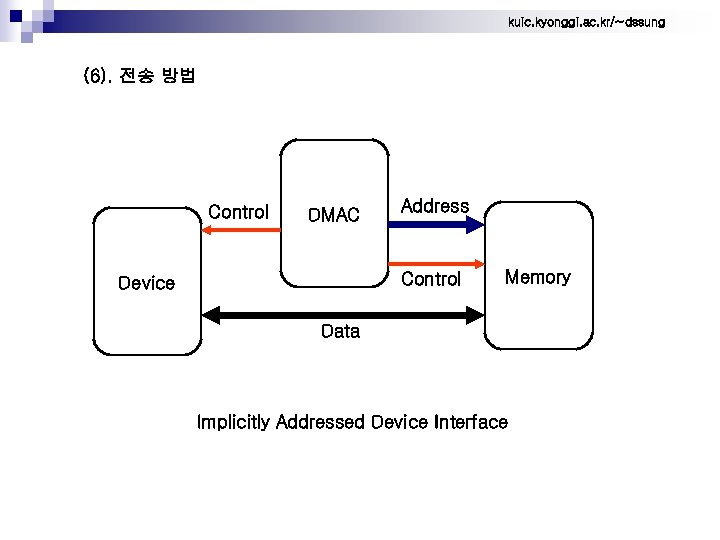

kuic. kyonggi. ac. kr/~dssung (6). 전송 방법 Control DMAC Address Control Device Memory Data Implicitly Addressed Device Interface

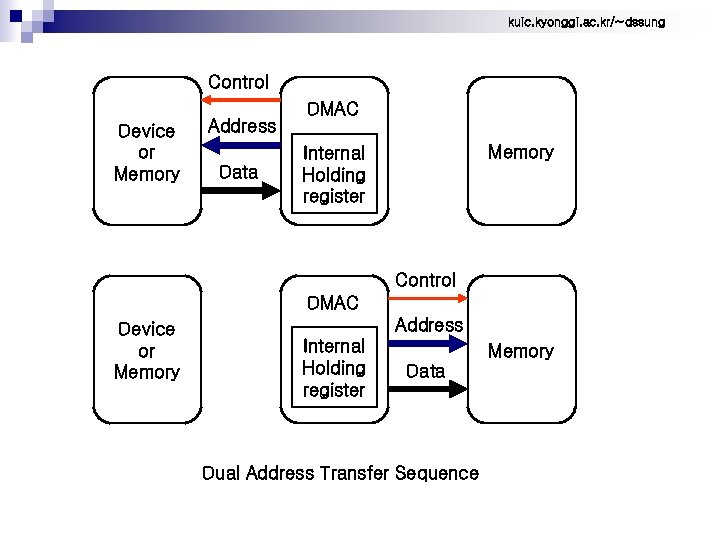

kuic. kyonggi. ac. kr/~dssung Control Device or Memory Address Data DMAC Memory Internal Holding register Control DMAC Device or Memory Address Internal Holding register Memory Data Dual Address Transfer Sequence

6a51effa7d67934f1735f1a875c28033.ppt